# ANALOG DEVICES

# 2 Pair/1 Pair ETSI Compatible HDSL Analog Front End

# AD6472

### FEATURES

Integrated Front End for Single Pair or Two Pair HDSL Systems

Meets ETSI Specifications

Supports 1168 Kbps and 2.32 Mbps

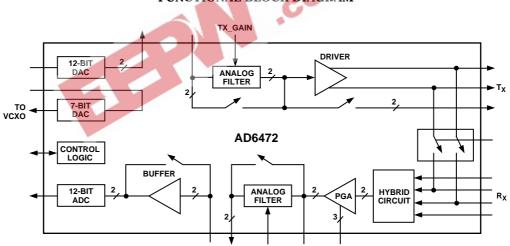

Transmit and Receive Signal Path Functions Receive Hybrid Amplifier, PGA and ADC Transmit DAC, Filter and Differential Outputs Programmable Filters

Control and Ancillary Functions

Timing Recovery DAC

Normal Loopback and Low Power Modes

Simple Interface-to-Digital Transceivers

Single 5 V Power Supply

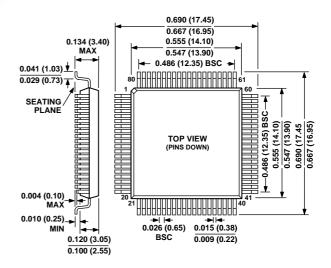

Power Consumption: 320 mW—(Excluding Driver) Package: 80-Lead MQFP

Operating Temperature: -40°C to +85°C

### **GENERAL DESCRIPTION**

The AD6472 is a single chip analog front end for two pair or single pair HDSL applications that use 1168 Kbps or 2.32 Mbps data rates.

The AD6472 integrates all the transmit and receive functional blocks together with the timing recovery DAC.

The digital interface is designed to support industry standard digital transceivers.

While providing the full analog front end for ETSI standards (two pair or single pair HDSL applications) the AD6472 supports other applications because the architecture allows for bypassing the functional blocks.

The normal, low power, and loopback modes and the digital interface combine to make the AD6472 simple to integrate into systems.

### FUNCTIONAL BLOCK DIAGRAM

#### REV.0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site: http://www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 1998

# AD6472—SPECIFICATIONS (T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub> unless otherwise noted)

| Parameter                                                                                                                                                                                                                                                                                                                                                         | Min                                                          | Тур                              | Max               | Units                                | Condition                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------|-------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRANSMIT CHANNEL                                                                                                                                                                                                                                                                                                                                                  |                                                              |                                  |                   |                                      |                                                                                                                                                                |

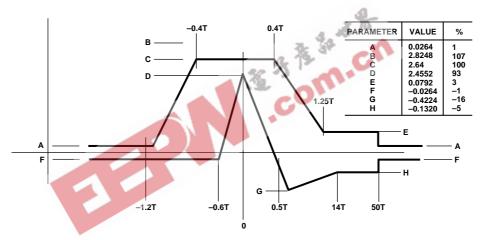

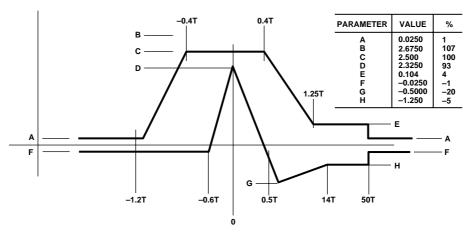

| SNR<br>THD                                                                                                                                                                                                                                                                                                                                                        | 68<br>66                                                     | 71<br>71                         |                   | dB<br>dB                             | The complete transmit path spectrum and pulse shape comply with ETSI requirements.                                                                             |

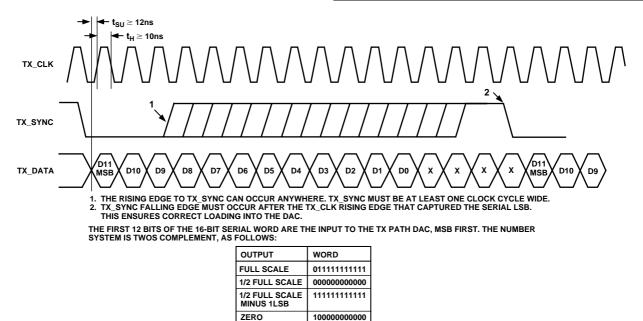

| TRANSMIT DAC<br>Clock Frequency<br>Resolution<br>Update Rate<br>Output Voltage                                                                                                                                                                                                                                                                                    |                                                              | 12<br>2                          | 18.688<br>1168    | MHz<br>Bits<br>kHz<br>V p-p Diff     | The transmit DAC maximum update rate is half<br>the maximum output data rate, i.e., 1168 kHz.<br>The maximum transmit clock is 16 × 1168 =<br>18.688 MHz.      |

| TRANSMIT FILTER<br>Corner Frequency (3 dB) <sup>1</sup><br>Accuracy<br>Gain                                                                                                                                                                                                                                                                                       |                                                              | 320<br>535<br>±5<br>9.53<br>3.53 | ±10               | kHz<br>kHz<br>%<br>dB<br>dB          | MODE_SEL1 = 0<br>MODE_SEL1 = 1                                                                                                                                 |

| LINE DRIVER<br>VCM<br>Output Power<br>Output Voltage                                                                                                                                                                                                                                                                                                              |                                                              | 2.5<br>13.5<br>6                 |                   | V<br>dBm<br>V p-p Diff               | Transformer Turns Ratio = 1:2.3 at 50 kHz<br>When Loaded by ETSI (RTR/TM3036)<br>HDSL Test Loops                                                               |

| TRANSMIT VOLTAGE LEVEL                                                                                                                                                                                                                                                                                                                                            |                                                              | 6<br>3                           |                   | V p-p Diff<br>V p-p Diff             | $TX\_GAIN = 0$ $TX\_GAIN = 1$                                                                                                                                  |

| RECEIVE CHANNEL<br>SNR<br>THD                                                                                                                                                                                                                                                                                                                                     | 68<br>66                                                     | 71<br>71                         |                   | dB<br>dB                             | cn                                                                                                                                                             |

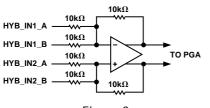

| HYBRID INTERFACE<br>Input Voltage Range<br>Input Impedance                                                                                                                                                                                                                                                                                                        |                                                              | 10                               | 5                 | V p-p Diff<br>kΩ                     | $V_{\rm CM}$ = 2.5 V. See Figure 3                                                                                                                             |

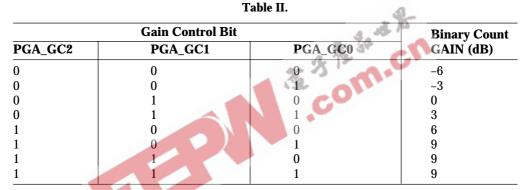

| PROGRAMMABLE GAIN AMPLIFIER<br>Overall Gain Accuracy<br>Gain Step<br>Gain Step Accuracy                                                                                                                                                                                                                                                                           |                                                              | ±1<br>3<br>±0.25                 |                   | dB<br>dB<br>dB                       | Condition –6 dB to +9 dB                                                                                                                                       |

| RECEIVE FILTER<br>Corner Frequency (-3 dB) <sup>1</sup><br>Accuracy                                                                                                                                                                                                                                                                                               |                                                              | $320 \\ 640 \\ \pm 5$            | ±10               | kHz<br>kHz<br>%                      | MODE_SEL1 = 0<br>MODE_SEL1 = 1                                                                                                                                 |

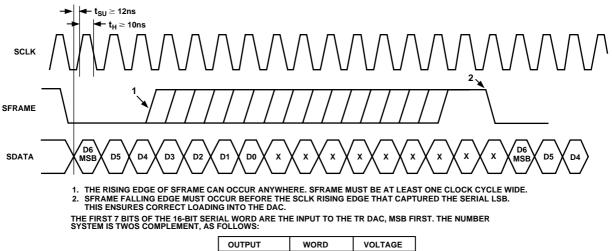

| TIMING RECOVERY DAC<br>Resolution<br>Output Low<br>Output High                                                                                                                                                                                                                                                                                                    | 7                                                            | 0.5<br>4.5                       |                   | Bits<br>V<br>V                       | Guaranteed Monotonic                                                                                                                                           |

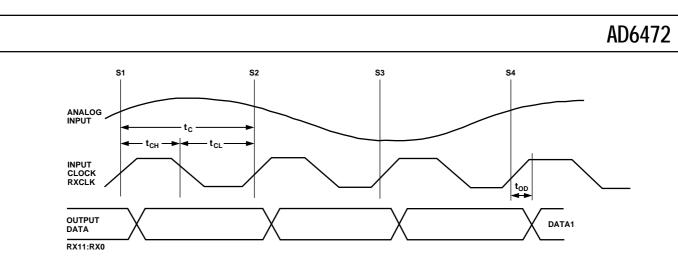

| $\begin{array}{c} \textbf{DIGITAL INTERFACE} \\ \textbf{Input Logic High, V_{IH}} \\ \textbf{Input Logic Low, V_{IL}} \\ \textbf{Output Logic High, V_{OH}} \\ \textbf{Output Logic Low, V_{OL}} \\ \textbf{Input Logic High, V_{IH}} \\ \textbf{Input Logic Low, V_{IL}} \\ \textbf{Output Logic Low, V_{IL}} \\ \textbf{Output Logic High, V_{OH}} \end{array}$ | 3.3<br>V <sub>DD</sub> - 0.3<br>2.0<br>V <sub>DD</sub> - 0.3 |                                  | 0.8<br>0.4<br>0.2 | V<br>V<br>V<br>V<br>V<br>V<br>V<br>V | 5 V Supply, $V_{\rm MIN}$ to $V_{\rm MAX}$ 3.3 V Supply, $V_{\rm MIN}$ to $V_{\rm MAX}$                                                                        |

| POWER SUPPLY VOLTAGE                                                                                                                                                                                                                                                                                                                                              | 4.75<br>3.15                                                 | 5<br>3.3                         | 5.25<br>3.45      | V<br>V                               | V <sub>MIN</sub> to V <sub>MAX</sub><br>5 V Supply<br>3.3 V Supply                                                                                             |

| POWER SUPPLY CURRENT<br>Normal Mode, Excl. Driver<br>OVRSAMP Mode<br>Line Driver<br>Low Power Mode                                                                                                                                                                                                                                                                |                                                              | 65<br>73<br>50<br>17             |                   | mA<br>mA<br>mA<br>mA                 | $V_{MIN}$ to $V_{MAX}$ , $T_{MIN}$ to $T_{MAX}$<br>5 V Supply, MODE_SEL1 = 0<br>5 V Supply, MODE_SEL1 = 1, MODE_SEL0 = 1<br>With 50 $\Omega$ Differential Load |

| OPERATING TEMPERATURE RANGE                                                                                                                                                                                                                                                                                                                                       | -40                                                          |                                  | +85               | °C                                   | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                                           |

NOTES <sup>1</sup>The ADC clock period t(1÷ f) is used for the dynamic tuning of the Tx and Rx filters.

Specifications subject to change without notice.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage0.3 V to +6.0 V                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------|

| Input Voltage                                                                                                                            |

| Output Voltage Swing $\dots \dots \dots$ |

| Operating Temperature Range (Ambient)40°C to +85°C                                                                                       |

| Storage Temperature Range                                                                                                                |

| Lead Temperature (5 sec) MQFP+280°C                                                                                                      |

\*Stresses above those listed in this section may cause permanent damage to the device. This is a stress rating only, functional operation of the device at these or any other conditions above those in the operation section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Thermal Characteristics**

80-Lead Plastic Quad Flatpack Package  $\dots \dots \theta_{JA} = 45^{\circ}C/W$

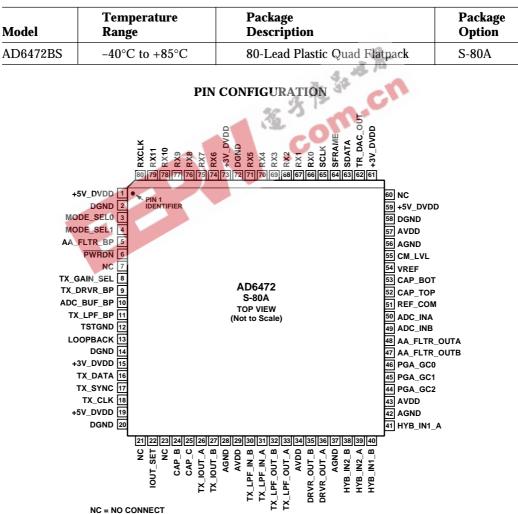

### **ORDERING GUIDE**

### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD6472 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### PIN CONFIGURATIONS

| 1   +5 V_DyDD   +5 V_Digital Supply.   41   HYB_INL_A   Hybrid Inverting Input.     2   DGND   Digital Ground.   42   AGND   Analog Ground.     4   MODE_SELD   Bit Rate—Filter Corner Select.   43   AVDD   +5 V Analog Supply.     5   AA_FLTR_BP   Antialisaing Filter Bypass.   46   PGA_GC1   PGA Gain Select Bits.     6   FWRDN   Power-Down Active Low.   46   PGA_GC1   PGA Gain Select Bits.     9   TX_GAIN SEL   Transmit Attenuation (6 dB) Select.   47   AA_FLTR_OUTB   Differential Output of the Antialiasing Filter.     10   ADC_BUF_BP   ADC Buffer Bypass.   49   ADC_INB   Differential Input to the ADC.     11   TX_LPF_BP   Transmit Filter Bypass.   49   ADC_INB   Differential Input to the ADC.     12   TSTGND   Factory test pin. Connect to DGND.   50   ADC_INA   Differential Input to the ADC.     13   LOOPBACK   LoopBack Select.   52   CAP_TOP   Decoupling Pin for ADC Reference.     14   TX_SYNC   Transmit Data Input.   57   CM_LVL   Case gond.     16   TX_DXTA   Transmit Data Input.   56   KND   Aiso Ground.     17   TX_SYNC   Transmit Data Inp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Pin | Mnemonic     | Description                    | Pin | Mnemonic     | Description                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|--------------------------------|-----|--------------|---------------------------------|

| 3   MODE_SEL0   Bit Rate—Filter Corner Select.   43   AVDD   +5 V Ånalog Supply.     4   MODE_SEL1.   Bit Rate—Filter Corner Select.   44   PCA_CC2   PCA Cain Select Bits.     6   PWRDN   Power-Down Active Low.   46   PCA_CC0   PCA Cain Select Bits.     7   NC   No Connect.   47   AA_FLTR_OUTB   Differential Output of the Antialiasing Filter.     9   TX_CGAIN_SEL   Transmit Attenuation (6 dB) Select.   40   AA_FLTR_OUTA   Differential Output of the Antialiasing Filter.     10   ADC_BUF_BP   ADC Buffer Bypass.   49   ADC_INB   Differential Input to the ADC.     12   TSTGND   Factory test pin. Connect to DGND.   50   ADC_INA   Differential Input to the ADC.     14   DGND   Digital Ground.   52   CAP_DOT   Decoupling Pin for ADC Reference.     15   +3 V_DVDD   +3.3 V Digital Supply.   53   CAP_BOT   Decoupling Pin for ADC Reference.     16   TX_DATA   Transmit Data Input.   54   CM_EVL   CM-BOT   Digital Ground.     18   TX_CLK   Transmit Data Input.   54   ANDD   +5 V_DVD   +5 V_DVD     19   +5 V_DVDD   +5 V Digital Supply.   64   +3 V_DVD   +5 V Digital Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1   | +5 V_DVDD    | +5 V Digital Supply.           | 41  | HYB_IN1_A    | Hybrid Inverting Input.         |

| 4MODE_SEL1Bit Rate—Filter Corner Select.44PGA_GC2PGA Gain Select Bits.5AA_FLTR_BPAntialiasing Filter Bypass.45PGA_GC1PGA Gain Select Bits.7NCNo Connect.47AA_FLTR_OUTBDifferential Output of the<br>Antialiasing Filter.8TX_GAIN_SELTransmit Driver Bypass.48AA_FLTR_OUTBDifferential Output of the<br>Antialiasing Filter.10ADC_BUF_BPADC BUF Bypass.40ADC_INADifferential Input to the ADC.11TX_LPF_BPTransmit Pilter Bypass.40ADC_INADifferential Input to the ADC.13LOOPBACKLoopback Select.51REF_COMReference Common.14DGNDDigital Ground.52CAP_DOPDecoupling Pin for ADC Reference.17TX_SYNCTransmit Data Frame Sync Input.57AMDD+5 V Digital Supply.5318TX_CLKTransmit Data Frame Sync Input.56CMEVDHaalag Ground.19+5 V_DVDD+5 V Digital Supply.56AMDDHogital Ground.22IOUT_SETDAC Complementary Current Foll Scale With Resistor Lorent Foll Scale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2   | DGND         | Digital Ground.                | 42  | AGND         | Analog Ground.                  |

| 5   A.FLTR_BP   Antialiasing Filter Bypass.   45   PGA_CC1   PGA Gain Select Bits.     6   PWRDN   Power-Down Active Low.   46   PGA_CC0   PGA Gain Select Bits.     7   NC   No Connect.   47   A.FLTR_OUTB   Differential Output of the Antialiasing Filter.     9   TX_DRVR_BP   Transmit Driver Bypass.   40   A.FLTR_OUTB   Differential Input to the ADC.     10   ADC_BUF_BP   ADC DE fuffer Bypass.   40   ADC_INB   Differential Input to the ADC.     11   TX_LDRVR_BD   Transmit Filter Bypass.   40   ADC_INB   Differential Input to the ADC.     12   TSTGND   Factory test pin. Connect to DGND.   50   ADC_INB   Differential Input to the ADC.     14   DGND   Digital Ground.   52   CAP_DOT   Decoupling Pin for ADC Reference.     17   TX_SVNC   Transmit Icbt Input.   54   VREF   Corumon-Mode Level.     18   TX_CLK   Transmit Cock Input.   56   ACMD   ADG INB   Digital Ground.     19   +5 V_DVDD   +5 V Digital Supply.   57   ADD   +5 V Analog Ground.   41     22   IOUT_SET   DAC Competer Informal Node.   58   NC   No Connect.   58     23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3   | MODE_SEL0    | Bit Rate—Filter Corner Select. | 43  | AVDD         | +5 V Analog Supply.             |

| 6   FWRDN   Power-Doom Active Low.   46   PGA_GC0   PGA Gain Select Bits.     7   NC   No Connect.   47   AA.FLTR_OUTB   Antialissing Filter.     9   TX.DRVR_BP   Transmit Driver Bypass.   48   AA_FLTR_OUTA   Differential Output of the Antialissing Filter.     10   ADC_BUF_BP   Transmit Filter Bypass.   49   AD_C_INB   Differential Input to the ADC.     11   TX_LPF_BP   Transmit Filter Bypass.   49   AD_C_INB   Differential Input to the ADC.     12   TSTGND   Factory test pin. Connect to DGND.   50   ADC_INB   Differential Input to the ADC.     13   LOOPBACK   Loopback Select.   52   CAP_BOT   Decoupling Pin for ADC Reference.     15   +3 V_DVDD   +3.3 V Digital Supply.   53   CAP_BOT   Common-Mode Level.     17   TX_STAK   Transmit Data Input.   56   ACMD   46ND   450     18   TX_CLK   Transmit Clock Input.   57   ADDD   +5 V Digital Supply.   57   ADDD   +5 V Analog Supply.     21   NC   No Connect.   61   +3 V_DVDD   +5 V Digital Supply.   56     22   IOUT_SET   DAC Output Current Full Scale   60   NC   No Connect.  <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4   | MODE_SEL1    | Bit Rate—Filter Corner Select. | 44  | PGA_GC2      | PGA Gain Select Bits.           |

| 7NCNo Connect.47AA_FLTR_OUTB<br>AA_FLTR_OUTB<br>Differential Output of the<br>Antialiasing Filter.8TX_GAIN_SELTransmit Attenuation (6 dB) Selet.AA_FLTR_OUTA<br>ATTENAME Driver Bypass.MA_FLTR_OUTA<br>ALLER_OUTADifferential Output of the<br>Antialiasing Filter.10ADC_BUF_BPADC Buffer Bypass.49ADC_INBDifferential Input to the ADC.11TX_LPF_BPTransmit Differ Bypass.49ADC_INADifferential Input to the ADC.13LOOPBACKLoopback Select.51REF_COMReference Common.14DGNDDigital Ground.52CAP_TOPDecoupling Pin for ADC Reference.15+3 V_DVDD+3 V Digital Supply.53CAP_BOTDecoupling Pin for ADC Reference.16TX_CLKTransmit Data Input.54VKEFExternal Voltage Reference.17TX_SYNCTransmit Data Frame Sync Input.56AKNDAnalog Ground.18TX_CLKTransmit Data Frame Sync Input.57DeCNDDigital Ground.20DGNDDigital Ground.57PGNDNo Connect.7621NCNo Connect.61+3 V_DVDD+5 V Digital Supply.7322IOUT_SETDAC Output Current Full Scale<br>(With Restor to Ground).62TR_DAC_OUTTming Recovery DAC Output23NCNCNC Connect.64+3 V_DVDD+5 V Digital Supply.24CAP_BDecoupling Pin for Internal Node.62SDATASerial Data <td>5</td> <td>AA_FLTR_BP</td> <td>Antialiasing Filter Bypass.</td> <td>45</td> <td>PGA_GC1</td> <td>PGA Gain Select Bits.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5   | AA_FLTR_BP   | Antialiasing Filter Bypass.    | 45  | PGA_GC1      | PGA Gain Select Bits.           |

| 8     TX_GAIN_SEL     Transmit Attenuation (6 dB) Select.     Image: Constraint of the const | 6   | PWRDN        | Power-Down Active Low.         | 46  | PGA_GC0      | PGA Gain Select Bits.           |

| 9TX_DRVR_BPTransmit Driver Bypass.48AA_FLTR_OUTADifferential Output of the<br>Antialiasing Filter.10ADC_BUF_BPADC Buffer Bypass.49ADC_INADifferential Input to the ADC.11TX_LPF_BPTransmit Filter Bypass.49ADC_INADifferential Input to the ADC.13LOOPBACKLoopback Select.51REF_COMReference Common.14DGNDDigital Ground.52CAP_BOTDecoupling Pin for ADC Reference.15+3 V_DVDD+3.3 V Digital Supply.53CAP_BOTExternal Voltage Reference.16TX_OATATransmit Data Input.54VREFCommon Mode Level.17TX_SYNCTransmit Data Input.56ACNDAnalog Ground.19+5 V_DVDD+5 V Digital Supply.56ACNDAnalog Ground.20DGNDDigital Ground.58DGNDDigital Ground.21NCNo Connect.59+5 V_DVDD+5 V Digital Supply.22IOUT_SETDAC Output Current Full Scale60NCNC Connect.23NCNo Connect.61+3 V_DVDD+3 V Digital Supply.24CAP_BDecoupling Pin for Internal Node.62TR_DAC_OUTTiming Recovery DAC Output25CAP_CDecoupling Pin for Internal Node.63SDATASerial Data26TX_IOUT_BTXDAC Complementary Current of64SFRAMEFrame Sync for Timing Recovery.28AGNDAnalog Ground. </td <td></td> <td></td> <td></td> <td>47</td> <td>AA_FLTR_OUTB</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |              |                                | 47  | AA_FLTR_OUTB |                                 |

| 10ADC BUF JP<br>ADC BUTE Bypas.ADC Buter Bypas.40ADC INTAntialiasing Filter.11TX_LPF_BP<br>Transmit Filter Bypas.40ADC_INADifferential Input to the ADC.12TSTGNDFactory test pin. Connect to DGND.50ADC_INADifferential Input to the ADC.14DCNDDigital Ground.52CAP_TOPDecoupling Pin for ADC Reference.15 $+3$ V_DVDD $+3.3$ V Digital Supply.53CAP_BOTDecoupling Pin for ADC Reference.16TX_DATATransmit Data Input.54VREFExternal Voltage. Reference.17TX_SYNCTransmit Data Input.56ACNDAnalog Ground.18TX_CLKTransmit Clock Input.56ACNDAnalog Ground.19 $+5$ VDDD $+5$ V Digital Supply.56ACNDAnalog Ground.21NCNo Connect.59 $+5$ V_DVDD $+5$ V Digital Supply.22IOUT_SETDAC Output Current Full Scale60NCNo Connect.23NCNo Congoet.61 $+3$ V_DVDD $+3$ V Digital Supply.24CAP_CDecoupling Pin for Internal Node.62TR_DAC_OUT25CAP_CDecoupling Pin for Internal Node.62SFRAME26TX_IOUT_BTXDAC Complementary Current64SFRAMEFrame Sync for Timing Recovery DAC.27TX_IOUT_BDifferential Input to LPF.67RX1Digital Output Data.30TX_LPF_IN_BDifferential Input to LPF. <td></td> <td></td> <td></td> <td>40</td> <td></td> <td>-</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |              |                                | 40  |              | -                               |

| 16INDECLOP JATINDECODE Spires49ADC_INBDifferential Input to the ADC.11TX_LPF_BPFactory test pin. Connect to DGND.50ADC_INADifferential Input to the ADC.12TSTCNDFactory test pin. Connect to DGND.50ADC_INADifferential Input to the ADC.13LOOPBACKLoopback Select.51REF_COMReference Common.14DGNDDigital Ground.52CAP_TOPDecoupling Pin for ADC Reference.15+3 V_DVDD+3.3 V Digital Supply.53CAP_BOTDecoupling Pin for ADC Reference.16TX_SYNCTransmit Data Input.54WREFExternal Voltage Reference.17TX_SYNCTransmit Clock Input.56ACNDAnalog Ground.19+5 V_DVDD+5 V Digital Supply.57ANDD+5 V Analog Supply.20DGNDDigital Ground.58DefNDDigital Ground.21NCNo Connect.59+5 V_DVDD+5 V Digital Supply.22IOUT_SETDAC Output Current Full Scale60NCNo Connect.23NCNo Connect.61+3 V_DVDD+3 V Digital Supply.24CAP_BDecoupling Pin for Internal Node.62TR_DAC_OUTTiming Recovery DAC Output Voltage.25CAP_CDecoupling Pin for Internal Node.63SDATASerial Data Input to Timing Recovery Output.26TX_LOUT_BTXDAC Complementary Current Output.64SFRAMEFrame Sync for Timing Recov                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |              |                                | 48  | AA_FLTR_OUTA |                                 |

| 111X_DEP_DT11 ansmit Price Dyass.50ADC_INADifferential Input to the ADC.13LOOPBACKLoopback Select.51REF_COMReference Common.14DGNDDigital Ground.52CAP_BOTDecoupling Pin for ADC Reference.15+3 V_DVDD+3.3 V Digital Supply.53CAP_BOTDecoupling Pin for ADC Reference.16TX_DATATransmit Data Input.54VREFExternal Voltage Reference.17TX_SYNCTransmit Clock Input.56ACNDDigital Ground.18TX_CLKTransmit Clock Input.56ACNDDigital Ground.19+5 V_DVDDb5 V Digital Supply.57AVDDDigital Ground.20DGNDDigital Ground.59+5 V_DVDD+5 V Digital Supply.21NCNo Connect.59+5 V_DVDD+5 V Digital Supply.22IOUT_SETDAC Output Current Full Scale59+5 V_DVDD+5 V Digital Supply.23NCNo Connect.61+3 V_DVDD+3 V Digital Supply.24CAP_BDecoupling Pin for Internal Node.62TR_DAC_OUTTiming Recovery. DAC.27TX_LOUT_BTXDAC Complementary Current<br>Output.63SDATASerial Data.28AGNDAnalog Ground.66RX2Digital Output Data.31TX_LPF_IN_BDifferential Input to LPF.67RX1Digital Output Data.34AVDD+5 V Analog Supply.67RX3Digi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |              | • •                            | 49  | ADC INB      | 0                               |

| 12Individual production11REF_COMReference Common.14DGNDDigital Ground.52CAP_TOPDecoupling Pin for ADC Reference.15 $+3V$ DVDD $+3.3$ V Digital Supply.53CAP_BOTDecoupling Pin for ADC Reference.16TX_DATATransmit Data Input.54VREFExternal Voltage Reference.17TX_SYNCTransmit Data Frame Sync Input.55CM_EVECommon-Mode Level.18TX_CLKTransmit Data Ground.56AGNDAnalog Ground.19 $+5$ V_DVDD $+5$ V Digital Supply.57AVDD $+5$ V Analog Supply.20DCNDDigital Ground.58DGNDDigital Ground.21NCNo Connect.59 $+5$ V_DVDD $+5$ V Digital Supply.22IOUT_SETDAC Output Current Full Scale60NCNo Connect.23NCNo Connect61 $+3$ V_DVDD $+3$ V Digital Supply.24CAP_BDecoupling Pin for Internal Node.62TR_DAC_OUTTiming Recovery. DAC Output25CAP_CDecoupling Pin for Internal Node.63SDATASerial Data.26TX_LOUT_ATXDAC Complementary Current<br>Output.64SFRAMEFrame Sync for Timing Recovery.27TX_LOT_BTXDAC Complementary Current<br>Output.66RX0Digital Output Data.28AGNDAnalog Ground.67RX1Digital Output Data.29TX_LPF_IN_BDifferential Input to LPF. <td></td> <td></td> <td>• -</td> <td></td> <td>_</td> <td>-</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |              | • -                            |     | _            | -                               |

| 13LOUP ACKDoublet Select.CAP_TOPDecoupling Pin for ADC Reference.14DGNDDigital Ground.52CAP_BOTDecoupling Pin for ADC Reference.15 $+3 V DVDD$ $+3.3 V Digital Supply.$ 53CAP_BOTDecoupling Pin for ADC Reference.16TX_DATATransmit Data Input.54VREFExternal Voltage Reference.17TX_SYNCTransmit Clock Input.56AGNDAnalog Ground.19 $+5 V DVDD$ $+5 V Digital Supply.$ 56ACNDAnalog Supply.20DCNDDigital Ground.58DGNDDigital Ground.21NCNo Connect.59 $+5 V DVDD$ $+5 V Digital Supply.$ 22IOUT_SETDAC Output Current Full Scale<br>(With Resistor to Ground).61 $+3 V_DVDD$ $+5 V Digital Supply.$ 23NCNo Connect.61 $+3 V_DDCD$ $+3 V Digital Supply.$ 24CAP_BDecoupling Pin for Internal Node.62TR_DAC_OUTTiming Recovery DAC Output<br>Voltage.25CAP_CDecoupling Pin for Internal Node.63SDATASerial Data Input to Timing Recovery.26TX_IOUT_ATXDAC Complementary Current<br>Output.64SFRAMEFrame Sync for Timing Recovery.28AGNDAnalog Ground.67RX1Digital Output Data.30TX_LFF_IN_BDifferential Input to LPF.<br>(If Driver Bypased).67RX1Digital Output Data.31TX_LFF_IN_BDifferential Output form Transmit<br>(If D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |              |                                |     |              | -                               |

| 11DATA<br>Decoupling Pin for ADC Reference.13 $+3.3 V$ DVDD $+3.3 V$ Digital Supply.53CAP_BOTDecoupling Pin for ADC Reference.16TX_DATATransmit Data Input.54VREFExternal Voltage Reference.17TX_SYNCTransmit Data Frame Sync Input.55CM_LVLCommon-Mode Level.18TX_CLKTransmit Clock Input.56ACNDAnalog Ground.20DGNDDigital Ground.57AVDD+5 V Digital Supply.21NCNo Connect.59+5 V_DVDD+5 V Digital Supply.22IOUT_SETDAC Output Current Full Scale60NCNo Connect.23NCNo Connect.61+3 V_DVDD+3 V Digital Supply.24CAP_CDecoupling Pin for Internal Node.62TR_DAC_OUTTriming Recovery DAC Output<br>Voltage.25CAP_CDecoupling Pin for Internal Node.64SFRAMEFrame Sync for Timing Recovery.27TX_IOUT_ATXDAC Complementary Current<br>Output.64SFRAMEFrame Sync for Timing Recovery.28AGNDAnalog Ground.66RX0Digital Output Data.30TX_LPF_IN_BDifferential Input to LPF.68RX2Digital Output Data.31TX_LPF_OUT_BDifferential Input to LPF.69RX3Digital Output Data.32TX_LPF_OUT_BDifferential Input to LPF.68RX2Digital Output Data.33TX_LPF_OUT_BDifferential Input to LPF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |              | -                              |     |              |                                 |

| 13     HOLDDD     HOLDDDD     HOLDDDD     HOLDDDD     HOLDDDD     HOLDDDDD     HOLDDDDDDDDDDDDD     HOLDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |              | 0                              |     | _            |                                 |

| 1017. DATA17. Inform Data Frame Sync Input.55CM_LVTCommon-Mode Level.18TX_CLKTransmit Clock Input.56AGND(1/2 Supply Voltage. Nominally.)19 $+5$ V DVDD $+5$ V Digital Supply.56AGNDAnalog Ground.20DGNDDigital Ground.58DGNDDigital Ground.21NCNo Connect.59 $+5$ V. DVDD $+5$ V Digital Supply.22IOUT_SETDAC Output Current Full Scale59 $+5$ V_DVDD $+5$ V Digital Supply.23NCNo Connect.60NCNo Connect.24CAP_CDecoupling Pin for Internal Node.62TR_DAC_OUTTiming Recovery DAC Output Voltage.25CAP_CDecoupling Pin for Internal Node.62TR_DAC_OUTTiming Recovery DAC.26TX_IOUT_ATXDAC Complementary Current Output.64SFRAMEFrame Sync for Timing Recovery.27TX_LOUT_BTXDAC Complementary Current Output.65SCLKClock for Timing Recovery.28AGNDAnalog Ground.66RX0Digital Output Data.29AVDD $+5$ V Analog Supply.66RX2Digital Output Data.31TX_LPF_IN_BDifferential Input to LPF.69RX3Digital Output Data.32TX_LPF_OUT_BDifferential Output from Transmit (If Driver Bypassed).71RX6Digital Output Data.33TX_LPF_OUT_ADifferential Output from Transmit (If Driver Bypassed).72DCND <td< td=""><td></td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |              |                                |     |              |                                 |

| 171A_STRC11 alisini Data Praine Sync Input.11/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/211/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |              | -                              |     |              | 0                               |

| 181A_CUA17 Algorithm Code liput.56AGNDAnalog Ground.19 $+5 V DVDD$ $+5 V Digital Supply.$ $57$ AVDD $+5 V Analog Supply.$ 20DGNDDigital Ground. $58$ DGNDDigital Ground.21NCNo Connect. $58$ DGNDNo Connect.22IOUT_SETDAC Output Current Full Scale $59$ $+5 V_DVDD$ $+5 V$ Digital Supply.23NCNo Connect. $61$ $+3 V_DVDD$ $+3 V$ Digital Supply.24CAP_BDecoupting Pin for Internal Node. $62$ $TR_DAC_OUT$ Timing Recovery DAC Output25CAP_CDecoupting Pin for Internal Node. $63$ SDATASerial Data Input to Timing Recovery Output.26TX_IOUT_ATXDAC Complementary Current<br>Output. $64$ SFRAMEFrame Sync for Timing Recovery.27TX_IOUT_BTXDAC Complementary Current<br>Output. $65$ SCLKClock for Timing Recovery.29AVDD $+5 V$ Analog Supply. $66$ RX0Digital Output Data.30TX_LPF_IN_BDifferential Input to LPF. $68$ RX2Digital Output Data.31TX_LPF_OUT_ADifferential Output from Transmit<br>(If Driver Bypassed). $70$ RX4Digital Output Data.33TX_LPF_OUT_ADifferential Driver Output. $75$ RX7Digital Output Data.34AVDD $+5 V$ Analog Supply. $74$ $+3 V DVDD$ $+3 V$ Digital Output Data.35DRVR_OUT_ADifferential Driver Outpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |              |                                | 33  |              |                                 |

| 19+5 V_DVDD+5 V Digital Supply.57AVDD+5 V Analog Supply.20DGNDDigital Ground.58DGNDDigital Ground.21NCNo Connect.59+5 V_DVDD+5 V Digital Supply.22IOUT_SETDAC Output Current Full Scale<br>(Wth Resistor to Ground).60NCNo Connect.23NCNo Connect.61+3 V_DVDD+3 V Digital Supply.24CAP_BDecoupling Pin for Internal Node.<br>Output.62TR_DAC_OUTTiming Recovery DAC Output<br>Voltage.25CAP_CDecoupling Pin for Internal Node.<br>Output.7X_IOUT_ATXDAC Complementary Current<br>Output.63SDATASerial Data Input to Timing Recovery.<br>Voltage.27TX_IOUT_BTXDAC Complementary Current<br>Output.64SFRAMEFrame Sync for Timing Recovery.<br>Clock for Timing Recovery.28AGNDAnalog Ground.66RX0Digital Output Data.31TX_LPF_IN_BDifferential Input to LPF.<br>Oifferential Input to LPF.68RX2Digital Output Data.32TX_LPF_OUT_BDifferential Output from Transmit<br>(ff Driver Bypassed).70RX4Digital Output Data.33TX_LPF_OUT_ADifferential Output from Transmit<br>(ff Driver Bypassed).71RX6Digital Output Data.34AVDD+5 V Analog Supply.73+3 V_DVDD+3 V Digital Supply.35DRVR_OUT_BDifferential Driver Output.74RX6Digital Output Data.36DRVR_OUT_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |              | •                              | 56  |              |                                 |

| 20DGNDDigital Ground.58DGNDDigital Ground.21NCNo Connect.58DGNDDigital Ground.22IOUT_SETDAC Output Current Full Scale59+5 V_DVDD+5 V Digital Supply.23NCNo Connect.61+3 V_DVDD+3 V Digital Supply.24CAP_BDecoupling Pin for Internal Node.62TR_DAC_OUTTiming Recovery DAC Output25CAP_CDecoupling Pin for Internal Node.63SDATASerial Data Input to Timing Recovery OAC.26TX_IOUT_ATXDAC Complementary Current<br>Output.64SFRAMEFrame Sync for Timing Recovery.27TX_IOUT_BTXDAC Complementary Current<br>Output.65SCLKClock for Timing Recovery.28AGNDAnalog Ground.66RX0Digital Output Data.30TX_LPF_IN_BDifferential Input to LPF.67RX1Digital Output Data.31TX_LPF_OUT_BDifferential Output from Transmit<br>(ff Driver Bypassed).70RX3Digital Output Data.33TX_LPF_OUT_ADifferential Output from Transmit<br>(ff Driver Bypassed).71RX5Digital Output Data.34AVDD+5 V Analog Supply.73+3 V_DVDD+3 V Digital Supply.35DRVR_OUT_BDifferential Driver Output.74RX6Digital Output Data.36DRVR_OUT_BDifferential Driver Output.75RX7Digital Output Data.36DRVR_OUT_BDifferential Driver Output. <td< td=""><td></td><td></td><td></td><td></td><td></td><td>•</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |              |                                |     |              | •                               |

| 21NCNo Connect.59+5 V_Digital Supply.22IOUT_SETDAC Output Current Full Scale<br>(With Resistor to Ground).60NCNo Connect.23NCNo Connect.61+3 V_DVDD+3 V Digital Supply.24CAP_BDecoupling Pin for Internal Node.<br>Decoupling Pin for Internal Node.62TR_DAC_OUTTiming Recovery DAC Output<br>Voltage.26TX_IOUT_ATXDAC Complementary Current<br>Output.63SDATASerial Data Input to Timing Recovery<br>ery DAC.27TX_IOUT_BTXDAC Complementary Current<br>Output.64SFRAMEFrame Sync for Timing Recovery.<br>Clock for Timing Recovery DAC.28AGNDAnalog Ground.66RX0Digital Output Data.30TX_LPF_IN_BDifferential Input to LPF.<br>(If Driver Bypased).67RX1Digital Output Data.31TX_LPF_OUT_BDifferential Input to LPF.<br>(If Driver Bypased).69RX3Digital Output Data.33TX_LPF_OUT_ADifferential Output from Transmit<br>(If Driver Bypased).70RX5Digital Output Data.34AVDD+5 V Analog Supply.73+3 V_DVDD+3 V Digital Supply.35DRVR_OUT_BDifferential Output from Transmit<br>(If Driver Bypased).71RX6Digital Output Data.34AVDD+5 V Analog Supply.73+3 V_DVDD+3 V Digital Supply.35DRVR_OUT_BDifferential Driver Output.74RX6Digital Output Data.36DRVR_OUT_BDifferen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |              | 0                              |     |              | • • • •                         |

| 22IDUT_SETDAC Output Current FPH Scale<br>(With Resistor to Group).60NCNo Connect.23NCNo Connect.61+3 V_DVDD+3 V Digital Supply.24CAP_BDecoupling Pin for Internal Node.62TR_DAC_OUTTiming Recovery DAC Output25CAP_CDecoupling Pin for Internal Node.63SDATASerial Data Input to Timing Recovery26TX_IOUT_ATXDAC Complementary Current<br>Output.64SFRAMEFrame Sync for Timing Recovery.27TX_IOUT_BTXDAC Complementary Current<br>Output.66RX0Digital Output Data.29AVDD+5 V Analog Supply.66RX1Digital Output Data.30TX_LPF_IN_BDifferential Input to LPF.68RX2Digital Output Data.31TX_LPF_OUT_BDifferential Output from Transmit<br>(If Driver Bypassed).70RX4Digital Output Data.33TX_LPF_OUT_ADifferential Driver Output.73+3 V_DVD+3 V Digital Supply.34AVDD+5 V Analog Supply.73+3 V_DVD+3 V Digital Supply.35DRVR_OUT_BDifferential Ortput from Transmit<br>(If Driver Bypassed).72DGNDDigital Ground.36DRVR_OUT_ADifferential Driver Output.75RX7Digital Output Data.36DRVR_OUT_ADifferential Driver Output.76RX8Digital Output Data.37AGNDAnalog Ground.76RX8Digital Output Data.38HYB_IN2_B <td< td=""><td></td><td></td><td></td><td></td><td>-</td><td>5</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |              |                                |     | -            | 5                               |

| 23NCNo Connect.61+3 V_DVD+3 V Digital Supply.24CAP_BDecoupling Pin for Internal Node.62TR_DAC_OUTTiming Recovery DAC Output25CAP_CDecoupling Pin for Internal Node.63SDATASerial Data Input to Timing Recovery DAC.26TX_IOUT_ATXDAC Complementary Current<br>Output.64SFRAMEFrame Sync for Timing Recovery DAC.27TX_IOUT_BTXDAC Complementary Current<br>Output.65SCLKClock for Timing Recovery DAC.<br>Serial Data.28AGNDAnalog Ground.66RX0Digital Output Data.29AVDD+5 V Analog Supply.66RX1Digital Output Data.30TX_LPF_IN_BDifferential Input to LPF.68RX2Digital Output Data.31TX_LPF_OUT_BDifferential Output from Transmit<br>(If Driver Bypassed).70RX4Digital Output Data.33TX_LPF_OUT_ADifferential Dutput from Transmit<br>(If Driver Bypassed).72DGNDDigital Ground.34AVDD+5 V Analog Supply.73+3 V_DVDD+3 V Digital Supply.35DRVR_OUT_BDifferential Driver Output.74RX6Digital Output Data.36DRVR_OUT_BDifferential Driver Output.75RX7Digital Output Data.36DRVR_OUT_ADifferential Driver Output.76RX8Digital Output Data.37AGNDAnalog Ground.76RX8Digital Output Data.38HYB_IN2_BHybri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22  | IOUT_SET     |                                |     |              | 0 110                           |

| 24CAP_BDecoupling Pin for Internal Node.<br>Decoupling Pin for Internal Node.<br>TX_IOUT_A62TR_DAC_OUTTiming Recovery DAC Output<br>Voltage.26TX_IOUT_ADecoupling Pin for Internal Node.<br>Output.63SDATASerial Data Input to Timing Recovery<br>ery DAC.27TX_IOUT_BTXDAC Complementary Current<br>Output.64SFRAMEFrame Sync for Timing Recovery.<br>SCLK28AGNDAnalog Ground.66RX0Digital Output Data.29AVDD+5 V Analog Supply.67RX1Digital Output Data.30TX_LPF_IN_BDifferential Input to LPF.68RX2Digital Output Data.31TX_LPF_OUT_BDifferential Output from Transmit<br>(If Driver Bypassed).70RX4Digital Output Data.33TX_LPF_OUT_BDifferential Output from Transmit<br>(If Driver Bypassed).71RX5Digital Ground.34AVDD+5 V Analog Supply.73+3 V_DVD+3 V Digital Supply.35DRVR_OUT_BDifferential Output from Transmit<br>(If Driver Bypassed).72DGNDDigital Ground.34AVDD+5 V Analog Supply.73+3 V_DVDD+3 V Digital Supply.35DRVR_OUT_BDifferential Driver Output.74RX6Digital Output Data.36DRVR_OUT_BDifferential Driver Output.75RX7Digital Output Data.37AGNDAnalog Ground.76RX8Digital Output Data.38HYB_IN2_BHybrid Noninverting Input.77 <td>23</td> <td>NC</td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23  | NC           |                                |     |              |                                 |

| 25CAP_C<br>CAP_CDecoupling Pin for Internal Node.Voltage.26TX_IOUT_ATXDAC Complementary Current<br>Output.63SDATASerial Data Input to Timing Recov-<br>ery DAC.27TX_IOUT_BTXDAC Complementary Current<br>Output.64SFRAMEFrame Sync for Timing Recovery.28AGNDAnalog Ground.65SCLKClock for Timing Recovery DAC.29AVDD+5 V Analog Supply.66RX0Digital Output Data.30TX_LPF_IN_BDifferential Input to LPF.68RX2Digital Output Data.31TX_LPF_IN_BDifferential Output from Transmit<br>(If Driver Bypassed).69RX3Digital Output Data.33TX_LPF_OUT_ADifferential Output from Transmit<br>(If Driver Bypassed).70RX4Digital Output Data.34AVDD+5 V Analog Supply.73+3 V_DVDD+3 V Digital Supply.35DRVR_OUT_BDifferential Oriver Output.74RX6Digital Output Data.36DRVR_OUT_BDifferential Driver Output.75RX7Digital Output Data.37AGNDAnalog Ground.66RX8Digital Output Data.38HYB_IN2_BHybrid Noninverting Input.77RX9Digital Output Data.39HYB_IN1_BHybrid Inverting Input.79RX11Digital Output Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |              |                                | 62  | TR_DAC_OUT   |                                 |

| 26TX_IOUT_ATXDAC Complementary Current<br>Output.63SDATASerial Data Input to Timing Recov-<br>ery DAC.27TX_IOUT_BTXDAC Complementary Current<br>Output.64SFRAMEFrame Sync for Timing Recovery.28AGNDAnalog Ground.65SCLKClock for Timing Recovery DAC.<br>Serial Data.29AVDD+5 V Analog Supply.66RX0Digital Output Data.30TX_LPF_IN_BDifferential Input to LPF.68RX2Digital Output Data.31TX_LPF_IN_ADifferential Input to LPF.69RX3Digital Output Data.32TX_LPF_OUT_BDifferential Output from Transmit<br>(If Driver Bypassed).70RX4Digital Output Data.33TX_LPF_OUT_ADifferential Output from Transmit<br>(If Driver Bypassed).72DGNDDigital Ground.34AVDD+5 V Analog Supply.73+3 V_DVDD+3 V Digital Supply.35DRVR_OUT_BDifferential Driver Output.74RX6Digital Output Data.36DRVR_OUT_ADifferential Driver Output.75RX7Digital Output Data.37AGNDAnalog Ground.76RX8Digital Output Data.38HYB_IN2_BHybrid Noninverting Input.77RX9Digital Output Data.39HYB_IN1_BHybrid Inverting Input.79RX11Digital Output Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |              |                                |     |              | Voltage.                        |

| 27TX_IOUT_BTXDAC Complementary Current<br>Output.64SFRAMEFrame Sync for Timing Recovery.28AGNDAnalog Ground.65SCLKClock for Timing Recovery DAC.<br>Serial Data.29AVDD+5 V Analog Supply.66RX0Digital Output Data.30TX_LPF_IN_BDifferential Input to LPF.67RX1Digital Output Data.31TX_LPF_IN_ADifferential Input to LPF.68RX2Digital Output Data.32TX_LPF_OUT_BDifferential Output from Transmit<br>(If Driver Bypassed).70RX4Digital Output Data.33TX_LPF_OUT_ADifferential Output from Transmit<br>(If Driver Bypassed).71RX5Digital Output Data.34AVDD+5 V Analog Supply.73+3 V_DVDD+3 V Digital Supply.35DRVR_OUT_BDifferential Driver Output.74RX6Digital Output Data.36DRVR_OUT_ADifferential Driver Output.75RX7Digital Output Data.37AGNDAnalog Ground.76RX8Digital Output Data.38HYB_IN2_BHybrid Noninverting Input.77RX9Digital Output Data.39HYB_IN2_AHybrid Noninverting Input.79RX11Digital Output Data.40HYB_IN1_BHybrid Inverting Input.79RX11Digital Output Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |              | TXDAC Complementary Current    | 63  | SDATA        |                                 |

| 28AGNDAnalog Ground.65SCLKClock for Timing Recovery DAC.<br>Serial Data.29AVDD+5 V Analog Ground.66RX0Digital Output Data.30TX_LPF_IN_BDifferential Input to LPF.67RX1Digital Output Data.31TX_LPF_IN_ADifferential Input to LPF.68RX2Digital Output Data.32TX_LPF_OUT_BDifferential Output from Transmit<br>(If Driver Bypassed).69RX3Digital Output Data.33TX_LPF_OUT_ADifferential Output from Transmit<br>(If Driver Bypassed).70RX4Digital Output Data.34AVDD+5 V Analog Supply.73+3 V_DVDD+3 V Digital Supply.35DRVR_OUT_BDifferential Driver Output.74RX6Digital Output Data.36DRVR_OUT_ADifferential Driver Output.75RX7Digital Output Data.37AGNDAnalog Ground.76RX8Digital Output Data.38HYB_IN2_BHybrid Noninverting Input.77RX9Digital Output Data.39HYB_IN2_AHybrid Noninverting Input.79RX11Digital Output Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 97  | TV IOUT D    | -                              | 64  | SFRAME       | Frame Sync for Timing Recovery. |

| 28AGNDAnalog Ground.66RX0Digital Output Data.29AVDD+5 V Analog Supply.67RX1Digital Output Data.30TX_LPF_IN_BDifferential Input to LPF.68RX2Digital Output Data.31TX_LPF_OUT_BDifferential Output from Transmit<br>(If Driver Bypassed).69RX3Digital Output Data.32TX_LPF_OUT_ADifferential Output from Transmit<br>(If Driver Bypassed).70RX4Digital Output Data.33TX_LPF_OUT_ADifferential Output from Transmit<br>(If Driver Bypassed).71RX5Digital Output Data.34AVDD+5 V Analog Supply.73+3 V_DVDD+3 V Digital Supply.35DRVR_OUT_BDifferential Driver Output.74RX6Digital Output Data.36DRVR_OUT_ADifferential Driver Output.75RX7Digital Output Data.37AGNDAnalog Ground.76RX8Digital Output Data.38HYB_IN2_BHybrid Noninverting Input.77RX9Digital Output Data.39HYB_IN1_BHybrid Inverting Input.79RX11Digital Output Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |              | Output.                        | 65  | SCLK         |                                 |

| 29AVDD+5 V Analog Supply.67RX1Digital Output Data.30TX_LPF_IN_BDifferential Input to LPF.68RX2Digital Output Data.31TX_LPF_IN_ADifferential Output from Transmit<br>(If Driver Bypassed).69RX3Digital Output Data.32TX_LPF_OUT_BDifferential Output from Transmit<br>(If Driver Bypassed).70RX4Digital Output Data.33TX_LPF_OUT_ADifferential Output from Transmit<br>(If Driver Bypassed).71RX5Digital Output Data.34AVDD+5 V Analog Supply.73+3 V_DVDD+3 V Digital Supply.35DRVR_OUT_BDifferential Driver Output.74RX6Digital Output Data.36DRVR_OUT_ADifferential Driver Output.75RX7Digital Output Data.37AGNDAnalog Ground.76RX8Digital Output Data.38HYB_IN2_BHybrid Noninverting Input.77RX9Digital Output Data.39HYB_IN1_BHybrid Inverting Input.79RX10Digital Output Data.40HYB_IN1_BHybrid Inverting Input.79RX11Digital Output Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |              |                                | 66  | RX0          |                                 |