# **ADVANCE INFORMATION**

October 1995

# 74LVT16652 3.3V ABT 16-Bit Transceiver/Register with TRI-STATE® Outputs

## **General Description**

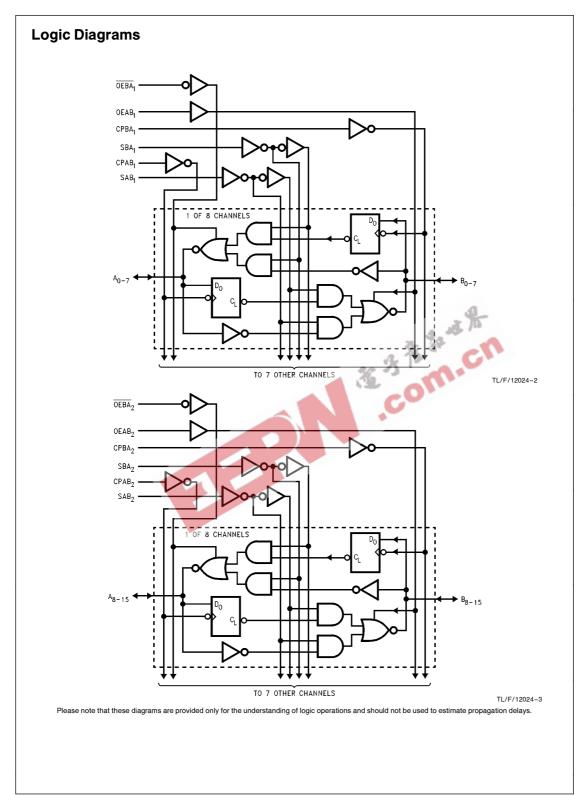

The LVT16652 consists of sixteen bus transceiver circuits with D-type flip-flops, and control circuitry arranged for multiplexed transmission of data directly from the input bus or from the internal registers. Each byte has separate control inputs which can be shorted together for full 16-bit operation. Data on the A or B bus will be clocked into the registers as the appropriate clock pin goes to HIGH logic level. Output Enable pins (OEAB, OEBA) are provided to control the transceiver function.

The transceivers are designed for low-voltage (3.3V)  $V_{\rm CC}$  applications, but with the capability to provide a TTL interface to a 5V environment. The LVT16652 is fabricated with an advanced BiCMOS technology to achieve high speed operation similar to 5V ABT while maintaining a low power dissipation.

#### **Features**

- $\blacksquare$  Input and output interface capability to systems at 5V  $V_{CC}$

- Bus-Hold data inputs eliminate the need for external pull-up resistors to hold unused inputs

- Live insertion/extraction permitted

- Power Up/Down high impedance provides glitch-free bus loading

- Outputs source/sink -32 mA/+64 mA

- Available in SSOP and TSSOP

- Functionally compatible with the 74 series 16652

- Latch-up performance exceeds 500 mA

# Connection Diagram

Pin Assignment for SSOP and TSSOP

| Pin Names                             | Description             |

|---------------------------------------|-------------------------|

| A <sub>0</sub> -A <sub>16</sub>       | Data Register A Inputs/ |

|                                       | TRI-STATE Outputs       |

| B <sub>0</sub> -B <sub>16</sub>       | Data Register B Inputs/ |

|                                       | TRI-STATE Outputs       |

| CPAB <sub>n</sub> , CPBA <sub>n</sub> | Clock Pulse Inputs      |

| SAB <sub>n</sub> , SBA <sub>n</sub>   | Select Inputs           |

| OEAB <sub>n</sub> , OEBA <sub>n</sub> | Output Enable Inputs    |

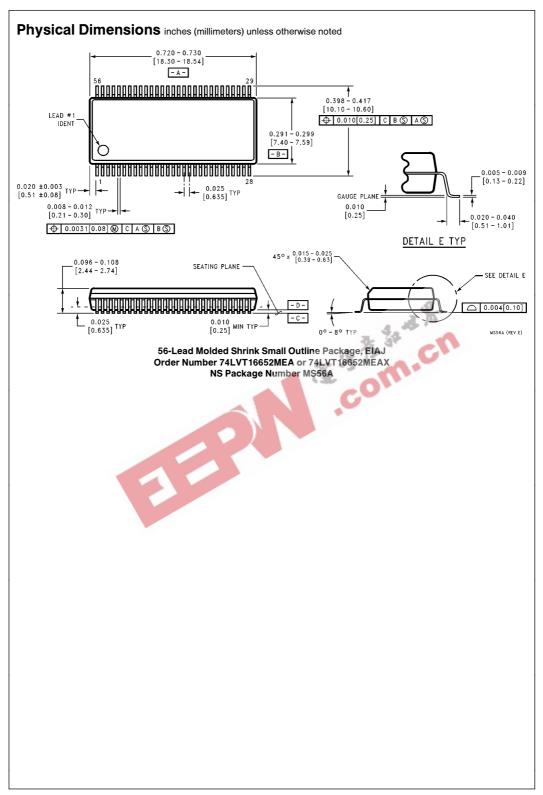

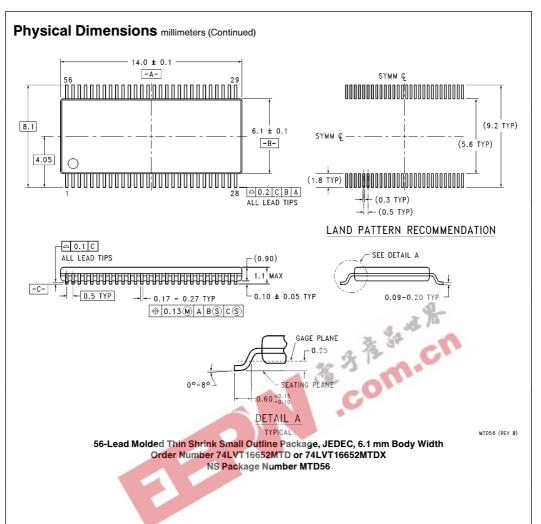

|                      | SSOP EIAJ                       | TSSOP JEDEC                     |

|----------------------|---------------------------------|---------------------------------|

| Order Number         | 74LVT16652MEA<br>74LVT16652MEAX | 74LVT16652MTD<br>74LVT16652MTDX |

| NS Package<br>Number | MS56A                           | MTD56                           |

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

# **Functional Description**

In the transceiver mode, data present at the HIGH impedance port may be stored in either the A or B register or both.

The select  $(SAB_n, SBA_n)$  controls can multiplex stored and real-time

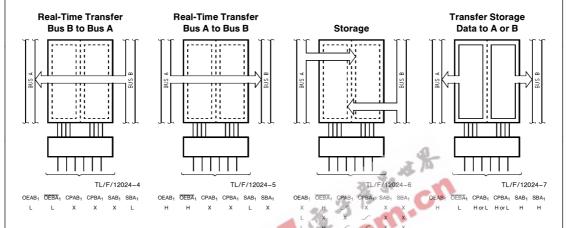

The examples in *Figure 1* demonstrate the four fundamental bus-management functions that can be performed with the LVT16652

Data on the A or B data bus, or both can be stored in the internal D flip-flop by LOW to HIGH transitions at the appro-

priate Clock Inputs (CPAB<sub>n</sub>, CPBA<sub>n</sub>) regardless of the Select or Output Enable Inputs. When SAB and SBA are in the real time transfer mode, it is also possible to store data without using the internal D flip-flops by simultaneously enabling OEAB<sub>n</sub> and  $\overline{\text{OEBA}}_n$ . In this configuration each Output reinforces its Input. Thus when all other data sources to the two sets of bus lines are in a HIGH impedance state, each set of bus lines will remain at its last state.

### FIGURE

# Truth Table (Note)

| Inputs            |                   |                   |                   |                  |                  | Inputs/Outputs                     |                                    | Operating Mode                                       |

|-------------------|-------------------|-------------------|-------------------|------------------|------------------|------------------------------------|------------------------------------|------------------------------------------------------|

| OEAB <sub>1</sub> | OEBA <sub>1</sub> | CPAB <sub>1</sub> | CPBA <sub>1</sub> | SAB <sub>1</sub> | SBA <sub>1</sub> | A <sub>0</sub> thru A <sub>7</sub> | B <sub>0</sub> thru B <sub>7</sub> |                                                      |

| L                 | Н                 | HorL              | H or L            | X                | Х                | Input                              | Input                              | Isolation                                            |

| L                 | Н                 |                   | 5                 | Х                | Х                | input                              |                                    | Store A and B Data                                   |

| X                 | Н                 |                   | H or L            | Х                | Х                | Input                              | Not Specified                      | Store A, Hold B                                      |

| Н                 | Н                 |                   |                   | Х                | Х                | Input                              | Output                             | Store A in Both Registers                            |

| L                 | Х                 | H or L            | \                 | X                | Х                | Not Specified                      | Input                              | Hold A, Store B                                      |

| L                 | L                 |                   | \                 | Х                | Х                | Output                             | Input                              | Store B in Both Registers                            |

| L                 | L                 | Х                 | X                 | Х                | L                | Output                             | Input                              | Real-Time B Data to A Bus                            |

| L                 | L                 | Х                 | H or L            | Х                | Н                | Cutput                             |                                    | Store B Data to A Bus                                |

| Н                 | Н                 | Х                 | X                 | L                | Х                | Input                              | Output                             | Real-Time A Data to B Bus                            |

| Н                 | Н                 | H or L            | Х                 | Н                | Х                | mpat                               |                                    | Stored A Data to B Bus                               |

| Н                 | L                 | H or L            | H or L            | Н                | Н                | Output                             | Output                             | Stored A Data to B Bus and<br>Stored B Data to A Bus |

$H = HIGH \ Voltage \ Level \qquad L = LOW \ Voltage \ Level \qquad X = Immaterial \qquad \checkmark = LOW \ to \ HIGH \ Clock \ Transition$

Note: The data output functions may be enabled or disabled by various signals at OEAB or OEBA inputs. Data input functions are always enabled, i.e., data at the bus pins will be stored on every LOW to HIGH transition on the clock inputs. This also applies to data I/O (A and B: 8–15) and #2 control pins.

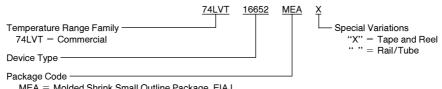

The device number is used to form part of a simplified purchasing code where the package type and temperature range are defined as follows:

MEA = Molded Shrink Small Outline Package, EIAJ

MTD = Molded Thin Shrink Small Outline Package, JEDEC, 4.4 mm

Body Width

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| N       | National Semiconductor<br>Corporation                                              | National Semiconductor Europe                                                                                                                                                  | National Semiconductor<br>Southeast Asia           | National Semiconductor Japan Ltd.          |

|---------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------|

| C       | Americas<br>Tel: 1(800) 272-9959<br>Fax: 1(800) 737-7018<br>Email: support@nsc.com | Fax: +49 (0) 180-530 85 86<br>Email: europe.support@nsc.com<br>Deutsch Tel: +49 (0) 180-530 85 85<br>English Tel: +49 (0) 180-532 78 32<br>Français Tel: +49 (0) 180-532 93 58 | Fax: (852) 2376 3901<br>Email: sea.support@nsc.com | Tel: 81-3-5620-7561<br>Fax: 81-3-5620-6179 |

| http:// | www.national.com                                                                   | Italiano Tel: +49 (0) 180-534 16 80                                                                                                                                            |                                                    |                                            |