- Choice of Memory Organizations

- SN74V263 8192  $\times$  18/16384  $\times$  9

- SN74V273 16384  $\times$  18/32768  $\times$  9

- SN74V283 32768  $\times$  18/65536  $\times$  9

- SN74V293 65536  $\times$  18/131072  $\times$  9

- 166-MHz Operation

- 6-ns Read/Write Cycle Time

- User-Selectable Input and Output Port Bus Sizing

- $\times 9$  in to  $\times 9$  out

- ×9 in to ×18 out

- $\times$ 18 in to  $\times$ 9 out

- ×18 in to ×18 out

- Big-Endian/Little-Endian User-Selectable Byte Representation

- 5-V-Tolerant Inputs

- Fixed, Low First-Word Latency

- Zero-Latency Retransmit

- Master Reset Clears Entire FIFO

- Partial Reset Clears Data, but Retains Programmable Settings

- Empty, Full, and Half-Full Flags Signal FIFO Status

- Programmable Almost-Empty and Almost-Full Flags; Each Flag Can Default to One of Eight Preselected Offsets

- Selectable Synchronous/Asynchronous Timing Modes for Almost-Empty and Almost-Full Flags

- Program Programmable Flags by Either Serial or Parallel Means

- Select Standard Timing (Using EF and FF Flags) or First-Word Fall-Through (FWFT) Timing (Using OR and IR Flags)

- Output Enable Puts Data Outputs in High-Impedance State

- Easily Expandable in Depth and Width

- Independent Read and Write Clocks Permit Reading and Writing Simultaneously

- High-Performance Submicron CMOS

Technology

- Glueless Interface With 'C6x DSPs

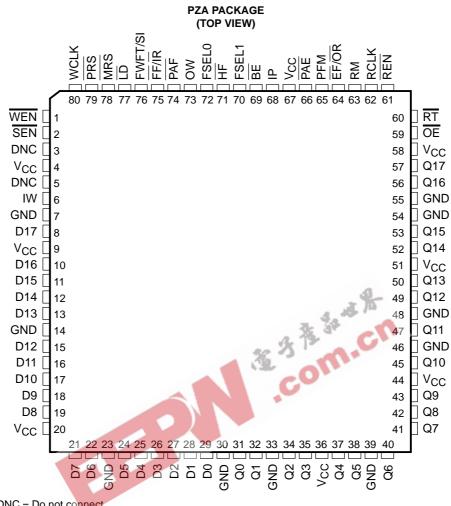

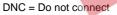

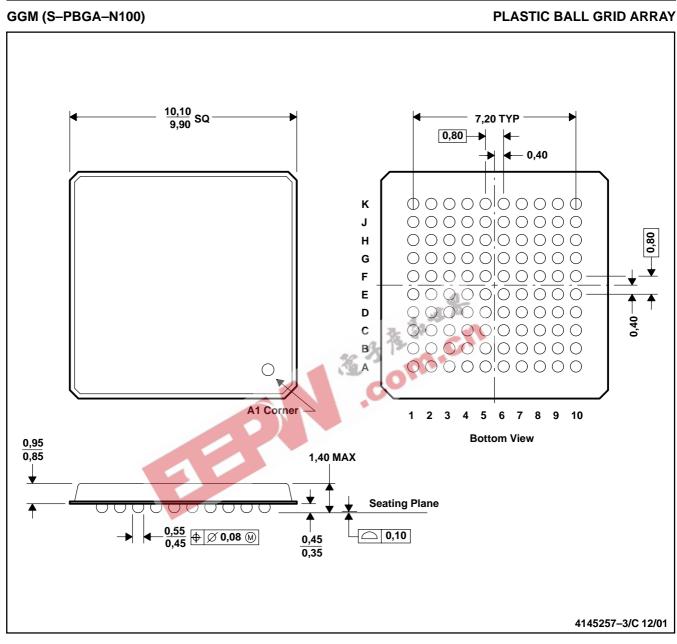

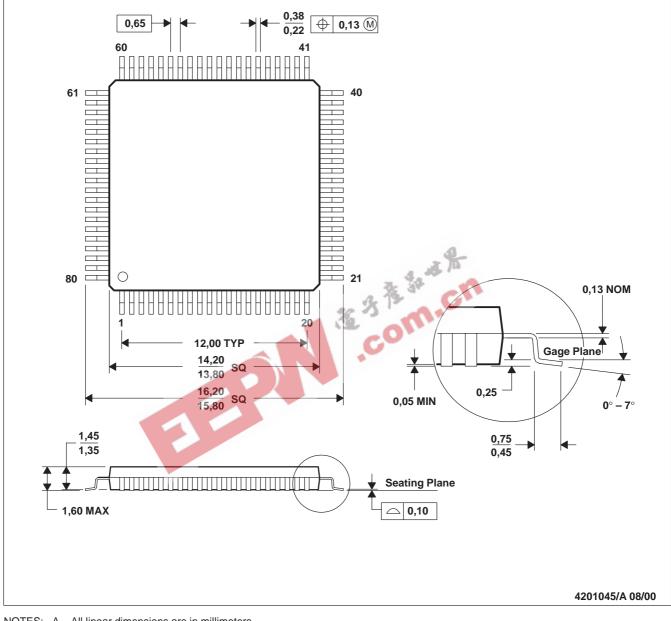

- Available in 80-Pin Thin Quad Flat Pack (TQFP) and 100-Pin Ball Grid Array (BGA)

Packages

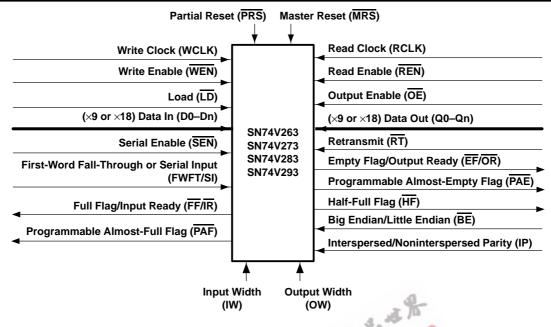

#### description

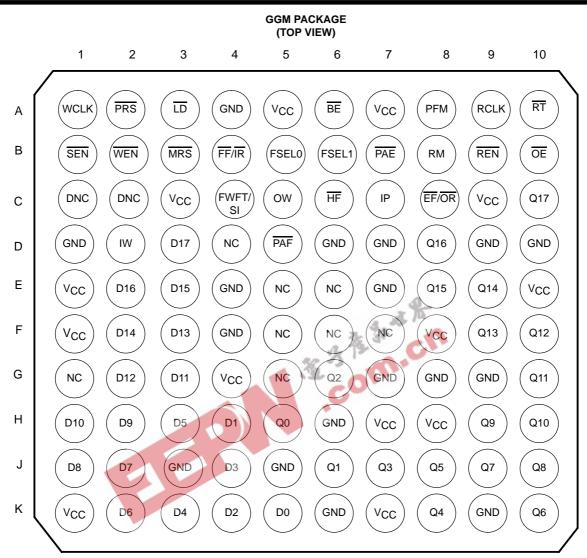

The SN74V263, SN74V273, SN74V283, and SN74V293 are exceptionally deep, high-speed, CMOS first-in first-out (FIFO) memories with clocked read and write controls and a flexible bus-matching ×9/×18 data flow.

There is flexible  $\times 9/\times 18$  bus matching on both read and write ports.

The period required by the retransmit operation is fixed and short.

The first-word data-latency period, from the time the first word is written to an empty FIFO to the time it can be read, is fixed and short.

These FIFOs are particularly appropriate for network, video, telecommunications, data communications, and other applications that need to buffer large amounts of data and match buses of unequal sizes.

Each FIFO has a data input port (Dn) and a data output port (Qn), both of which can assume either an 18-bit or 9-bit width, as determined by the state of external control pins' input width (IW) and output width (OW) during the master-reset cycle.

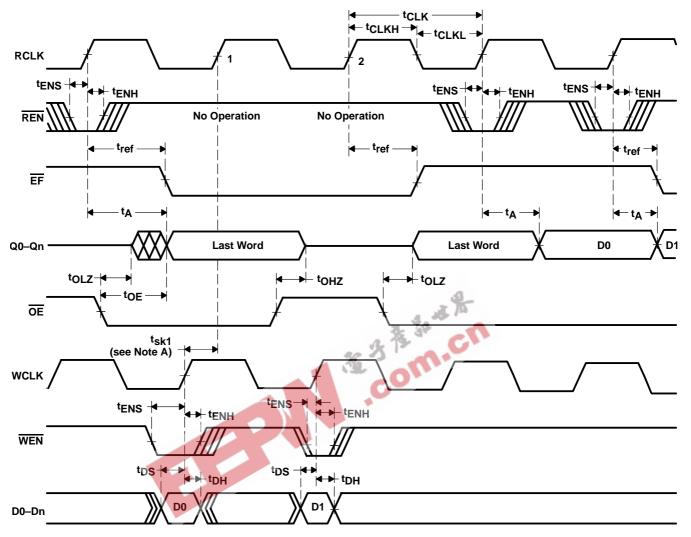

The input port is controlled by write-clock (WCLK) and write-enable (WEN) inputs. Data is written into the FIFO on every rising edge of WCLK when WEN is asserted. The output port is controlled by read-clock (RCLK) and read-enable (REN) inputs. Data is read from the FIFO on every rising edge of RCLK when REN is asserted. An output-enable (OE) input is provided for 3-state control of the outputs.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2003, Texas Instruments Incorporated

# SN74V263, SN74V273, SN74V283, SN74V293 8192 $\times$ 18, 16384 $\times$ 18, 32768 $\times$ 18, 65536 $\times$ 18 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES

SCAS669D - JUNE 2001 - REVISED FEBRUARY 2003

DNC = Do not connect

#### description (continued)

The frequencies of both the RCLK and the WCLK signals can vary from 0 to  $f_{MAX}$ , with complete independence. There are no restrictions on the frequency of one clock input with respect to the other.

There are two possible timing modes of operation with these devices: first-word fall-through (FWFT) mode and standard mode.

In FWFT mode, the first word written to an empty FIFO is clocked directly to the data output lines after three transitions of the RCLK signal. REN need not be asserted for accessing the first word. However, subsequent words written to the FIFO do require a low on REN for access. The state of the FWFT/SI input during master reset determines the timing mode in use.

In standard mode, the first word written to an empty FIFO does not appear on the data output lines unless a specific read operation is performed. A read operation, which consists of activating  $\overline{\text{REN}}$  and enabling a rising RCLK edge, shifts the word from internal memory to the data output lines.

# $\begin{array}{l} \text{SN74V263, SN74V273, SN74V283, SN74V293} \\ \text{8192} \times 18, 16384 \times 18, 32768 \times 18, 65536 \times 18 \\ \text{3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES} \\ \text{SCAS669D - JUNE 2001 - REVISED FEBRUARY 2003} \end{array}$

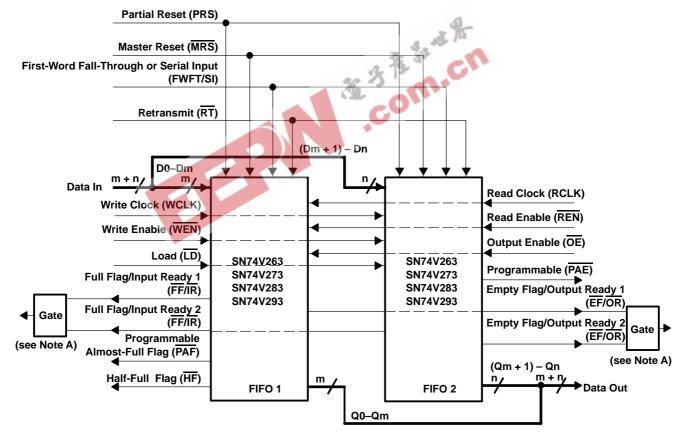

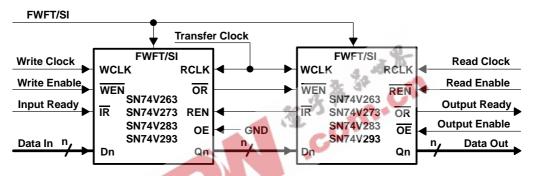

#### functional block diagram

#### description (continued)

For applications requiring more data-storage capacity than a single FIFO can provide, the FWFT timing mode permits depth expansion by chaining FIFOs in series (i.e., the data outputs of one FIFO are connected to the corresponding data inputs of the next). No external logic is required.

These FIFOs have five flag pins: empty flag or output ready ( $\overline{EF}/\overline{OR}$ ), full flag or input ready ( $\overline{FF}/\overline{IR}$ ), half-full flag ( $\overline{HF}$ ), programmable almost-empty flag ( $\overline{PAE}$ ), and programmable almost-full flag ( $\overline{PAF}$ ). The  $\overline{IR}$  and  $\overline{OR}$  functions are selected in FWFT mode. The  $\overline{EF}$  and  $\overline{FF}$  functions are selected in standard mode.  $\overline{HF}$ ,  $\overline{PAE}$ , and  $\overline{PAF}$  always are available for use, regardless of timing mode.

$\overrightarrow{PAE}$  and  $\overrightarrow{PAF}$  can be programmed independently to switch at any point in memory. Programmable offsets determine the flag-switching threshold and can be loaded by parallel or serial methods. Eight default offset settings also are provided, so that  $\overrightarrow{PAE}$  can be set to switch at a predefined number of locations from the empty boundary. The  $\overrightarrow{PAF}$  threshold also can be set at similar predefined values from the full boundary. The default offset values are set during master reset by the state of FSEL0, FSEL1, and  $\overrightarrow{LD}$ .

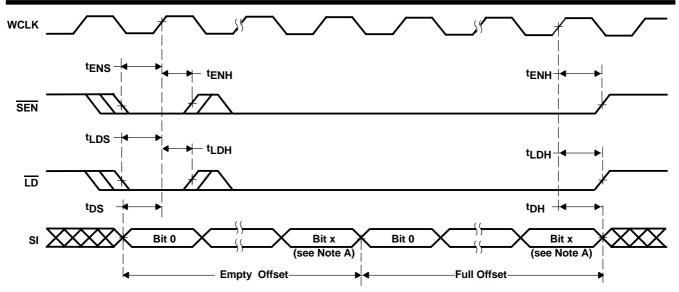

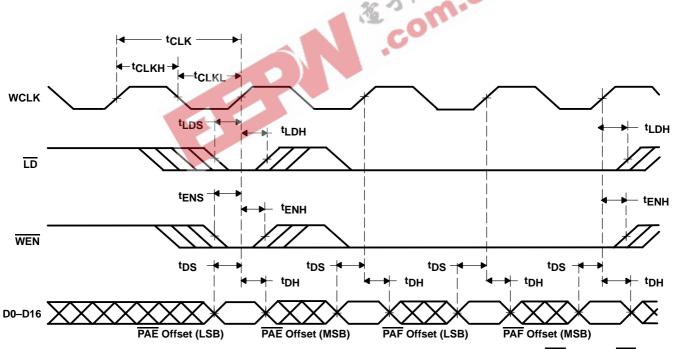

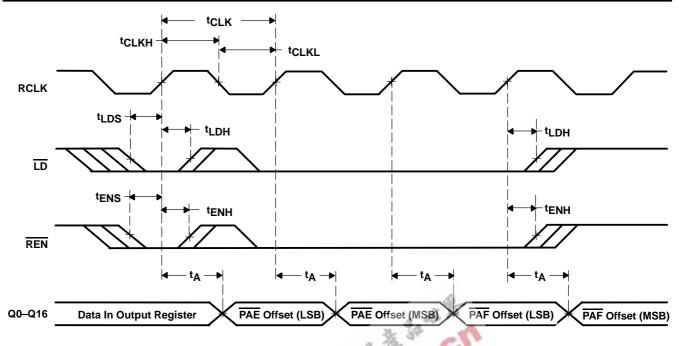

For serial programming,  $\overline{SEN}$ , together with  $\overline{LD}$ , loads the offset registers via the serial input (SI) on each rising edge of WCLK. For parallel programming,  $\overline{WEN}$ , together with  $\overline{LD}$ , loads the offset registers via Dn on each rising edge of WCLK. REN, together with  $\overline{LD}$ , can read the offsets in parallel from Qn on each rising edge of RCLK, regardless of whether serial or parallel offset loading has been selected.

#### description (continued)

Also, the timing modes of PAE and PAF outputs can be selected. Timing modes can be set to be either asynchronous or synchronous for PAE and PAF.

If the asynchronous PAE/PAF configuration is selected, PAE is asserted low on the low-to-high transition of RCLK. PAE is reset to high on the low-to-high transition of WCLK. Similarly, PAF is asserted low on the low-to-high transition of WCLK, and PAF is reset to high on the low-to-high transition of RCLK.

If the synchronous PAE/PAF configuration is selected, PAE is asserted and updated on the rising edge of RCLK only and not WCLK. Similarly, PAF is asserted and updated on the rising edge of WCLK only and not RCLK. The desired mode is configured during master reset by the state of the programmable-flag mode (PFM) pin.

The retransmit function allows data to be reread from the FIFO more than once. A low on the  $\overline{RT}$  input during a rising RCLK edge initiates a retransmit operation by setting the read pointer to the first location of the memory array. Zero-latency retransmit timing mode can be selected using the retransmit timing mode (RM). During master reset, a low on RM selects zero-latency retransmit. A high on RM during master reset selects normal latency.

If zero-latency retransmit operation is selected, the first data word to be retransmitted is placed on the output register with respect to the same RCLK edge that initiated the retransmit, if  $\overline{RT}$  is low.

During master reset (MRS), the functions for all the operating modes are programmed. These include FWFT or standard timing, input bus width, output bus width, big endian or little endian, retransmit mode, programmable-flag operating and programming method, programmable-flag default offsets, and interspersed parity select. The read and write pointers are set to the first location of the FIFO. Then, based on the selected timing mode, EF is set low or OR is set high and FF is set high or IR is set low. Also, PAE is set low, PAF is set high, and HF is set high. The Q outputs are set low.

Partial reset (PRS) also sets the read and write pointers to the first location of the memory. However, the timing mode, programmable-flag programming method, default or programmed offset settings, input and output bus widths, big endian/little endian, interspersed parity select, and retransmit mode existing before partial reset is asserted remain unchanged. The flags are updated according to the timing mode and offsets in effect. PRS is useful for resetting a device in mid-operation when reprogramming programmable flags and other functions would be undesirable.

Figure 1. Single-Device-Configuration Signal Flow

#### description (continued)

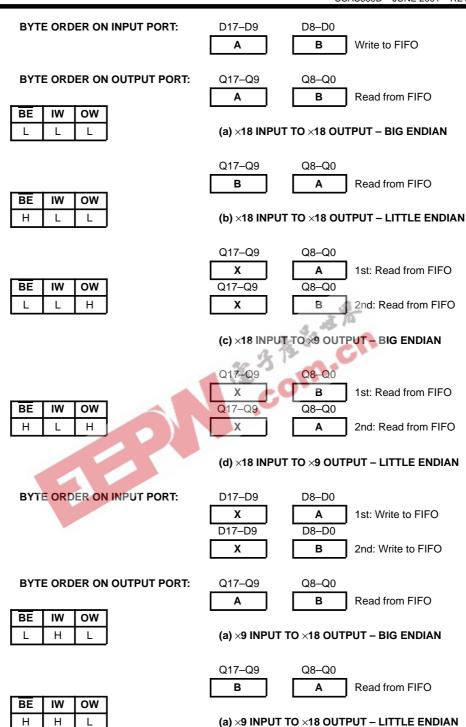

A big-endian/little-endian data word format is provided. This function is useful when data is written into the FIFO in long-word ( $\times$ 18) format and read out of the FIFO in small-word ( $\times$ 9) format. If big-endian mode is selected, the most significant byte (MSB) (word) of the long word written into the FIFO is read out of the FIFO first, followed by the least significant byte (LSB). If little-endian format is selected, the LSB of the long word written into the FIFO is read out first, followed by the MSB. The mode desired is configured during master reset by the state of the big-endian/little-endian ( $\overline{BE}$ ) pin.

The interspersed/noninterspersed parity (IP) bit function allows the user to select the parity bit in the word loaded into the parallel port (D0–Dn) when programming the flag offsets. If interspersed-parity mode is selected, the FIFO assumes that the parity bit is located in bit position D8 during the parallel programming of the flag offsets. If noninterspersed-parity mode is selected, D8 is assumed to be a valid bit and D16 and D17 are ignored. IP mode is selected during master reset by the state of the IP input pin. This mode is relevant only when the input width is set to  $\times$ 18 mode.

The SN74V263, SN74V273, SN74V283, and SN74V293 are fabricated using TI's high-speed submicron CMOS technology.

For more information on this device family, see the following application reports:

- Interfacing TI High-Speed External FIFOs With TI DSP Via DSPs' External Memory Interface (EMIF) (literature number SPRA534)

- Interfacing TI High-Speed External FIFOs With TI DSP Via DSPs' Expansion Bus (XBus) (literature number SPRA547)

#### Table 1. Bus-Matching Configuration Modes

| IW | ow | WRITE PORT WIDTH | READ PORT WIDTH |

|----|----|------------------|-----------------|

| L  | L  | ×18              | ×18             |

| L  | Н  | ×18              | ×9              |

| Н  | L  | ×9               | ×18             |

| Н  | Н  | ×9               | ×9              |

#### **Terminal Functions**

| TERMINAL<br>NAME | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BE               | I   | Big endian/little endian. During master reset, a low on $\overline{\text{BE}}$ selects big-endian operation. A high on $\overline{\text{BE}}$ during master reset selects little-endian format.                                                                                                                                                                                                                                                                                                |

| D0-D17           | I   | Data inputs. Data inputs for an 18- or 9-bit bus. When in 18-bit mode, D0–D17 are used. When in 9-bit mode, D0–D8 are used and the unused inputs (D9–D17) should be tied low.                                                                                                                                                                                                                                                                                                                  |

| EF/OR            | ο   | Empty flag/output ready. In FWFT mode, the OR function is selected. OR indicates whether there is valid data available at the outputs. In the standard mode, the EF function is selected. EF indicates whether the FIFO memory is empty.                                                                                                                                                                                                                                                       |

| FF/IR            | о   | Full flag/input ready. In FWFT mode, the IR function is selected. IR indicates whether there is space available for writing to the FIFO memory. In standard mode, the FF function is selected. FF indicates whether the FIFO memory is full.                                                                                                                                                                                                                                                   |

| FSEL0            | I   | Flag-select bit 0. During master reset, FSEL0, along with FSEL1 and LD, selects the default offset values for PAE and PAF. Up to eight possible settings are available.                                                                                                                                                                                                                                                                                                                        |

| FSEL1            | I   | Flag-select bit 1. During master reset, FSEL1, along with FSEL0 and LD, selects the default offset values for PAE and PAF. Up to eight possible settings are available.                                                                                                                                                                                                                                                                                                                        |

| FWFT/SI          | I   | First-word fall-through/serial in. During master reset, FWFT/SI selects FWFT or standard mode. After master reset, FWFT/SI functions as a serial input for loading offset registers.                                                                                                                                                                                                                                                                                                           |

| HF               | 0   | Half-full flag. HF indicates whether the FIFO memory is more or less than half full.                                                                                                                                                                                                                                                                                                                                                                                                           |

| IP               | I   | Interspersed parity. During master reset, a low on IP selects noninterspersed-parity mode. A high on IP selects interspersed-parity mode.                                                                                                                                                                                                                                                                                                                                                      |

| IW               | I   | Input width. IW selects the bus width of the write port. During master reset, when IW is low, the write port is configured with a $\times$ 18 bus width. If IW is high, the write port is a $\times$ 9 bus width.                                                                                                                                                                                                                                                                              |

| LD               | I   | Load. This is a dual-purpose pin. During master reset, the state of the LD input, along with FSEL0 and FSEL1, determines one of eight default offset values for the PAE and PAF flags, along with the method by which these offset registers can be programmed, parallel or serial (see Table 2). After master reset, LD enables writing to and reading from the offset registers.                                                                                                             |

| MRS              | I   | Master reset. MRS initializes the read and write pointers to zero and sets the output register to all zeroes. During master reset, the FIFO is configured for either FWFT or standard mode, bus-matching configurations, one of eight programmable-flag default settings, serial or parallel programming of the offset settings, big-endian/little-endian format, zero- or normal-latency retransmit, interspersed parity, and synchronous versus asynchronous programmable-flag timing modes. |

| OE               | I   | Output enable. OE controls the output impedance of Qn.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ow               | I   | Output width. OW selects the bus width of the read port. During master reset, when OW is low, the read port is configured with a $\times$ 18 bus width. If OW is high, the read port is a $\times$ 9 bus width.                                                                                                                                                                                                                                                                                |

| PAE              | 0   | Programmable almost-empty flag. PAE goes low if the number of words in the FIFO memory is less than or equal to offset n, which is stored in the empty offset register. PAE goes high if the number of words in the FIFO memory is greater than offset n. Add one if PAE is in FWFT mode.                                                                                                                                                                                                      |

| PAF              | 0   | Programmable almost-full flag. PAF goes high if the number of free locations in the FIFO memory is more than offset m, which is stored in the full offset register. PAF goes low if the number of free locations in the FIFO memory is less than or equal to m.                                                                                                                                                                                                                                |

**Terminal Functions (Continued)**

| TERMINAL<br>NAME | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                           |

|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFM              | I   | Programmable-flag mode. During master reset, a low on PFM selects asynchronous programmable-flag timing mode. A high on PFM selects synchronous programmable-flag timing mode.                                                                                                                                                                                        |

| PRS              | I   | Partial reset. PRS initializes the read and write pointers to zero and sets the output register to all zeroes. During partial reset, the existing mode (standard or FWFT), programming method (serial or parallel), and programmable-flag settings, input and output bus widths, big/little endian, interspersed parity select, and retransmit mode are all retained. |

| Q0–Q17           | 0   | Data outputs. Data outputs for a 18- or 9-bit bus. When in 18-bit mode, Q0–Q17 are used and when in 9-bit mode, Q0–Q8 are used, and the unused outputs, Q9–Q17 should not be connected. Outputs are not 5-V tolerant regardless of the state of OE.                                                                                                                   |

| RCLK             | I   | Read clock. When enabled by $\overline{\text{REN}}$ , the rising edge of RCLK reads data from the FIFO memory and offsets from the programmable registers.                                                                                                                                                                                                            |

| REN              | Ι   | Read enable. REN enables RCLK for reading data from the FIFO memory and offset registers.                                                                                                                                                                                                                                                                             |

| RM               | I   | Retransmit latency mode. During master reset, a low on RM selects zero-latency retransmit timing mode. A high on RM selects normal-latency mode.                                                                                                                                                                                                                      |

| RT               | I   | Retransmit. RT asserted on the rising edge of RCLK initializes the READ pointer to zero, sets the EF flag to low (OR to high in FWFT mode) and does not disturb the write pointer, programming method, existing timing mode, or programmable flag settings. RT is useful to reread data starting from the first physical location of the FIFO.                        |

| SEN              | Ι   | Serial enable. SEN enables serial loading of programmable flag offsets.                                                                                                                                                                                                                                                                                               |

| WCLK             | I   | Write clock. When enabled by WEN, the rising edge of WCLK writes data into the FIFO and offsets into the programmable registers for parallel programming and, when enabled by SEN, the rising edge of WCLK writes one bit of data into the programmable register for serial programming.                                                                              |

| WEN              | I   | Write enable. WEN enables WCLK for writing data into the FIFO memory and offset registers.                                                                                                                                                                                                                                                                            |

#### detailed description

inputs

#### data in (D0-Dn)

Data inputs for 18-bit-wide data (D0–D17) or data inputs for 9-bit wide data (D0–D8).

#### controls

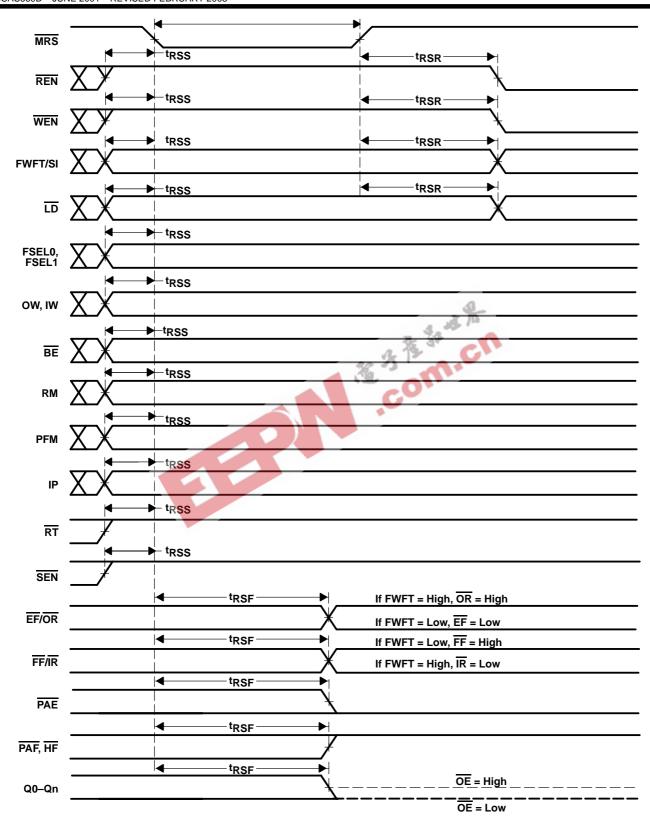

#### master reset (MRS)

A master reset is accomplished when the MRS input is taken to a low state. This operation sets the internal read and write pointers to the first location of the RAM array. PAE goes low, PAF goes high, and HF goes high.

If FWFT/SI is high, the FWFT mode, along with  $\overline{IR}$  and  $\overline{OR}$ , is selected.  $\overline{OR}$  goes high and  $\overline{IR}$  goes low. If FWFT/SI is low during master reset, the standard mode, along with  $\overline{EF}$  and  $\overline{FF}$ , is selected.  $\overline{EF}$  goes low and  $\overline{FF}$  goes high.

All control settings, such as OW, IW, BE, RM, PFM, and IP, are defined during the master reset cycle.

During a master reset, the output register is initialized to all zeroes. A master reset is required after power up, before a write operation can take place. MRS is asynchronous.

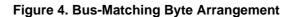

See Figure 5 for timing information.

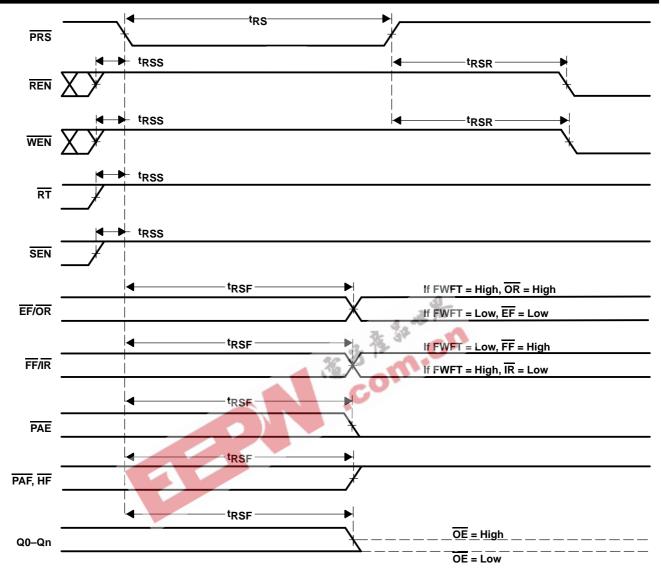

#### partial reset (PRS)

A partial reset is accomplished when the PRS input is taken to a low state. As in the case of the master reset, the internal read and write pointers are set to the first location of the RAM array, PAE goes low, PAF goes high, and HF goes high.

Whichever mode is active at the time of partial reset remains selected (FWFT or standard mode). If FWFT mode is active,  $\overline{OR}$  goes high and  $\overline{IR}$  goes low. If the standard mode is active,  $\overline{FF}$  goes high and  $\overline{EF}$  goes low.

Following partial reset, all values held in the offset registers remain unchanged. The programming method (parallel or serial) active at the time of partial reset also is retained. The output register is initialized to all zeroes. PRS is asynchronous.

A partial reset is useful for resetting the device during operation, when reprogramming programmable-flag offset settings might not be convenient.

See Figure 6 for timing information.

#### retransmit (RT)

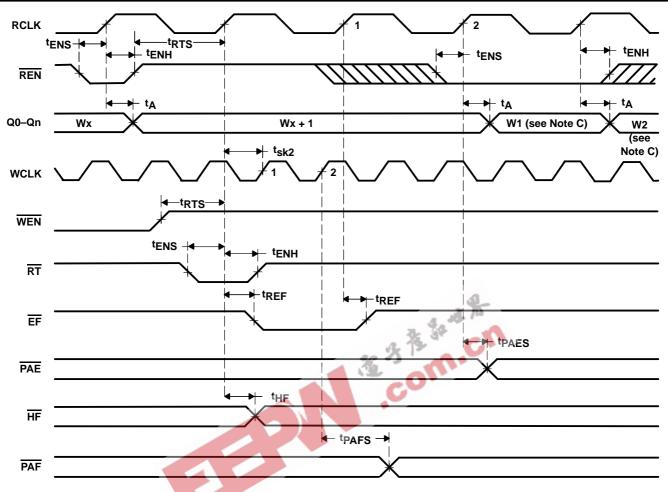

The retransmit operation allows previously read data to be accessed again. There are two modes of retransmit operation: normal latency and zero latency. There are two stages to retransmit. The first stage is a setup procedure that resets the read pointer to the first location of memory. The second stage is the actual retransmit, which consists of reading out the memory contents, starting at the beginning of the memory.

Retransmit setup is initiated by holding RT low during a rising RCLK edge. REN and WEN must be high before RCLK rises when RT is low. When zero latency is used, REN need not be high before RCLK rises while RT is low.

If FWFT mode is selected, the FIFO marks the beginning of the retransmit setup by setting OR high. During this period, the internal read pointer is set to the first location of the RAM array.

When OR goes low, retransmit setup is complete; at the same time, the contents of the first location appear on the outputs. Because FWFT mode is selected, the first word appears on the outputs and no low on REN is necessary. Reading all subsequent words requires a low on REN to enable the rising edge of RCLK.

#### See Figure 12 for timing information.

If standard mode is selected, the FIFO marks the beginning of the retransmit setup by setting  $\overline{EF}$  low. The change in level is noticeable only if  $\overline{EF}$  was high before setup. During this period, the internal read pointer is initialized to the first location of the RAM array.

When EF goes high, retransmit setup is complete and read operations can begin, starting with the first location in memory. Since standard mode is selected, every word read, including the first word following retransmit setup, requires a low on REN to enable the rising edge of RCLK.

See Figure 11 for timing information.

In retransmit operation, the zero-latency mode can be selected using the retransmit latency mode (RM) pin during a master reset. This can be applied to the standard mode and the FWFT mode.

#### retransmit latency mode (RM)

A zero-latency retransmit timing mode can be selected using RM. During master reset, a low on RM selects zero-latency retransmit. A high on RM during master reset selects normal latency.

If zero-latency retransmit operation is selected, the first data word to be retransmitted is placed on the output register with respect to the same RCLK edge that initiated the retransmit based on  $\overline{RT}$  being low.

See Figures 13 and 14 for timing information.

#### first-word fall-through/serial in (FWFT/SI)

FWFT/SI is a dual-purpose pin. During master reset, the state of the FWFT/SI input determines whether the device operates in FWFT mode or standard mode.

If, at the time of master reset, FWFT/SI is high, FWFT mode is selected. This mode uses  $\overline{OR}$  to indicate whether there is valid data at the data outputs (Qn). It also uses  $\overline{IR}$  to indicate whether the FIFO memory has any free space for writing. In the FWFT mode, the first word written to an empty FIFO goes directly to Qn after three RCLK rising edges;  $\overline{REN}$  = low is not necessary. Subsequent words must be accessed using  $\overline{REN}$  and RCLK.

If, at the time of master reset, FWFT/SI is low, standard mode is selected. This mode uses  $\overline{EF}$  to indicate whether there are any words present in the FIFO memory. It also uses the  $\overline{FF}$  to indicate whether the FIFO memory has any free space for writing. In standard mode, every word read from the FIFO, including the first, must be requested using  $\overline{REN}$  and RCLK.

After master reset, FWFT/SI acts as a serial input for loading PAE and PAF offsets into the programmable registers. The serial input function can be used only when the serial loading method is selected during master reset. Serial programming using the FWFT/SI pin functions the same way in both FWFT and standard modes.

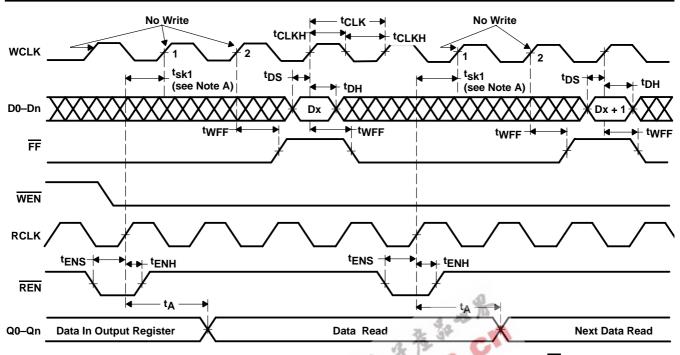

#### write clock (WCLK)

A write cycle is initiated on the rising edge of the WCLK input. Data setup and hold times must be met, with respect to the low-to-high transition of WCLK. It is permissible to stop WCLK. Note that while WCLK is idle, the FF/IR, PAF, and HF flags are not updated. (WCLK is capable only of updating the HF flag to low.) The write and read clocks can be either independent or coincident.

#### write enable (WEN)

When WEN is low, data can be loaded into the FIFO RAM array on the rising edge of every WCLK cycle if the device is not full. Data is stored in the RAM array sequentially and independently of any ongoing read operation.

When WEN is high, no new data is written in the RAM array on each WCLK cycle.

To prevent data overflow in the FWFT mode,  $\overline{IR}$  goes high, inhibiting further write operations. After completion of a valid read cycle,  $\overline{IR}$  goes low, allowing a write to occur. The  $\overline{IR}$  flag is updated by two WCLK cycles + t<sub>sk</sub> after the valid RCLK cycle.

To prevent data overflow in the standard mode,  $\overline{FF}$  goes low, inhibiting further write operations. After completion of a valid read cycle,  $\overline{FF}$  goes high, allowing a write to occur. The  $\overline{FF}$  is updated by two WCLK cycles + t<sub>sk</sub> after the RCLK cycle.

WEN is ignored when the FIFO is full in either FWFT or standard modes.

#### read clock (RCLK)

A read cycle is initiated on the rising edge of the RCLK input. Data can be read on the outputs, on the rising edge of the RCLK input. It is permissible to stop RCLK. While RCLK is idle, the EF/OR, PAE and HF flags are not updated. RCLK is capable only of updating the HF flag to high. The write and read clocks can be independent or coincident.

#### read enable (REN)

When REN is low, data is loaded from the RAM array into the output register on the rising edge of every RCLK cycle, if the device is not empty.

When REN is high, the output register holds the previous data and no new data is loaded into the output register. The data outputs Q0–Qn maintain the previous data value.

In the FWFT mode, the first word written to an empty FIFO automatically goes to the outputs Qn on the third valid low-to-high transition of RCLK +  $t_{sk}$  after the first write. REN does not need to be asserted low. To access all other words, a read must be executed using REN. The RCLK low-to-high transition after the last word has been read from the FIFO, OR goes high with a true read (RCLK with REN = low), inhibiting further read operations. REN is ignored when the FIFO is empty.

In the standard mode, every word accessed at Qn, including the first word written to an empty FIFO, must be requested using  $\overline{\text{REN}}$ . When the last word has been read from the FIFO,  $\overline{\text{EF}}$  goes low, inhibiting further read operations.  $\overline{\text{REN}}$  is ignored when the FIFO is empty. Once a write is performed,  $\overline{\text{EF}}$  goes high, allowing a read to occur. The  $\overline{\text{EF}}$  flag is updated by two RCLK cycles + t<sub>sk</sub> after the valid WCLK cycle.

#### serial enable (SEN)

The SEN input is an enable used only for serial programming of the offset registers. The serial programming method must be selected during master reset. SEN always is used with LD. When these lines are both low, data at the SI input can be loaded into the program register, with one bit for each low-to-high transition of WCLK.

When SEN is high, the programmable registers retain the previous settings and no offsets are loaded. SEN functions the same way in FWFT and standard modes.

#### output enable (OE)

When  $\overline{OE}$  is asserted (low), the parallel output buffers receive data from the output register. When  $\overline{OE}$  is high, the output data bus (Qn) goes into the high-impedance state.

#### load (LD)

$\overline{\text{LD}}$  is a dual-purpose pin. During master reset, the state of the  $\overline{\text{LD}}$  input, along with FSEL0 and FSEL1, determines one of eight default offset values for the  $\overline{\text{PAE}}$  and  $\overline{\text{PAF}}$  flags, along with the method by which these offset registers can be programmed, parallel or serial (see Table 2). After master reset,  $\overline{\text{LD}}$  enables write operations to and read operations from the offset registers. Only the offset loading method currently selected can be used to write to the registers. Offset registers can be read only in parallel.

After master reset, LD is used to activate the programming process of the flag offset values PAE and PAF. Pulling LD low begins a serial loading, or a parallel load, or a read of these offset values.

#### input width (IW)/output width (OW) bus matching

IW and OW define the input and output bus widths. During master reset, the state of these pins is used to configure the device bus sizes (see Table 1 for control settings). All flags operate based on the word/byte size boundary, as defined by the selection of the widest input or output bus width.

#### big endian/little endian (BE)

During master reset, a low on  $\overline{\text{BE}}$  selects big-endian operation. A high on  $\overline{\text{BE}}$  during master reset selects little-endian format. This function is useful when data is written into the FIFO in word format (×18) and read out of the FIFO in word format (×18) or byte format (×9). If big-endian mode is selected, the MSB of the word written into the FIFO is read out of the FIFO first, followed by the LSB. If little-endian format is selected, the LSB of the word written into the FIFO is read out first, followed by the MSB. The desired mode is configured during master reset by the state of the  $\overline{\text{BE}}$ .

See Figure 4 for the byte arrangement.

#### programmable-flag mode (PFM)

During master reset, a low on PFM selects asynchronous programmable-flag timing mode. A high on PFM selects synchronous programmable-flag timing mode. If asynchronous PAF/PAE configuration is selected (PFM low during MRS), PAE is asserted low on the low-to-high transition of RCLK. PAE is reset to high on the low-to-high transition of WCLK. Similarly, PAF is asserted low on the low-to-high transition of WCLK, and PAF is reset to high on the low-to-high transition of RCLK.

If the synchronous PAE/PAF configuration is selected (PFM high during MRS), PAE is asserted and updated on the rising edge of RCLK only, and not WCLK. Similarly, PAF is asserted and updated on the rising edge of WCLK only, and not RCLK. The mode desired is configured during master reset by the state of PFM.

#### interspersed parity (IP)

During master reset, a low on IP selects noninterspersed-parity mode. A high selects interspersed-parity mode. The IP bit function allows the user to select the parity bit in the word loaded into the parallel port (D0–Dn) when programming the flag offsets. If interspersed-parity mode is selected, the FIFO assumes that the parity bit is located in bit positions D8 and D17 during the parallel programming of the flag offsets and, therefore, ignores D8 when loading the offset register in parallel mode. This also is applied to the output register when reading the value of the offset register. If interspersed parity is selected, output Q8 is invalid. If noninterspersed-parity mode is selected, D16 and D17 are the parity bits and are ignored during parallel programming of the offset register. If bits also is a valid bit when performing a read of the offset register. Interspersed-parity mode is selected during master reset by state of IP.

#### outputs

#### full flag/input ready (FF/IR)

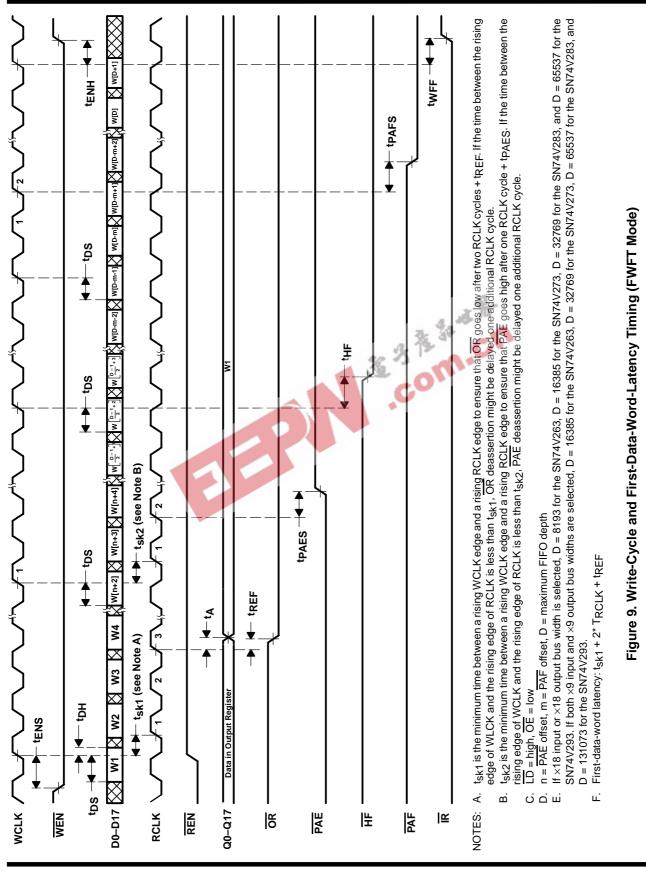

$\overline{FI/IR}$  is a dual-purpose pin. In FWFT mode, the  $\overline{IR}$  function is selected.  $\overline{IR}$  goes low when memory space is available for writing in data. When there is no longer any free space left,  $\overline{IR}$  goes high, inhibiting further write operations. If no reads are performed after a reset (either MRS or PRS), IR goes high after D writes to the FIFO. If ×18 input or ×18 output bus width is selected, D = 8193 for the SN74V263, D = 16385 for the SN74V273, D = 32769 for the SN74V283, and D = 65537 for the SN74V293. If both ×9 input and ×9 output bus widths are selected, D = 16385 for the SN74V263, D = 32769 for the SN74V263, D = 16385 for the SN74V263, D = 131073 for the SN74V293.

See Figure 9 for timing information.

In standard mode, the FF function is selected. When the FIFO is full, FF goes low, inhibiting further write operations. When FF is high, the FIFO is not full. If no reads are performed after a reset (either MRS or PRS), FF goes low after D writes to the FIFO. If ×18 input or ×18 output bus width is selected, D = 8192 for the SN74V263, D = 16384 for the SN74V273, D = 32768 for the SN74V283, and D = 65536 for the SN74V293. If both ×9 input and ×9 output bus widths are selected, D = 16384 for the SN74V263, D = 32768 for the SN74V263, D = 32768 for the SN74V273, D = 65536 for the SN74V283, and D = 131072 for the SN74V293.

#### See Figure 7 for timing information.

The  $\overline{IR}$  status not only measures the contents of the FIFO memory, but also counts the presence of a word in the output register. Thus, in FWFT mode, the total number of writes necessary to deassert  $\overline{IR}$  is one greater than needed to assert  $\overline{FF}$  in standard mode.

FF/IR is synchronous and updated on the rising edge of WCLK. FF/IR are double register-buffered outputs.

#### empty flag/output ready (EF/OR)

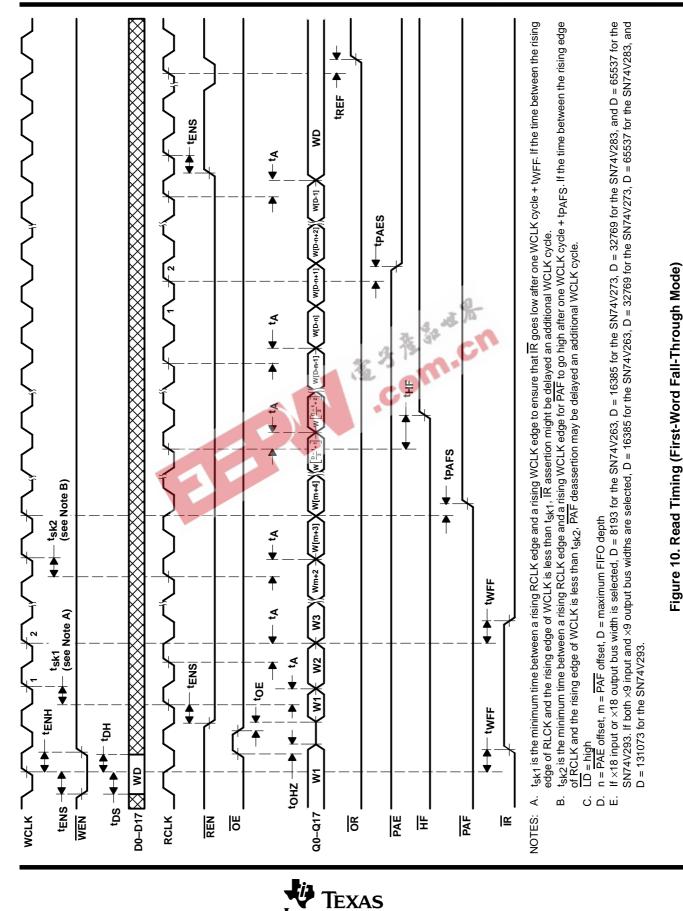

$\overline{\text{EF}/\text{OR}}$  is a dual-purpose pin. In FWFT mode, the  $\overline{\text{OR}}$  function is selected.  $\overline{\text{OR}}$  goes low at the same time that the first word written to an empty FIFO appears valid on the outputs.  $\overline{\text{OR}}$  stays low after the RCLK low-to-high transition that shifts the last word from the FIFO memory to the outputs.  $\overline{\text{OR}}$  goes high only with a true read (RCLK with  $\overline{\text{REN}}$  = low). The previous data stays at the outputs, indicating the last word was read. Further data reads are inhibited until  $\overline{\text{OR}}$  goes low again.

See Figure 10 for timing information.

In the standard mode, the  $\overline{EF}$  function is selected. When the FIFO is empty,  $\overline{EF}$  goes low, inhibiting further read operations. When  $\overline{EF}$  is high, the FIFO is not empty.

See Figure 8 for timing information.

EF/OR is synchronous and updated on the rising edge of RCLK.

In FWFT mode,  $\overline{OR}$  is a triple register-buffered output. In standard mode,  $\overline{EF}$  is a double register-buffered output.

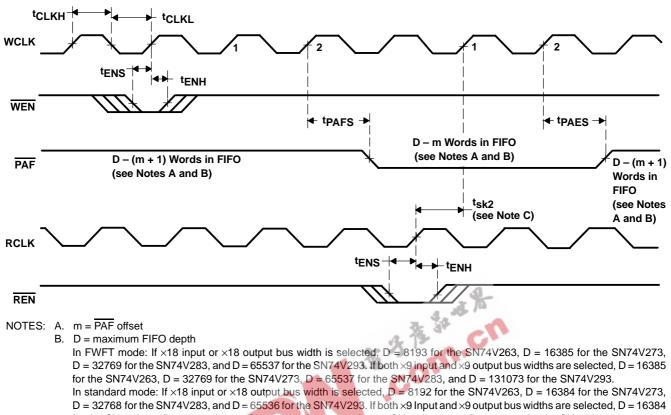

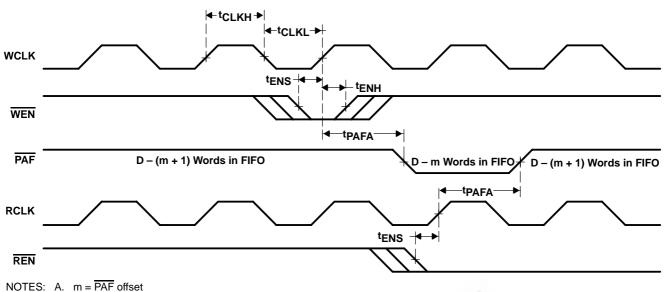

#### programmable almost-full flag (PAF)

PAF goes low when the FIFO reaches the almost-full condition. In FWFT mode, if ×18 input or ×18 output bus width is selected, PAF goes low after (8193 - m) writes for the SN74V263, (16385 - m) writes for the SN74V273, (32769 - m) writes for the SN74V283, and (65537 - m) writes for the SN74V293. If both ×9 input and ×9 output bus widths are selected, PAF goes low after (16385 - m) writes for the SN74V263, (32769 - m) writes for the SN74V283, and (13073 - m) writes for the SN74V293. If both ×9 input and ×9 output bus widths are selected, PAF goes low after (16385 - m) writes for the SN74V263, (32769 - m) writes for the SN74V273, (65537 - m) writes for the SN74V283, and (131073 - m) writes for the SN74V293. The offset m is the full offset value. The default setting for this value is shown in Table 2.

In standard mode, if no reads are performed after  $\overline{MRS}$ ,  $\overline{PAF}$  goes low after (D - m) words are written to the FIFO. If ×18 input or ×18 output bus width is selected, (D - m) = (8192 - m) writes for the SN74V263, (16384 - m) writes for the SN74V273, (32768 - m) writes for the SN74V283, and (65536 - m) writes for the SN74V293. If both ×9 input and ×9 output bus widths are selected, (D - m) = (16384 - m) writes for the SN74V263, (32768 - m) writes for the SN74V283, and (131072 - m) writes for the SN74V293. The offset m is the full offset value. The default setting for this value is shown in Table 2.

See Figure 18 for timing information.

If asynchronous PAF configuration is selected, the PAF is asserted low on the low-to-high transition of WCLK. PAF is reset to high on the low-to-high transition of RCLK. If synchronous PAF configuration is selected, the PAF is updated on the rising edge of WCLK (see Figure 20).

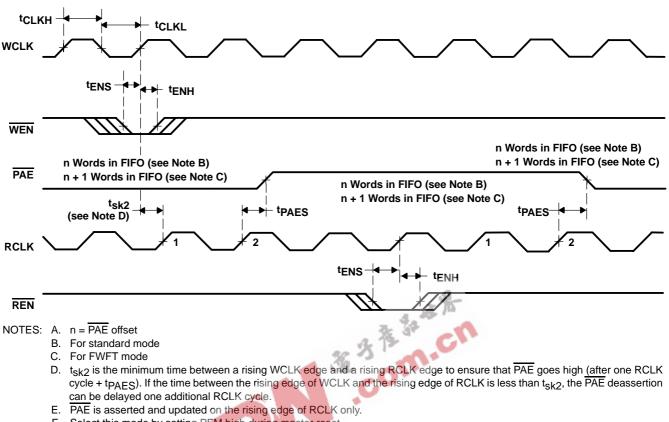

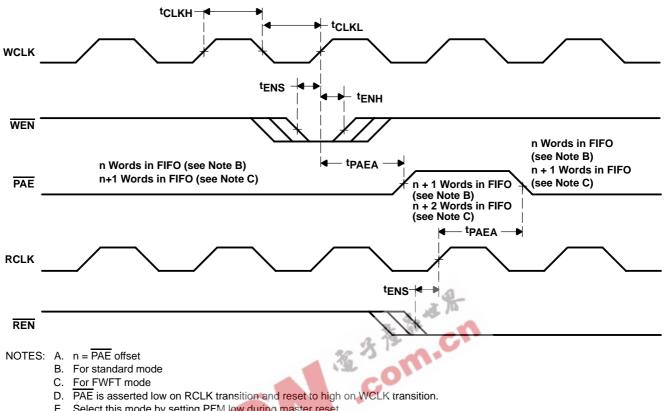

#### programmable almost-empty flag (PAE)

PAE goes low when the FIFO reaches the almost-empty condition. In FWFT mode,  $\overline{PAE}$  goes low when there are n + 1 words, or fewer, in the FIFO. The default setting for this value is shown in Table 2.

In standard mode, PAE goes low when there are n words, or fewer, in the FIFO. The offset n is the empty offset value. The default setting for this value is shown in Table 2.

See Figure 19 for timing information.

If asynchronous  $\overline{PAE}$  configuration is selected,  $\overline{PAE}$  is asserted low on the low-to-high transition of the read clock (RCLK).  $\overline{PAE}$  is reset to high on the low-to-high transition of the write clock (WCLK). If synchronous  $\overline{PAE}$  configuration is selected,  $\overline{PAE}$  is updated on the rising edge of RCLK.

See Figure 21 for timing information.

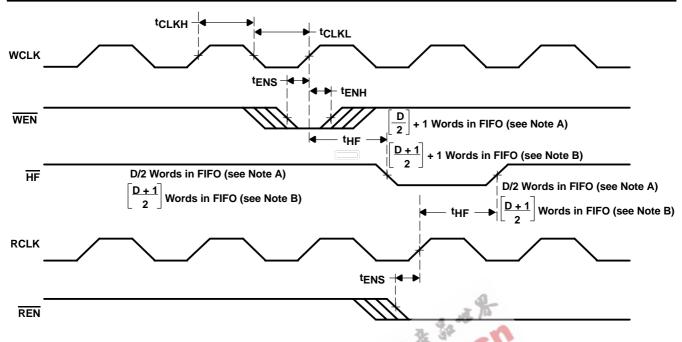

#### half-full flag (HF)

The HF output indicates a half-full FIFO. The rising WCLK edge that fills the FIFO beyond half-full sets HF low. The flag remains low until the difference between the write and read pointers becomes less than or equal to half of the total depth of the device. The rising RCLK edge that accomplishes this condition sets HF high.

In FWFT mode, if no reads are performed after reset ( $\overline{\text{MRS}}$  or  $\overline{\text{PRS}}$ ),  $\overline{\text{HF}}$  goes low after [(D - 1)/2] + 2 writes to the FIFO. If  $\times$ 18 input or  $\times$ 18 output bus width is selected, D = 8193 for the SN74V263, D = 16385 for the SN74V273, D = 32769 for the SN74V283, and D = 65537 for the SN74V293. If both  $\times 9$  input and  $\times 9$  output bus widths are selected, D = 16385 for the SN74V263, D = 32769 for the SN74V273, D = 65537 for the SN74V283, and D = 131073 for the SN74V293.

In standard mode, if no reads are performed after reset (MRS or PRS), HF goes low after (D/2) + 1 writes to the FIFO. If  $\times$ 18 input or  $\times$ 18 output bus width is selected, D = 8192 for the SN74V263, D = 16384 for the SN74V273, D = 32768 for the SN74V283, and D = 65536 for the SN74V293. If both ×9 input and ×9 output bus widths are selected, D = 16384 for the SN74V263, D = 32768 for the SN74V273, D = 65536 for the SN74V283, and D = 131072 for the SN74V293.

See Figure 22 for timing information. Because HF is updated by both RCLK and WCLK, it is considered asynchronous.

#### data outputs (Q0-Qn)

Lie data outputs for Q0–Q17 are data outputs for 18-bit-wide data or Q0–Q8 are data outputs for 9-bit-wide data.

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Terminal voltage range with respect to GND, V <sub>TERM</sub> | –0.5 V to 4.5 V |

|---------------------------------------------------------------|-----------------|

| Continuous output current, $I_O (V_O = 0 \text{ to } V_{CC})$ | ±50 mA          |

| Storage temperature range, T <sub>stg</sub>                   | –55°C to 125°C  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### recommended operating conditions

|       |                                       | MIN  | TYP | MAX  | UNIT |

|-------|---------------------------------------|------|-----|------|------|

| VCC   | Supply voltage (see Note 1)           | 3.15 | 3.3 | 3.45 | V    |

| GND   | Supply voltage                        | 0    | 0   | 0    | V    |

| VIH   | High-level input voltage (see Note 2) | 2    |     | 5.5  | V    |

| VIL   | Low-level input voltage               |      |     | 0.8  | V    |

| ТА    | Operating free-air temperature        | 0    |     | 70   | °C   |

| NOTEO |                                       |      |     |      |      |

a the

NOTES: 1.  $V_{CC}$  = 3.3 V ± 0.15 V, JESD8-A compliant 2. Outputs are not 5-V tolerant.

#### electrical characteristics over recommended operating conditions (unless otherwise noted)

| PARAMETER        | TEST CONDITIONS                                                                                              | MIN | MAX | UNIT |

|------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|------|

| VOH              | $I_{OH} = -2 \text{ mA}$                                                                                     | 2.4 |     | V    |

| VOL              | I <sub>OL</sub> = 8 mA                                                                                       |     | 0.4 | V    |

| lı               | $V_{I} = 0.4 V \text{ to } V_{CC}$                                                                           |     | ±1  | μA   |

| IOZ              | $\overline{OE} \ge V_{IH}$ , $V_O = 0.4 V \text{ to } V_{CC}$                                                |     | ±10 | μA   |

| ICC1             | ×9 input to ×9 output, See Notes 3, 4, and 5                                                                 |     | 30  | mA   |

| I <sub>CC2</sub> | ×18 input to ×18 output, See Notes 3, 4, and 5                                                               |     | 35  | mA   |

| ICC3             | Standby, See Notes 3 and 6                                                                                   |     | 15  | mA   |

| C <sub>IN</sub>  | $V_{I} = 0,$ $T_{A} = 25^{\circ}C, f = 1 \text{ MHz}$                                                        |     | 10  | pF   |

| COUT             | $V_{O} = 0$ , $T_{A} = 25^{\circ}C$ , $f = 1 \text{ MHz}$ , Output deselected ( $\overline{OE} \ge V_{IH}$ ) |     | 10  | pF   |

NOTES: 3. Tested with outputs open  $(I_{OUT} = 0)$

4. RCLK and WCLK switch at 20 MHz and data inputs switch at 10 MHz.

5. For ×18 bus widths, typical I<sub>CC2</sub> = 5 + f<sub>S</sub> + 0.02 × C<sub>L</sub> × f<sub>S</sub> (in mA); for ×9 bus widths, typical I<sub>CC1</sub> = 5 + 0.775 f<sub>S</sub> + 0.02 × C<sub>L</sub> × f<sub>S</sub> (in mA). These equations are valid under the following conditions:

$V_{CC}$  = 3.3 V,  $T_A$  = 25°C,  $f_S$  = WCLK frequency = RCLK frequency (in MHz, using TTL levels), data switching at  $f_S/2$ ,  $C_L$  = capacitive load (in pF).

6. All inputs = (V<sub>CC</sub> - 0.2 V) or (GND + 0.2 V), except RCLK and WCLK, which switch at 20 MHz.

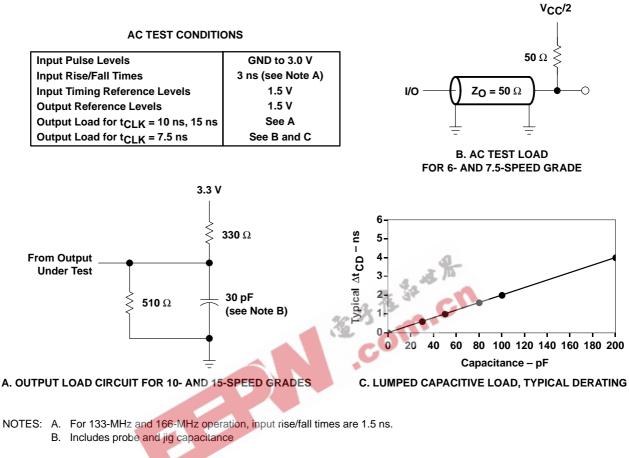

timing requirements over recommended ranges of supply voltage and operating free-air temperature (see Figure 2 through Figure 22)<sup>†</sup>

|                   |                                                                  | SN74V263-6<br>SN74V273-6<br>SN74V283-6<br>SN74V293-6 |     | SN74V263-7.5<br>SN74V273-7.5<br>SN74V283-7.5<br>SN74V293-7.5 |      | I74V273-6 SN74V273-7.5 SN74V273-10 SN74V273-1<br>I74V283-6 SN74V283-7.5 SN74V283-10 SN74V283-1 |     | SN74V273-10<br>SN74V283-10 |      | SN74V273-15<br>SN74V283-15 |  | UNIT |

|-------------------|------------------------------------------------------------------|------------------------------------------------------|-----|--------------------------------------------------------------|------|------------------------------------------------------------------------------------------------|-----|----------------------------|------|----------------------------|--|------|

|                   |                                                                  | MIN                                                  | MAX | MIN                                                          | MAX  | MIN                                                                                            | MAX | MIN                        | MAX  |                            |  |      |

| fclock            | Clock cycle frequency                                            |                                                      | 166 |                                                              | 133  |                                                                                                | 100 |                            | 66.7 | MHz                        |  |      |

| t <sub>A</sub>    | Data access time                                                 | 2                                                    | 4.5 | 2                                                            | 5    | 2                                                                                              | 6.5 | 2                          | 10   | ns                         |  |      |

| <sup>t</sup> CLK  | Clock cycle time                                                 | 6                                                    |     | 7.5                                                          |      | 10                                                                                             |     | 15                         |      | ns                         |  |      |

| <sup>t</sup> CLKH | Clock high time                                                  | 2.5                                                  |     | 3.5                                                          |      | 4.5                                                                                            |     | 6                          |      | ns                         |  |      |

| <sup>t</sup> CLKL | Clock low time                                                   | 2.5                                                  |     | 3.5                                                          |      | 4.5                                                                                            |     | 6                          |      | ns                         |  |      |

| <sup>t</sup> DS   | Data setup time                                                  | 1.5                                                  |     | 2.5                                                          |      | 3.5                                                                                            |     | 4                          |      | ns                         |  |      |

| <sup>t</sup> DH   | Data hold time                                                   | 0.5                                                  |     | 0.5                                                          |      | 0.5                                                                                            |     | 1                          |      | ns                         |  |      |

| <sup>t</sup> ENS  | Enable setup time                                                | 1.5                                                  |     | 2.5                                                          |      | 3.5                                                                                            |     | 4                          |      | ns                         |  |      |

| <sup>t</sup> ENH  | Enable hold time                                                 | 0.5                                                  |     | 0.5                                                          |      | 0.5                                                                                            |     | 1                          |      | ns                         |  |      |

| <sup>t</sup> LDS  | Load setup time                                                  | 2                                                    |     | 3.5                                                          |      | 3.5                                                                                            |     | 4                          |      | ns                         |  |      |

| <sup>t</sup> LDH  | Load hold time                                                   | 0                                                    |     | 0.5                                                          |      | 0.5                                                                                            |     | 1                          |      | ns                         |  |      |

| <sup>t</sup> RS   | Reset pulse duration <sup>‡</sup>                                | 10                                                   |     | 10                                                           |      | 10                                                                                             |     | 15                         |      | ns                         |  |      |

| <sup>t</sup> RSS  | Reset setup time                                                 | 15                                                   |     | 15                                                           |      | 15                                                                                             |     | 15                         |      | ns                         |  |      |

| <sup>t</sup> RSR  | Reset recovery time                                              | 10                                                   |     | 10                                                           |      | 10                                                                                             |     | 15                         |      | ns                         |  |      |

| <sup>t</sup> RSF  | Reset to flag and output time                                    |                                                      | 15  | 0                                                            | 15   |                                                                                                | 15  |                            | 15   | ns                         |  |      |

| <sup>t</sup> RTS  | Retransmit setup time                                            | 2                                                    |     | 3.5                                                          |      | 3.5                                                                                            |     | 4                          |      | ns                         |  |      |

| <sup>t</sup> OLZ  | Output enable to output in low impedance                         | 0                                                    |     | 0                                                            |      | 0                                                                                              |     | 0                          |      | ns                         |  |      |

| <sup>t</sup> OE   | Output enable to output valid                                    | 2                                                    | 4.5 | 2                                                            | 6    | 2                                                                                              | 6   | 2                          | 8    | ns                         |  |      |

| <sup>t</sup> OHZ  | Output enable to output in high impedance                        | 2                                                    | 4.5 | 2                                                            | 6    | 2                                                                                              | 6   | 2                          | 8    | ns                         |  |      |

| tWFF              | Write clock to FF or IR                                          |                                                      | 4.5 |                                                              | 5    |                                                                                                | 6.5 |                            | 10   | ns                         |  |      |

| <sup>t</sup> REF  | Read clock to EF or OR                                           |                                                      | 4.5 |                                                              | 5    |                                                                                                | 6.5 |                            | 10   | ns                         |  |      |

| <sup>t</sup> PAFA | Clock to asynchronous programmable<br>almost-full flag           |                                                      | 8.5 |                                                              | 12.5 |                                                                                                | 16  |                            | 20   | ns                         |  |      |

| <sup>t</sup> PAFS | Write clock to synchronous programmable<br>almost-full flag      |                                                      | 4.5 |                                                              | 5    |                                                                                                | 6.5 |                            | 10   | ns                         |  |      |

| <sup>t</sup> PAEA | Clock to asynchronous programmable<br>almost-empty flag          |                                                      | 8.5 |                                                              | 12.5 |                                                                                                | 16  |                            | 20   | ns                         |  |      |

| <sup>t</sup> PAES | Read clock to synchronous programmable<br>almost-empty flag      |                                                      | 4.5 |                                                              | 5    |                                                                                                | 6.5 |                            | 10   | ns                         |  |      |

| <sup>t</sup> HF   | Clock to half-full flag                                          |                                                      | 7   |                                                              | 12.5 |                                                                                                | 16  |                            | 20   | ns                         |  |      |

| <sup>t</sup> sk1  | Skew time between read clock and write clock for EF/OR and FF/IR | 4                                                    |     | 5                                                            |      | 7                                                                                              |     | 9                          |      | ns                         |  |      |

| <sup>t</sup> sk2  | Skew time between read clock and write clock for PAE and PAF     | 4                                                    |     | 7                                                            |      | 10                                                                                             |     | 14                         |      | ns                         |  |      |

<sup>†</sup>All ac timings apply to both FWFT mode and standard modes.

<sup>‡</sup> Pulse durations less than minimum values are not allowed.

#### PARAMETER MEASUREMENT INFORMATION

#### functional description

#### timing modes: FWFT mode vs standard mode

The SN74V263, SN74V273, SN74V283, and SN74V293 support two different timing modes of operation: FWFT or standard. The selection of the mode is determined during master reset by the state of FWFT/SI.

If, at the time of master reset, FWFT/SI is high, then FWFT mode is selected. This mode uses  $\overline{OR}$  to indicate whether there is valid data at the data outputs (Qn). It also uses  $\overline{IR}$  to indicate whether the FIFO has any free space for writing. In the FWFT mode, the first word written to an empty FIFO goes directly to Qn after three RCLK rising edges;  $\overline{REN}$  = low is not necessary. Subsequent words must be accessed using  $\overline{REN}$  and RCLK.

If, at the time of master reset, FWFT/SI is low, then standard mode is selected. This mode uses  $\overline{EF}$  to indicate whether there are any words present in the FIFO. It also uses the  $\overline{FF}$  function to indicate whether the FIFO has any free space for writing. In standard mode, every word read from the FIFO, including the first, must be requested, using  $\overline{REN}$  and RCLK.

Various signals (both input and output) operate differently, depending on which timing mode is in effect.

#### FWFT mode

In FWFT mode, status flags  $\overline{IR}$ ,  $\overline{PAF}$ ,  $\overline{HF}$ ,  $\overline{PAE}$ , and  $\overline{OR}$  operate as outlined in Table 4. To write data into the FIFO,  $\overline{WEN}$  must be low. Data presented to the DATA IN lines is clocked into the FIFO on subsequent transitions of WCLK. After the first write is performed, the  $\overline{OR}$  flag goes low after three low-to-high transitions on RCLK. Subsequent writes continue to fill up the FIFO.  $\overline{PAE}$  goes high after n + 2 words have been loaded into the FIFO, where n is the empty offset value. The default setting for these values is in the footnote of Table 2. This parameter also is user programmable (see the *programmable-flag offset loading* section).

If one continues to write data into the FIFO and assumes no read operations are taking place,  $\overline{HF}$  switches to low after the [(D - 1)/2 + 2] words were written into the FIFO. If ×18 input or ×18 output bus width is selected, [(D - 1)/2 + 2] = 4098th word for the SN74V263, 8194th word for SN74V273, 16386th word for the SN74V283, and 32770th word for the SN74V293. If both ×9 input and ×9 output bus widths are selected, [(D - 1)/2 + 2] = 8194th word for the SN74V263, 16386th word for SN74V273, 32770th word for the SN74V283, and 65,538th word for the SN74V293. Continuing to write data into the FIFO causes PAF to go low. Again, if no reads are performed, the PAF goes low after (D - m) writes to the FIFO. If ×18 input or ×18 output bus width is selected, (D - m) = (8193 - m) writes for the SN74V263, (16385 - m) writes for the SN74V273, (32769 - m) writes for the SN74V283, and (65537 - m) writes for the SN74V263, (32769 - m) writes for the SN74V283, and (131073 - m) writes for the SN74V293. The offset m is the full offset value. The default settings for these values are given in the footnote of Table 2.

When the FIFO is full, the  $\overline{IR}$  flag goes high, inhibiting further write operations. If no reads are performed after a reset,  $\overline{IR}$  goes high after D writes to the FIFO. If ×18 input or ×18 output bus width is selected, D = 8193 writes for the SN74V263, D = 16385 writes for the SN74V273, D = 32769 writes for the SN74V283, and D = 65537 writes for the SN74V293. If both ×9 input and ×9 output bus widths are selected, D = 16385 writes for the SN74V263, D = 32769 writes for the SN74V273, D = 65537 writes for the SN74V283, and D = 131073 writes for the SN74V293. Note that the additional word in FWFT mode is due to the capacity of the memory plus output register.

If the FIFO is full, the first read operation cause the  $\overline{IR}$  flag to go low after two low-to-high transitions of WCLK. Subsequent read operations causes the  $\overline{PAF}$  and  $\overline{HF}$  to go high at the conditions shown in Table 4. If further read operations occur without write operations,  $\overline{PAE}$  goes low when there are n + 1 words in the FIFO, where n is the empty offset value. Continuing read operations causes the FIFO to become empty. When the last word has been read from the FIFO,  $\overline{OR}$  goes high, inhibiting further read operations.  $\overline{REN}$  is ignored when the FIFO is empty.

#### FWFT mode (continued)

When configured in FWFT mode, the OR flag output is triple register buffered, and the IR flag output is double register buffered.

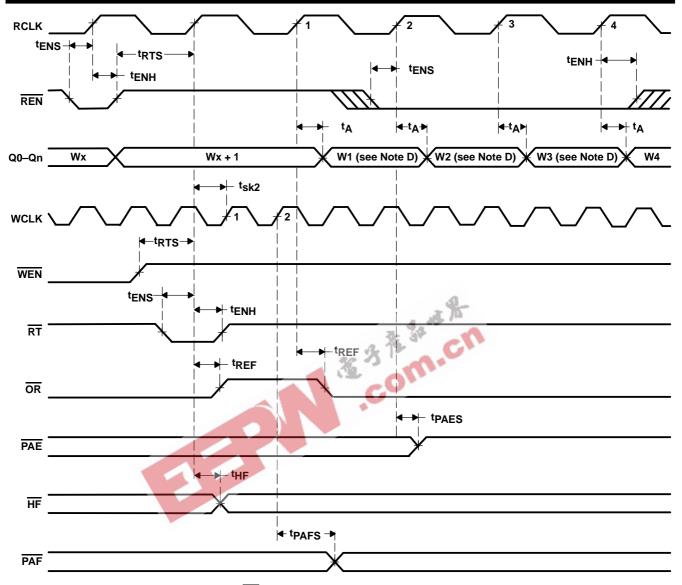

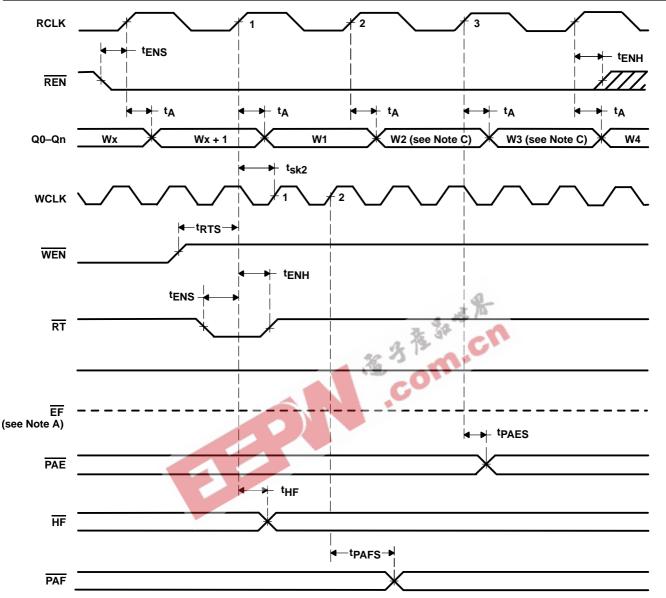

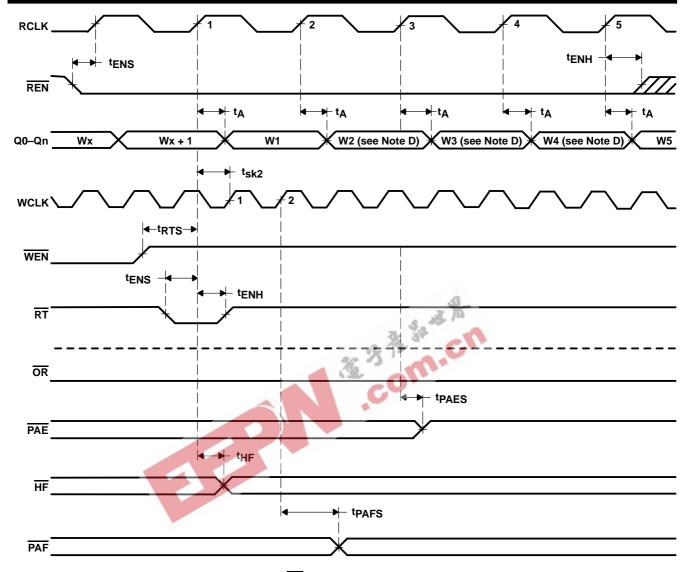

Timing diagrams for FWFT mode can be found in Figures 9, 10, and 12.

#### standard mode

In this mode, status flags FF, PAF, HF, PAE, and EF operate as outlined in Table 3. To write data into to the FIFO, WEN must be low. Data presented to the DATA IN lines is clocked into the FIFO on subsequent transitions of WCLK. After the first write is performed, EF goes high after two low-to-high transitions on RCLK. Subsequent writes continue to fill up the FIFO. PAE goes high after n + 1 words have been loaded into the FIFO, where n is the empty offset value. The default setting for these values is in the footnote of Table 2. This parameter also is user programmable (see the *programmable-flag offset loading* section).

If one continues to write data into the FIFO and assumes no read operations are taking place,  $\overline{HF}$  switches to low after (D/2 + 1) words are written into the FIFO. If ×18 input or ×18 output bus width is selected, (D/2 + 1) = 4097th word for the SN74V263, 8193th word for the SN74V273, 16385th word for the SN74V283, and 32769th word for the SN74V293. If both ×9 input and ×9 output bus widths are selected, (D/2 + 1) = 8193rd word for the SN74V263, 16385th word for the SN74V273, 32769th word for the SN74V283, and 65537th word for the SN74V293. Continuing to write data into the FIFO causes PAF to go low. Again, if no reads are performed, PAF goes low after (D – m) writes to the FIFO. If ×8 input or ×18 output bus width is selected, (D – m) = (8192 – m) writes for the SN74V263, (16384 – m) writes for the SN74V273, (32768 – m) writes for the SN74V283, and (65536 – m) writes for the SN74V293. If both ×9 input and ×9 output bus widths are selected, (D – m) = (16384 – m) writes for the SN74V263, (32768 – m) writes for the SN74V273, (65536 – m) writes for the SN74V283, and (131072 – m) writes for the SN74V293. Offset m is the full offset value. The default setting for these values is in the footnote of Table 2. This parameter also is user programmable (see the *programmable-flag offset loading* section).

When the FIFO is full,  $\overline{FF}$  goes low, inhibiting further write operations. If no reads are performed after a reset,  $\overline{FF}$  goes low after D writes to the FIFO. If the ×18 input or ×18 output bus width is selected, D = 8192 writes for the SN74V263, D = 16384 writes for the SN74V273, D = 32768 writes for the SN74V283, and D = 65536 writes for the SN74V293. If both ×9 input and ×9 output bus widths are selected, D = 16384 writes for the SN74V263, D = 32768 writes for the SN74V283, D = 65536 writes for the SN74V283, and D = 131072 writes for the SN74V293.

If the FIFO is full, the first read operation causes  $\overline{FF}$  to go high after two low-to-high transitions on WCLK. Subsequent read operations cause  $\overline{PAF}$  and  $\overline{HF}$  to go high at the conditions shown in Table 3. If further read operations occur without write operations,  $\overline{PAE}$  goes low when there are n words in the FIFO, where n is the empty offset value. Continuing read operations causes the FIFO to become empty. When the last word has been read from the FIFO,  $\overline{EF}$  goes low, inhibiting further read operations.  $\overline{REN}$  is ignored when the FIFO is empty.

When configured in standard mode, the  $\overline{EF}$  and  $\overline{FF}$  outputs are double register-buffered outputs.

See Figures 7, 8, and 11 for timing diagrams for standard mode.

|    |       |       | OFFSETS (n, m)†      |

|----|-------|-------|----------------------|

| LD | FSEL0 | FSEL1 | SN74V263<br>SN74V273 |

| Н  | L     | L     | 1,023                |

| L  | L     | Н     | 511                  |

| L  | Н     | L     | 255                  |

| L  | L     | L     | 127                  |

| L  | Н     | Н     | 63                   |

| Н  | L     | Н     | 31                   |

| Н  | Н     | L     | 15                   |

| Н  | Н     | Н     | 7                    |

| Table 2. | Default | Programmable | Flag | Offsets |

|----------|---------|--------------|------|---------|

|----------|---------|--------------|------|---------|

|   |        |       | OFFSETS (n, m) <sup>†</sup> |                  |          |  |  |  |

|---|--------|-------|-----------------------------|------------------|----------|--|--|--|

|   | FSEL0  | FSEL1 | SN74                        | V283             |          |  |  |  |

|   | I OLLU | IOLLI | ALL OTHER<br>MODES          | ×9 TO ×9<br>MODE | SN74V293 |  |  |  |

| L | L      | Н     | 511                         | 16383            | 16383    |  |  |  |

| L | Н      | L     | 255                         | 8191             | 8191     |  |  |  |

| L | Н      | Н     | 63                          | 4,095            | 4,095    |  |  |  |

| Н | L      | Н     | 31                          | 2,047            | 2,047    |  |  |  |

| Н | L      | L     | 1,023                       | 1,023            | 1,023    |  |  |  |

| Н | Н      | L     | 15                          | 511              | 511      |  |  |  |

| Н | Н      | Н     | 7                           | 255              | 255      |  |  |  |

| L | L      | L     | 127                         | 127              | 127      |  |  |  |

$\dagger$  n = empty offset for  $\overline{PAE}$ , m = full offset for  $\overline{PAF}$

#### programming flag offsets

Full and empty flag offset values are user programmable. The SN74V263, SN74V273, SN74V283, and SN74V293 have internal registers for these offsets. Eight default offset values are selectable during master reset. These offset values are shown in Table 2. Offset values also can be programmed into the FIFO by serial or parallel loading. The loading method is selected using LD. During master reset, the state of the LD input determines whether serial or parallel flag offset programming is enabled. A high on LD during master reset selects serial loading of offset values. A low on LD during master reset selects parallel loading of offset values.

In addition to loading offset values into the FIFO, it also is possible to read the current offset values. Offset values can be read via the parallel output ports Q0–Qn, regardless of the programming mode selected (serial or parallel). It is not possible to read the offset values in serial fashion.

Figure 3 summarizes the control pins and sequence for both serial and parallel programming modes. A more detailed description is given in the following paragraphs.

The offset registers can be programmed (and reprogrammed) any time after master reset, regardless of whether serial or parallel programming has been selected. Valid programming ranges are from 0 to D - 1.

#### synchronous vs asynchronous programmable-flag timing selection

The SN74V263, SN74V273, SN74V283, and SN74V293 can be configured during the master reset cycle with either synchronous or asynchronous timing for PAF and PAE flags by use of the PFM pin.

If synchronous PAF/PAE configuration is selected (PFM high during MRS), PAF is asserted and updated on the rising edge of WCLK only and not RCLK. Similarly, PAE is asserted and updated on the rising edge of RCLK only and not WCLK (see Figure 18 for synchronous PAF timing and Figure 19 for synchronous PAE timing).

If asynchronous PAF/PAE configuration is selected (PFM low during MRS), PAF is asserted low on the low-to-high transition of WCLK and PAF is reset to high on the low-to-high transition of RCLK. Similarly, PAE is asserted low on the low-to-high transition of RCLK. PAE is reset to high on the low-to-high transition of WCLK (see Figure 20 for asynchronous PAF timing and Figure 21 for asynchronous PAE timing).

#### Table 3. Status Flags for Standard Mode

| IW = OW = ×9                  |                             | SN74V263                     | SN74V273                      | SN74V283                      | SN74V293                          |    |     |    |     |    |

|-------------------------------|-----------------------------|------------------------------|-------------------------------|-------------------------------|-----------------------------------|----|-----|----|-----|----|

| IW ≠ OW OR<br>IW = OW = ×18   | SN74V263                    | SN74V273 SN74V283            |                               | SN74V293                      |                                   | FF | PAF | HF | PAE | EF |

|                               | 0                           | 0                            | 0                             | 0                             | 0                                 | Н  | Н   | Н  | L   | L  |

|                               | 1 to n                      | 1 to n                       | 1 to n                        | 1 to n                        | 1 to n                            | Н  | Н   | Н  | L   | Н  |

|                               | (n + 1) to 4096             | (n + 1) to 8192              | (n + 1) to 16384              | (n + 1) to 32768              | (n + 1) to 65536                  | Н  | Н   | Н  | Н   | Н  |

| Number of<br>Words<br>in FIFO | 4097 to<br>[8192 – (m + 1)] | 8193 to<br>[16384 – (m + 1)] | 16385 to<br>[32768 – (m + 1)] | 32769 to<br>[65536 – (m + 1)] | 65537 to<br>[131072 –<br>(m + 1)] | н  | н   | L  | н   | н  |

|                               | (8192 – m) to<br>8191       | (16384 – m) to<br>16383      | (32768 – m) to<br>32767       | (65536 – m) to<br>65535       | (131072 – m) to<br>131071         | н  | L   | L  | н   | н  |

|                               | 8192                        | 16384                        | 32768                         | 65536                         | 131072                            | L  | L   | L  | Н   | н  |

NOTE 1: See Table 2 for values for n, m.

#### Table 4. Status Flags for FWFT Mode

| IW = OW = ×9                |                             | SN74V263                     | SN74V273                      | SN74V283                      | SN74V293                       |    |     |    |     |    |

|-----------------------------|-----------------------------|------------------------------|-------------------------------|-------------------------------|--------------------------------|----|-----|----|-----|----|