### **INTEGRATED CIRCUITS**

# DATA SHEET

# 74F194

4-bit bidirectional universal shift register

Product specification

1989 Apr 04

IC15 Data Handbook

### 4-bit bidirectional universal shift register

74F194

#### **FEATURES**

- Shift right and shift left capability

- Synchronous parallel and serial data transfer

- Easily expanded for both serial and parallel operation

- Asynchronous Master Reset

- Hold (do nothing) mode

#### **DESCRIPTION**

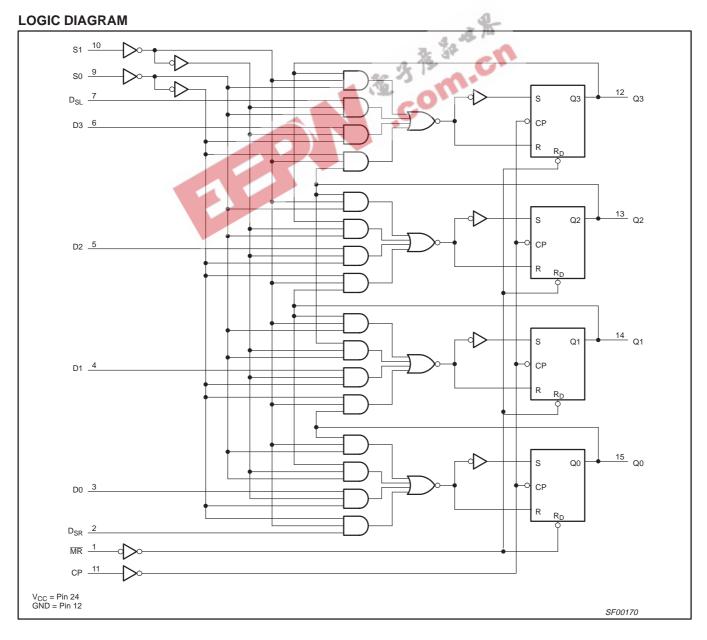

The functional characteristics of the 74F194 4-Bit Bidirectional Shift Register are indicated in the Logic Diagram and Function Table. The register is fully synchronous, with all operations taking place in less than 9ns (typical) for 74F, making the device especially useful for implementing very high speed CPUs, or for memory buffer registers.

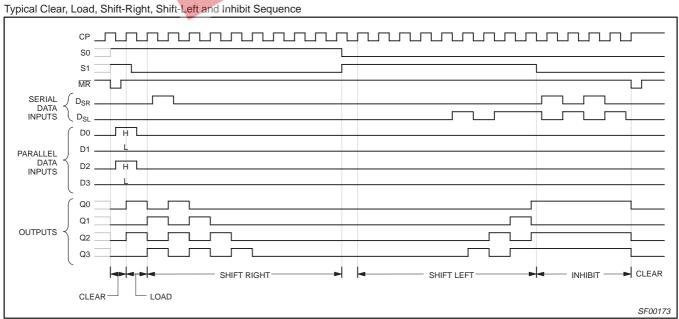

The 74F194 design has special logic features which increase the range of application. The synchronous operation of the device is determined by two Mode Select inputs, S0 and S1. As shown in the Mode Select-Function Table, data can be entered and shifted from left to right (shift right, Q0→Q1, etc.), or right to left (shift left, Q3-Q2, etc.), or parallel data can be entered, loading all 4 bits of the register simultaneously. When both S0 and S1 are Low, existing data is retained in a hold (do nothing) mode. The first and last stages provide D-type Serial Data inputs (DSR, DSL) to allow multistage shift right or shift left data transfers without interfering with parallel load operation. Mode Select and data inputs on the 74F194 are edge-triggered, responding only to the Low-to-High transition of the Clock (CP). Therefore, the only timing restriction is that the Mode Select and selected data inputs must be stable one setup time prior to the Low-to-High transition of the clock pulse. Signals on the Mode Select, Parallel Data (D0-D3) and Serial Data (D<sub>SR</sub>, D<sub>SI</sub>) can change when the clock is in either state, provided only the recommended setup and hold times, with respect to the clock rising edge, are observed. The four Parallel Data inputs (D0-D3) are D-type inputs. Data appearing on (D0-D3) inputs when S0 and S1 are High is transferred to the Q0-Q3 outputs respectively, following the next Low-to-High transition of the clock. When Low, the asynchronous Master Reset (MR) overrides all other input conditions and forces the Q outputs Low.

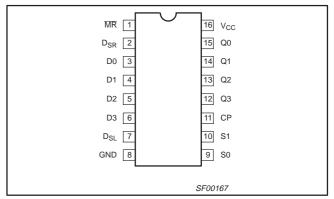

#### PIN CONFIGURATION

| TYPE   | TYPICAL f <sub>MAX</sub> | TYPICAL<br>SUPPLY CURRENT<br>(TOTAL) |

|--------|--------------------------|--------------------------------------|

| 74F194 | 150MHz                   | 33mA                                 |

#### ORDERING INFORMATION

| DESCRIPTION        | COMMERCIAL RANGE $V_{CC}$ = 5V $\pm 10\%$ , $T_{amb}$ = 0°C to +70°C | PKG DWG # |

|--------------------|----------------------------------------------------------------------|-----------|

| 16-pin plastic DIP | N74F194N                                                             | SOT38-4   |

| 16-pin plastic SO  | N74F194D                                                             | SOT109-1  |

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS            | DESCRIPTION                                  | 74F (U.L.) HIGH/LOW | LOAD VALUE HIGH/LOW |

|-----------------|----------------------------------------------|---------------------|---------------------|

| D0-D3           | Parallel data inputs                         | 1.0/1.0             | 20μA/0.6mA          |

| D <sub>SR</sub> | Serial data input (Shift Right)              | 1.0/1.0             | 20μA/0.6mA          |

| D <sub>SL</sub> | Serial data input (Shift Left)               | 1.0/1.0             | 20μA/0.6mA          |

| S0, S1          | Mode Select inputs                           | 1.0/1.0             | 20μA/0.6mA          |

| СР              | Clock Pulse input (active rising edge)       | 1.0/1.0             | 20μA/0.6mA          |

| MR              | Asynchronous master Reset input (Active Low) | 1.0/1.0             | 20μA/0.6mA          |

| Q0-Q3           | Data outputs                                 | 50/33               | 1.0mA/20mA          |

NOTE: One (1.0) FAST unit load is defined as: 20µA in the High state and 0.6mA in the Low state.

# 4-bit bidirectional universal shift register

74F194

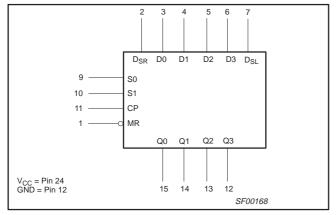

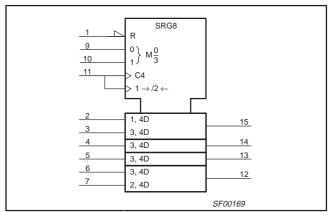

#### **LOGIC SYMBOL**

#### **IEC/IEEE SYMBOL**

April 4, 1989 3

# 4-bit bidirectional universal shift register

74F194

#### **FUNCTION TABLE**

|            |    |     | INPUTS |                 |                 |    |    | OUTI | PUTS |    | OPERATING MODES   |

|------------|----|-----|--------|-----------------|-----------------|----|----|------|------|----|-------------------|

| СР         | MR | S1  | S0     | D <sub>SR</sub> | D <sub>SL</sub> | Dn | Q0 | Q1   | Q2   | Q3 | OPERATING MODES   |

| Х          | L  | Х   | Х      | Х               | Х               | Х  | L  | L    | L    | L  | Reset (clear)     |

| Х          | Н  | I   | Т      | Х               | Х               | Х  | q0 | q1   | q2   | q3 | Hold (do nothing) |

| $\uparrow$ | Н  | h   |        | Х               | ı               | Х  | q1 | q2   | q3   | L  | Shift left        |

| 1          | н  | h   | ı      | Х               | h               | X  | q1 | q2   | q3   | Н  | Shirt left        |

| $\uparrow$ | Н  | I   | h      | I               | Х               | Х  | L  | q0   | q1   | q2 | Chift sight       |

| 1          | Н  | - 1 | h      | h               | X               | X  | Н  | q0   | q1   | q2 | Shift right       |

| $\uparrow$ | Н  | h   | h      | Х               | Х               | dn | d0 | d1   | d2   | d3 | Parallel load     |

#### **ABSOLUTE MAXIMUM RATINGS**

(Operation beyond the limits set forth in this table may impair the useful life of the device. Unless otherwise noted these limits are over the operating free-air temperature range.)

| SYMBOL           | PARAMETER                                      | RATING             | UNIT |

|------------------|------------------------------------------------|--------------------|------|

| V <sub>CC</sub>  | Supply voltage                                 | -0.5 to +7.0       | V    |

| V <sub>IN</sub>  | Input voltage                                  | -0.5 to +7.0       | V    |

| I <sub>IN</sub>  | Input current                                  | -30 to +5          | mA   |

| V <sub>OUT</sub> | Voltage applied to output in High output state | $-0.5$ to $V_{CC}$ | V    |

| I <sub>OUT</sub> | Current applied to output in Low output state  | 40                 | mA   |

| T <sub>amb</sub> | Operating free-air temperature range           | 0 to +70           | °C   |

| T <sub>stg</sub> | Storage temperature range                      | -65 to +150        | °C   |

#### RECOMMENDED OPERATING CONDITIONS

| SYMBOL           | PARAMETER                            |     | LIMITS |     | UNIT |

|------------------|--------------------------------------|-----|--------|-----|------|

| STWIBUL          | PARAMETER                            | MIN | NOM    | MAX | UNII |

| V <sub>CC</sub>  | Supply voltage                       | 4.5 | 5.0    | 5.5 | V    |

| V <sub>IH</sub>  | High-level input voltage             | 2.0 |        |     | V    |

| $V_{IL}$         | Low-level input voltage              |     |        | 0.8 | V    |

| I <sub>IK</sub>  | Input clamp current                  |     |        | -18 | mA   |

| I <sub>OH</sub>  | High-level output current            |     |        | -1  | mA   |

| I <sub>OL</sub>  | Low-level output current             |     |        | 20  | mA   |

| T <sub>amb</sub> | Operating free-air temperature range | 0   |        | +70 | °C   |

April 4, 1989

H = High voltage level

h = High voltage level one setup time prior to Low-to-High clock transition

L = Low voltage level

I = Low voltage level one setup time prior to Low-to-High clock transition

X = Don't care

↑ = Low-to-High clock transition

$<sup>\</sup>uparrow$  = Low-to-High clock transition dn(qn) = Lower case letters indicate the state of the referenced input (or output) one setup time prior to the Low-to-High clock transition.

### 4-bit bidirectional universal shift register

74F194

#### DC ELECTRICAL CHARACTERISTICS

| SYMBOL          | PARAMETER                                 | TEST CONDITION               | NIC1               |      | LIMITS           |      | UNIT |

|-----------------|-------------------------------------------|------------------------------|--------------------|------|------------------|------|------|

| STWIDUL         | PARAMETER                                 | TEST CONDITIO                | JNS.               | MIN  | TYP <sup>2</sup> | MAX  | UNII |

| V               | High-level output voltage <sup>3</sup>    | $V_{CC} = MIN, V_{IL} = MAX$ | 2.5                |      |                  | V    |      |

| V <sub>OH</sub> | nigh-level output voltages                | $V_{IH} = MIN, I_{OH} = MAX$ | ±5%V <sub>CC</sub> | 2.7  | 3.4              |      | V    |

| V               | Low lovel output veltage                  | $V_{CC} = MIN, V_{IL} = MAX$ |                    | 0.30 | 0.50             | V    |      |

| V <sub>OL</sub> | Low-level output voltage                  | $V_{IH} = MIN, I_{OL} = MAX$ | ±5%V <sub>CC</sub> |      | 0.30             | 0.50 | V    |

| V <sub>IK</sub> | Input clamp voltage                       | $V_{CC} = MIN, I_I = I_{IK}$ |                    |      | -0.73            | -1.2 | V    |

| I <sub>I</sub>  | Input current at maximum input voltage    | $V_{CC} = MAX, V_I = 7.0V$   |                    |      |                  | 100  | μΑ   |

| I <sub>IH</sub> | High-level input current                  | $V_{CC} = MAX, V_I = 2.7V$   |                    |      |                  | 20   | μΑ   |

| I <sub>IL</sub> | Low-level input current                   | $V_{CC} = MAX, V_I = 0.5V$   |                    |      |                  | -0.6 | mA   |

| los             | Short-circuit output current <sup>4</sup> | V <sub>CC</sub> = MAX        |                    | -60  |                  | -150 | mA   |

| Icc             | Supply current (total) <sup>5</sup>       | V <sub>CC</sub> = MAX        |                    |      | 33               | 46   | mA   |

#### NOTES:

- For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

All typical values are at V<sub>CC</sub> = 5V, T<sub>amb</sub> = 25°C.

Output High state will change to Low stat if an external voltage of less than 0.0V is applied.

- Output high state will change to Low stat if an external voltage of less than 0.0v is applied.

Not more than one output should be shorted at a time. For testing I<sub>OS</sub>, the use of high-speed test apparatus and/or sample-and-hold techniques are preferable in order to minimize internal heating and more accurately reflect operational values. Otherwise, prolonged shorting of a High output may raise the chip temperature well above normal and thereby cause invalid readings in other parameter tests. In any sequence of parameter tests, I<sub>OS</sub> tests should be performed last.

With all outputs open, D<sub>i</sub> inputs grounded and a 4.5V applied to S0, S1, MR and the serial inputs, I<sub>CC</sub> is tested with a momentary ground,

- then 4.5V applied to CP.

#### AC ELECTRICAL CHARACTERISTICS

|                                      |                               |                   |                | LIMITS                                                               |            |                                                                           |            |     |  |  |  |  |

|--------------------------------------|-------------------------------|-------------------|----------------|----------------------------------------------------------------------|------------|---------------------------------------------------------------------------|------------|-----|--|--|--|--|

| SYMBOL                               | PARAMETER                     | TEST<br>CONDITION | T <sub>a</sub> | <sub>CC</sub> = +5.0<br><sub>mb</sub> = +25<br>0pF, R <sub>L</sub> = | °C         | V <sub>CC</sub> = +5.<br>T <sub>amb</sub> = 0°C<br>C <sub>L</sub> = 50pF, | UNIT       |     |  |  |  |  |

|                                      |                               |                   | MIN            | TYP                                                                  | MAX        | MIN                                                                       | MAX        |     |  |  |  |  |

| f <sub>MAX</sub>                     | Maximum clock frequency       | Waveform 1        | 105            | 150                                                                  |            | 90                                                                        |            | MHz |  |  |  |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>CP to Qn | Waveform 1        | 3.5<br>3.5     | 5.2<br>5.5                                                           | 7.0<br>7.0 | 3.5<br>3.5                                                                | 8.0<br>8.0 | ns  |  |  |  |  |

| t <sub>PHL</sub>                     | Propagation delay MR to Qn    | Waveform 2        | 4.5            | 8.6                                                                  | 12.0       | 4.5                                                                       | 14.0       | ns  |  |  |  |  |

#### **AC SETUP REQUIREMENTS**

|                                          |                                                                        |                   |                                                        | LIMITS                                                               |                    |                                                                           |      |    |  |  |  |  |

|------------------------------------------|------------------------------------------------------------------------|-------------------|--------------------------------------------------------|----------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------|------|----|--|--|--|--|

| SYMBOL                                   | PARAMETER                                                              | TEST<br>CONDITION | V <sub>c</sub><br>T <sub>a</sub><br>C <sub>L</sub> = 5 | <sub>CC</sub> = +5.0<br><sub>mb</sub> = +25<br>0pF, R <sub>L</sub> = | )V<br>°C<br>= 500Ω | V <sub>CC</sub> = +5.<br>T <sub>amb</sub> = 0°0<br>C <sub>L</sub> = 50pF, | UNIT |    |  |  |  |  |

|                                          |                                                                        |                   | MIN                                                    | TYP                                                                  | MAX                | MIN                                                                       | MAX  |    |  |  |  |  |

| t <sub>S</sub> (H)<br>t <sub>S</sub> (L) | Setup time, High or Low<br>Dn, D <sub>SL</sub> , D <sub>SR</sub> to CP | Waveform 3        | 4.0<br>4.0                                             |                                                                      |                    | 4.0<br>4.0                                                                |      | ns |  |  |  |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold time, High or Low<br>Dn, D <sub>SL</sub> , D <sub>SR</sub> to CP  | Waveform 3        | 0                                                      |                                                                      |                    | 1.0<br>1.0                                                                |      | ns |  |  |  |  |

| t <sub>S</sub> (H)<br>t <sub>S</sub> (L) | Setup time, High or Low<br>Sn to CP                                    | Waveform 3        | 8.0<br>8.0                                             |                                                                      |                    | 9.0<br>8.0                                                                |      | ns |  |  |  |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold time, High or Low<br>Sn to CP                                     | Waveform 3        | 0<br>0                                                 |                                                                      |                    | 0<br>0                                                                    |      | ns |  |  |  |  |

| t <sub>W</sub> (H)                       | CP Pulse width, High                                                   | Waveform 1        | 5.0                                                    |                                                                      |                    | 5.5                                                                       |      | ns |  |  |  |  |

| t <sub>W</sub> (L)                       | MR Pulse width, Low                                                    | Waveform 2        | 5.0                                                    |                                                                      |                    | 5.0                                                                       |      | ns |  |  |  |  |

| t <sub>REC</sub>                         | Recovery time, MR to CP                                                | Waveform 2        | 7.0                                                    |                                                                      |                    | 8.0                                                                       |      | ns |  |  |  |  |

5 April 4, 1989

## 4-bit bidirectional universal shift register

74F194

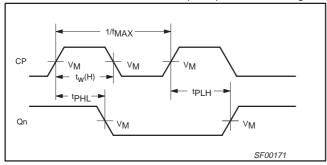

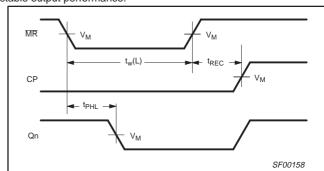

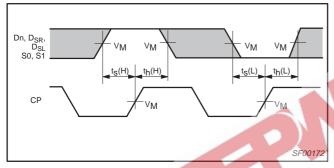

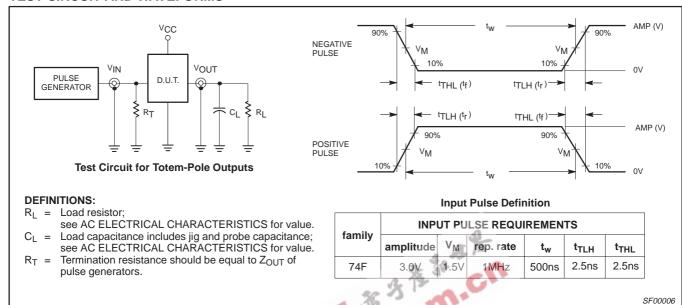

#### **AC WAVEFORMS**

For all waveforms,  $V_M = 1.5V$ .

The shaded areas indicate when the input is permitted to change for predictable output performance.

Waveform 1. Propagation Delay, Clock Input to Output, Clock Pulse Width, and Maximum Clock Frequency

Waveform 2. Master Reset Pulse Width, Master Reset to Output Delay, and Master Reset to Clock Recovery Time

Waveform 3. Setup and Hold Times

#### **TIMING DIAGRAM**

6 April 4, 1989

## 4-bit bidirectional universal shift register

74F194

#### **TEST CIRCUIT AND WAVEFORMS**

April 4, 1989 7

# 4-bit bidirectional universal shift register

74F194

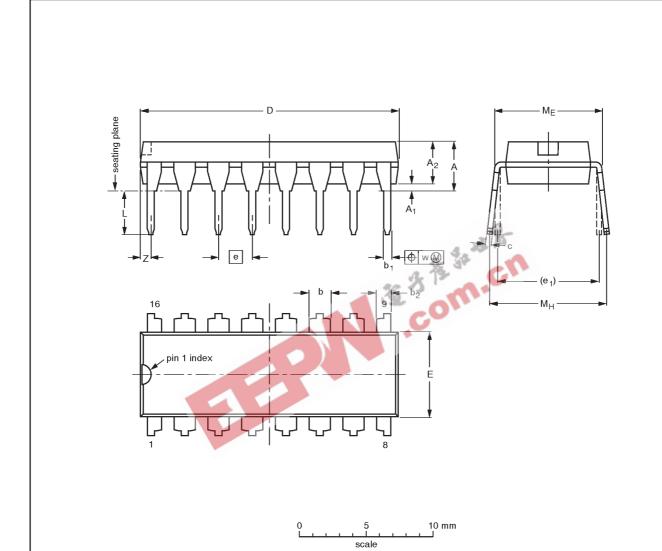

### DIP16: plastic dual in-line package; 16 leads (300 mil)

SOT38-4

#### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | b <sub>2</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | ME           | M <sub>H</sub> | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|--------------|----------------|-------|--------------------------|

| mm     | 4.2       | 0.51                   | 3.2                    | 1.73<br>1.30   | 0.53<br>0.38   | 1.25<br>0.85   | 0.36<br>0.23   | 19.50<br>18.55   | 6.48<br>6.20     | 2.54 | 7.62           | 3.60<br>3.05 | 8.25<br>7.80 | 10.0<br>8.3    | 0.254 | 0.76                     |

| inches | 0.17      | 0.020                  | 0.13                   | 0.068<br>0.051 | 0.021<br>0.015 | 0.049<br>0.033 | 0.014<br>0.009 | 0.77<br>0.73     | 0.26<br>0.24     | 0.10 | 0.30           | 0.14<br>0.12 | 0.32<br>0.31 | 0.39<br>0.33   | 0.01  | 0.030                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE |     | REFER | ENCES | EUROPEAN   | ISSUE DATE                      |

|---------|-----|-------|-------|------------|---------------------------------|

| VERSION | IEC | JEDEC | EIAJ  | PROJECTION | ISSUE DATE                      |

| SOT38-4 |     |       |       |            | <del>92-11-17</del><br>95-01-14 |

1989 Apr 04 8

# 4-bit bidirectional universal shift register

74F194

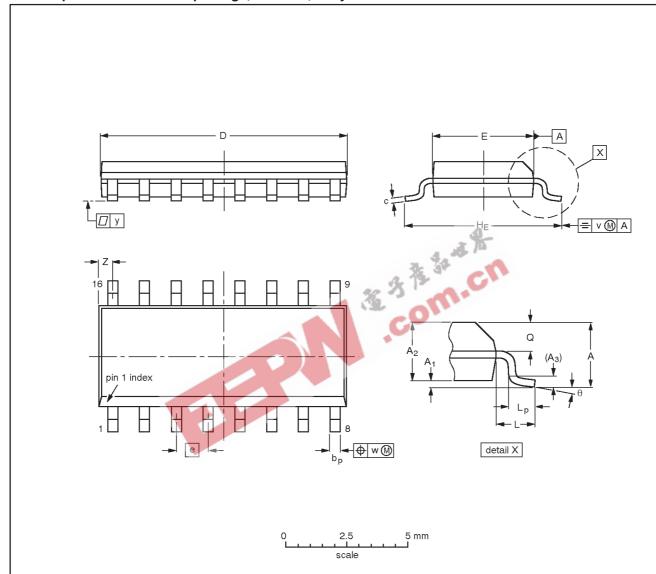

### SO16: plastic small outline package; 16 leads; body width 3.9 mm

SOT109-1

#### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | c                | D <sup>(1)</sup> | E <sup>(1)</sup> | е     | HE             | L     | Lp             | Q          | v    | w    | у     | Z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|----------------|--------------|------------------|------------------|------------------|-------|----------------|-------|----------------|------------|------|------|-------|------------------|----|

| mm     | 1.75      | 0.25<br>0.10   | 1.45<br>1.25   | 0.25           | 0.49<br>0.36 | 0.25<br>0.19     | 10.0<br>9.8      | 4.0<br>3.8       | 1.27  | 6.2<br>5.8     | 1.05  | 1.0<br>0.4     | 0.7<br>0.6 | 0.25 | 0.25 | 0.1   | 0.7<br>0.3       | 8° |

| inches | 0.069     | 0.010<br>0.004 | 0.057<br>0.049 | 0.01           |              | 0.0100<br>0.0075 | 0.39<br>0.38     | 0.16<br>0.15     | 0.050 | 0.244<br>0.228 | 0.041 | 0.039<br>0.016 |            | 0.01 | 0.01 | 0.004 | 0.028<br>0.012   | 0° |

#### Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

| OUTLINE  | REFERENCES |          |      |  | EUROPEAN   | ISSUE DATE                      |

|----------|------------|----------|------|--|------------|---------------------------------|

| VERSION  | IEC        | JEDEC    | EIAJ |  | PROJECTION | ISSUE DATE                      |

| SOT109-1 | 076E07S    | MS-012AC |      |  |            | <del>95-01-23</del><br>97-05-22 |

1989 Apr 04 9

### 4-bit bidirectional universal shift register

74F194

#### Data sheet status

| Data sheet status         | Product status | Definition [1]                                                                                                                                                                                                                                             |

|---------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development    | This data sheet contains the design target or goal specifications for product development. Specification may change in any manner without notice.                                                                                                          |

| Preliminary specification | Qualification  | This data sheet contains preliminary data, and supplementary data will be published at a later date.  Philips Semiconductors reserves the right to make chages at any time without notice in order to improve design and supply the best possible product. |

| Product specification     | Production     | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                       |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 1998 All rights reserved. Printed in U.S.A.

print code Date of release: 10-98

Document order number: 9397-750-05095

Let's make things better.