# CD54AC193/3A CD54ACT193/3A

**Presettable Synchronous** 4-Bit Binary Up/Down Counter with Reset

June 1997

## Description

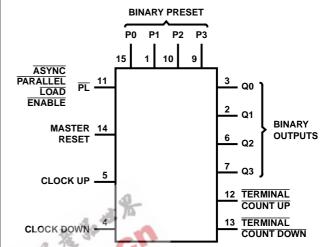

The CD54AC193/3A and CD54ACT193/3A are up/down binary counters with separate up/down clocks. These devices utilize the Harris Advanced CMOS Logic technology. Presetting the counter to the number on preset data inputs (P0-P3) is accomplished by a LOW asynchronous parallel load input (PL). The counter is incremented on the LOW-to-HIGH transition of the Clock-Up input (and a HIGH level on the Clock-Down input) and decremented on the LOW-to-HIGH transition of the Clock-Down input (and a HIGH level on the Clock-Up input). A HIGH level on the Reset input overrides any other input to clear the counter to its zero state. The TCU (carry) output goes LOW half a clock period before the zero count is reached and returns to a HIGH level at the zero count. The TCD (borrow) output in the count down mode likewise goes LOW half a clock period before the maximum count (15 counts) and returns to HIGH at the maximum count. Cascading is effected by connecting the TCU and TCD outputs of a less significant counter to the Clock-Up and Clock-Down inputs, respectively, of the next most significant counter.

COMPLETE DATA SHEET

**COMING SOON!**

The CD54AC193/3A and CD54ACT193/3A are supplied in 16-lead dual-in-line ceramic packages (F suffix).s

### Functional Diagram

#### ACT INPUT LOAD TABLE

| INPUT                   | UNIT LOAD (NOTE 1) |  |

|-------------------------|--------------------|--|

| P0 - P3, <del>P</del> L | 0.75               |  |

| MR, CPU, CPD            | 0.85               |  |

#### NOTE

1. Unit load is  $\Delta I_{CC}$  limit specified in DC Electrical Specifications Table, e.g., 2.4mA Max at +25°C.

#### **Absolute Maximum Ratings**

| DC Supply Voltage, V <sub>CC</sub> 0.5V to +6V                         |

|------------------------------------------------------------------------|

| DC Input Diode Current, I <sub>IK</sub>                                |

| For $V_I < -0.5V$ or $V_I > V_{CC} + 0.5V$                             |

| DC Output Diode Current, I <sub>OK</sub>                               |

| For $V_O < -0.5V$ or $V_O > V_{CC} + 0.5V$                             |

| DC Output Source or Sink Current, Per Output Pin, IO                   |

| For $V_O > -0.5V$ or $V_O < V_{CC} + 0.5V$                             |

| DC V <sub>CC</sub> or GND Current, I <sub>CC</sub> or I <sub>GND</sub> |

| For Up to 4 Outputs Per Device, Add ±25mA For Each                     |

| Additional Output±100mA                                                |

|                                                                        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Recommended Operating Conditions**

| Supply Voltage Range, V <sub>CC</sub>                       |   |

|-------------------------------------------------------------|---|

| Unless Otherwise Specified, All Voltages Referenced to GND  |   |

| T <sub>A</sub> = Full Package Temperature Range             |   |

| CD54AC Types                                                | / |

| CD54ACT Types                                               | / |

| DC Input or Output Voltage, V <sub>I</sub> , V <sub>O</sub> | ) |

| Operating Temperature, T <sub>A</sub> | 55°C to +125°C       |

|---------------------------------------|----------------------|

| Input Rise and Fall Slew Rate, dt/dv  |                      |

| at 1.5V to 3V (AC Types)              | . 0ns/V to 50ns/V $$ |

| at 3.6V to 5.5V (AC Types)            | . 0ns/V to 20ns/V $$ |

| at 4.5V to 5.5V (AC Types)            | . Ons/V to 10ns/V    |