COMPLETE DATA SHEET **COMING SOON!**

# CD54AC191/3A CD54ACT191/3A

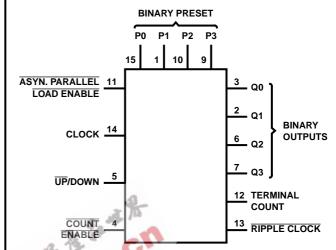

**Presettable Synchronous** 4-Bit Binary Up/Down Counters

June 1997

## Description

The CD54AC191/3A and CD54ACT191/3A are asynchronously presettable binary up/down synchronous counters that utilize the Harris Advanced CMOS Logic technology. Presetting the counter to the number on preset data inputs (P0-P3) is accomplished by setting LOW the asynchronous parallel load input (PL). Counting occurs when PL is HIGH. Count Enable ( $\overline{CE}$ ) is LOW, and the Up/Down ( $\overline{U}/D$ ) input is either LOW for up-counting or HIGH for down-counting. The counter is incremented or decremented synchronously with the LOW-to-HIGH transition of the clock.

When an overflow or underflow of the counter occurs, the Terminal Count (TC) output, which is LOW during counting, goes HIGH and remains HIGH for one clock cycle. This output can be used for look-ahead carry in high-speed cascading. The TC output also initiates the Ripple Clock (RC) output which, normally HIGH, goes LOW and remains LOW for the low-level portion of the clock pulse. These counters can be cascaded using the Ripple Count output.

The CD54AC191/3A and CD54ACT191/3A are supplied in 16-lead dual-in-line ceramic packages (F suffix).

# Functional Diagram

### **ACT INPUT LOAD TABLE**

| INPUT                                  | UNIT LOAD (NOTE 1) |

|----------------------------------------|--------------------|

| P0 - P3, <u>PL</u>                     | 0.75               |

| CL, $\overline{U}/D$ , $\overline{CE}$ | 0.85               |

1. Unit load is  $\Delta I_{\hbox{\footnotesize CC}}$  limit specified in DC Electrical Specifications Table, e.g., 2.4mA Max at +25°C.

#### **Absolute Maximum Ratings**

| DC Supply Voltage, V <sub>CC</sub> 0.5V to +6V                         | / |

|------------------------------------------------------------------------|---|

| DC Input Diode Current, I <sub>IK</sub>                                |   |

| For $V_1 < -0.5V$ or $V_1 > V_{CC} + 0.5V$                             | ١ |

| DC Output Diode Current, I <sub>OK</sub>                               |   |

| For $V_O < -0.5V$ or $V_O > V_{CC} + 0.5V$                             | ١ |

| DC Output Source or Sink Current, Per Output Pin, IO                   |   |

| For $V_O > -0.5V$ or $V_O < V_{CC} + 0.5V$                             | ١ |

| DC V <sub>CC</sub> or GND Current, I <sub>CC</sub> or I <sub>GND</sub> |   |

| For Up to 4 Outputs Per Device, Add ±25mA For Each                     |   |

| Additional Output                                                      | ١ |

|                                                                        |   |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### **Recommended Operating Conditions**

| Supply Voltage Range, V <sub>CC</sub>                      |

|------------------------------------------------------------|

| Unless Otherwise Specified, All Voltages Referenced to GND |

| T <sub>A</sub> = Full Package Temperature Range            |

| CD54AC Types                                               |

| CD54ACT Types                                              |

| DC Input or Output Voltage, $V_I, V_O$                     |

| Operating Temperature, T <sub>A</sub> | 55°C to +125°C  |

|---------------------------------------|-----------------|

| Input Rise and Fall Slew Rate, dt/dv  |                 |

| at 1.5V to 3V (AC Types)              | 0ns/V to 50ns/V |

| at 3.6V to 5.5V (AC Types)            | 0ns/V to 20ns/V |

| at 4.5V to 5.5V (AC Types)            | 0ns/V to 10ns/V |