# 68HC(7)05H12

General Release Specification Rev. 1.0

November, 1998

## **General Release Specification**

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

© Motorola, Inc., 1997

# **List of Sections**

| List of Sections                          |

|-------------------------------------------|

| Table of Contents                         |

| List of Figures                           |

| List of Tables                            |

| List of Tables                            |

| Memory 25                                 |

| CPU and Instruction Set                   |

| Interrupts59                              |

| Resets                                    |

| Operating Modes 75                        |

| Input/Output Ports                        |

| Core Timer                                |

| 16-Bit Timers                             |

| Serial Peripheral Interface (SPI)         |

| Serial Communications Interface (SCI) 125 |

| Analog to Digital Converter               |

| EEPROM                                    |

MC68HC(7)05H12 - Rev. 1.0

General Release Specification

## **List of Sections**

| Pulse Width Modulator (PWM) | 159 |

|-----------------------------|-----|

| EPROM                       | 167 |

| Electrical Characteristics  | 173 |

| Mechanical Specifications   | 183 |

| Index                       | 185 |

**MOTOROLA**

# **Section 1. General Description**

| 1.1    | Contents                           | . 17 |

|--------|------------------------------------|------|

| 1.2    | Introduction                       | .17  |

| 1.3    | Features                           | .18  |

| 1.4    | Mask Options                       | .20  |

| 1.5    | Pin Assignments                    | .20  |

| 1.6    | Functional Pin Description         | .21  |

| 1.6.1  | VDD and VSS                        | .21  |

| 1.6.2  | VDD and VSS                        | .21  |

| 1.6.3  | OSC1, OSC2                         | .21  |

| 1.6.4  | RESET                              | .21  |

| 1.6.5  | TRQ/VPP                            | .21  |

| 1.6.6  | PA0-PA7/Keyboard Interrupt         | . 22 |

| 1.6.7  | PB0-PB7/ECLK, MISO, MOSI, SCK      | .22  |

| 1.6.8  | PC0-PC7/TCAP0-3, TCMP0-1, RDI, TDO | .22  |

| 1.6.9  | PD0-PD3/AN0-AN3                    | . 23 |

| 1.6.10 | ) VREFH                            | .23  |

| 1.6.11 | PE0–PE7                            | .23  |

| 1.6.12 | PF0-PF3                            | .23  |

| 1.6.13 | PVDD1, PVSS1, PVDD2, PVSS2         | . 23 |

|        | Section 2. Memory                  |      |

| 2.1    | Contents                           | 25   |

|        |                                    |      |

| 2.2    | Introduction                       |      |

| 2.3    | Registers                          | . 26 |

| 2.3.1  | System Control Register            | . 34 |

| 2.4    | RAM                                | .35  |

| 2.5    | ROM                                | .35  |

|        |                                    |      |

| 2.6   | Monitor ROM                           | .35        |

|-------|---------------------------------------|------------|

| 2.7   | User EPROM (for the 705 version only) | .35        |

| 2.8   | EEPROM                                | .35        |

|       |                                       |            |

|       | Section 3. CPU and Instruction Set    |            |

| 3.1   | Contents                              | .37        |

| 3.2   | Introduction                          | .38        |

| 3.3   | CPU Registers                         | .38        |

| 3.3.1 | Accumulator                           |            |

| 3.3.2 | Index Register                        |            |

| 3.3.3 | Stack Pointer                         |            |

| 3.3.4 | Program Counter                       | .40        |

| 3.3.5 | Condition Code Register               | .40        |

| 3.4   | Program Counter                       | .42        |

| 3.5   | Instruction Set Overview              |            |

| 3.6   | Addressing Modes                      | .42        |

| 3.6.1 | Inherent                              |            |

| 3.6.2 | Immediate                             | .43        |

| 3.6.3 | Direct                                | .43        |

| 3.6.4 | Extended                              | .43        |

| 3.6.5 | Indexed, No Offset                    | .44        |

| 3.6.6 | Indexed, 8-Bit Offset                 |            |

| 3.6.7 | Indexed,16-Bit Offset                 |            |

| 3.6.8 | Relative                              | .45        |

| 3.7   | Instruction Types                     | .45        |

| 3.7.1 | Register/Memory Instructions          | .46        |

| 3.7.2 | Read-Modify-Write Instructions        | .47        |

| 3.7.3 | Jump/Branch Instructions              |            |

| 3.7.4 | Bit Manipulation Instructions         |            |

| 3.7.5 | Control Instructions                  | .51        |

| 3.8   | Instruction Set Summary               | .52        |

|       | Section 4. Interrupts                 |            |

| 11    | Contents                              | <b>E</b> 0 |

| 4.1   | Contents                              | .59        |

|       |                                       |            |

General Release Specification

MC68HC(7)05H12 — Rev. 1.0

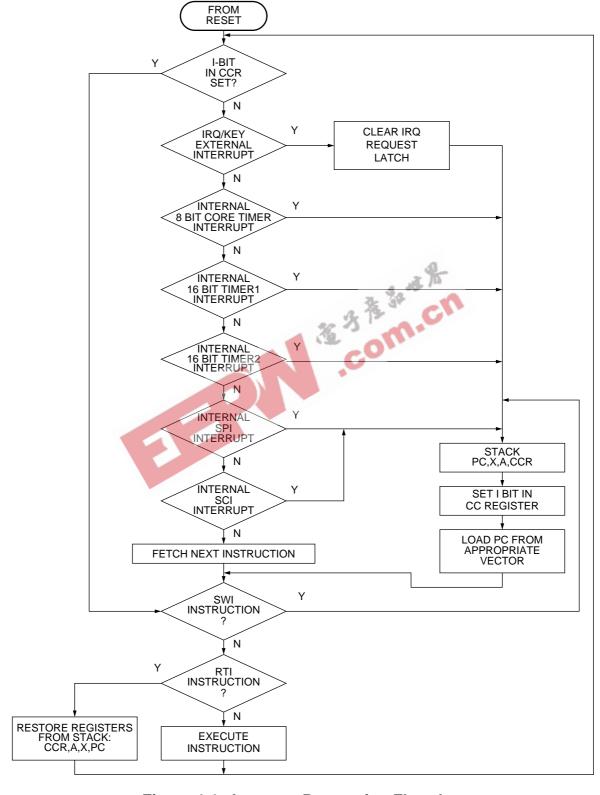

| 4.2            | Introduction                                               |

|----------------|------------------------------------------------------------|

| 4.3            | CPU Interrupt Processing60                                 |

| 4.4            | Reset Interrupt Sequence                                   |

| 4.5            | Software Interrupt (SWI)63                                 |

| 4.6            | Hardware Interrupts                                        |

| 4.7            | External Interrupt (IRQ/Keyboard)                          |

| 4.8            | 8-Bit Timer Interrupt                                      |

| 4.9            | 16-Bit Timer1 Interrupt                                    |

| 4.10           | 16-Bit Timer2 Interrupt                                    |

| 4.11           | SCI Interrupt                                              |

| 4.12           | SPI Interrupt                                              |

| 4.13           | WAIT Mode65                                                |

|                | Section 5. Resets                                          |

| 5.1            | Contents                                                   |

| 5.2            | Introduction                                               |

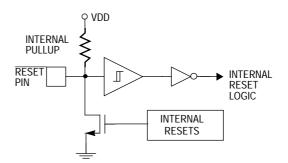

| 5.3            | External Reset (RESET)67                                   |

| 5.4            | Internal Resets                                            |

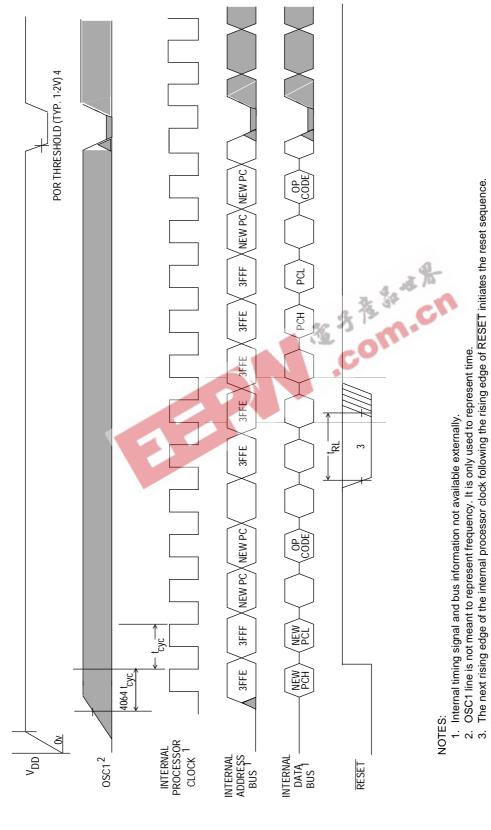

| 5.5            | Power-On Reset (POR)                                       |

| 5.6            | Computer Operating Properly Reset (COPR)70                 |

| 5.6.1          | Resetting the COP                                          |

| 5.6.2<br>5.6.3 | COP During WAIT Mode71 COP Watchdog Timer Considerations71 |

| 5.6.4          | COP Register                                               |

| 5.7            | Illegal Address Reset                                      |

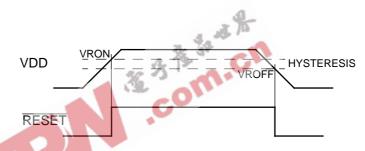

| 5.8            | Low Voltage Reset (LVR)72                                  |

| 5.8.1          | LVR Operation in WAIT73                                    |

| 6.1            | Contents                                                   |

# **Section 6. Operating Modes**

| 6.2            | Introduction                                         |

|----------------|------------------------------------------------------|

| 6.3            | User Mode                                            |

| 6.4            | Monitor Mode                                         |

| 6.5            | Low Power Modes                                      |

| 6.5.1          | WAIT Mode                                            |

| 6.5.2          | Data Retention Mode78                                |

| 6.5.3          | Slow Mode                                            |

|                | Section 7 Input/Output Ports                         |

|                | Section 7. Input/Output Ports                        |

| 7.1            | Contents                                             |

| 7.2            | Introduction                                         |

| 7.3            | Port A                                               |

| 7.3.1          | Port A Keyboard Interrupt80                          |

| 7.3.2          | Port A Interrupt Edge Register                       |

| 7.3.3          | Port A Interrupt Control Register81                  |

| 7.3.4          | Port A Interrupt Status Register                     |

| 7.4            | Port B                                               |

| 7.5            | Port C                                               |

| 7.6            | Port D                                               |

| 7.7            | Port E and Port F (Power Drivers)                    |

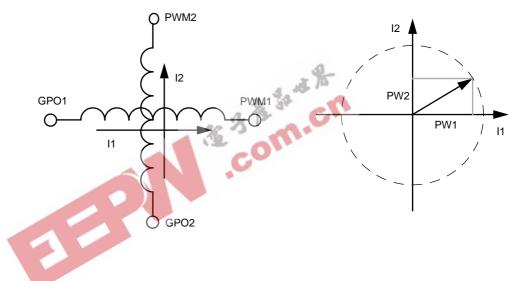

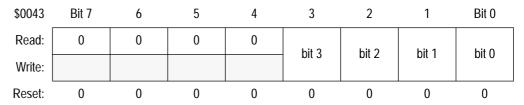

| 7.7.1          | Power Drivers for 360∞Air Core Driven Instruments 85 |

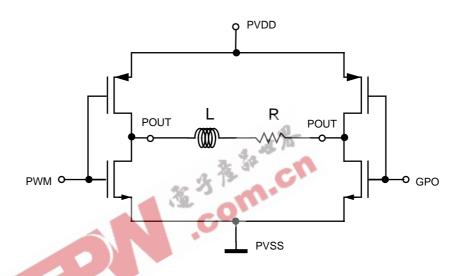

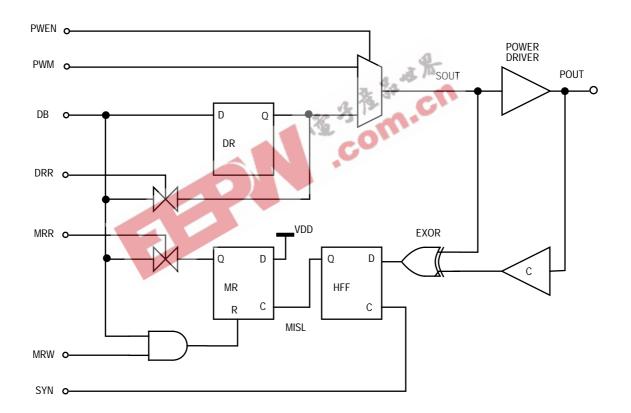

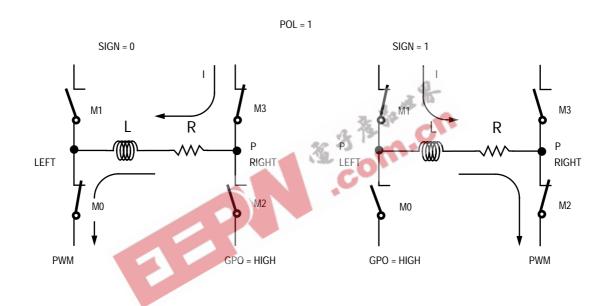

| 7.7.2          | H-Bridge Driver                                      |

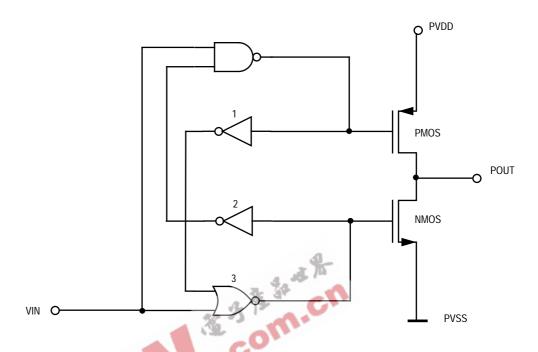

| 7.7.3          | Power Driver Circuit                                 |

| 7.7.4          | Short Circuit Detection                              |

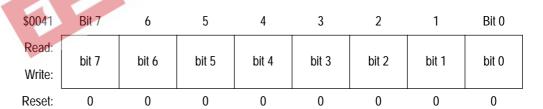

| 7.7.5          | Port E and Port F Mismatch Registers                 |

| 7.7.6<br>7.7.7 | Driver States                                        |

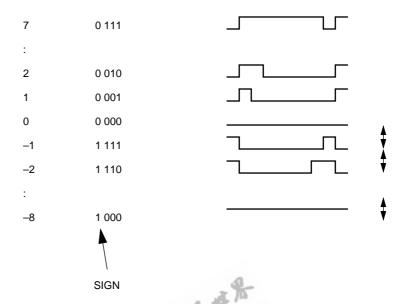

| 7.7.8          | H-Bridge Control with the PWM94                      |

| 7.8            | Port E and Port F During WAIT Mode95                 |

| 7.9            | Input/Output Programming                             |

| 8.1            | Contents                                             |

| J. 1           | Outlone                                              |

General Release Specification

MC68HC(7)05H12 - Rev. 1.0

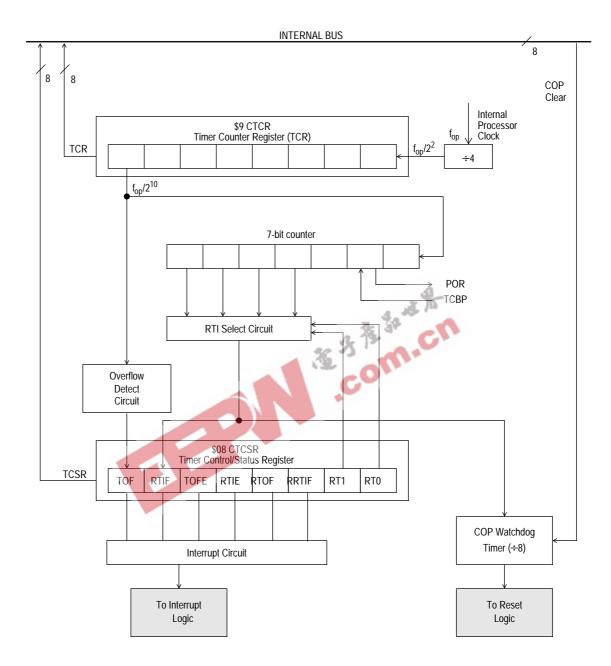

## **Section 8. Core Timer**

| 8.2    | Introduction                                         |

|--------|------------------------------------------------------|

| 8.3    | Registers99                                          |

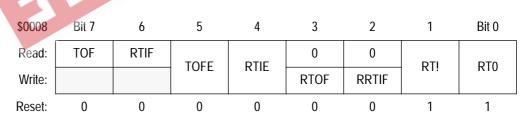

| 8.3.1  | Core Timer Status and Control Register (CTSCR)       |

| 8.3.2  | Computer Operating Properly (COP) Watchdog Reset 101 |

| 8.3.3  | Core Timer Counter Register (CTCR)101                |

| 8.4    | Core Timer During WAIT102                            |

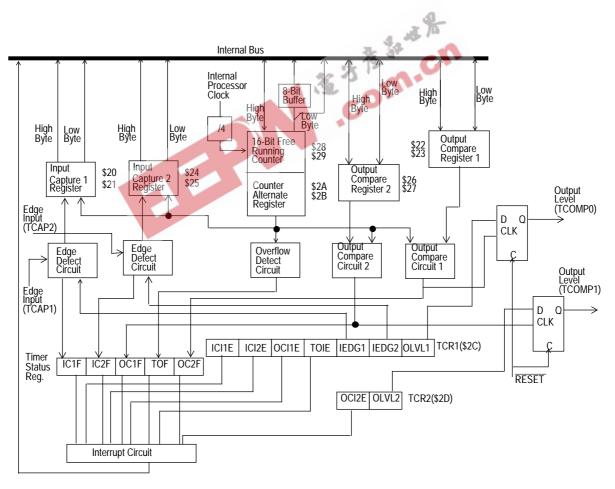

|        | Section 9. 16-Bit Timers                             |

| 9.1    | Contents                                             |

| 9.2    | Introduction                                         |

| 9.3    | Registers105                                         |

| 9.3.1  | Counter                                              |

| 9.3.1  | Output Compare Registers                             |

| 9.3.3  | Output Compare Register 1                            |

| 9.3.4  | Output Compare Register 2                            |

| 9.3.5  | Input Capture Registers                              |

| 9.3.6  | Input Capture Register 1108                          |

| 9.3.7  | Input Capture Register 2109                          |

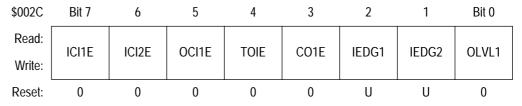

| 9.3.8  | Timer Control Register 1                             |

| 9.3.9  | Timer Control Register 2                             |

| 9.3.10 | Timer Status Register                                |

| 9.4    | Timer During WAIT Mode112                            |

|        | Section 10. Serial Peripheral Interface (SPI)        |

| 10.1   | Contents                                             |

| 10.2   | Introduction                                         |

| 10.3   | SPI Signal Description                               |

| 10.3.1 |                                                      |

| 10.3.2 |                                                      |

| 10.3.3 | · · · · · · · · · · · · · · · · · · ·                |

| 10.4   | SPI Functional Description                           |

| 10.5   | Registers                                            |

| 10.5.1 | _                                                    |

| <ul><li>10.5.2 SPI Status Register (SPSR)</li></ul>                                                            |      |

|----------------------------------------------------------------------------------------------------------------|------|

| 10.6 SPI During WAIT Mode                                                                                      |      |

|                                                                                                                |      |

| Section 11. Serial Communications Interface (S                                                                 | SCI) |

| 11.1 Contents                                                                                                  | 125  |

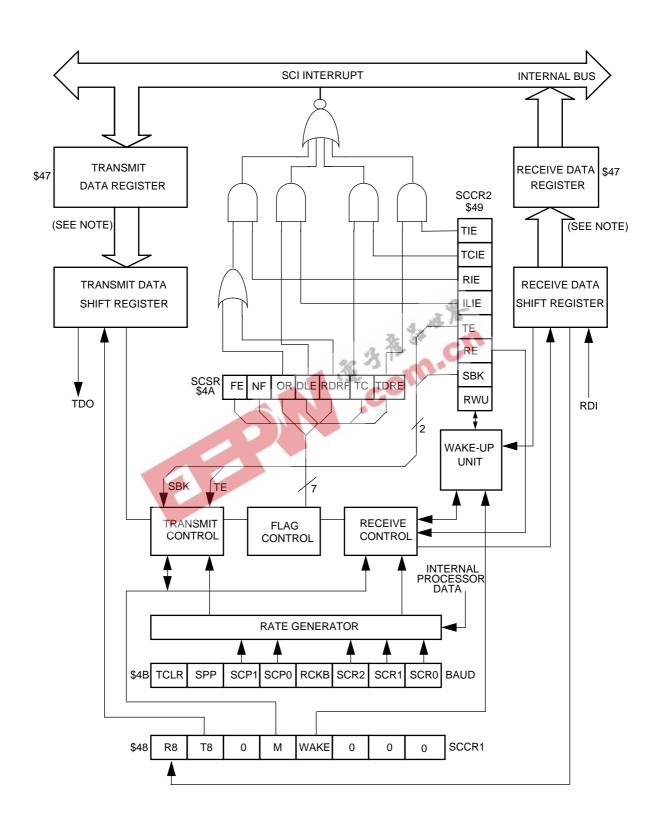

| 11.2 Introduction                                                                                              | 125  |

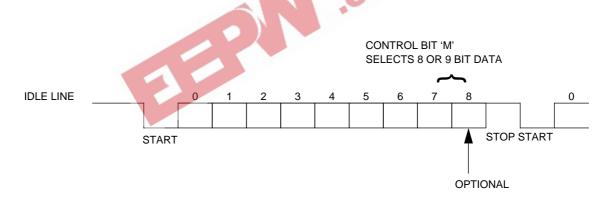

| 11.3 Data Format                                                                                               | 130  |

| 11.4 Receiver Wake-up Operation                                                                                |      |

| <ul><li>11.4.1 Idle Line Wake-up</li></ul>                                                                     |      |

| 11.5 Possive Data (PDI)                                                                                        | 122  |

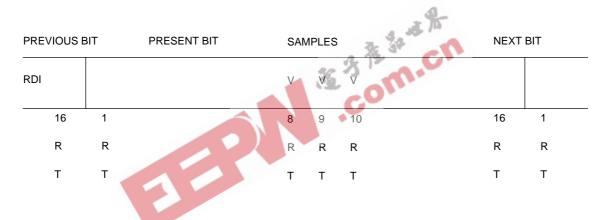

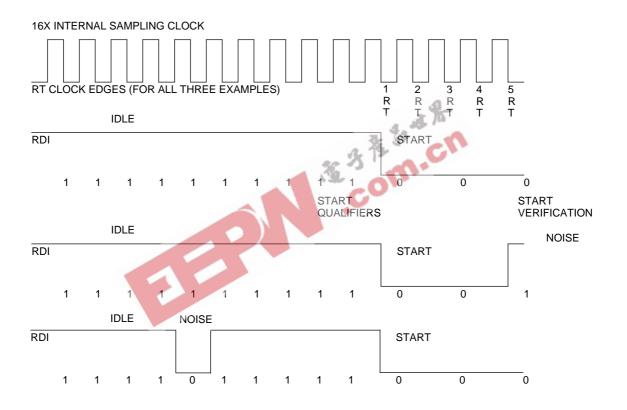

| 11.6 Start Bit Detection                                                                                       | 132  |

| 11.6 Start Bit Detection.  11.7 Transmit Data (TDO)                                                            | 135  |

| 11.8 Registers                                                                                                 | 135  |

| 11.8.1 Serial Communications Data Register (SCDAT)                                                             |      |

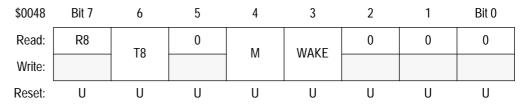

| 11.8.2 Serial Communications Control Register 1 (SCCR1)                                                        |      |

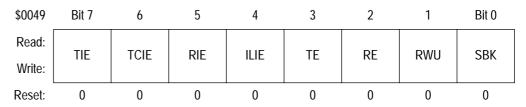

| 11.8.3 Serial Communications Control Register 2 (SCCR2)                                                        |      |

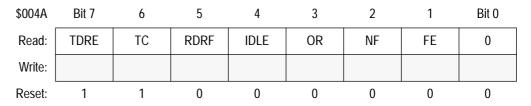

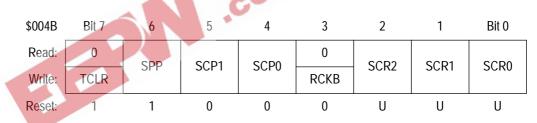

| <ul><li>11.8.4 Serial Communications Status Register (SCSR)</li><li>11.8.5 Baud Rate Register (BAUD)</li></ul> |      |

|                                                                                                                |      |

| 11.9 SCI During WAIT Mode                                                                                      | 142  |

| Section 12. Analog to Digital Converter                                                                        |      |

| 12.1 Contents                                                                                                  | 143  |

| 12.2 Introduction                                                                                              | 144  |

| 12.3 A/D Principle                                                                                             | 144  |

| 12.4 A/D Operation                                                                                             | 145  |

| 12.5 Internal and Master Oscillator                                                                            | 145  |

| 12.6 A/D Registers                                                                                             | 146  |

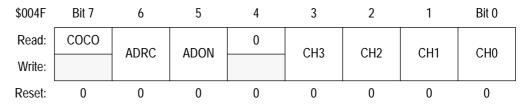

| 12.6.1 A/D Status and Control Register (ADSCR)                                                                 | 146  |

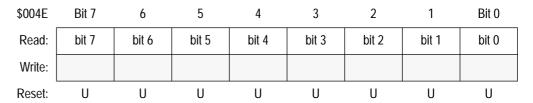

| 12.6.2 A/D Data Register                                                                                       | 148  |

| 12.7 A/D During WAIT Mode                                                                                      | 148  |

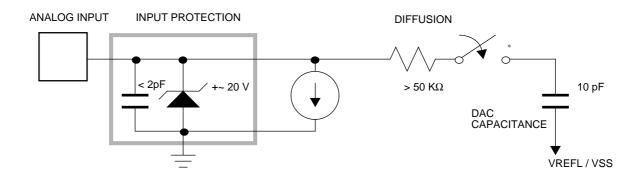

| 12.8 Analog Input                                                                                              | 148  |

|                                                                                                                |      |

| 12.9 Conversion Accuracy Definitions                  | 50             |

|-------------------------------------------------------|----------------|

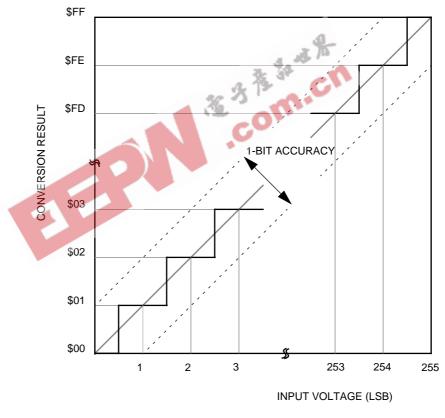

| 12.9.1 Transfer Curve15                               | 50             |

| 12.9.2 Monotonicity                                   | 50             |

| 12.9.3 Quantization Error                             |                |

| 12.9.4 Offset Error                                   |                |

| 12.9.5 Gain Scale Error                               |                |

| 12.9.6 Differential Linearity Error                   |                |

| 12.9.7 Integral Linearity Error                       |                |

| 12.9.8 Total Unadjusted Error                         | 51             |

|                                                       |                |

| Section 13. EEPROM                                    |                |

| 13.1 Contents                                         |                |

| 13.2 Introduction                                     | 53             |

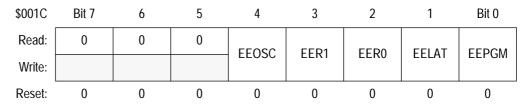

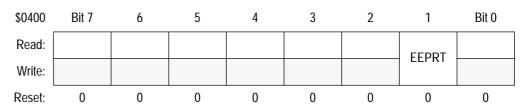

| 13.3 EEPROM Control Register (EEPCR)                  | 54             |

| 13.4 EEPROM Options Register (EEOPR)15                | 55             |

| 13.5 EEPROM Read, Erase and Programming Procedures 15 | 56             |

| 13.5.1 Read Procedure                                 |                |

| 13.5.2 Erase Procedure                                | 56             |

| 13.5.3 Programming Procedure                          | 57             |

| 13.6 Operation in WAIT                                | 57             |

|                                                       |                |

| Section 14. Pulse Width Modulator (PWM)               |                |

| 14.1 Contents                                         | 59             |

| 14.2 Introduction                                     | 59             |

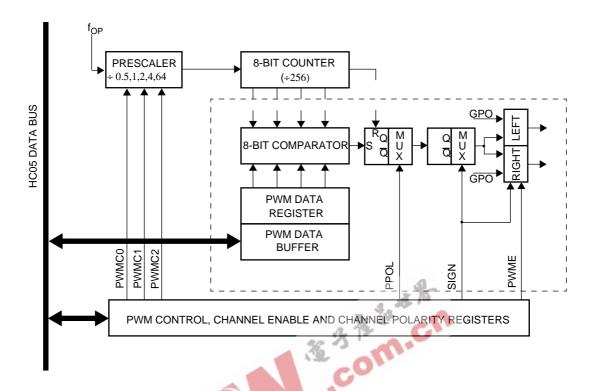

| 14.3 Functional Description                           | 60             |

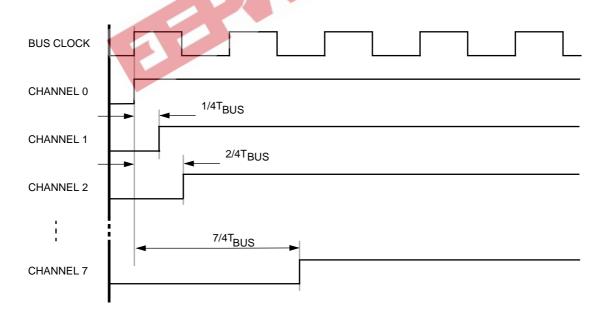

| 14.3.1 PWM Channel Microshifting                      |                |

| 14.4 Registers                                        | 62             |

| 14.4.1 PWM Data Registers                             |                |

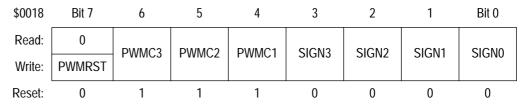

| 14.4.2 PWM Control Register                           |                |

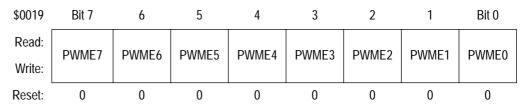

| 14.4.3 PWM Channel Enable Register                    | 35             |

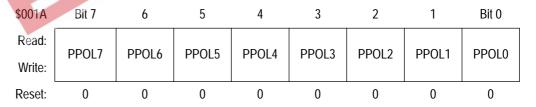

| 14.4.4 PWM Channel Polarity Register                  | <del>3</del> 5 |

| 14.5 PWM During WAIT Mode                             | 66             |

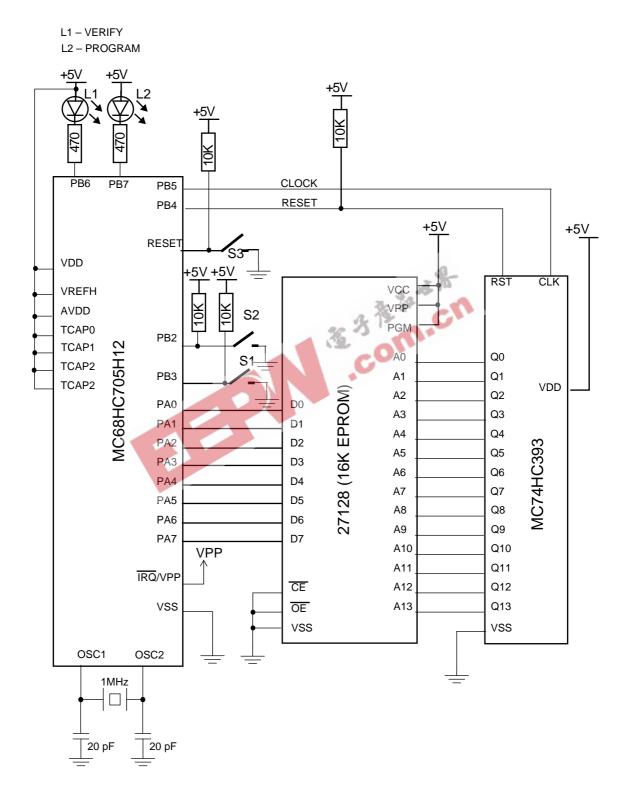

## **Section 15. EPROM**

| 15.1   | Contents                                                |

|--------|---------------------------------------------------------|

| 15.2   | Introduction                                            |

| 15.3   | EPROM Bootloader167                                     |

| 15.3.1 | Bootloader Functions                                    |

| 15.4   | EPROM Programming                                       |

| 15.4.1 | 3 3 3 ( )                                               |

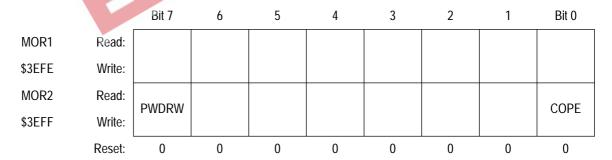

| 15.5   | Mask Option Register (MOR)                              |

|        | Section 16. Electrical Characteristics                  |

| 16.1   |                                                         |

| 16.2   | Movimum Patings 174                                     |

|        | Contents173Maximum Ratings174Thermal Characteristics175 |

| 16.3   | Thermal Characteristics . T                             |

| 16.4   | Power Considerations                                    |

| 16.5   | DC Electrical Characteristics                           |

| 16.6   | Control Timing                                          |

| 16.7   | A/D Converter Characteristics                           |

| 16.8   | EEPROM Characteristics                                  |

| 16.9   | EPROM Characteristics                                   |

| 16.10  | Power Driver Characteristics                            |

| 16.11  | Power-on Reset/Low Voltage Reset Characteristics 181    |

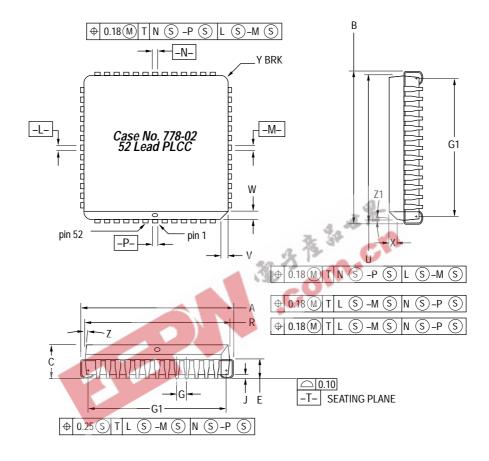

|        | Section 17. Mechanical Specifications                   |

| 47.4   |                                                         |

| 17.1   | Contents                                                |

| 17.2   | Pin Assignments183                                      |

| 17.3   | Package Dimensions                                      |

|        |                                                         |

Index

# **List of Figures**

| Figure | Title                                       | Page |

|--------|---------------------------------------------|------|

| 1-1    | MC68HC(7)05H12 Block Diagram                | 19   |

| 1-2    | MC68HC(7)05H12 Pin Assignments              |      |

|        | (52-pin PLCC package)                       |      |

| 2-1    | MC68HC(7)05H12 Memory Map                   | 26   |

| 2-2    | I/O Register Summary                        |      |

| 2-3    | I/O Registers \$0000–\$000F                 | 29   |

| 2-4    | I/O Registers \$0010–\$001F                 | 30   |

| 2-5    | I/O Registers \$0020–\$002F                 |      |

| 2-6    | I/O Registers \$0030-\$003F                 | 32   |

| 2-7    | I/O Registers \$0040–\$004F                 | 33   |

| 2-8    | System Control Register (SYSCR)             | 34   |

| 3-1    | Programming Model                           | 38   |

| 3-2    | Accumulator                                 | 39   |

| 3-3    | Index Register                              | 39   |

| 3-4    | Stack Pointer                               | 39   |

| 3-5    | Program Counter                             | 40   |

| 3-6    | Condition Code Register                     | 40   |

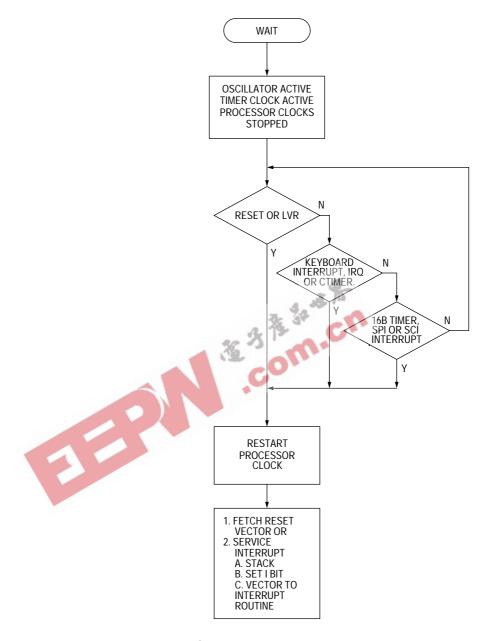

| 4-1    | Interrupt Processing Flowchart              |      |

| 5-1    | Internal Resets                             |      |

| 5-2    | RESET and POR Timing Diagram                | 69   |

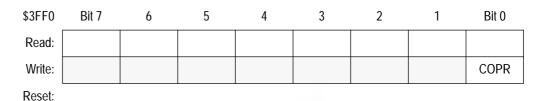

| 5-3    | COP Watchdog Timer Location Register (COPR) |      |

| 5-4    | Low Voltage Reset                           | 73   |

| 6-1    | WAIT Flowchart                              | 77   |

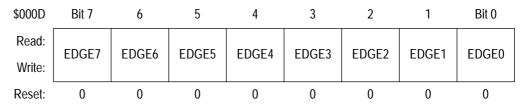

| 7-1    | Port A Interrupt Edge Register (PAIED)      | 81   |

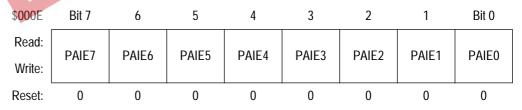

| 7-2    | Port A Interrupt Control Register (PAICR)   | 81   |

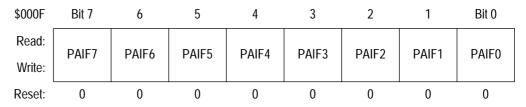

| 7-3    | Port A Interrupt Status Register (PAISR)    | 82   |

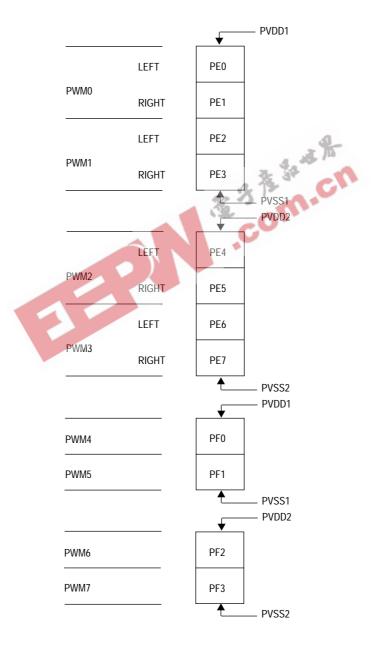

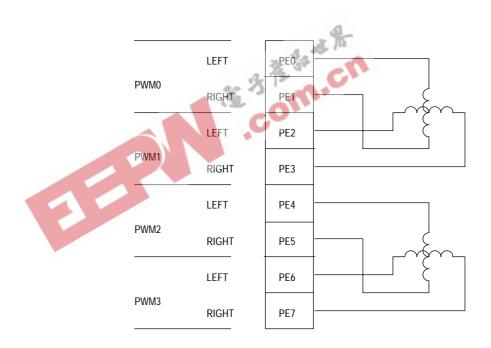

| 7-4    | Port E and Port F (Power Drivers)           | 84   |

| 7-5    | Driving Cross Coupled Coils                 | 85   |

11

# List of Figures

| 7-6  | H-Bridge Driver Circuit                                    | 86   |

|------|------------------------------------------------------------|------|

| 7-7  | Power Driver Circuit                                       | 87   |

| 7-8  | Short Circuit Detection Circuitry                          | 88   |

| 7-9  | Port E Mismatch Register (PEMISM)                          | 89   |

| 7-10 | Port F Mismatch Register (PFMISM)                          | 90   |

| 7-11 | H-Bridge States                                            | 91   |

| 7-12 | Port E Configuration for two 360° instruments              | 92   |

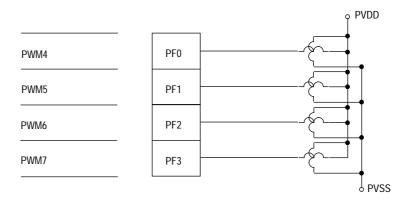

| 7-13 | Port F Configuration for four 90° instruments (version 1). | 93   |

| 7-14 | Port F Configuration for four 90° instruments (version 2). | 93   |

| 7-15 | H-Bridge Control with PWM                                  | 94   |

| 7-16 | Correspondence between Data and PWM Values                 | 95   |

| 7-17 | Port I/O Circuitry                                         | 96   |

| 8-1  | Core Timer Block Diagram                                   | 98   |

| 8-2  | Core Timer Status and Control Register (CTSCR)             | 99   |

| 8-3  | Core Timer Counter Register (CTCR)                         | .102 |

| 9-1  | Timer Block Diagram (Timer1)                               | .104 |

| 9-2  | 16-Bit Timer Register Addresses (Timer1)                   | .105 |

| 9-3  | Timer Control Register 1 (TCR1)                            | .110 |

| 9-4  | Timer Control Register 2 (TCR2)                            | .112 |

| 9-5  | Timer Status Register (TSR)                                | .113 |

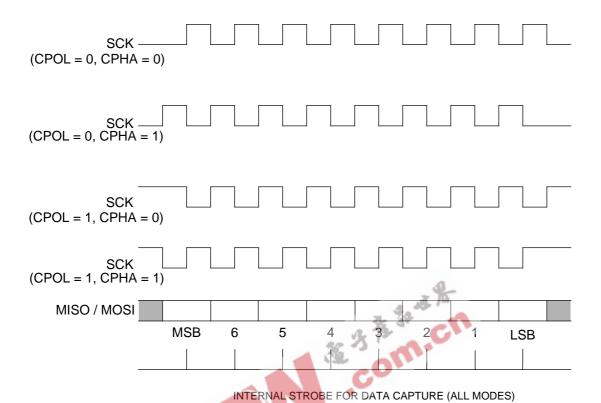

| 10-1 | Data Clock Timing Diagram                                  | .118 |

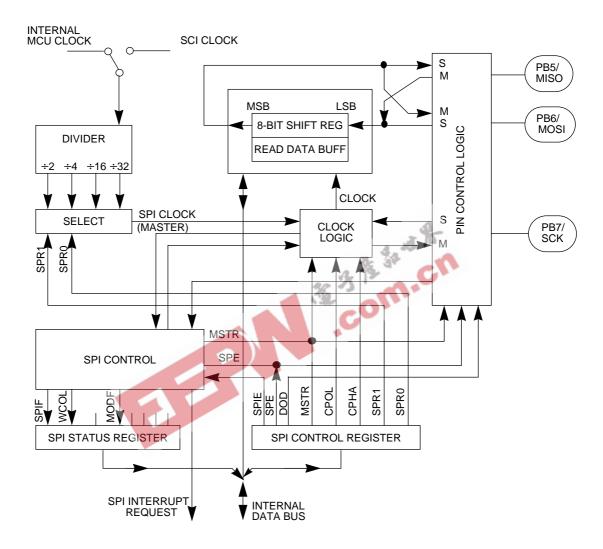

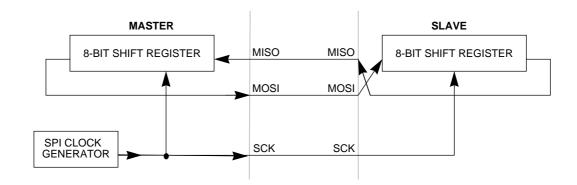

| 10-2 | Serial Peripheral Block Diagram                            | .119 |

| 10-3 | Serial Peripheral Interface Master-Slave Interconnection   | .120 |

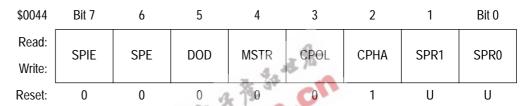

| 10-4 | SPI Control Register (SPCR)                                | .121 |

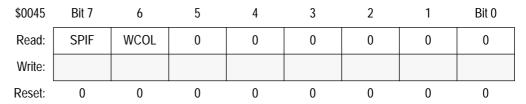

| 10-5 | SPI Status Register (SPSR)                                 | .123 |

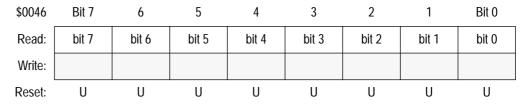

| 10-6 | SPI Data I/O Register (SPDAT)                              | .124 |

| 11-1 | Serial Communications Interface Block Diagram              | .128 |

| 11-2 | Data Format                                                |      |

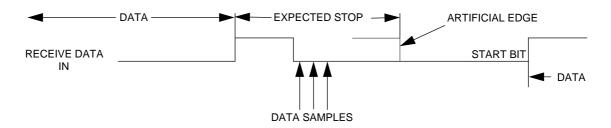

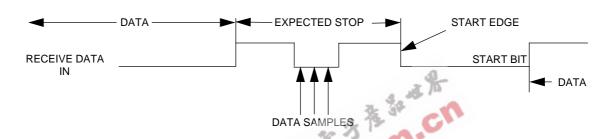

| 11-3 | Sampling Technique Used On All Bits                        |      |

| 11-4 | Examples of Start Bit Sampling Techniques                  |      |

| 11-5 | SCI Artificial Start Following a Framing Error             |      |

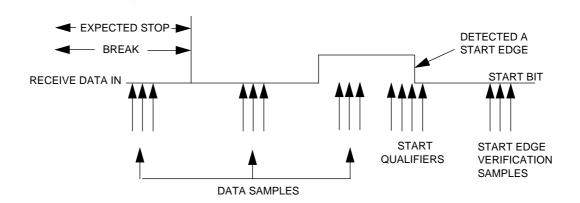

| 11-6 | SCI Start Bit Following a Break                            |      |

| 11-7 | SCI Data Register (SCDAT)                                  |      |

| 11-8 | SCI Control Register 1 (SCCR1)                             |      |

| 11-9 | SCI Control Register 2 (SCCR2)                             | .137 |

| 11-10 | SCI Status Register (SCSR)                     |

|-------|------------------------------------------------|

| 11-11 | SCI Baud Rate Register (BAUD)                  |

| 12-1  | A/D Status and Control Register (ADSCR)146     |

| 12-2  | A/D Data Register (ADDR)148                    |

| 12-3  | Electrical Model of an A/D Input Pin149        |

| 12-4  | Transfer Curve of an Ideal 8-Bit A/D Converter |

| 13-1  | EEPROM Control Register (EEPCR)                |

| 13-2  | EEPROM Options Register (EEOPR)155             |

| 14-1  | PWM Block Diagram (one channel)                |

| 14-2  | PWM Microshifts                                |

| 14-3  | PWM Data Registers (PWM0–7)                    |

| 14-4  | PWM Control Register (PWMCTL)164               |

| 14-5  | PWM Channel Enable Register (PWMEN)165         |

| 14-6  | PWM Channel Polarity Register (PWMPOL)         |

| 15-1  | MC68HC705H12 Programming Circuit               |

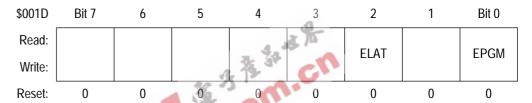

| 15-2  | EPROM Programming Register (EPROG)170          |

| 15-3  | Mask Options Registers (MOR1 and MOR2)171      |

| 17-1  | 52-Pin PLCC Pin Assignments183                 |

| 17-2  | 52-Pin PLCC Package Dimensions                 |

13

# General Release Specification — MC68HC(7)05H12

# **List of Tables**

| Table | Title                            | Page |

|-------|----------------------------------|------|

| 3-1   | Register/Memory Instructions     | 46   |

| 3-2   | Read-Modify-Write Instructions   | 47   |

| 3-3   | Jump and Branch Instructions     | 49   |

| 3-4   | Bit Manipulation Instructions    | 50   |

| 3-5   | Control Instructions             | 51   |

| 3-6   | Instruction Set Summary          | 52   |

| 3-7   | Opcode Map                       |      |

| 4-1   | Reset/Interrupt Vector Addresses | 61   |

| 6-1   | Operating Mode Entry Conditions  |      |

| 7-1   | I/O Pin Functions                |      |

| 8-1   | RTI Rates                        | 100  |

| 8-2   | Minimum COP Reset Times          | 101  |

| 10-1  | SPI Clock Rate Selection         | 122  |

| 11-1  | First Prescaler Stage            | 141  |

| 11-2  | Second Prescaler Stage           | 141  |

| 12-1  | A/D Clock Selection              | 147  |

| 12-2  | A/D Channel Assignments          | 147  |

| 13-1  | Erase Mode Select                | 154  |

| 14-1  | PWM Clock Rate                   | 164  |

| 15-1  | Bootloader Functions             | 168  |

# Section 1. General Description

## 1.1 Contents

| 1.2    | Introduction                       |

|--------|------------------------------------|

| 1.3    | Features                           |

| 1.4    | Mask Options                       |

| 1.5    | Pin Assignments20                  |

| 1.6    | Functional Pin Description         |

| 1.6.1  | VDD and VSS                        |

| 1.6.2  | AVDD21                             |

| 1.6.3  | OSC1, OSC221                       |

| 1.6.4  | RESET21                            |

| 1.6.5  | IRQ/VPP                            |

| 1.6.6  | PA0-PA7/Keyboard Interrupt         |

| 1.6.7  | PB0-PB7/ECLK, MISO, MOSI, SCK22    |

| 1.6.8  | PC0-PC7/TCAP0-3, TCMP0-1, RDI, TDO |

| 1.6.9  | PD0-PD3/AN0-AN323                  |

| 1.6.10 | VREFH                              |

| 1.6.11 | PE0-PE7                            |

| 1.6.12 | PF0-PF3                            |

| 1.6.13 | PVDD1, PVSS1, PVDD2, PVSS2         |

|        |                                    |

## 1.2 Introduction

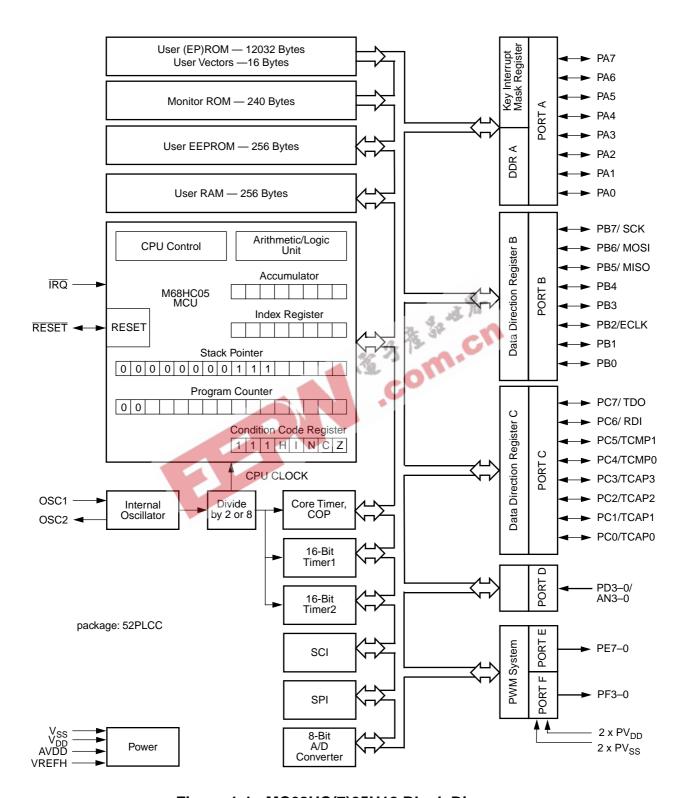

The MC68HC(7)05H12 HCMOS microcomputer is a member of the M68HC05 family. This 8 bit microcomputer unit (MCU) contains on-chip oscillator, CPU, RAM, (EP)ROM, monitor ROM, EEPROM, parallel I/O, one core timer, COP watchdog system, two 16-bit programmable timers, synchronous and asynchronous serial interface, a 4 channel A/D converter, and an 8 channel 8-bit PWM with on-chip power driver circuitry.

MC68HC(7)05H12 - Rev. 1.0

General Release Specification

## **General Description**

### 1.3 Features

- HC05 core

- 52 PLCC package

- 12032 bytes of user (EP)ROM + 240 bytes of monitor ROM + 16 bytes user vectors

- 256 bytes of RAM

- 256 bytes of EEPROM

- Multipurpose core timer, real time interrupt (RTI), COP watchdog timer

- Two 16-bit timers with two input captures and two output compares each

- Serial peripheral interface (SPI)

- Serial communications interface (SCI)

- 4 channel A/D converter (8-bit resolution)

- Keyboard interrupt for 8 I/O lines

- 8 channel 8-bit PWM system for control of H-bridge drivers

- 12 special power drivers to drive two major gauges and four minor gauges, with short circuit detection and slew rate limitation for reduced RFI (EMC)

- Power saving WAIT mode

- 2 selectable bus frequencies (slow mode)

- Low voltage reset (LVR) circuitry to hold the CPU in reset

Figure 1-1. MC68HC(7)05H12 Block Diagram

## **General Description**

## 1.4 Mask Options

There are three mask options:

- COP watchdog timer (enable/disable)

- Low voltage reset (LVR) (enable/disable)

- Ports E/F in WAIT mode (enable/disable)

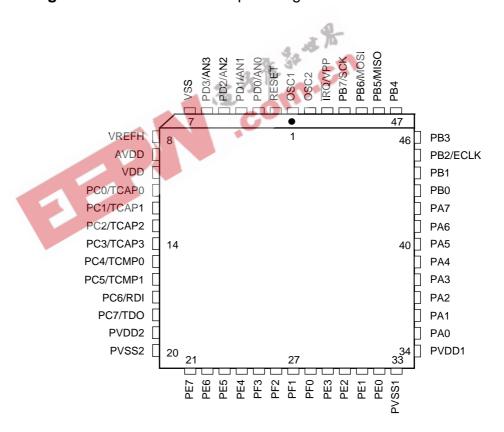

## 1.5 Pin Assignments

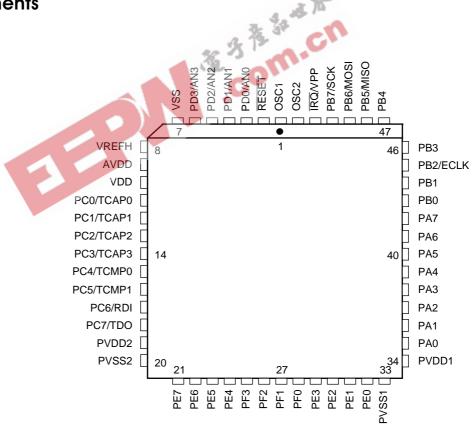

Figure 1-2 shows the PLCC pin assignments.

Figure 1-2. MC68HC(7)05H12 Pin Assignments (52-pin PLCC package)

## 1.6 Functional Pin Description

The following paragraphs give a description of the general function of each pin.

#### 1.6.1 VDD and VSS

Power is supplied to the MCU through VDD and VSS. VDD is the positive supply, and VSS is ground.

#### 1.6.2 AVDD

AVDD is a separate supply pin providing power to the A/D converter.

## 1.6.3 OSC1, OSC2

s are the The OSC1 and OSC2 pins are the connections for the on-chip oscillator. A crystal connected across these pins or an external signal connected to OSC1 provides the oscillator clock. The frequency, f<sub>OSC</sub>, of the oscillator or external clock source is divided by two or eight (slow mode) to produce the internal operating frequency, for.

#### 1.6.4 **RESET**

This pin can be used as an input to reset the MCU to a known start-up state by pulling it to the low state. The RESET pin contains an internal Schmitt trigger to improve its noise immunity as an input. The RESET pin has an internal pulldown device that pulls the RESET pin low when there is an internal COP watchdog reset, power-on reset (POR), illegal address reset, or an internal low voltage reset. Refer to **Section 5 Resets**. The RESET pin contains an internal pullup device.

#### 1.6.5 **IRQ**/**VPP**

The interrupt triggering sensitivity of this pin can be programmed as falling edge sensitive or falling edge and low level sensitive. The IRQ pin

MC68HC(7)05H12 - Rev. 1.0

General Release Specification

## **General Description**

contains an internal Schmitt trigger as part of its input to improve noise immunity. See **Section 4 Interrupts** for more details on the interrupts.

IRQ/VPP is also the EPROM programming power pin.

## 1.6.6 PA0-PA7/Keyboard Interrupt

These eight I/O lines comprise port A. The state of any pin is software programmable and all port A lines are configured as inputs during power-on or reset. The eight I/O lines are shared with the keyboard interrupt function. See **Section 7 Input/Output Ports** for more details on the I/O ports.

在各世界

### 1.6.7 PB0-PB7/ECLK, MISO, MOSI, SCK

These eight I/O lines comprise port B. The state of any pin is software programmable and all port B lines are configured as inputs during power-on or reset. See Section 7 Input/Output Ports for more details on the I/O ports. The port pins PB5–PB7 are shared with the SPI system (MISO, MOSI, SCK). See Section 10 Serial Peripheral Interface (SPI) for more details on the operation of the SPI. Pin PB2 is shared with the internal system clock ECLK. See Section 2.3.1 System Control Register.

## 1.6.8 PC0-PC7/TCAP0-3, TCMP0-1, RDI, TDO

These eight I/O lines comprise port C. The state of any pin is software programmable and all port C lines are configured as inputs during power-on or reset. See **Section 7 Input/Output Ports** for more details on the I/O ports. The port pins PC0–PC5 are shared with the 16-bit timer (TCAP0–3, TCMP0–1). See **Section 9 16-Bit Timers** for more details on the operation of the 16-bit timers. The port pins PC6 and PC7 are shared with the SCI system (RDI and TDO). Refer to **Section 11 Serial Communications Interface (SCI)**.

#### 1.6.9 PD0-PD3/AN0-AN3

These four input only lines comprise port D. See

**Section 7 Input/Output Ports** for more details on the I/O ports. When the A/D converter is active, one of the 4 input lines may be selected by the A/D multiplexer for conversion. See **Section 12 Analog to Digital Converter** for more details on the operation of the A/D subsystem.

#### 1.6.10 VREFH

This pin provides the positive reference voltage for the A/D converter. VSS provides the negative reference voltage for the A/D converter.

#### 1.6.11 PEO-PE7

These eight output only lines comprise port E. See

Section 7 Input/Output Ports for more details on the I/O ports. The eight lines are shared with four PWM H-bridge driver pairs. The outputs are formed by special power drivers. See Section 14 Pulse Width Modulator (PWM) for more details on the PWM subsystem.

#### 1.6.12 PFO-PF3

These four output only lines comprise port F. See

Section 7 Input/Output Ports for more details on the I/O ports. The

four lines are shared with four PWM channels. The outputs are formed

by special power drivers. See Section 14 Pulse Width Modulator

(PWM) for more details on the PWM subsystem.

#### 1.6.13 PVDD1, PVSS1, PVDD2, PVSS2

Power is supplied to the power drivers through PVDD and PVSS. PVDD1 and PVSS1 are the supply pins for PE0–3 and PF0–1 and PVDD2 and PVSS2 are the supply pins for PE4–7 and PF2–3.

The VSS pin and the PVSS1 and PVSS2 pins are connected internally.

# Section 2. Memory

## 2.1 Contents

| 2.2   | Introduction                            |

|-------|-----------------------------------------|

| 2.3   | Registers                               |

| 2.3.1 | System Control Register                 |

| 2.4   | RAM                                     |

| 2.5   | ROM35                                   |

| 2.6   | Monitor ROM                             |

|       | User EPROM (for the 705 version only)35 |

| 2.8   | EEPROM                                  |

## 2.2 Introduction

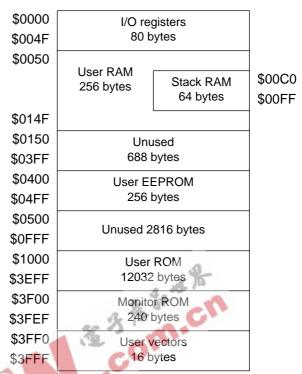

The MC68HC(7)05H12 has a 16K byte memory map consisting of registers (for I/O, control and status), user RAM, user ROM (or EPROM), EEPROM, monitor ROM, and reset and interrupt vectors as shown in **Figure 2-1**.

Figure 2-1. MC68HC(7)05H12 Memory Map

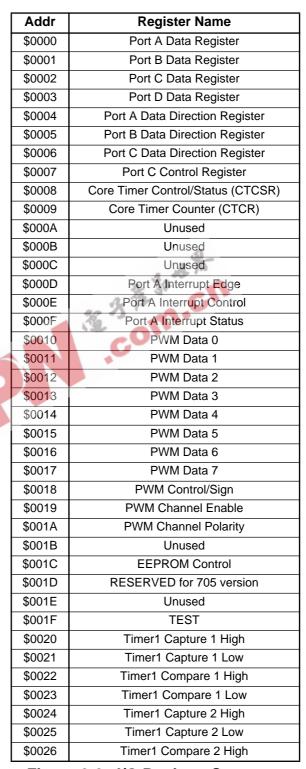

## 2.3 Registers

The I/O and control registers reside in locations \$0000–\$004F. The overall organization of these registers is shown in Figure 1-2. The bit assignments for each register are shown in Figure 2-3, Figure 2-4, Figure 2-5, Figure 2-6, and Figure 2-7.

26

Figure 2-2. I/O Register Summary

Figure 2-2. I/O Register Summary

| Addr   | Register              | R/W    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2     | Bit 1 | Bit 0 |

|--------|-----------------------|--------|-------|-------|-------|-------|-----------|-----------|-------|-------|

| \$0000 | Port A Data           | R<br>W | PA7   | PA6   | PA5   | PA4   | PA3       | PA2       | PA1   | PA0   |

| \$0001 | Port B Data           | R<br>W | PB7   | PB6   | PB5   | PB4   | PB3       | PB2       | PB1   | PB0   |

| \$0002 | Port C Data           | R<br>W | PC7   | PC6   | PC5   | PC4   | PC3       | PC2       | PC1   | PC0   |

| \$0003 | Port D Data           | R<br>W | 0     | 0     | 0     | 0     | PD3       | PD2       | PD1   | PD0   |

| \$0004 | Port A Data Direction | R<br>W | DDRA7 | DDRA6 | DDRA5 | DDRA4 | DDRA3     | DDRA2     | DDRA1 | DDRA0 |

| \$0005 | Port B Data Direction | R<br>W | DDRB7 | DDRB6 | DDRB5 | DDRB4 | DDRB3     | DDRB2     | DDRB1 | DDRB0 |

| \$0006 | Port C Data Direction | R<br>W | DDRC7 | DDRC6 | DDRC5 | DDRC4 | DDRC3     | DDRC2     | DDRC1 | DDRC0 |

| \$0007 | Port C Control        | R<br>W | 0     | 0     | TCMP1 | TCMP0 | 0         | 0         | 0     | 0     |

| \$0008 | CTSCR                 | R<br>W | TOF   | RTIF  | TOFE  | RTIE  | 0<br>RTOF | 0<br>RTIF | RT1   | RT0   |

| \$0009 | CTCR                  | R<br>W | bit 7 | bit 6 | bit 5 | bit 4 | bit 3     | bit 2     | bit 1 | bit 0 |

| \$000A | Unimplemented         | R<br>W |       |       |       |       |           |           |       |       |

| \$000B | Unimplemented         | R<br>W |       |       |       |       |           |           |       |       |

| \$000C | Unimplemented         | R<br>W |       |       |       |       |           |           |       |       |

| \$000D | PAIED                 | R<br>W | EDGE7 | EDGE6 | EDGE5 | EDGE4 | EDGE3     | EDGE2     | EDGE1 | EDGE0 |

| \$000E | PAICR                 | R<br>W | PAIE7 | PAIE6 | PAIE5 | PAIE4 | PAIE3     | PAIE2     | PAIE1 | PAIE0 |

| \$000F | PAISR                 | R<br>W | PAIF7 | PAIF6 | PAIF5 | PAIF4 | PAIF3     | PAIF2     | PAIF1 | PAIF0 |

Figure 2-3. I/O Registers \$0000-\$000F

| Addr   | Register                 | R/W    | Bit 7      | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|--------|--------------------------|--------|------------|--------|--------|--------|--------|--------|--------|--------|

| \$0010 | PWM Data 0               | R<br>W | bit 7      | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  |

| \$0011 | PWM Data 1               | R<br>W | bit 7      | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  |

| \$0012 | PWM Data 2               | R<br>W | bit 7      | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  |

| \$0013 | PWM Data 3               | R<br>W | bit 7      | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  |

| \$0014 | PWM Data 4               | R<br>W | bit 7      | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  |

| \$0015 | PWM Data 5               | R<br>W | bit 7      | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  |

| \$0016 | PWM Data 6               | R<br>W | bit 7      | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  |

| \$0017 | PWM Data 7               | R<br>W | bit 7      | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  |

| \$0018 | PWMCTL                   | R<br>W | 0<br>PWMRS | PWMC3  | PWMC2  | PWMC1  | SIGN3  | SIGN2  | SIGN1  | SIGN0  |

| \$0019 | PWMEN                    | R<br>W | PWME7      | PWME6  | PWME5  | PWME4  | PWME3  | PWME2  | PWME1  | PWME0  |

| \$001A | PWMPOL                   | R<br>W | PPOL7      | PPOL6  | PPOL5  | PPOL4  | PPOL3  | PPOL2  | PPOL1  | PPOL0  |

| \$001B | Unimplemented            | R<br>W |            |        |        |        |        |        |        |        |

| \$001C | EEPCR                    | R<br>W | 0          | 0      | 0      | EEOSC  | ER1    | EER0   | EELAT  | EEPGM  |

| \$001D | Reserved for 705 version | R<br>W |            |        |        |        |        |        |        |        |

| \$001E | Unimplemented            | R<br>W |            |        |        |        |        |        |        |        |

| \$001F | TEST                     | R      | 0          | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| 40011  | 1201                     | W      | ††††††     | †††††† | †††††† | †††††† | †††††† | †††††† | †††††† | †††††† |

Figure 2-4. I/O Registers \$0010-\$001F

| Addr   | Register                        | R/W    | Bit 7  | Bit 6  | Bit 5  | Bit 4    | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

|--------|---------------------------------|--------|--------|--------|--------|----------|--------|--------|-------|-------|

| \$0020 | Timer 1 Input                   | R      | bit 15 | bit 14 | bit 13 | bit 12   | bit 11 | bit 10 | bit 9 | bit 8 |

| \$0020 | Capture1 High                   | W      |        |        |        |          |        |        |       |       |

| \$0021 | Timer 1 Input                   | R      | bit 7  | bit 6  | bit 5  | bit 4    | bit 3  | bit 2  | bit 1 | bit 0 |

| φυυ21  | Capture1 Low                    | W      |        |        |        |          |        |        |       |       |

| \$0022 | Timer 1 Output<br>Compare1 High | R<br>W | bit 15 | bit 14 | bit 13 | bit 12   | bit 11 | bit 10 | bit 9 | bit 8 |

| \$0023 | Timer 1 Output<br>Compare1 Low  | R<br>W | bit 7  | bit 6  | bit 5  | bit 4    | bit 3  | bit 2  | bit 1 | bit 0 |

| \$0024 | Timer 1 Input                   | R      | bit 15 | bit 14 | bit 13 | bit 12   | bit 11 | bit 10 | bit 9 | bit 8 |

| φυυ24  | Capture2 High                   | W      |        |        |        |          |        |        |       |       |

| \$0025 | Timer 1 Input                   | R      | bit 7  | bit 6  | bit 5  | bit 4    | bit 3  | bit 2  | bit 1 | bit 0 |

| φυυ25  | Capture2 Low                    | W      |        |        |        |          |        |        |       |       |

| \$0026 | Timer 1 Output<br>Compare2 High | R<br>W | bit 15 | bit 14 | bit 13 | bit 12   | bit 11 | bit 10 | bit 9 | bit 8 |

| \$0027 | Timer 1 Output<br>Compare2 Low  | R<br>W | bit 7  | bit 6  | bit 5  | bit 4    | bit 3  | bit 2  | bit 1 | bit 0 |

| \$0028 | Timer 1 Counter High            | R      | bit 15 | bit 14 | bit 13 | bit 12   | bit 11 | bit 10 | bit 9 | bit 8 |

| \$0020 |                                 | W      |        |        | CAL    | $O_{II}$ |        |        |       |       |

| \$0029 | Timer 1 Counter Low             | R      | bit 7  | bit 6  | bit 5  | bit 4    | bit 3  | bit 2  | bit 1 | bit 0 |

| ΨΟΟΖΟ  | Timer T Counter Low             | W      |        |        |        |          |        |        |       |       |

| \$002A | Timer 1 Alternate               | R      | bit 15 | bit 14 | bit 13 | bit 12   | bit 11 | bit 10 | bit 9 | bit 8 |

| ΨΟΟΖΑ  | Counter High                    | W      |        |        |        |          |        |        |       |       |

| \$002B | Timer 1 Alternate               | R      | bit 7  | bit 6  | bit 5  | bit 4    | bit 3  | bit 2  | bit 1 | bit 0 |

| Ψ002B  | Counter Low                     | W      |        |        |        |          |        |        |       |       |

| \$002C | Timer 1 Control 1               | R<br>W | ICI1E  | ICI2E  | OCI1E  | TOIE     | CO1E   | IEDG1  | IEDG2 | OLVL1 |

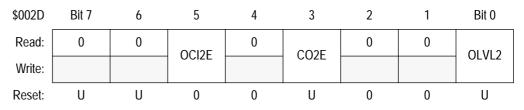

| \$002D | Timer 1 Control 2               | R<br>W | 0      | 0      | OC2IE  | 0        | CO2E   | 0      | 0     | OLVL2 |

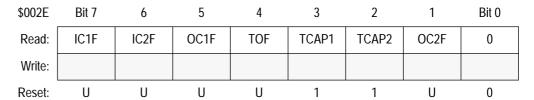

| #000F  | Time and Otate                  | R      | IC1F   | IC2F   | OC1F   | TOF      | TCAP1  | TCAP2  | OC2F  | 0     |

| \$002E | Timer 1 Status                  | W      |        |        |        |          |        |        |       |       |

| \$000F | l lucionario anno ante d        | R      |        |        |        |          |        |        |       |       |

| \$002F | Unimplemented                   | W      |        |        |        |          |        |        |       |       |

Figure 2-5. I/O Registers \$0020-\$002F

| Addr     | Register                        | R/W    | Bit 7  | Bit 6  | Bit 5  | Bit 4    | Bit 3  | Bit 2  | Bit 1 | Bit 0    |

|----------|---------------------------------|--------|--------|--------|--------|----------|--------|--------|-------|----------|

| \$0030   | Timer 2 Input Capture1          | R      | bit 15 | bit 14 | bit 13 | bit 12   | bit 11 | bit 10 | bit 9 | bit 8    |

| \$0030   | High                            | W      |        |        |        |          |        |        |       |          |

| \$0031   | Timer 2 Input Capture1          | R      | bit 7  | bit 6  | bit 5  | bit 4    | bit 3  | bit 2  | bit 1 | bit 0    |

| \$0031   | Low                             | W      |        |        |        |          |        |        |       |          |

| \$0032   | Timer 2 Output<br>Compare1 High | R<br>W | bit 15 | bit 14 | bit 13 | bit 12   | bit 11 | bit 10 | bit 9 | bit 8    |

| \$0033   | Timer 2 Output<br>Compare1 Low  | R<br>W | bit 7  | bit 6  | bit 5  | bit 4    | bit 3  | bit 2  | bit 1 | bit 0    |

| \$0034   | Timer 2 Input Capture2          | R      | bit 15 | bit 14 | bit 13 | bit 12   | bit 11 | bit 10 | bit 9 | bit 8    |

| \$0034   | High                            | W      |        |        |        |          |        |        |       |          |

| \$0035   | Timer 2 Input Capture2          | R      | bit 7  | bit 6  | bit 5  | bit 4    | bit 3  | bit 2  | bit 1 | bit 0    |

| ΨΟΟΟΟ    | Low                             | W      |        |        |        |          |        |        |       |          |

| \$0036   | Timer 2 Output<br>Compare2 High | R<br>W | bit 15 | bit 14 | bit 13 | bit 12   | bit 11 | bit 10 | bit 9 | bit 8    |

| \$0037   | Timer 2 Output<br>Compare2 Low  | R<br>W | bit 7  | bit 6  | bit 5  | bit 4    | bit 3  | bit 2  | bit 1 | bit 0    |

| \$0038   | Timer 2 Counter High            | R      | bit 15 | bit 14 | bit 13 | bit 12   | bit 11 | bit 10 | bit 9 | bit 8    |

| ψ0030    | Timer 2 Counter riight          | W      |        |        | 135    | $O_{II}$ |        |        |       |          |

| \$0039   | Timer 2 Counter Low             | R      | bit 7  | bit 6  | bit 5  | bit 4    | bit 3  | bit 2  | bit 1 | bit 0    |

| Ψοσσσ    | Timor 2 Godiner Low             | W      |        |        |        |          |        |        |       |          |

| \$003A   | Timer 2 Alternate               | R      | bit 15 | bit 14 | bit 13 | bit 12   | bit 11 | bit 10 | bit 9 | bit 8    |

| 400071   | Counter High                    | W      |        |        |        |          |        |        |       |          |

| \$003B   | Timer 2 Alternate               | R      | bit 7  | bit 6  | bit 5  | bit 4    | bit 3  | bit 2  | bit 1 | bit 0    |

| <b>—</b> | Counter Low                     | W      |        |        |        |          |        |        |       |          |

| \$003C   | Timer 2 Control 1               | R      | ICI1E  | ICI2E  | OCI1E  | TOIE     | CO1E   | IEDG1  | IEDG2 | OLVL1    |

|          |                                 | W      |        |        | 0001   |          |        |        |       | 011/11/2 |

| \$003D   | Timer 2 Control 2               | R      | 0      | 0      | OC2IE  | 0        | CO2E   | 0      | 0     | OLVL2    |

|          |                                 | W      | 1045   | IOOF   | 0045   | TOF      | TOAD4  | TOADC  | 0005  |          |

| \$003E   | Timer 2 Status                  | R      | IC1F   | IC2F   | OC1F   | TOF      | TCAP1  | TCAP2  | OC2F  | 0        |

|          |                                 | W      |        |        |        |          |        |        |       |          |

| \$003F   | Unimplemented                   | R<br>W |        |        |        |          |        |        |       |          |

Figure 2-6. I/O Registers \$0030-\$003F

| Addr   | Register           | R/W    | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1 | Bit 0 |

|--------|--------------------|--------|-----------|-------|-------|-------|-----------|-------|-------|-------|

| \$0040 | Port E Data        | R<br>W | PE7       | PE6   | PE5   | PE4   | PE3       | PE2   | PE1   | PE0   |

| \$0041 | Port E Mismatch    | R<br>W | bit 7     | bit 6 | bit 5 | bit 4 | bit 3     | bit 2 | bit 1 | bit 0 |

| \$0042 | Port F Data        | R<br>W | 0         | 0     | 0     | 0     | PF3       | PF2   | PF1   | PF0   |

| \$0043 | Port F Mismatch    | R<br>W | 0         | 0     | 0     | 0     | bit 3     | bit 2 | bit 1 | bit 0 |

| \$0044 | SPI Control        | R<br>W | SPIE      | SPE   | DOD   | MSTR  | CPOL      | СРНА  | SPR1  | SPR0  |

| \$0045 | SPI Status         | R<br>W | SPIF      | WCOL  | 0     | 0     | 0         | 0     | 0     | 0     |

| \$0046 | SPI Data           | R<br>W | bit 7     | bit 6 | bit 5 | bit 4 | bit 3     | bit 2 | bit 1 | bit 0 |

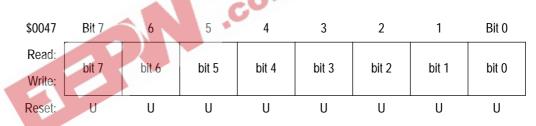

| \$0047 | SCI Data           | R<br>W | bit 7     | bit 6 | bit 5 | bit 4 | bit 3     | bit 2 | bit 1 | bit 0 |

| \$0048 | SCI Control 1      | R<br>W | R8        | Т8    | 0     | М     | WAKE      | 0     | 0     | 0     |

| \$0049 | SCI Control 2      | R<br>W | TIE       | TCIE  | RIE   | ILIE  | TE        | RE    | RWU   | SBK   |

| \$004A | SCI Status         | R<br>W | TDRE      | ТС    | RDRF  | IDLE  | OR        | NF    | FE    | 0     |

| \$004B | SCI BAUD           | R<br>W | 0<br>TCLR | SPP   | SCP1  | SCP0  | 0<br>RCKB | SCR2  | SCR1  | SCR0  |

| \$004C | Unimplemented      | R<br>W |           |       |       |       |           |       |       |       |

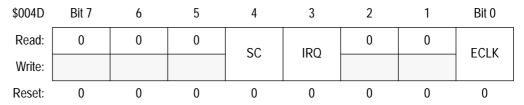

| \$004D | System Control     | R<br>W | 0         | 0     | 0     | SC    | IRQ       | 0     | 0     | ECLK  |

| \$004E | A/D Data           | R<br>W | bit 7     | bit 6 | bit 5 | bit 4 | bit 3     | bit 2 | bit 1 | bit 0 |

| \$004F | A/D Status/Control | R<br>W | COCO      | ADRC  | ADON  | 0     | СНЗ       | CH2   | CH1   | CH0   |

Figure 2-7. I/O Registers \$0040-\$004F

## 2.3.1 System Control Register

The MC68HC(7)05H12 contains a system control register which is located at \$004D. This register is used to control the IRQ interrupt sensitivity, the bus frequency, and the external availability of the internal bus clock.

Figure 2-8. System Control Register (SYSCR)

SC — System Clock Option

After power on reset the internal bus frequency  $f_{OP}$  is =  $f_{OSC}/2$ . The SC bit allows the user to reduce the system speed to  $f_{OSC}/8$ .

$$1 = f_{OP} = f_{OSC}/8 \text{ (Slow Mode)}$$

$$0 = f_{OP} = f_{OSC}/2$$

IRQ — IRQ Sensitivity

IRQ edge or level sensitive

1 = IRQ input edge and level sensitive

0 = IRQ input edge sensitive

ECLK — Internal System Clock Available

The ECLK bit makes the internal system clock (bus frequency  $f_{OP}$ ) available to the user. Refer to **Section 7.4 Port B** for more details.

- 1 = The PB2/ECLK pin provides the internal system clock independently of the value of the port B data direction register

- 0 = The internal system clock is not available, the PB2/ECLK pin is an ordinary I/O port line

#### **2.4 RAM**

The user RAM consists of 256 bytes ranging from \$0050 to \$014F. The stack begins at address \$00FF. The stack pointer can access 64 bytes of RAM in the range \$00FF to \$00C0.

The stack is located in the middle of the RAM address space. Data written to addresses within the stack address range could be overwritten during stack activity.

### **2.5 ROM**

The 12032 bytes of the user ROM are located from \$1000 to \$3EFF, plus 16 bytes of user vectors from \$3FF0 to \$3FFF.

### 2.6 Monitor ROM

The monitor ROM ranges from \$3F00 to \$3FEF. The vectors for the bootloader are located from \$3FE0 to \$3FEF.

# 2.7 User EPROM (for the 705 version only)

The 12032 bytes of the user EPROM are located from \$1000 to \$3EFD, including two bytes of mask option registers (MOR) at \$3EFE and \$3EFF, plus 16 bytes of user vectors from \$3FF0 to \$3FFF. Refer to **Section 15 EPROM** for programming details.

#### 2.8 EEPROM

This device contains 256 bytes of EEPROM. Programming the EEPROM is performed by the user on a single-byte basis by manipulating the EEPROM control register, located at address \$001C. Refer to **Section 13 EEPROM** for programming details.

# Section 3. CPU and Instruction Set

# 3.1 Contents

| 3.2   | Introduction                     |

|-------|----------------------------------|

| 3.3   | CPU Registers                    |

| 3.3.1 | Accumulator                      |

| 3.3.2 | Index Register39                 |

| 3.3.3 | Stack Pointer39                  |

| 3.3.4 | Program Counter40                |

| 3.3.5 | Stack Pointer                    |

| 3.4   | Arithmetic/Logic Unit (ALU)42    |

| 3.5   | Instruction Set Overview         |

| 3.6   | Addressing Modes                 |

| 3.6.1 | Inherent43                       |

| 3.6.2 | Immediate                        |

| 3.6.3 | Direct43                         |

| 3.6.4 | Extended                         |

| 3.6.5 | Indexed, No Offset               |

| 3.6.6 | Indexed, 8-Bit Offset            |

| 3.6.7 | Indexed,16-Bit Offset            |

| 3.6.8 | Relative                         |

| 3.7   | Instruction Types45              |

| 3.7.1 | Register/Memory Instructions     |

| 3.7.2 | Read-Modify-Write Instructions47 |

| 3.7.3 | Jump/Branch Instructions         |

| 3.7.4 | Bit Manipulation Instructions    |

| 3.7.5 | Control Instructions             |

| 3.8   | Instruction Set Summary52        |

### 3.2 Introduction

This chapter describes the CPU registers and the HC05 instruction set.

# 3.3 CPU Registers

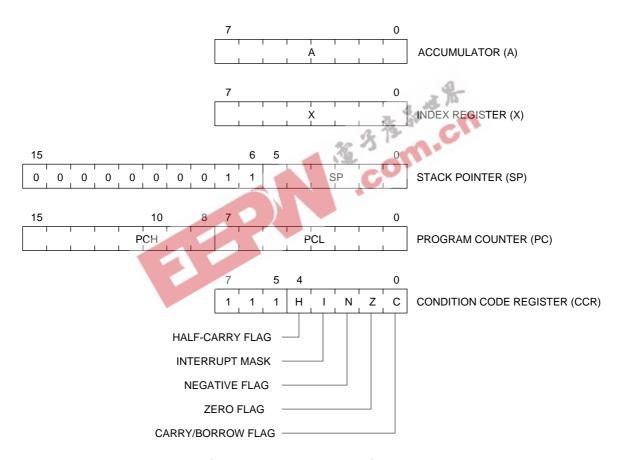

**Figure 3-1** shows the five CPU registers. CPU registers are not part of the memory map.

Figure 3-1. Programming Model

#### 3.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and results of arithmetic and non-arithmetic operations.

Figure 3-2. Accumulator

## 3.3.2 Index Register

In the indexed addressing modes, the CPU uses the byte in the index register to determine the conditional address of the operand.

Figure 3-3. Index Register

The 8-bit index register can also serve as a temporary data storage location.

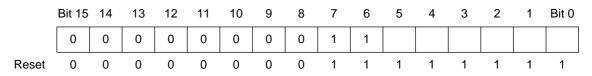

#### 3.3.3 Stack Pointer

The stack pointer is a 16-bit register that contains the address of the next location on the stack. During a reset or after the reset stack pointer (RSP) instruction, the stack pointer is preset to \$00FF. The address in the stack pointer decrements as data is pushed onto the stack and increments as data is pulled from the stack.

Figure 3-4. Stack Pointer

MC68HC(7)05H12 - Rev. 1.0

General Release Specification

The ten most significant bits of the stack pointer are permanently fixed at 000000011, so the stack pointer produces addresses from \$00C0 to \$00FF. If subroutines and interrupts use more than 64 stack locations, the stack pointer wraps around to address \$00FF and begins writing over the previously stored data. A subroutine uses two stack locations. An interrupt uses five locations.

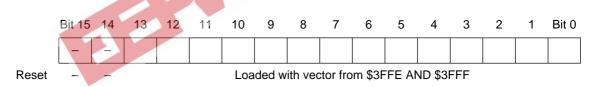

### 3.3.4 Program Counter

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched. The two most significant bits of the program counter are ignored internally.

Normally, the address in the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, and interrupt operations load the program counter with an address other than that of the next sequential location.

Figure 3-5. Program Counter

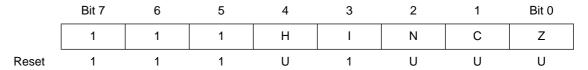

### 3.3.5 Condition Code Register

The condition code register is an 8-bit register whose three most significant bits are permanently fixed at 111. The condition code register contains the interrupt mask and four flags that indicate the results of the instruction just executed. The following paragraphs describe the functions of the condition code register.

Figure 3-6. Condition Code Register

**General Release Specification**

MC68HC(7)05H12 - Rev. 1.0

### **Half-Carry Flag**

The CPU sets the half-carry flag when a carry occurs between bits 3 and 4 of the accumulator during an ADD or ADC operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations.

### Interrupt Mask

Setting the interrupt mask disables interrupts. If an interrupt request occurs while the interrupt mask is logic zero, the CPU saves the CPU registers on the stack, sets the interrupt mask, and then fetches the interrupt vector. If an interrupt request occurs while the interrupt mask is set, the interrupt request is latched. Normally, the CPU processes the latched interrupt as soon as the interrupt mask is cleared again.

A return from interrupt (RTI) instruction pulls the CPU registers from the stack, restoring the interrupt mask to its cleared state. After any reset, the interrupt mask is set and can be cleared only by a software instruction.

### **Negative Flag**

The CPU sets the negative flag when an arithmetic operation, logical operation, or data manipulation produces a negative result.

#### **Zero Flag**

The CPU sets the zero flag when an arithmetic operation, logical operation, or data manipulation produces a result of \$00.

#### Carry/Borrow Flag

The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some logical operations and data manipulation instructions also clear or set the carry/borrow flag.

## 3.4 Arithmetic/Logic Unit (ALU)

The ALU performs the arithmetic and logical operations defined by the instruction set.

The binary arithmetic circuits decode instructions and set up the ALU for the selected operation. Most binary arithmetic is based on the addition algorithm, carrying out subtraction as negative addition. Multiplication is not performed as a discrete operation but as a chain of addition and shift operations within the ALU. The multiply instruction (MUL) requires 11 internal clock cycles to complete this chain of operations.

### 3.5 Instruction Set Overview

The MCU instruction set has 62 instructions and uses eight addressing modes. The instructions include all those of the M146805 CMOS Family plus one more: the unsigned multiply (MUL) instruction. The MUL instruction allows unsigned multiplication of the contents of the accumulator (A) and the index register (X). The high-order product is stored in the index register, and the low-order product is stored in the accumulator.

# 3.6 Addressing Modes

The CPU uses eight addressing modes for flexibility in accessing data. The addressing modes provide eight different ways for the CPU to find the data required to execute an instruction. The eight addressing modes are:

- Inherent

- Immediate

- Direct

- Extended

- Indexed, no offset

- Indexed, 8-bit offset

- Indexed, 16-bit offset

- Relative

#### 3.6.1 Inherent

Inherent instructions are those that have no operand, such as return from interrupt (RTI). Some of the inherent instructions act on data in the CPU registers, such as set carry flag (SEC) and increment accumulator (INCA). Inherent instructions require no operand address and are one byte long.

#### 3.6.2 Immediate

Immediate instructions are those that contain a value to be used in an operation with the value in the accumulator or index register. Immediate instructions require no operand address and are two bytes long. The opcode is the first byte, and the immediate data value is the second byte.

#### **3.6.3 Direct**

Direct instructions can access any of the first 256 memory locations with two bytes. The first byte is the opcode, and the second is the low byte of the operand address. In direct addressing, the CPU automatically uses \$00 as the high byte of the operand address.

#### 3.6.4 Extended

Extended instructions use three bytes and can access any address in memory. The first byte is the opcode; the second and third bytes are the high and low bytes of the operand address.

When using the Motorola assembler, the programmer does not need to specify whether an instruction is direct or extended. The assembler automatically selects the shortest form of the instruction.

### **CPU** and Instruction Set

### 3.6.5 Indexed, No Offset

Indexed instructions with no offset are 1-byte instructions that can access data with variable addresses within the first 256 memory locations. The index register contains the low byte of the effective address of the operand. The CPU automatically uses \$00 as the high byte, so these instructions can address locations \$0000–\$00FF.

Indexed, no offset instructions are often used to move a pointer through a table or to hold the address of a frequently used RAM or I/O location.

#### 3.6.6 Indexed, 8-Bit Offset

Indexed, 8-bit offset instructions are 2-byte instructions that can access data with variable addresses within the first 511 memory locations. The CPU adds the unsigned byte in the index register to the unsigned byte following the opcode. The sum is the effective address of the operand. These instructions can access locations \$0000–\$01FE.

Indexed 8-bit offset instructions are useful for selecting the kth element in an n-element table. The table can begin anywhere within the first 256 memory locations and could extend as far as location 510 (\$01FE). The k value is typically in the index register, and the address of the beginning of the table is in the byte following the opcode.

#### 3.6.7 Indexed.16-Bit Offset

Indexed, 16-bit offset instructions are 3-byte instructions that can access data with variable addresses at any location in memory. The CPU adds the unsigned byte in the index register to the two unsigned bytes following the opcode. The sum is the effective address of the operand. The first byte after the opcode is the high byte of the 16-bit offset; the second byte is the low byte of the offset.

Indexed, 16-bit offset instructions are useful for selecting the kth element in an n-element table anywhere in memory.

As with direct and extended addressing, the Motorola assembler determines the shortest form of indexed addressing.

**General Release Specification**

MC68HC(7)05H12 — Rev. 1.0

#### 3.6.8 Relative

Relative addressing is only for branch instructions. If the branch condition is true, the CPU finds the effective branch destination by adding the signed byte following the opcode to the contents of the program counter. If the branch condition is not true, the CPU goes to the next instruction. The offset is a signed, two's complement byte that gives a branching range of –128 to +127 bytes from the address of the next location after the branch instruction.

When using the Motorola assembler, the programmer does not need to calculate the offset, because the assembler determines the proper offset and verifies that it is within the span of the branch.

为老品本品

# 3.7 Instruction Types

The MCU instructions fall into the following five categories:

- Register/Memory Instructions

- Read-Modify-Write Instructions

- Jump/Branch Instructions

- Bit Manipulation Instructions

- Control Instructions

# 3.7.1 Register/Memory Instructions

These instructions operate on CPU registers and memory locations. Most of them use two operands. One operand is in either the accumulator or the index register. The CPU finds the other operand in memory.

Table 3-1. Register/Memory Instructions

| Instruction                                         | Mnemonic |

|-----------------------------------------------------|----------|

| Add Memory Byte and Carry Bit to Accumulator        | ADC      |

| Add Memory Byte to Accumulator                      | ADD      |

| AND Memory Byte with Accumulator                    | AND      |

| Bit Test Accumulator                                | BIT      |

| Compare Accumulator                                 | CMP      |

| Compare Index Register with Memory Byte             | CPX      |

| EXCLUSIVE OR Accumulator with Memory Byte           | EOR      |

| Load Accumulator with Memory Byte                   | LDA      |

| Load Index Register with Memory Byte                | LDX      |

| Multiply                                            | MUL      |

| OR Accumulator with Memory Byte                     | ORA      |

| Subtract Memory Byte and Carry Bit from Accumulator | SBC      |

| Store Accumulator in Memory                         | STA      |

| Store Index Register in Memory                      | STX      |

| Subtract Memory Byte from Accumulator               | SUB      |

### 3.7.2 Read-Modify-Write Instructions

These instructions read a memory location or a register, modify its contents, and write the modified value back to the memory location or to the register.

**NOTE:** Do not use read-modify-write operations on write-only registers.

Table 3-2. Read-Modify-Write Instructions

| Instruction                         | Mnemonic            |

|-------------------------------------|---------------------|

| Arithmetic Shift Left (Same as LSL) | ASL                 |

| Arithmetic Shift Right              | ASR                 |

| Bit Clear                           | BCLR <sup>(1)</sup> |

| Bit Set                             | BSET <sup>(1)</sup> |

| Clear Register                      | CLR                 |

| Complement (One's Complement)       | СОМ                 |

| Decrement                           | DEC                 |

| Increment                           | INC                 |

| Logical Shift Left (Same as ASL)    | LSL                 |

| Logical Shift Right                 | LSR                 |

| Negate (Two's Complement)           | NEG                 |

| Rotate Left through Carry Bit       | ROL                 |

| Rotate Right through Carry Bit      | ROR                 |

| Test for Negative or Zero           | TST <sup>(2)</sup>  |

<sup>1.</sup> Unlike other read-modify-write instructions, BCLR and BSET use only direct addressing.

<sup>2.</sup> TST is an exception to the read-modify-write sequence because it does not write a replacement value.

### **CPU** and Instruction Set

### 3.7.3 Jump/Branch Instructions

Jump instructions allow the CPU to interrupt the normal sequence of the program counter. The unconditional jump instruction (JMP) and the jump-to-subroutine instruction (JSR) have no register operand. Branch instructions allow the CPU to interrupt the normal sequence of the program counter when a test condition is met. If the test condition is not met, the branch is not performed.

The BRCLR and BRSET instructions cause a branch based on the state of any readable bit in the first 256 memory locations. These 3-byte instructions use a combination of direct addressing and relative addressing. The direct address of the byte to be tested is in the byte following the opcode. The third byte is the signed offset byte. The CPU finds the effective branch destination by adding the third byte to the program counter if the specified bit tests true. The bit to be tested and its condition (set or clear) is part of the opcode. The span of branching is from –128 to +127 from the address of the next location after the branch instruction. The CPU also transfers the tested bit to the carry/borrow bit of the condition code register.

Table 3-3. Jump and Branch Instructions

| Instruction                    | Mnemonic |

|--------------------------------|----------|

| Branch if Carry Bit Clear      | BCC      |

| Branch if Carry Bit Set        | BCS      |

| Branch if Equal                | BEQ      |

| Branch if Half-Carry Bit Clear | внсс     |

| Branch if Half-Carry Bit Set   | BHCS     |

| Branch if Higher               | BHI      |

| Branch if Higher or Same       | BHS      |

| Branch if IRQ Pin High         | BIH      |

| Branch if IRQ Pin Low          | BIL      |

| Branch if Lower                | BLO      |

| Branch if Lower or Same        | BLS      |

| Branch if Interrupt Mask Clear | BMC      |

| Branch if Minus                | BMI      |

| Branch if Interrupt Mask Set   | BMS      |

| Branch if Not Equal            | BNE      |

| Branch if Plus                 | BPL      |

| Branch Always                  | BRA      |

| Branch if Bit Clear            | BRCLR    |

| Branch Never                   | BRN      |

| Branch if Bit Set              | BRSET    |

| Branch to Subroutine           | BSR      |

| Unconditional Jump             | JMP      |

| Jump to Subroutine             | JSR      |

### 3.7.4 Bit Manipulation Instructions

The CPU can set or clear any writable bit in the first 256 bytes of memory, which includes I/O registers and on-chip RAM locations. The CPU can also test and branch based on the state of any bit in any of the first 256 memory locations.

**Table 3-4. Bit Manipulation Instructions**

| Instruction         | Mnemonic |

|---------------------|----------|

| Bit Clear           | BCLR     |

| Branch if Bit Clear | BRCLR    |

| Branch if Bit Set   | BRSET    |

| Bit Set             | BSET     |

#### 3.7.5 Control Instructions

These instructions act on CPU registers and control CPU operation during program execution.

**Table 3-5. Control Instructions**

| Instruction                            | Mnemonic |

|----------------------------------------|----------|

| Clear Carry Bit                        | CLC      |

| Clear Interrupt Mask                   | CLI      |

| No Operation                           | NOP      |

| Reset Stack Pointer                    | RSP      |

| Return from Interrupt                  | RTI      |

| Return from Subroutine                 | RTS      |

| Set Carry Bit                          | SEC      |

| Set Interrupt Mask                     | SEI      |

| Software Interrupt                     | SWI      |

| Transfer Accumulator to Index Register | TAX      |

| Transfer Index Register to Accumulator | TXA      |

| Stop CPU Clock and Enable Interrupts   | WAIT     |

51

# 3.8 Instruction Set Summary

**Table 3-6. Instruction Set Summary**

| Source                                                              | Operation Desc                        | Description                                            | I    |          | fect on<br>CCR |          |          |                                                                         |                                  |                                              | Cycles                |

|---------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------|------|----------|----------------|----------|----------|-------------------------------------------------------------------------|----------------------------------|----------------------------------------------|-----------------------|

| Form                                                                |                                       |                                                        | Н    | I        | N              | Z        | С        | Add                                                                     | Opcode                           | Operand                                      | ػٙ                    |

| ADC #opr<br>ADC opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC ,X  | Add with Carry                        | $A \leftarrow (A) + (M) + (C)$                         | \$\$ | _        | \$\$           | \$\$     | \$◊      | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                   | A9<br>B9<br>C9<br>D9<br>E9       | ii<br>dd<br>hh II<br>ee ff<br>ff             | 1 1                   |

| ADD #opr<br>ADD opr<br>ADD opr,<br>ADD opr,X<br>ADD opr,X<br>ADD ,X | Add without Carry                     | A ← (A) + (M)                                          | \$0  | _        | \$0            | <b>‡</b> | <b>‡</b> | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                   | AB<br>BB<br>CB<br>DB<br>EB<br>FB | ii<br>dd<br>hh II<br>ee ff<br>ff             | 1 1                   |

| AND #opr<br>AND opr<br>AND opr<br>AND opr,X<br>AND opr,X<br>AND ,X  | Logical AND                           | $A \leftarrow (A) + (M)$ $A \leftarrow (A) \wedge (M)$ | _    |          | \$\$           | <b>‡</b> | _        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                   | A4<br>B4<br>C4<br>D4<br>E4       | ii<br>dd<br>hh II<br>ee ff<br>ff             |                       |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X                      | Arithmetic Shift Left (Same as LSL)   | C 0 b7 b0                                              |      | _        | \$0            | <b>‡</b> | <b>‡</b> | DIR<br>INH<br>INH<br>IX1<br>IX                                          | 38<br>48<br>58<br>68<br>78       | dd<br>ff                                     | 5<br>3<br>6<br>5      |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR ,X                      | Arithmetic Shift Right                | b7 b0                                                  |      | _        | \$0            | <b>‡</b> | <b>‡</b> | DIR<br>INH<br>INH<br>IX1<br>IX                                          | 37<br>47<br>57<br>67<br>77       | dd<br>ff                                     | 5<br>3<br>3<br>6<br>5 |

| BCC rel                                                             | Branch if Carry Bit Clear             | PC ← (PC) + 2 + rel ? C = 0                            | -    | -        | _              | _        | _        | REL                                                                     | 24                               | rr                                           | 3                     |