April 1994 Revised February 2005

# 74VHC4066 Quad Analog Switch

#### **General Description**

These devices are digitally controlled analog switches utilizing advanced silicon-gate CMOS technology. These switches have low "on" resistance and low "off" leakages. They are bidirectional switches, thus any analog input may be used as an output and visa-versa. Also the 4066 switches contain linearization circuitry which lowers the "on" resistance and increases switch linearity. The 4066 devices allow control of up to 12V (peak) analog signals with digital control signals of the same range. Each switch has its own control input which disables each switch when low. All analog inputs and outputs and digital inputs are protected from electrostatic damage by diodes to  $\rm V_{CC}$  and around.

#### **Features**

- Typical switch enable time: 15 ns

- Wide analog input voltage range: 0–12V

- Low "on" resistance: 30 typ. ('4066)

- Low quiescent current: 80 µA maximum (74VHC)

- Matched switch characteristics

- Individual switch controls

- Pin and function compatible with the 74HC4066

## **Ordering Code:**

| Order Number     | Package | Package Description                                                                  |

|------------------|---------|--------------------------------------------------------------------------------------|

|                  | Number  |                                                                                      |

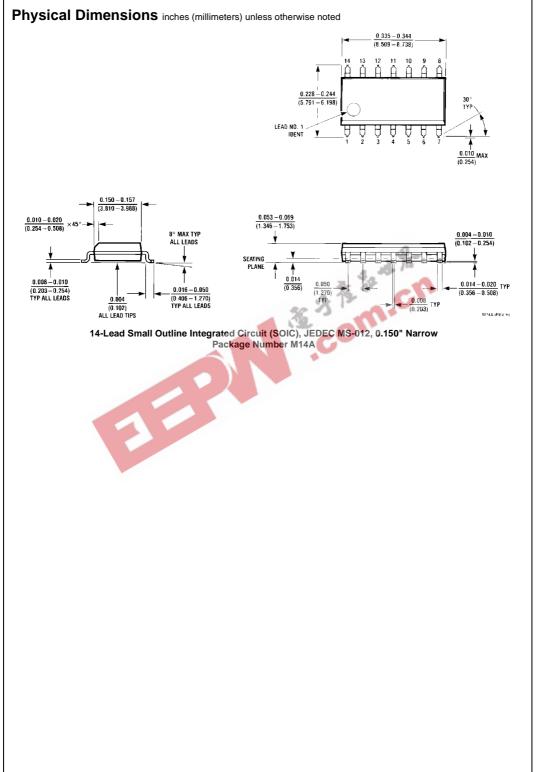

| 74VHC4066M       | M14A    | 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow         |

| 74VHC4066MX_NL   | M14A    | Pb-Free 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |

| (Note 1)         |         |                                                                                      |

| 74VHC4066MTC     | MTC14   | 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide          |

| 74VHC4066MTCX_NL | MTC14   | Pb-Free 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm       |

| (Note 1)         |         | Wide                                                                                 |

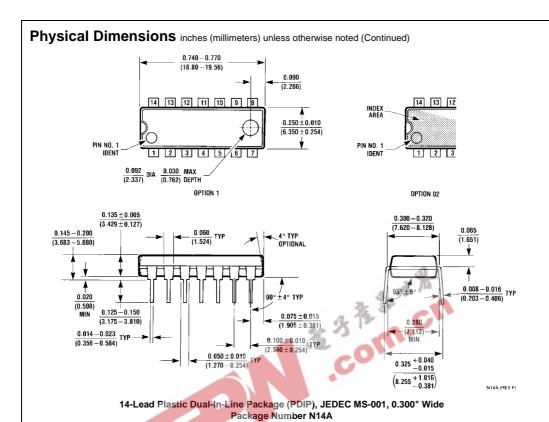

| 74VHC4066N       | N14A    | 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide               |

Surface mount packages are also available on Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

Note 1: "\_NL" indicates Pb-Free package (per JEDEC S-STD-020B). Device available in Tape and Reel only.

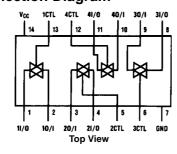

## **Connection Diagram**

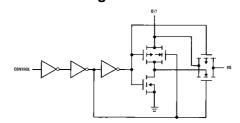

## **Schematic Diagram**

#### **Truth Table**

| Input | Switch  |

|-------|---------|

| CTL   | I/O-O/I |

| L     | "OFF"   |

| Н     | "ON"    |

# Absolute Maximum Ratings(Note 2)

(Note 3)

| Supply Voltage (V <sub>CC</sub> )                        | -0.5 to +15V                                                                |

|----------------------------------------------------------|-----------------------------------------------------------------------------|

| DC Control Input Voltage (V <sub>IN</sub> )              | $-1.5$ to $V_{CC} + 1.5V$                                                   |

| DC Switch I/O Voltage (V <sub>IO</sub> )                 | $V_{\mbox{\footnotesize EE}}$ – 0.5 to $V_{\mbox{\footnotesize CC}}$ + 0.5V |

| Clamp Diode Current (I <sub>IK</sub> , I <sub>OK</sub> ) | ±20 mA                                                                      |

| DC Output Current, per pin (I <sub>OUT</sub> )           | ±25 mA                                                                      |

| DC V <sub>CC</sub> or GND Current, per pin               |                                                                             |

| (I <sub>CC</sub> )                                       | ±50 mA                                                                      |

| Storage Temperature Range ( $T_{STG}$ )                  | -65°C to +150°C                                                             |

| Power Dissipation (P <sub>D</sub> ) (Note 4)             | 600 mW                                                                      |

| S.O. Package only                                        | 500 mW                                                                      |

| Lead Temperature (T <sub>L</sub> )                       |                                                                             |

| (Soldering 10 seconds)                                   | 260°C                                                                       |

# Recommended Operating Conditions

|                                                             | Min | Max      | Units |

|-------------------------------------------------------------|-----|----------|-------|

| Supply Voltage (V <sub>CC</sub> )                           | 2   | 12       | V     |

| DC Input or Output Voltage                                  | 0   | $V_{CC}$ | V     |

| $(V_{IN}, V_{OUT})$                                         |     |          |       |

| Operating Temperature Range (T <sub>A</sub> )               | -40 | +85      | °C    |

| Input Rise or Fall Times (t <sub>r</sub> , t <sub>f</sub> ) |     |          |       |

| $V_{CC} = 2.0V$                                             |     | 1000     | ns    |

| $V_{CC} = 4.5V$                                             |     | 500      | ns    |

| $V_{CC} = 9.0V$                                             |     | 400      | ns    |

Note 2: Absolute Maximum Ratings are those values beyond which damage to the device may occur.

Note 3: Unless otherwise specified all voltages are referenced to ground.

Note 4: Power Dissipation temperature derating — plastic "N" package: –

12 mW/°C from 65°C to 85°C.

# DC Electrical Characteristics (Note 5)

| Symbol          | Parameter               | Conditions                                    | V <sub>GC</sub> | T <sub>A</sub> =25°C |        | T <sub>A</sub> =-40 to 85°C | Units |

|-----------------|-------------------------|-----------------------------------------------|-----------------|----------------------|--------|-----------------------------|-------|

|                 |                         |                                               |                 | Тур                  | Guarar | teed Limits                 | Units |

| V <sub>IH</sub> | Minimum HIGH Level      |                                               | 2.0V            |                      | 1.5    | 1.5                         | V     |

|                 | Input Voltage           | 26                                            | 4.5V            | 400                  | 3.15   | 3.15                        | V     |

|                 |                         | 130                                           | 9.0V            |                      | 6.3    | 5.3                         | V     |

|                 |                         |                                               | 12.0V           |                      | 8.4    | 8.4                         | V     |

| V <sub>IL</sub> | Maximum LOW Level       |                                               | 2.0V            |                      | 0.5    | 0.5                         | V     |

|                 | Input Voltage           |                                               | 4.5V            |                      | 1.35   | 1.35                        | V     |

|                 |                         |                                               | 9.0V            |                      | 2.7    | 2.7                         | V     |

|                 |                         |                                               | 12.0V           |                      | 3.6    | 3.6                         | V     |

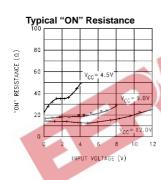

| R <sub>ON</sub> | Maximum "ON" Resistance | $V_{CTL} = V_{IH}$ , $I_S = 2.0 \text{ mA}$   | 4.5V            | 100                  | 170    | 200                         | Ω     |

|                 | See (Note 6)            | V <sub>IS</sub> = V <sub>CC</sub> to GND      | 9.0V            | 50                   | 85     | 105                         | Ω     |

|                 |                         | (Figure 1)                                    | 12.0V           | 30                   | 70     | 85                          | Ω     |

|                 |                         |                                               | 2.0V            | 120                  | 180    | 215                         | Ω     |

|                 |                         | $V_{CTL} = V_{IH}$ , $I_S = 2.0 \text{ mA}$   | 4.5V            | 50                   | 80     | 100                         | Ω     |

|                 |                         | $V_{IS} = V_{CC}$ or GND                      | 9.0V            | 35                   | 60     | 75                          | Ω     |

|                 |                         | (Figure 1)                                    | 12.0V           | 20                   | 40     | 60                          | Ω     |

| R <sub>ON</sub> | Maximum "ON" Resistance | V <sub>CTL</sub> = V <sub>IH</sub>            | 4.5V            | 10                   | 15     | 20                          | Ω     |

|                 | Matching                | $V_{IS} = V_{CC}$ to GND                      | 9.0V            | 5                    | 10     | 15                          | Ω     |

|                 |                         |                                               | 12.0V           | 5                    | 10     | 15                          | Ω     |

| I <sub>IN</sub> | Maximum Control         | V <sub>IN</sub> = V <sub>CC</sub> or GND      |                 |                      | ±0.05  | ±0.5                        | μА    |

|                 | Input Current           | $V_{CC} = 2 - 6V$                             |                 |                      |        |                             |       |

| I <sub>IZ</sub> | Maximum Switch "OFF"    | V <sub>OS</sub> = V <sub>CC</sub> or GND      | 6.0V            | 10                   | ±60    | ±600                        | nA    |

|                 | Leakage Current         | $V_{IS} = GND \text{ or } V_{CC}$             | 9.0V            | 15                   | ±80    | ±800                        | nA    |

|                 |                         | V <sub>CTL</sub> = V <sub>IL</sub> (Figure 2) | 12.0V           | 20                   | ±100   | ±1000                       | nA    |

| I <sub>IZ</sub> | Maximum Switch "ON"     | V <sub>IS</sub> = V <sub>CC</sub> to GND      | 6.0V            | 10                   | ±40    | ±150                        | nA    |

|                 | Leakage Current         | $V_{CTL} = V_{IH}$                            | 9.0V            | 15                   | ±50    | ±200                        | nA    |

|                 |                         | V <sub>OS</sub> = OPEN (Figure 3)             | 12.0V           | 20                   | ±60    | ±300                        | nA    |

| I <sub>CC</sub> | Maximum Quiescent       | $V_{IN} = V_{CC}$ or GND                      | 6.0V            |                      | 1.0    | 10                          | μА    |

|                 | Supply Current          | $I_{OUT} = 0 \mu A$                           | 9.0V            |                      | 2.0    | 20                          | μА    |

|                 |                         |                                               | 12.0V           |                      | 4.0    | 40                          | μΑ    |

Note 5: For a power supply of  $5V \pm 10\%$  the worst case on resistance ( $R_{ON}$ ) occurs for VHC at 4.5V. Thus the 4.5V values should be used when designing with this supply. Worst case  $V_{IH}$  and  $V_{IL}$  occur at  $V_{CC} = 5.5V$  and 4.5V respectively. (The  $V_{IH}$  value at 5.5V is 3.85V.) The worst case leakage current occurs for CMOS at the higher voltage and so the 5.5V values should be used.

Note 6: At supply voltages (V<sub>CC</sub> – GND) approaching 2V the analog switch on resistance becomes extremely non-linear. Therefore it is recommended that these devices be used to transmit digital only when using these supply voltages.

# **AC Electrical Characteristics**

$V_{CC} = 2.0V - 6.0V V_{EE} = 0V - 12V, C_L = 50 pF$  (unless otherwise specified)

| Symbol                                         | Parameter                   | Conditions                                       | V <sub>CC</sub>      | T <sub>A</sub> =2 | 25°C         | T <sub>A</sub> =-40 to 85°C | Units |

|------------------------------------------------|-----------------------------|--------------------------------------------------|----------------------|-------------------|--------------|-----------------------------|-------|

| Cyllibol                                       | rarameter                   | Conditions                                       | Typ Guaranteed Limit |                   | nteed Limits | - Onits                     |       |

| t <sub>PHL</sub> , t <sub>PLH</sub>            | Maximum Propagation         |                                                  | 3.3V                 | 25                | 30           | 20                          | ns    |

|                                                | Delay Switch In to Out      |                                                  | 4.5V                 | 5                 | 10           | 13                          | ns    |

|                                                |                             |                                                  | 9.0V                 | 4                 | 8            | 10                          | ns    |

|                                                |                             |                                                  | 12.0V                | 3                 | 7            | 11                          | ns    |

| t <sub>PZL</sub> , t <sub>PZH</sub>            | Maximum Switch Turn         | $R_L = 1 k\Omega$                                | 3.3V                 | 30                | 58           | 73                          | ns    |

|                                                | "ON" Delay                  |                                                  | 4.5V                 | 12                | 20           | 25                          | ns    |

|                                                |                             |                                                  | 9.0V                 | 6                 | 12           | 15                          | ns    |

|                                                |                             |                                                  | 12.0V                | 5                 | 10           | 13                          | ns    |

| t <sub>PHZ</sub> , t <sub>PLZ</sub>            | Maximum Switch Turn         | $R_L = 1 k\Omega$                                | 3.3V                 | 60                | 100          | 125                         | ns    |

| <sup>t</sup> PHZ <sup>,</sup> <sup>t</sup> PLZ | "OFF" Delay                 |                                                  | 4.5V                 | 25                | 36           | 45                          | ns    |

|                                                |                             |                                                  | 9.0V                 | 20                | 32           | 40                          | ns    |

|                                                |                             |                                                  | 12.0V                | 15                | 30           | 38                          |       |

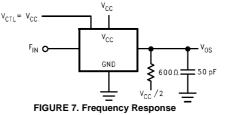

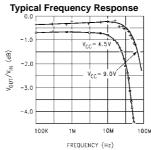

|                                                | Minimum Frequency           | $R_L = 600\Omega$                                | 4.5V                 | 40                |              |                             | MHz   |

|                                                | Response (Figure 7)         | $V_{IS} = 2 V_{PP}$ at $(V_{CC}/2)$              | 9.0V                 | 100               | .0           |                             | MHz   |

|                                                | $20 \log (V_O/V_I) = -3 dB$ | (Note 7)(Note 8)                                 |                      |                   | - 10         |                             |       |

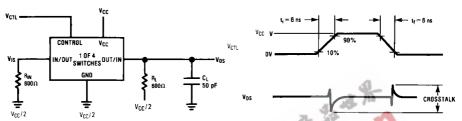

|                                                | Crosstalk Between           | $R_L = 600\Omega$ , $F = 1 MHz$                  |                      | 4.                | 200          |                             |       |

|                                                | any Two Switches            | (Note 8)(Note 9)                                 | 4.5V                 | -52               |              |                             | dB    |

|                                                | (Figure 8)                  |                                                  | 9.0V 🐔               | -50               |              |                             | dB    |

|                                                | Peak Control to Switch      | $R_L = 600\Omega$ , $F = 1 \text{ MHz}$          | 4.5V                 | 100               | 10           |                             | mV    |

|                                                | Feedthrough Noise           | C <sub>L</sub> = 50 pF                           | 9.0V                 | 250               |              |                             | mV    |

|                                                | (Figure 9)                  |                                                  |                      |                   |              |                             |       |

|                                                | Switch OFF Signal           | $R_L = 600\Omega$ , $F = 1 MHz$                  |                      |                   |              |                             |       |

|                                                | Feedthrough                 | $V_{(CT)}V_{IL}$                                 |                      |                   |              |                             |       |

|                                                | Isolation                   | (Note 8)(Note 9)                                 | 4.5V                 | -42               |              |                             | dB    |

|                                                | (Figure 10)                 |                                                  | 9.0V                 | -44               |              |                             | dB    |

| THD                                            | Total Harmonic              | $R_L = 10 \text{ k}\Omega, C_L = 50 \text{ pF},$ |                      |                   |              |                             |       |

|                                                | Distortion                  | F = 1 kHz                                        |                      |                   |              |                             |       |

|                                                | (Figure 11)                 | $V_{IS} = 4 V_{PP}$                              | 4.5V                 | .013              |              |                             | %     |

|                                                |                             | $V_{IS} = 8 V_{PP}$                              | 9.0V                 | .008              |              |                             | %     |

| C <sub>IN</sub>                                | Maximum Control             |                                                  |                      | 5                 | 10           | 10                          | pF    |

|                                                | Input Capacitance           |                                                  |                      |                   |              |                             |       |

| C <sub>IN</sub>                                | Maximum Switch              |                                                  |                      | 20                |              |                             | pF    |

|                                                | Input Capacitance           |                                                  |                      |                   |              |                             |       |

| C <sub>IN</sub>                                | Maximum Feedthrough         | V <sub>CTL</sub> = GND                           |                      | 0.5               |              |                             | pF    |

|                                                | Capacitance                 |                                                  |                      |                   |              |                             |       |

| C <sub>PD</sub>                                | Power Dissipation           |                                                  |                      | 15                |              |                             | pF    |

|                                                |                             |                                                  |                      |                   |              |                             |       |

3

Note 7: Adjust 0 dBm for F = 1 kHz (Null  $R_L/R_{ON}$  Attenuation).

Note 8:  $V_{IS}$  is centered at  $V_{CC}/2$ . Note 9: Adjust input for 0 dBm.

# **AC Test Circuits and Switching Time Waveforms** 1 OF 4 SWITCHES FIGURE 1. "ON" Resistance FIGURE 2. "OFF" Channel Leakage Current SWITCHES GND FIGURE 3. "ON" Channel Leakage Current 1 OF 4 O/ FIGURE 4. $t_{\text{PHL}}, t_{\text{PLH}}$ Propagation Delay Time Signal Input to Signal Output tpzL tpLZ 1/0 1 GF 4 O/ SWITCHES GND 10% FIGURE 5. $t_{\text{PZL}}$ , $t_{\text{PLZ}}$ Propagation Delay Time Control to Signal Output tpzh tpHZ 1/0 1 OF 4 O/ SWITCHES O/ GND FIGURE 6. $t_{\mbox{\scriptsize PZH}}, t_{\mbox{\scriptsize PHZ}}$ Propagation Delay Time Control to Signal Output

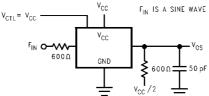

# AC Test Circuits and Switching Time Waveforms (Continued)

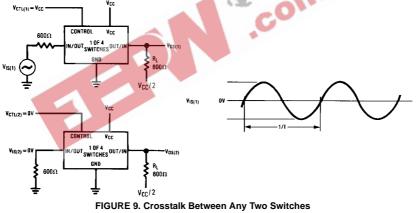

# **Crosstalk and Distortion Test Circuits**

FIGURE 8. Crosstalk: Control Input to Signal Output

FIGURE 9. Crosstalk Between Any Two Switches

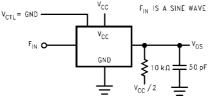

## **Crosstalk and Distortion Test Circuits** (Continued)

FIGURE 10. Switch OFF Signal Feedthrough Isolation

FIGURE 11. Sinewave Distortion

# **Typical Performance Characteristics**

# **Special Considerations**

In certain applications the external load-resistor current may include both  $V_{CC}$  and signal line components. To avoid drawing  $V_{CC}$  current when switch current flows into the analog switch input pins, the voltage drop across the switch must not exceed 0.6V (calculated from the ON Resistance).

# Physical Dimensions inches (millimeters) unless otherwise noted (Continued) -A-7.72 4.16 6.4 3.2 LAND PATTERN RECOMMENDATION PIN #1 IDENT. -0.90<sup>+0.15</sup> -C-L<sub>0.10±0.05</sub> 0.65 0.19 - 0.30 (+) 0.13(A) A B(S) C(S) 42.00°TOP & BOTTOM R0.09 min GAGE PLANE NOTES: A. CONFORMS TO JEDEC REGISTRATION MO-153 VARIATION AB-REF NOTE 6, DATED 7/93 B. DIMENSIONS ARE IN MILLIMETERS C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS D. DIMENSIONING AND TOLERANCES PER ANSI Y14.5M, 1982 0.25 SEATING PLANE DETAIL A MTC14revD 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide Package Number MTC14

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

9