#### ADVANCE INFORMATION

March 1996

# 74LVXC164245 16-Bit Dual Supply Configurable Voltage Interface Transceiver with TRI-STATE® Outputs

#### **General Description**

The LVXC164245 is a 48-pin dual-supply, 16-bit configurable voltage interface transceiver suited for PCMCIA and other real time configurable I/O applications. The V $_{\rm CCB}$  pin accepts a 5V supply level. The "B" port is a dedicated 5V port. The V $_{\rm CCA}$  pin accepts a 3V-to-5V supply level. The "A" port is configured to track the V $_{\rm CCA}$  supply level respectively. A 5V level on the V $_{\rm CC}$  pin will configure the I/O pins at a 5V level and a 3V V $_{\rm CC}$  will configure the I/O pins at a 3V level. This device will allow the V $_{\rm CCA}$  voltage source pin and I/O pins on the "A" port to float when  $\overline{\rm OE}$  is HIGH. This feature is necessary to buffer data to and from a PCMCIA socket that permits PCMCIA cards to be inserted and removed during normal operation.

#### **Features**

- Power up/down high impedance provides glitch-free bus loading

- $\blacksquare$  Allows A port and  $V_{CCA}$  to float simultaneously when  $\overline{OE}$  is HIGH

- Bidirectional interface between 5V and 3V-to-5V buses

- Inputs compatible with TTL level

- $\blacksquare$  Allow dual  $V_{CC}$  supplies power up/down easily when  $\overline{\text{OE}}$  is HIGH

- Guaranteed simultaneous switching noise level and dynamic threshold performance

- Available in SSOP and TSSOP packages

- Implements patented Quiet Series™ EMI reduction circuitry

- Flexible V<sub>CCA</sub> operating range

- Functionally compatible with the 74 series 16245

## **Logic Symbol**

| Pin Names                       | Description                      |  |

|---------------------------------|----------------------------------|--|

| ŌĒn                             | Output Enable Input (Active Low) |  |

| T/R <sub>n</sub>                | Transmit/Receive Input           |  |

| A <sub>0</sub> -A <sub>15</sub> | Side A Inputs/TRI-STATE Outputs  |  |

| B <sub>0</sub> -B <sub>15</sub> | Side B Inputs/TRI-STATE Outputs  |  |

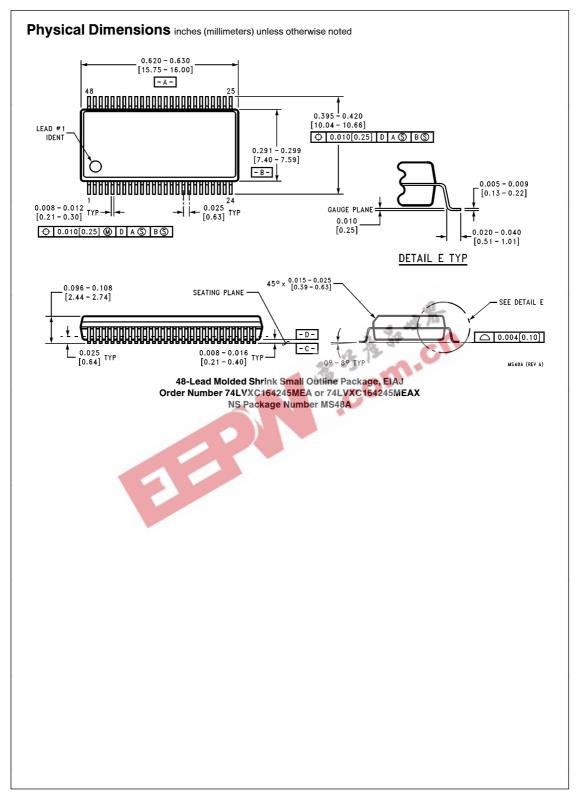

|                          | SSOP                                | TSSOP JEDEC                         |

|--------------------------|-------------------------------------|-------------------------------------|

| Order Number             | 74LVXC164245MEA<br>74LVXC164245MEAX | 74LVXC164245MTD<br>74LVXC164245MTDX |

| See NS Package<br>Number | MS48A                               | MTD48                               |

## Connection Diagram

TL/F/12535-2

### **Functional Description**

The LVXC164245 contains sixteen non-inverting bidirectional buffers with TRI-STATE outputs. The device is byte controlled with each byte functioning identically, but independent of the other. The control pins can be shorted together to obtain full 16-bit operation.

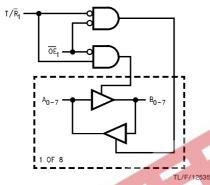

#### **Truth Tables**

| Inputs          |                    | Outputs                                                                       |

|-----------------|--------------------|-------------------------------------------------------------------------------|

| ŌĒ <sub>1</sub> | $T/\overline{R}_1$ | Outputo                                                                       |

| L               | L                  | Bus B <sub>0</sub> -B <sub>7</sub> Data to Bus A <sub>0</sub> -A <sub>7</sub> |

| L               | Н                  | Bus $A_0 - A_7$ Data to Bus $B_0 - B_7$                                       |

| Н               | Χ                  | HIGH-Z State on $A_0$ - $A_7$ , $B_0$ - $B_7$                                 |

H = High Voltage Level

L = Low Voltage Level

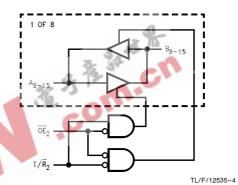

| Inputs            |                    | Outputs                                                                         |  |

|-------------------|--------------------|---------------------------------------------------------------------------------|--|

| $\overline{OE}_2$ | $T/\overline{R}_2$ | Guipais                                                                         |  |

| L                 | L                  | Bus B <sub>8</sub> -B <sub>15</sub> Data to Bus A <sub>8</sub> -A <sub>15</sub> |  |

| L                 | Н                  | Bus A <sub>8</sub> -A <sub>15</sub> Data to Bus B <sub>8</sub> -B <sub>15</sub> |  |

| Н                 | Х                  | HIGH-Z State on $A_8-A_{15}$ , $B_8-B_{15}$                                     |  |

X = Immaterial

Z = High Impedance

# **Logic Diagrams**

Please note that these diagrams are provided only for the understanding of logic operations and should not be used to estimate propagation delays.

# Physical Dimensions millimeters (Continued) 12.5 ± 0.1 -A-GAGE PLANE - 0.25 8.1 6.1 ± 0.1 -B-SEATING PLANE 00-80 4.05 $0.60^{\,+0.15}_{\,-0.10}$ DETAIL A △ 0.2 C B A TYPICAL ALL LEAD TIPS - SEE DETAIL A △ 0.1 C (0.90)ALL LEAD TIPS 1.1 MAX 0.09-0.20 TYP 0.10 ± 0.05 TYP 0.17 - 0.27 TYP ⊕ | 0.13 M | A | B S | C S | MTD48 (REV A) 48-Lead Molded Thin Shrink Small Outline Package, JEDEC, 6.1 mm Body Width Order Number 74LVXC164245MTD or 74LVXC164245MTDX NS Package Number MTD48

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.