74ABT5074

#### **FEATURES**

- Metastable immune characteristics

- Pin compatible with 74F74 and 74F5074

- Typical f<sub>MAX</sub> = 200MHz

- Output skew guaranteed less than 2.0ns

- High source current (I<sub>OH</sub> = 15mA) ideal for clock driver applications

- Output capability: +20mA/–15mA

- Latch-up protection exceeds 500mA per Jedec JC40.2 Std 17

- ESD protection exceeds 2000V per MIL STD 883 Method 3015 and 200V per Machine Model

#### **DESCRIPTION**

The 74ABT5074 is a dual positive edge-triggered D-type flip-flop featuring individual data, clock, set and reset inputs; also true and complementary outputs.

Set ( $\overline{S}Dn$ ) and reset ( $\overline{R}Dn$ ) are asynchronous active low inputs and operate independently of the clock (CPn) input. Data must be stable just one setup time prior to the low-to-high transition of the clock for guaranteed propagation delays.

Clock triggering occurs at a voltage level and is not directly related to the transition time of the positive-going pulse. Following the hold time interval, data at the Dn input may be changed without affecting the levels of the output.

The 74ABT5074 is designed so that the outputs can never display a metastable state due to setup and hold time violations. If setup time and hold time are violated the propagation delays may be extended beyond the specifications but the outputs will not glitch or display a metastable state. Typical metastability parameters for the 74ABT5074 are:

$$\tau \cong 94 ps$$

and  $T_o \cong 1.3 \times 10^7 \, sec$

where  $\tau$  represents a function of the rate at which a latch in a metastable state resolves that condition and  $T_0$  represents a function of the measurement of the propensity of a latch to enter a metastable state.

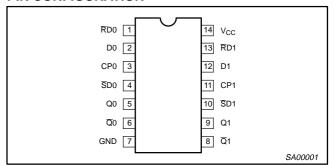

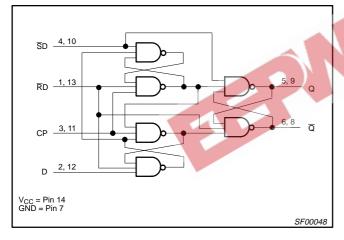

#### PIN CONFIGURATION

#### PIN DESCRIPTION

| PIN NUMBER | SYMBOL                 | NAME AND FUNCTION                        |

|------------|------------------------|------------------------------------------|

| 2, 12      | D0, D1                 | Data inputs                              |

| 3, 11      | CP0, CP1               | Clock inputs (active rising edge)        |

| 4, 10      | SD0, SD1               | Set inputs (active-Low)                  |

| 1, 13      | RD0, RD1               | Reset inputs (active-Low)                |

| 5, 9       | Q0, Q1                 | Data outputs (active-Low), non-inverting |

| 6, 8       | <b>Q</b> 0, <b>Q</b> 1 | Data outputs (active-Low), inverting     |

| 7          | GND                    | Ground (0V)                              |

| 14         | V <sub>CC</sub>        | Positive supply voltage                  |

### **QUICK REFERENCE DATA**

| SYMBOL                               | PARAMETER                            | CONDITIONS<br>T <sub>amb</sub> = 25°C; GND = 0V | TYPICAL    | UNIT |

|--------------------------------------|--------------------------------------|-------------------------------------------------|------------|------|

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>CPn to Qn or Qn | $C_L = 50pF; V_{CC} = 5V$                       | 2.8<br>2.4 | ns   |

| C <sub>IN</sub>                      | Input capacitance                    | $V_I = 0V$ or $V_{CC}$                          | 3          | pF   |

| I <sub>CC</sub>                      | Total supply current                 | Outputs disabled; V <sub>CC</sub> =5.5V         | 2          | μΑ   |

## **ORDERING INFORMATION**

| PACKAGES                                                | TEMPERATURE RANGE | ORDER CODE  | DRAWING NUMBER |

|---------------------------------------------------------|-------------------|-------------|----------------|

| 14-pin plastic DIP                                      | −40°C to +85°C    | 74ABT5074N  | SOT27-1        |

| 14-pin plastic SOL                                      | −40°C to +85°C    | 74ABT5074D  | SOT108-1       |

| 14-pin plastic shrink small outline SSOP Type II        | −40°C to +85°C    | 74ABT5074DB | SOT337-1       |

| 14-pin plastic thin shrink small outline (TSSOP) Type I | −40°C to +85°C    | 74ABT5074PW | SOT402-1       |

74ABT5074

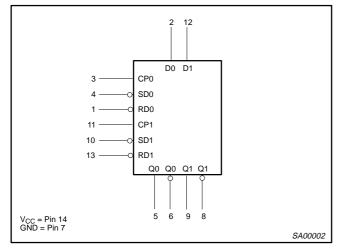

# **LOGIC SYMBOL**

### **IEC/IEEE SYMBOL**

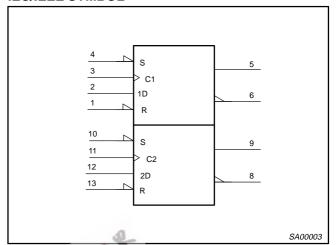

# **LOGIC DIAGRAM**

# **FUNCTION TABLE**

| -  | INPUTS |    | OUTF | PUTS | OPERATING |                    |

|----|--------|----|------|------|-----------|--------------------|

| SD | RD     | СР | D    | Q    | Q         | MODE               |

| L  | Η      | Х  | Х    | Н    | L         | Asynchronous set   |

| Н  | ┙      | Х  | Х    | L    | Н         | Asynchronous reset |

| L  | L      | Х  | Х    | L    | Н         | Undetermined*      |

| Н  | Н      | 1  | h    | Н    | L         | Load "1"           |

| Н  | Η      | 1  | Ī    | L    | Н         | Load "0"           |

| Н  | Η      | 1  | Х    | NC   | NC        | Hold               |

## NOTES:

H = High voltage level

h = High voltage level one setup time prior to low-to-high clock transition

L = Low voltage level

Low voltage level one setup time prior to low-to-high clock transition

NC= No change from the previous setup

X = Don't care

= Low-to-high clock transition

↑ = Not low-to-high clock transition

This setup is unstable and will change when either set or reset return to the high level

74ABT5074

#### METASTABLE IMMUNE CHARACTERISTICS

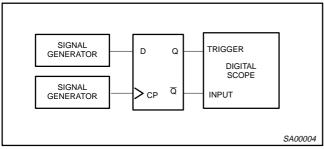

Philips Semiconductors uses the term 'metastable immune' to describe characteristics of some of the products in its family. By running two independent signal generators (see Figure 1) at nearly the same frequency (in this case 10MHz clock and 10.02MHz data) the device-under-test can often be driven into a metastable state. If the Q output is then used to trigger a digital scope set to infinite persistence the  $\overline{\mathbf{Q}}$  output will build a waveform. An experiment was run by continuously operating the devices in the region where metastability will occur.

Figure 1. Test Setup

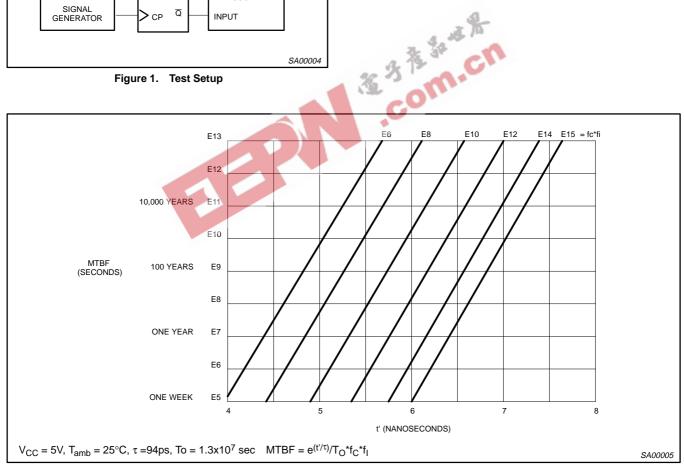

After determining the  $T_0$  and  $\tau$  of the flop, calculating the mean time between failures (MTBF) is simple. Suppose a designer wants to use the 74ABT5074 for synchronizing asynchronous data that is arriving at 10MHz (as measured by a frequency counter), has a clock frequency of 50MHz, and has decided that he would like to sample the output of the 74ABT5074 7 nanoseconds after the clock edge. He simply plugs his number into the following equation:

$$MTBF = e^{(t'/\tau)}/T_O^*f_C^*f_I$$

In this formula, f<sub>C</sub> is the frequency of the clock, f<sub>I</sub> is the average input event frequency, and t' is the time after the clock pulse that the output is sampled (t' > h, h being the normal propagation delay). In this situation the f<sub>I</sub> will be twice the data frequency of 20 MHz because input events consist of both of low and high transitions. Multiplying f<sub>1</sub> by f<sub>2</sub> gives an answer of 10<sup>15</sup> Hz<sup>2</sup>. From Figure 2 it is clear that the MTBF is greater than  $10^{10}$  seconds. Using the above formula the actual MTBF is  $1.69 \times 10^{10}$  seconds or about 535 years.

Figure 2. Mean Time Between Failures (MTBF) versus t'

74ABT5074

# TYPICAL VALUES FOR $\tau$ AND $T_{0}$ AT VARIOUS $V_{CC}S$ AND TEMPERATURES

| V               | T <sub>amb</sub> = -40°C |                               | ,     | T <sub>amb</sub> = 25°C       | T <sub>amb</sub> = 85°C |                               |  |

|-----------------|--------------------------|-------------------------------|-------|-------------------------------|-------------------------|-------------------------------|--|

| V <sub>CC</sub> | τ                        | T <sub>0</sub>                | τ     | T <sub>0</sub>                | τ                       | T <sub>0</sub>                |  |

| 5.5V            | 84ps                     | $1.0 \times 10^6  \text{sec}$ | 93ps  | $3.8 \times 10^6 \text{ sec}$ | 89ps                    | 1.5 × 10 <sup>9</sup> sec     |  |

| 5.0V            | 84ps                     | $2.7 \times 10^8 \text{ sec}$ | 94ps  | $1.3 \times 10^7 \text{ sec}$ | 106ps                   | $2.2 \times 10^6 \text{ sec}$ |  |

| 4.5V            | 89ps                     | 1.0 × 10 <sup>9</sup> sec     | 103ps | 2.1 × 10 <sup>7</sup> sec     | 115ps                   | 4.4 × 10 <sup>6</sup> sec     |  |

# ABSOLUTE MAXIMUM RATINGS1, 2

| SYMBOL           | PARAMETER                      | CONDITIONS                  | RATING       | UNIT |

|------------------|--------------------------------|-----------------------------|--------------|------|

| V <sub>CC</sub>  | DC supply voltage              |                             | -0.5 to +7.0 | V    |

| I <sub>IK</sub>  | DC input diode current         | V <sub>I</sub> < 0          | -18          | mA   |

| VI               | DC input voltage <sup>3</sup>  |                             | -1.2 to +7.0 | V    |

| I <sub>OK</sub>  | DC output diode current        | V <sub>O</sub> < 0          | -50          | mA   |

| V <sub>OUT</sub> | DC output voltage <sup>3</sup> | Output in Off or High state | -0.5 to +5.5 | V    |

| I <sub>OUT</sub> | DC output current              | Output in Low state         | 40           | mA   |

| T <sub>stg</sub> | Storage temperature range      | 1 % 2                       | -65 to 150   | °C   |

# RECOMMENDED OPERATING CONDITIONS

| CVMDOL           | PARAMETER                            |     | LIMITS                                                             |      |  |

|------------------|--------------------------------------|-----|--------------------------------------------------------------------|------|--|

| SYMBOL           | PARAMETER                            | MIN | LIMITS      MAX      5.5      V <sub>CC</sub> 0.8      −15      20 | UNIT |  |

| V <sub>CC</sub>  | DC supply voltage                    | 4.5 | 5.5                                                                | V    |  |

| VI               | Input voltage                        | 0   | V <sub>CC</sub>                                                    | V    |  |

| V <sub>IH</sub>  | High-level input voltage             | 2.0 |                                                                    | V    |  |

| V <sub>IL</sub>  | Low-level Input voltage              |     | 0.8                                                                | ٧    |  |

| I <sub>OH</sub>  | High-level output current            |     | -15                                                                | mA   |  |

| l <sub>OL</sub>  | Low-level output current             |     | 20                                                                 | mA   |  |

| Δt/Δν            | Input transition rise or fall rate   | 0   | 10                                                                 | ns/V |  |

| T <sub>amb</sub> | Operating free-air temperature range | -40 | +85                                                                | °C   |  |

Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the Stesses beyond those isset may cause perhanent damage to the device. These are stess ratings only and turctional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150°C.

The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

74ABT5074

# DC ELECTRICAL CHARACTERISTICS

| SYMBOL           | PARAMETER                                            | TEST CONDITIONS                                                     | T <sub>amb</sub> = +25°C |       |      | $T_{amb} = -40^{\circ}C \text{ to } +85^{\circ}C$ |      | UNIT |

|------------------|------------------------------------------------------|---------------------------------------------------------------------|--------------------------|-------|------|---------------------------------------------------|------|------|

|                  |                                                      |                                                                     | MIN                      | TYP   | MAX  | MIN                                               | MAX  |      |

| V <sub>IK</sub>  | Input clamp voltage                                  | $V_{CC} = 4.5V; I_{IK} = -18mA$                                     |                          | -0.9  | -1.2 |                                                   | -1.2 | V    |

| V <sub>OH</sub>  | High-level output voltage                            | $V_{CC}$ = 4.5V; $I_{OH}$ = -15mA; $V_{I}$ = $V_{IL}$ or $V_{IH}$   | 2.5                      | 2.9   |      | 2.5                                               |      | V    |

| V <sub>OL</sub>  | Low-level output voltage                             | $V_{CC}$ = 4.5V; $I_{OL}$ = 20mA; $V_{I}$ = $V_{IL}$ or $V_{IH}$    |                          | 0.35  | 0.5  |                                                   | 0.5  | V    |

| lı               | Input leakage current                                | $V_{CC} = 5.5V$ ; $V_I = GND \text{ or } 5.5V$                      |                          | ±0.01 | ±1.0 |                                                   | ±1.0 | μΑ   |

| l <sub>OFF</sub> | Power-off leakage current                            | $V_{CC}$ = 0.0V; $V_{O}$ or $V_{I} \le 4.5V$                        |                          | ±5.0  | ±100 |                                                   | ±100 | μΑ   |

| ΙO               | Output current <sup>1</sup>                          | $V_{CC} = 5.5V; V_O = 2.5V$                                         | -50                      | -75   | -180 | -50                                               | -180 | mA   |

| I <sub>CC</sub>  | Quiescent supply current                             | $V_{CC} = 5.5V$ ; $V_I = GND$ or $V_{CC}$                           |                          | 2     | 50   |                                                   | 50   | μΑ   |

| Δl <sub>CC</sub> | Additional supply current per input pin <sup>2</sup> | $V_{CC}$ = 5.5V; one input at 3.4V, other inputs at $V_{CC}$ or GND |                          | 0.25  | 500  |                                                   | 500  | μΑ   |

- Not more than one output should be tested at a time, and the duration of the test should not exceed one second.

This is the increase in supply current for each input at 3.4V.

# **AC CHARACTERISTICS**

GND = 0V,  $t_R = t_F = 2.5$ ns,  $C_L = 50$ pF,  $R_L = 500\Omega$

|                                      |                                                |          | LIMITS                                              |            |            |                                                                  |            |      |

|--------------------------------------|------------------------------------------------|----------|-----------------------------------------------------|------------|------------|------------------------------------------------------------------|------------|------|

| SYMBOL                               | PARAMETER                                      | WAVEFORM | T <sub>amb</sub> = +25°C<br>V <sub>CC</sub> = +5.0V |            |            | T <sub>amb</sub> = -40 to +85°C<br>V <sub>CC</sub> = +5.0V ±0.5V |            | UNIT |

|                                      |                                                |          | MIN                                                 | TYP        | MAX        | MIN                                                              | MAX        |      |

| f <sub>max</sub>                     | Maximum clock frequency                        | 1        | 180                                                 | 250        |            | 150                                                              |            | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>CPn to Qn or Qn           | 1        | 1.0<br>1.0                                          | 2.8<br>2.4 | 3.9<br>3.5 | 1.0<br>1.0                                                       | 4.5<br>3.7 | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>SDn, RDn to Qn or Qn      | 2        | 1.0<br>1.0                                          | 3.5<br>3.1 | 4.6<br>4.2 | 1.0<br>1.0                                                       | 5.5<br>4.7 | ns   |

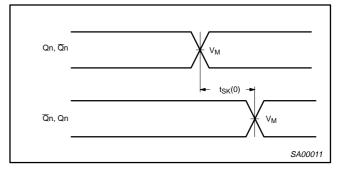

| t <sub>sk(o)</sub>                   | Output skew <sup>1, 2</sup><br>CPn to Qn to Qn | 4        |                                                     |            | 1.5        |                                                                  | 2.0        | ns   |

- | t<sub>PN</sub> actual t<sub>PM</sub> actual | for any output compared to any other output where N and M are either LH or HL.

Skew times are valid only under same test conditions (temperature, V<sub>CC</sub>, loading, etc.).

## **AC SETUP REQUIREMENTS**

GND = 0V,  $t_R$  =  $t_F$  = 2.5ns,  $C_L$  = 50pF,  $R_L$  = 500 $\Omega$

| SYMBOL                                   | PARAMETER                            | WAVEFORM | T <sub>amb</sub> =<br>V <sub>CC</sub> = | +25°C<br>+5.0V | $T_{amb} = -40 \text{ to } +85^{\circ}\text{C}$<br>$V_{CC} = +5.0\text{V} \pm 0.5\text{V}$ | UNIT |

|------------------------------------------|--------------------------------------|----------|-----------------------------------------|----------------|--------------------------------------------------------------------------------------------|------|

|                                          |                                      |          | MIN                                     | TYP            | MIN                                                                                        |      |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup time, High or Low<br>Dn to CPn | 1        | 2.5<br>2.5                              | 1.5<br>1.5     | 2.5<br>2.5                                                                                 | ns   |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold time, High or Low<br>Dn to CPn  | 1        | 0<br>0                                  | -1.4<br>-1.4   | 0<br>0                                                                                     | ns   |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | CPn pulse width,<br>high or low      | 1        | 1.5<br>2.4                              | 0.6<br>1.8     | 1.5<br>2.9                                                                                 | ns   |

| t <sub>w</sub> (L)                       | SDn or RDn pulse width, low          | 2        | 2.0                                     | 1.3            | 2.2                                                                                        | ns   |

| t <sub>rec</sub>                         | Recovery time<br>SDn or RDn to CPn   | 3        | 2.4                                     | 1.3            | 2.8                                                                                        | ns   |

74ABT5074

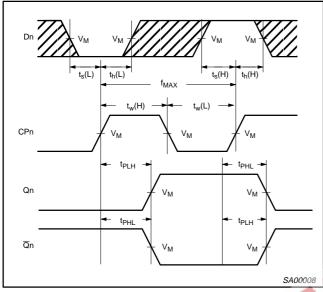

# **AC WAVEFORMS**

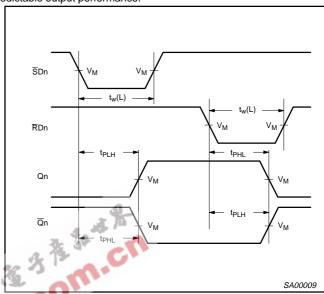

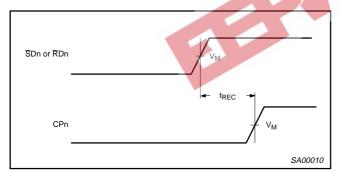

$V_{M}$  = 1.5V,  $V_{IN}$  = GND to 3.0V The shaded areas indicate when the input is permitted to change for the predictable output performance.

Waveform 1. Propagation Delay for Data to Output, Data Setup Time and Hold Time, and Clock Width

Waveform 2. Propagation Delay for Set and Reset to Output, Set and Reset Pulse Width

Waveform 3. Recovery Time for Set or Reset to Output

Waveform 4. Output Skew

SA00058

# Synchronizing dual D-type flip-flop with metastable immune characteristics

# 74ABT5074

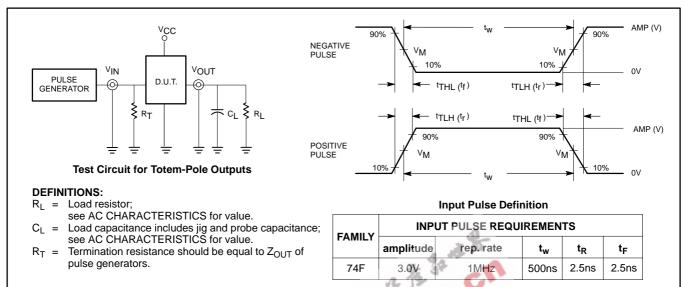

### **TEST CIRCUIT AND WAVEFORM**