July 1988 Revised September 2000

# 74ACT818 8-Bit Diagnostic Register

## **General Description**

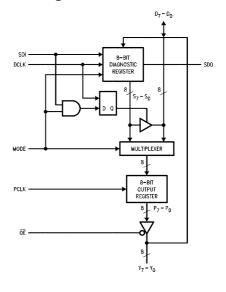

The ACT818 is a high-speed, general-purpose pipeline register with an on-board diagnostic register for performing serial diagnostics and/or writable control store loading.

The D-to-Y path provides an 8-bit parallel data path pipeline register for normal system operation. The diagnostic register can load parallel data to or from the pipeline register and can output data through the D input port (as in WCS loading).

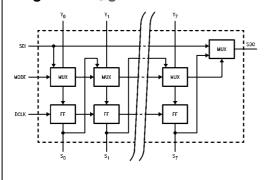

The 8-bit diagnostic register has multiplexer inputs that select parallel inputs from the Y-port or adjacent bits in the diagnostic register to operate as a right-shift-only register. This register can then participate in a serial loop throughout the system where normal data, address, status and control registers are replaced with ACT818 diagnostic pipeline registers. The loop can be used to scan in a complete test routine starting point (Data, Address, etc.). Then after a specified number of machine cycles it scans out the results to be inspected for the expected results. WCS loading can be accomplished using the same technique. An instruction word can be serially shifted into the shadow register and written into the WCS RAM by enabling the D output.

#### **Features**

- On-line and off-line system diagnostics

- Swaps the contents of diagnostic register and output register

- Diagnostic register and diagnostic testing

- Cascadable for wide control words as used in microprogramming

- Edge-triggered D registers

- Outputs source/sink 24 mA

- ACT818 has TTL-compatible inputs

- ACT818 is functionally- and pin-compatible to AMD Am29818 and MMI 74S818

#### Applications

- Register for microprogram control store

- Status register

- Data register

- Instruction register

- Interrupt mask register

- · Pipeline register

- General purpose register

- Parallel-serial/serial-parallel converter

#### **Ordering Code:**

| Order Number Order Package |      | Package Description                                                   |  |  |  |  |

|----------------------------|------|-----------------------------------------------------------------------|--|--|--|--|

|                            | ,    | 5 .                                                                   |  |  |  |  |

| 74ACT818SPC                | N24C | 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |  |  |  |  |

## **Logic Symbol**

#### **Connection Diagram**

FACT™ is a trademark of Fairchild Semiconductor Corporation

# **Pin Descriptions**

| Pin Names                      | Description             |

|--------------------------------|-------------------------|

| D <sub>0</sub> -D <sub>7</sub> | Data Inputs             |

| SDI                            | Serial Data Input       |

| DCLK                           | Diagnostics Clock       |

| MODE                           | Control Input           |

| PCLK                           | Pipeline Register Clock |

| OEY                            | Output Enable Input     |

| SDO                            | Serial Data Output      |

| Y <sub>0</sub> -Y <sub>7</sub> | Data Outputs            |

## **Functional Description**

Data transfers into the diagnostic register occur on the LOW-to-HIGH transition of DCLK. Mode and SDI determine what data source will be loaded. The pipeline register is loaded on the LOW-to-HIGH transition of PCLK. Mode selects whether the data source is the data input or the diagnostic register output. Because of the independence of the clock inputs, data can be shifted in the diagnostic register via DCLK and loaded into the pipeline register from the data input via PCLK simultaneously, as long as no setup or hold times are violated. This simultaneous operation is

## **Function Table**

| Inputs |      |      | Outputs | 3   | Operation                                                                                            |                                                            |                                                       |

|--------|------|------|---------|-----|------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------|

| SDI    | MODE | DCLK | PCLK    | SDO | Diagnostic Reg.                                                                                      | Pipeline Reg.                                              | Operation                                             |

| Χ      | L    | \    | Х       | S7  | SI <si 1,<="" td="" –=""><td>NA</td><td>Serial Shift; D<sub>7</sub>-D<sub>0</sub> Disabled</td></si> | NA                                                         | Serial Shift; D <sub>7</sub> -D <sub>0</sub> Disabled |

|        |      |      |         |     | SO <sd<sub>I</sd<sub>                                                                                | 12 19                                                      | G                                                     |

| Χ      | L    | X    |         | S7  | NA                                                                                                   | PI <di< td=""><td>Normal Load Pipeline Register</td></di<> | Normal Load Pipeline Register                         |

| L      | Н    | \    | Х       | L   | SI <yi< td=""><td>NA</td><td>Load Diagnostic Register from Y;</td></yi<>                             | NA                                                         | Load Diagnostic Register from Y;                      |

|        |      |      |         |     |                                                                                                      | C                                                          | DI Disabled                                           |

| Х      | Н    | Х    | ~       | SDI | NA                                                                                                   | ●PI <si< td=""><td>Load Pipeline Register from</td></si<>  | Load Pipeline Register from                           |

|        |      |      |         |     |                                                                                                      |                                                            | Diagnostic Register                                   |

| Н      | Н    | ~    | X       | H   | Hold                                                                                                 | NA                                                         | Hold Diagnostic Register; DI                          |

|        |      |      |         |     |                                                                                                      |                                                            | Enabled                                               |

- H = HIGH Voltage Level

L = LOW Voltage Level

- X = Immaterial

∠ = LOW-to-HIGH Clock Transition

## **Diagnostic Register**

# **Block Diagram**

# **Absolute Maximum Ratings**(Note 1)

#### **Recommended Operating Conditions**

Supply Voltage (V<sub>CC</sub>) DC Input Diode Current (I<sub>IK</sub>) -0.5V to +7.0V

$V_1 = -0.5V$ -20 mA  $V_{I} = V_{CC} + 0.5V$ +20 mA

DC Input Voltage (V<sub>I</sub>) -0.5V to  $V_{CC}$  +0.5V

DC Output Diode Current ( $I_{OK}$ )

$V_O = -0.5V$ -20 mA  $V_O = V_{CC} + 0.5V$ +20 mA -0.5 V to  $\text{V}_{\text{CC}} + 0.5 \text{V}$

DC Output Voltage (V<sub>O</sub>)

DC Output Source

or Sink Current (I<sub>O</sub>) ± 50 mA

DC V<sub>CC</sub> or Ground Current

per Output Pin (I <sub>CC</sub> or I<sub>GND</sub>)  $\pm$  50 mA

Storage Temperature (T<sub>STG</sub>) -65°C to +150°C

Junction Temperature (T<sub>J</sub>)

PDIP 140°C Supply Voltage (V<sub>CC</sub>) 4.5V to 5.5V Input Voltage (V<sub>I</sub>) 0V to  $V_{\mbox{\footnotesize CC}}$ 0V to V<sub>CC</sub> Output Voltage (V<sub>O</sub>) -40°C to +85°C Operating Temperature (T<sub>A</sub>) Minimum Input Edge Rate (ΔV/Δt) 125 mV/ns

V<sub>IN</sub> from 0.8V to 2.0V V<sub>CC</sub> @ 4.5V, 5.5V

**Note 1:** Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, with-

#### **DC Electrical Characteristics**

| Symbol           | Parameter                                             | V <sub>CC</sub> T <sub>A</sub> = |     | +25°C               | T <sub>A</sub> = -40°C to +85°C | Units | Conditions                             |  |

|------------------|-------------------------------------------------------|----------------------------------|-----|---------------------|---------------------------------|-------|----------------------------------------|--|

| Symbol           | Parameter                                             | (V)                              | Тур | yp Guaranteed Limit |                                 | Units |                                        |  |

| V <sub>IH</sub>  | Minimum HIGH Level                                    | 4.5                              | 1.5 | 2.0                 | 2.0                             | V     | V <sub>OUT</sub> = 0.1V                |  |

|                  | Input Voltage                                         | 5.5                              | 1.5 | 2.0                 | 2.0                             | V     | or V <sub>CC</sub> – 0.1V              |  |

| V <sub>IL</sub>  | Maximum LOW Level                                     | 4.5                              | 1.5 | 0.8                 | 0.8                             | V     | V <sub>OUT</sub> = 0.1V                |  |

|                  | Input Voltage                                         | 5.5                              | 1.5 | 0.8                 | 0.8                             | · ·   | or V <sub>CC</sub> – 0.1V              |  |

| I <sub>IN</sub>  | Maximum Input Leakage Current                         | 5.5                              |     | ± 0.1               | ± 1.0                           | μΑ    | $V_{IN} = V_{CC}$                      |  |

| loz              | Maximum 3-STATE                                       | A                                |     |                     |                                 |       | OE = V <sub>IH</sub>                   |  |

|                  | Leakage Current                                       | 5.5                              |     | ± 0.5               | ± 5.0                           | μΑ    | V <sub>OUT</sub> = 0V, V <sub>CC</sub> |  |

| I <sub>CC</sub>  | Maximum Quiescent Supply Current                      | 5.5                              |     | 8.0                 | 80.0                            | μΑ    | $V_{IN} = V_{CC}$ or GND               |  |

| I <sub>CCT</sub> | Maximum Additional                                    | 5.5                              |     |                     | 1.5                             | mA    | $V_{IN} = V_{CC} - 2.1V$               |  |

|                  | I <sub>CC</sub> /Input                                | 5.5                              |     |                     | 1.5                             | mA    | $V_{CC} = 5.5V$                        |  |

| V <sub>OH</sub>  | Minimum HIGH                                          |                                  |     |                     |                                 |       | $V_{IN} = V_{IL} \text{ or } V_{IH}$   |  |

|                  | Level Output Voltage,                                 | 4.5                              |     | 3.86                | 3.76                            | V     | $I_{OH} = -24 \text{ mA}$              |  |

|                  | Y <sub>0</sub> –Y <sub>7</sub> Outputs                | 5.5                              |     | 4.86                | 4.76                            | V     | I <sub>OH</sub> =-24 mA (Note 2)       |  |

|                  | Minimum HIGH                                          |                                  |     |                     |                                 |       |                                        |  |

|                  | Level Output Voltage,                                 | 4.5                              |     | 3.86                | 3.76                            | V     | $I_{OH} = -8 \text{ mA}$               |  |

|                  | D <sub>0</sub> -D <sub>7</sub> , SDO Outputs          | 5.5                              |     | 4.86                | 4.76                            | V     | $I_{OH} = -8 \text{ mA}$               |  |

| V <sub>OL</sub>  | Maximum LOW                                           |                                  |     |                     |                                 |       | $V_{IN} = V_{IL} \text{ or } V_{IH}$   |  |

|                  | Level Output Voltage,                                 | 4.5                              |     | 0.36                | 0.44                            | V     | $I_{OL} = 24 \text{ mA}$               |  |

|                  | Y <sub>0</sub> –Y <sub>7</sub> Outputs                | 5.5                              |     | 0.36                | 0.44                            | V     | I <sub>OL</sub> = 24 mA (Note 2)       |  |

|                  | Maximum LOW Level Output Voltage,                     | 4.5                              |     | 0.36                | 0.44                            | V     | $I_{OL} = 8 \text{ mA}$                |  |

|                  | D <sub>0</sub> –D <sub>7</sub> , SDO Outputs          | 5.5                              |     | 0.36                | 0.44                            | V     | $I_{OL} = 8 \text{ mA}$                |  |

| I <sub>OLD</sub> | Minimum Dynamic Output Current                        | 5.5                              |     |                     | 75                              | mA    | V <sub>OLD</sub> = 1.65V Max           |  |

|                  | Y <sub>0</sub> –Y <sub>7</sub> Outputs                | 0.0                              |     |                     | 70                              | 110.4 | VOLD = 1.00 V Max                      |  |

| I <sub>OHD</sub> | Minimum Dynamic Output Current                        | 5.5                              |     |                     | -75                             | mA    | V <sub>OHD</sub> = 3.85V Min           |  |

|                  | Y <sub>0</sub> –Y <sub>7</sub> Outputs                |                                  |     |                     |                                 | 110 ( | VOHD = 0.00 V WIII                     |  |

| I <sub>OLD</sub> | Minimum Dynamic Output Current                        | 5.5                              |     |                     | 32                              | mA    | V <sub>OLD</sub> = 1.65V Max           |  |

|                  | D <sub>0</sub> -D <sub>7</sub> , SDO Outputs (Note 3) | 0.0                              |     |                     | 02                              |       | - OLD 1100 T III MAT                   |  |

| I <sub>OHD</sub> | Minimum Dynamic Output Current                        | 5.5                              |     |                     | -32                             | mA    | V <sub>OHD</sub> = 3.85V Min           |  |

| יטחט.            | D <sub>0</sub> -D <sub>7</sub> , SDO Outputs (Note 3) | 2.0                              |     |                     | 32                              |       | - OUD 2:237 HIII                       |  |

Note 2: All outputs loaded; thresholds on input associated with output under test.

Note 3: Test load 50 pF,  $500\Omega$  to ground.

|                  |                                              | V <sub>CC</sub> |                        | $T_A = +25^{\circ}C$ |      | T <sub>A</sub> = -40°  | C to +85°C |      |

|------------------|----------------------------------------------|-----------------|------------------------|----------------------|------|------------------------|------------|------|

| Symbol           | Parameter                                    | (V)             | C <sub>L</sub> = 50 pF |                      |      | C <sub>L</sub> = 50 pF |            | Unit |

|                  |                                              | (Note 4)        | Min                    | Тур                  | Max  | Min                    | Max        |      |

| t <sub>PHL</sub> | Propagation Delay PCLK to Y                  | 5.0             | 3.0                    | 6.0                  | 9.0  | 2.5                    | 9.5        | ns   |

| t <sub>PLH</sub> | Propagation Delay PCLK to Y                  | 5.0             | 3.0                    | 6.5                  | 9.0  | 2.5                    | 10.0       | ns   |

| t <sub>PHL</sub> | Propagation Delay MODE to SDO                | 5.0             | 4.0                    | 8.0                  | 11.0 | 3.5                    | 12.0       | ns   |

| <sup>t</sup> PLH | Propagation Delay MODE to SDO                | 5.0             | 4.0                    | 8.0                  | 11.5 | 4.0                    | 12.5       | ns   |

| t <sub>PHL</sub> | Propagation Delay<br>SDI to SDO              | 5.0             | 3.5                    | 7.5                  | 10.5 | 3.0                    | 12.0       | ns   |

| t <sub>PLH</sub> | Propagation Delay SDI to SDO                 | 5.0             | 3.5                    | 7.5                  | 10.5 | 3.5                    | 12.0       | ns   |

| t <sub>PHL</sub> | Propagation Delay DCLK to SDO                | 5.0             | 4.5                    | 9.0                  | 12.5 | 4.0                    | 14.0       | ns   |

| t <sub>PLH</sub> | Propagation Delay DCLK to SDO                | 5.0             | 4.5                    | 9.5                  | 13.0 | 4.0                    | 14.5       | ns   |

| t <sub>PZL</sub> | Output Enable Time OEY to Yn                 | 5.0             | 2.5                    | 6.0                  | 9.0  | 2.5                    | 10.0       | ns   |

| <sup>t</sup> PLZ | Output Disable Time OEY to Yn                | 5.0             | 1.5                    | 5.5                  | 8.0  | 1.0                    | 9.0        | ns   |

| <sup>†</sup> PZL | Output Enable Time<br>DCLK to D <sub>n</sub> | 5.0             | 3.0                    | 8.0                  | 12.0 | 3.0                    | 13.5       | ns   |

| t <sub>PLZ</sub> | Output Disable Time DCLK to D <sub>n</sub>   | 5.0             | 2.0                    | 8.5                  | 11.0 | 1.5                    | 12.0       | ns   |

| <sup>t</sup> PZH | Output Enable Time OEY to Yn                 | 5.0             | 3.0                    | 8.0                  | 10.0 | 2.5                    | 11.0       | ns   |

| t <sub>PHZ</sub> | Output Disable Time OEY to Yn                | 5.0             | 2.5                    | 9.0                  | 11.0 | 2.0                    | 11.5       | ns   |

| t <sub>PZH</sub> | Output Enable Time DCLK to Dn                | 5.0             | 3.0                    | 6.5                  | 11.5 | 3.0                    | 13.0       | ns   |

| t <sub>PHZ</sub> | Output Disable Time DCLK to Dn               | 5.0             | 3.0                    | 7.5                  | 12.0 | 2.0                    | 13.0       | ns   |

Note 4: Voltage Range 5.0 is 5.0V ± 0.5V.

# **AC Operating Requirements**

|                |                                 | V <sub>CC</sub> | $T_A = +25^{\circ}C$    |       | $T_A = -40^{\circ}C$ to $+85^{\circ}C$ |       |

|----------------|---------------------------------|-----------------|-------------------------|-------|----------------------------------------|-------|

| Symbol         | Parameter                       | (V)             | <b>C</b> <sub>L</sub> = | 50 pF | C <sub>L</sub> = 50 pF                 | Units |

|                |                                 | (Note 5)        | Тур                     | Gua   | aranteed Minimum                       |       |

| t <sub>S</sub> | Setup Time D to PCLK            | 5.0             | 1.0                     | 4.0   | 5.0                                    | ns    |

| t <sub>H</sub> | Hold Time D to PCLK             | 5.0             | 0.0                     | 1.0   | 1.0                                    | ns    |

| t <sub>H</sub> | Setup Time<br>MODE to PCLK      | 5.0             | 2.5                     | 4.5   | 5.5                                    | ns    |

| t <sub>H</sub> | Hold Time<br>MODE to PCLK       | 5.0             | -1.0                    | 0.0   | 0.0                                    | ns    |

| ts             | Setup Time<br>Y to DCLK         | 5.0             | 0.5                     | 2.5   | 2.5                                    | ns    |

| t <sub>S</sub> | Hold Time<br>Y to DCLK          | 5.0             | 0                       | 1.0   | 1.5                                    | ns    |

| t <sub>S</sub> | Setup Time<br>MODE to DCLK      | 5.0             | 2.0                     | 4.0   | 4.0                                    | ns    |

| t <sub>H</sub> | Hold Time<br>MODE to DCLK       | 5.0             | -0.5                    | 1.0   | 1.0                                    | ns    |

| t <sub>S</sub> | Setup Time<br>SDI to DCLK       | 5.0             | 2.0                     | 3.5   | 4.5                                    | ns    |

| t <sub>H</sub> | Hold Time<br>SDI to DCLK        | 5.0             | -0.5                    | 1.0   | 1.0                                    | ns    |

| t <sub>S</sub> | Setup Time<br>DCLK to PCLK      | 5.0             | 6.0                     | 9.0   | 10.5                                   | ns    |

| t <sub>S</sub> | Setup Time<br>PCLK to DCLK      | 5.0             | 6.0                     | 11.0  | 11.5                                   | ns    |

| t <sub>W</sub> | Pulse Width PCLK HIGH or LOW    | 5.0             | 2.0                     | 3.0   | 3.0                                    | ns    |

| t <sub>W</sub> | Pulse Width<br>DCLK HIGH or LOW | 5.0             | 2.0                     | 3.0   | 3.0                                    | ns    |

Note 5: Voltage range 5.0 is 5.0V ± 0.5V.

# Capacitance

| Symbol          | Parameter                     | Тур | Units | Conditions             |  |

|-----------------|-------------------------------|-----|-------|------------------------|--|

| C <sub>IN</sub> | Input Capacitance             | 4.5 | pF    | V <sub>CC</sub> = OPEN |  |

| Cpp             | Power Dissipation Capacitance | 20  | pF    | $V_{CC} = 5.0V$        |  |

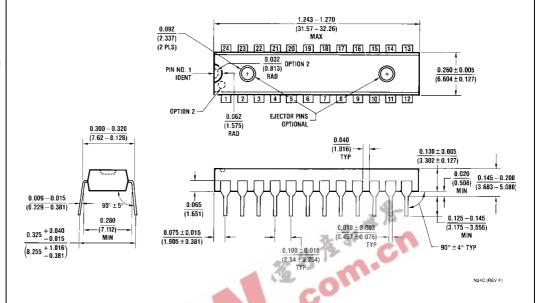

#### Physical Dimensions inches (millimeters) unless otherwise noted

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N24C

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com