#### **Unit Loading/Fan Out**

| Din Namas                       | Description                                   | U.L.    | Input I <sub>IH</sub> /I <sub>IL</sub>  |  |

|---------------------------------|-----------------------------------------------|---------|-----------------------------------------|--|

| Pin Names                       | ames Description                              |         | Output I <sub>OH</sub> /I <sub>OL</sub> |  |

| CS                              | Chip Select Input (Active LOW)                | 1.0/1.0 | 20 µA/-0.6 mA                           |  |

| SHCP                            | Shift Clock Pulse Input (Active Falling Edge) | 1.0/1.0 | 20 µA/-0.6 mA                           |  |

| STMR                            | Store Master Reset Input (Active LOW)         | 1.0/1.0 | 20 µA/-0.6 mA                           |  |

| STCP                            | Store Clock Pulse Input                       | 1.0/1.0 | 20 µA/-0.6 mA                           |  |

| R/W                             | Read/Write Input                              | 1.0/1.0 | 20 µA/-0.6 mA                           |  |

| SI/O                            | Serial Data Input or                          | 3.5/1.0 | 70 μA/–0.6 mA                           |  |

|                                 | 3-STATE Serial Output                         | 150/40  | –3 mA/24 mA                             |  |

| Q <sub>0</sub> –Q <sub>15</sub> | Parallel Data Outputs                         | 50/33.3 | –1 mA/20 mA                             |  |

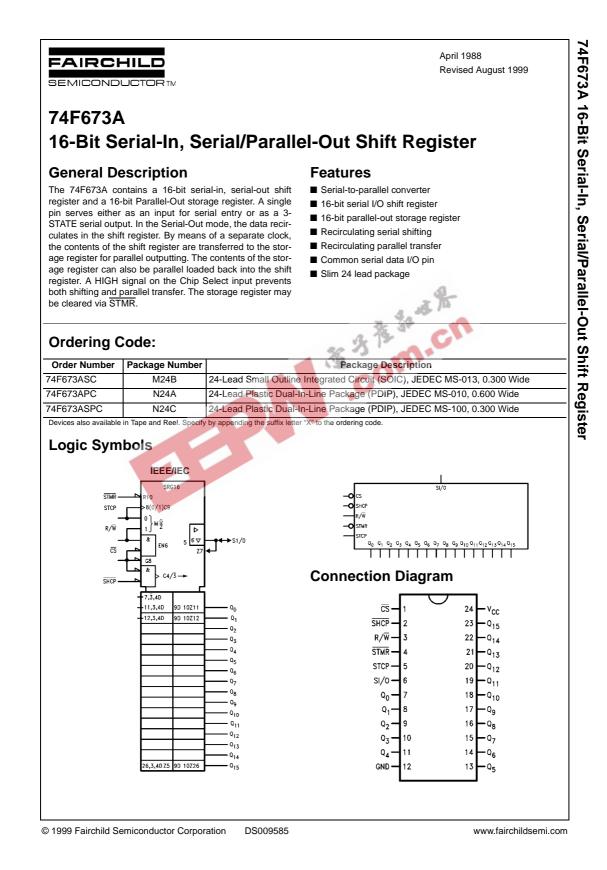

#### **Functional Description**

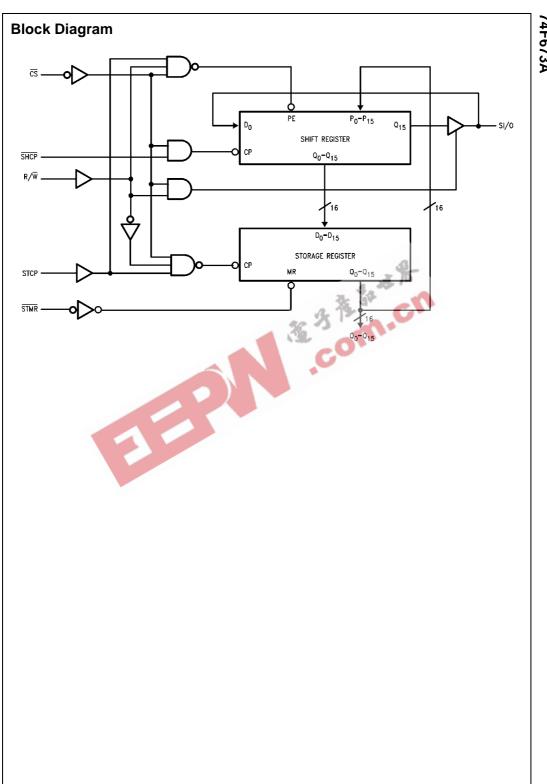

The 16-bit shift register operates in one of four modes, as indicated in the Shift Register Operations Table. A HIGH signal on the Chip Select ( $\overline{CS}$ ) input prevents clocking and forces the Serial Input/Output (SI/O) 3-STATE buffer into the high impedance state. During serial shift-out operations, the SI/O buffer is active (i.e., enabled) and the output data is also recirculated back into the shift register. When parallel loading the shift register from the storage register, serial shifting is inhibited.

The storage register has an asynchronous master reset (STMR) input that overrides all other inputs and forces the  $Q_0-Q_{15}$  outputs LOW. The storage register is in the Hold mode when either  $\overline{CS}$  or the Read/Write (R/ $\overline{W}$ ) input is HIGH. With  $\overline{CS}$  and R/ $\overline{W}$  both LOW, the storage register is parallel loaded from the shift register.

### Shift Register Operations Table

|    | Control Input |      |      | SI/O     | Oneverting Marks   |

|----|---------------|------|------|----------|--------------------|

| CS | R/W           | SHCP | STCP | Status   | Operating Mode     |

| Н  | Х             | Х    | Х    | High Z   | Hold               |

| L  | L             |      | X    | Data In  | Serial Load        |

| L  | н             | 7    | E    | Data Out | Serial Output      |

|    |               |      |      |          | with Recirculation |

| L  | Н             | ~    | Н    | Active   | Parallel Load;     |

|    |               |      |      |          | No Shifting        |

H = HIGH Voltage Level

L = LOW Voltage Level X = Immaterial

~ = HIGH-to-LOW Transition

### **Storage Register Operations Table**

|      | Contro | l Inputs | Operating |                    |

|------|--------|----------|-----------|--------------------|

| STMR | CS     | R/W      | STCP      | Mode               |

| L    | Х      | Х        | Х         | Reset; Outputs LOW |

| Н    | н      | Х        | Х         | Hold               |

| н    | х      | н        | Х         | Hold               |

| Н    | L      | L        | <i>_</i>  | Parallel Load      |

H = HIGH Voltage Level L = LOW Voltage Level

122

X = Immaterial  $\mathcal{I} = \text{LOW-to-HIGH Transition}$

### Absolute Maximum Ratings(Note 1)

| Storage Temperature                         | -65°C to +150°C               |

|---------------------------------------------|-------------------------------|

| Ambient Temperature under Bias              | -55°C to +125°C               |

| Junction Temperature under Bias             | -55°C to +150°C               |

| V <sub>CC</sub> Pin Potential to Ground Pin | -0.5V to +7.0V                |

| Input Voltage (Note 2)                      | -0.5V to +7.0V                |

| Input Current (Note 2)                      | -30 mA to +5.0 mA             |

| Voltage Applied to Output                   |                               |

| in HIGH State (with $V_{CC} = 0V$ )         |                               |

| Standard Output                             | -0.5V to V <sub>CC</sub>      |

| 3-STATE Output                              | -0.5V to +5.5V                |

| Current Applied to Output                   |                               |

| in LOW State (Max)                          | twice the rated $I_{OL}$ (mA) |

|                                             |                               |

### Recommended Operating Conditions

Free Air Ambient Temperature Supply Voltage

0°C to +70°C +4.5V to +5.5V

Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

### **DC Electrical Characteristics**

| Symbol            | Parameter                       | Min | Тур | Max         | Units | Vcc    | Conditions                                      |

|-------------------|---------------------------------|-----|-----|-------------|-------|--------|-------------------------------------------------|

| V <sub>IH</sub>   | Input HIGH Voltage              | 2.0 |     |             | V     | lu     | Recognized as a HIGH Signal                     |

| V <sub>IL</sub>   | Input LOW Voltage               |     |     | 0.8         | V     |        | Recognized as a LOW Signal                      |

| V <sub>CD</sub>   | Input Clamp Diode Voltage       |     |     | -1.2        | V     | Min    | I <sub>IN</sub> = -18 mA (Non I/O pins)         |

| V <sub>OH</sub>   | Output HIGH 10% V <sub>CC</sub> | 2.5 | 30  | 2           | -     |        | I <sub>OH</sub> = -1 mA (Q <sub>n</sub> , SI/O) |

|                   | Voltage 10% V <sub>CC</sub>     | 2.4 |     |             | V     | Min    | I <sub>OH</sub> = -3 mA (SI/O)                  |

|                   | 5% V <sub>CC</sub>              | 2.7 |     | <i>"</i> •O | v     | IVIIII | $I_{OH} = -1 \text{ mA} (Q_n, \text{SI/O})$     |

|                   | 5% V <sub>CC</sub>              | 2.7 |     | 0           |       |        | $I_{OH} = -3 \text{ mA} (SI/O)$                 |

| V <sub>OL</sub>   | Output LOW 10% V <sub>CC</sub>  |     |     | 0.5         | V     | Min    | I <sub>OL</sub> = 20 mA (Q <sub>n</sub> )       |

|                   | Voltage 10% V <sub>CC</sub>     |     |     | 0.5         | v     | IVIIII | I <sub>OL</sub> = 24 mA (SI/O)                  |

| I <sub>IH</sub>   | Input HIGH Current              |     |     | 20          | μΑ    | Max    | V <sub>IN</sub> = 2.7V (Non I/O pins)           |

| I <sub>BVI</sub>  | Input HIGH Current              |     |     | 100         | μA    | Max    | V <sub>IN</sub> = 7.0V (Non I/O pins)           |

|                   | Breakdown Test                  |     |     | 100         | μΑ    | IVICIA | $v_{\rm IN} = 7.00$ (Non 1/O pins)              |

| I <sub>BVIT</sub> | Input HIGH Current              |     |     | 1.0         | mA    | Мах    | V <sub>IN</sub> = 5.5V (SI/O)                   |

|                   | Breakdown Test (I/O)            |     |     | 1.0         |       | IVIAX  | V <sub>IN</sub> = 3.3V (31/0)                   |

| IIL               | Input LOW Current               |     |     | -0.6        | mA    | Max    | V <sub>IN</sub> = 0.5V                          |

| I <sub>IH</sub> + | Output Leakage                  |     |     | 70          | μA    | Мах    | V <sub>OUT</sub> = 2.7V (SI/O)                  |

| I <sub>OZH</sub>  | Current                         |     |     | 70          | μΑ    | IVIAX  | v <sub>OUT</sub> = 2.7 v (31/0)                 |

| I <sub>IL</sub> + | Output Leakage                  |     |     | -650        | μA    | Мах    | V <sub>OUT</sub> = 0.5V (SI/O)                  |

| I <sub>OZL</sub>  | Current                         |     |     | -030        | μΑ    | IVIAX  | v <sub>OUT</sub> = 0.3 v (31/O)                 |

| I <sub>OS</sub>   | Output Short-Circuit Current    | -60 |     | -150        | mA    | Max    | V <sub>OUT</sub> = 0V                           |

| ICEX              | Output HIGH Leakage Current     |     |     | 250         | μΑ    | Max    | V <sub>OUT</sub> = V <sub>CC</sub>              |

| I <sub>ZZ</sub>   | Bus Drainage Test               |     |     | 500         | μΑ    | 0.0V   | V <sub>OUT</sub> = 5.25V                        |

| I <sub>CCH</sub>  | Power Supply Current            |     | 114 | 172         | mA    | Max    | V <sub>O</sub> = HIGH                           |

| I <sub>CCL</sub>  | Power Supply Current            |     | 114 | 172         | mA    | Max    | V <sub>O</sub> = LOW                            |

| Symbol           | Parameter               |     | $T_{A} = +25^{\circ}C$ $V_{CC} = +5.0V$ $C_{L} = 50 \text{ pF}$ |      |     | $T_{A} = 0^{\circ}C \text{ to } +70^{\circ}C$ $V_{CC} = +5.0V$ $C_{L} = 50 \text{ pF}$ |     |

|------------------|-------------------------|-----|-----------------------------------------------------------------|------|-----|----------------------------------------------------------------------------------------|-----|

|                  |                         | Min | Тур                                                             | Max  | Min | Max                                                                                    | 1   |

| f <sub>MAX</sub> | Maximum Clock Frequency | 100 | 130                                                             |      | 85  |                                                                                        | MHz |

| t <sub>PLH</sub> | Propagation Delay       | 3.0 | 8.0                                                             | 10.5 | 2.5 | 12.0                                                                                   | ns  |

| t <sub>PHL</sub> | STCP to Q <sub>n</sub>  | 3.0 | 10.5                                                            | 13.5 | 2.5 | 15.0                                                                                   | 113 |

| t <sub>PHL</sub> | Propagation Delay       | 6.0 | 16.5                                                            | 20.5 | 5.5 | 22.5                                                                                   | ns  |

|                  | STMR to Q <sub>n</sub>  | 0.0 | 10.0                                                            | 20.0 | 0.0 | 22.0                                                                                   |     |

| t <sub>PLH</sub> | Propagation Delay       | 4.0 | 6.5                                                             | 8.5  | 3.5 | 9.5                                                                                    | ns  |

| t <sub>PHL</sub> | SHCP to SI/O            | 4.5 | 8.0                                                             | 10.5 | 4.0 | 12.0                                                                                   |     |

| t <sub>PZH</sub> | Output Enable Time      | 5.0 | 8.5                                                             | 11.0 | 4.0 | 12.5                                                                                   |     |

| t <sub>PZL</sub> | CS to SI/O              | 5.5 | 9.0                                                             | 11.5 | 4.5 | 13.0                                                                                   |     |

| t <sub>PHZ</sub> | Output Disable Time     | 3.5 | 5.5                                                             | 7.5  | 3.0 | 8.5                                                                                    | ns  |

| t <sub>PLZ</sub> | CS to SI/O              | 3.0 | 4.5                                                             | 6.5  | 2.5 | 7.5                                                                                    |     |

| t <sub>PZH</sub> | Output Enable Time      | 4.5 | 7.5                                                             | 9.5  | 4.0 | 10.5                                                                                   |     |

| t <sub>PZL</sub> | R/W to SI/O             | 4.5 | 8.0                                                             | 10.0 | 4.0 | 11.5                                                                                   |     |

| t <sub>PHZ</sub> | Output Disable Time     | 3.0 | 5.5                                                             | 7.0  | 2.5 | 8.0                                                                                    | ns  |

| t <sub>PLZ</sub> | R/W to SI/O             | 2.5 | 4.0                                                             | 5.5  | 2.0 | 6.5                                                                                    |     |

| AC | Operating | Requirements |

|----|-----------|--------------|

|----|-----------|--------------|

| Symbol             | Parameter               |     | T <sub>A</sub> = +25°C<br>V <sub>CC</sub> = +5.0V |     | $T_{A} = 0^{\circ}C \text{ to } +70^{\circ}C$ $V_{CC} = +5.0V$ |    |  |

|--------------------|-------------------------|-----|---------------------------------------------------|-----|----------------------------------------------------------------|----|--|

|                    |                         | Min | Max                                               | Min | Max                                                            |    |  |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW | 3.5 |                                                   | 4.0 |                                                                |    |  |

| t <sub>S</sub> (L) | CS or R/W to STCP       | 6.0 |                                                   | 7.0 |                                                                | ns |  |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW  | 0   |                                                   | 0   |                                                                |    |  |

| t <sub>H</sub> (L) | CS or R/W to STCP       | 0   |                                                   | 0   |                                                                |    |  |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW | 3.0 |                                                   | 3.5 |                                                                |    |  |

| t <sub>S</sub> (L) | SI/O to SHCP            | 3.0 |                                                   | 3.5 |                                                                |    |  |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW  | 3.0 |                                                   | 3.5 |                                                                | ns |  |

| t <sub>H</sub> (L) | SI/O to SHCP            | 3.0 |                                                   | 3.5 |                                                                |    |  |

74F673A 16-Bit Serial-In, Serial/Parallel-Out Shift Register