# ADC0816/ADC0817 8-Bit μP Compatible A/D Converters with 16-Channel Multiplexer

### **General Description**

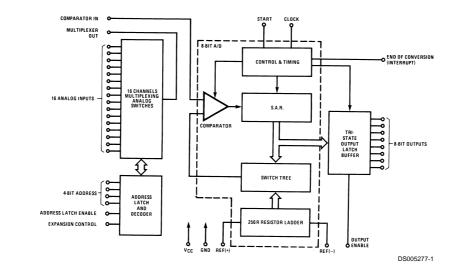

The ADC0816, ADC0817 data acquisition component is a monolithic CMOS device with an 8-bit analog-to-digital converter, 16-channel multiplexer and microprocessor compatible control logic. The 8-bit A/D converter uses successive approximation as the conversion technique. The converter features a high impedance chopper stabilized comparator, a 256R voltage divider with analog switch tree and a successive approximation register. The 16-channel multiplexer can directly access any one of 16-single-ended analog signals, and provides the logic for additional channel expansion. Signal conditioning of any analog input signal is eased by direct access to the multiplexer output, and to the input of the 8-bit A/D converter.

The device eliminates the need for external zero and full-scale adjustments. Easy interfacing to microprocessors is provided by the latched and decoded multiplexer address inputs and latched TTL TRI-STATE® outputs.

The design of the ADC0816, ADC0817 has been optimized by incorporating the most desirable aspects of several A/D conversion techniques. The ADC0816, ADC0817 offers high speed, high accuracy, minimal temperature dependence, excellent long-term accuracy and repeatability, and consumes minimal power. These features make this device ideally suited to applications from process and machine control to consumer and automotive applications. For similar performance in an 8-channel, 28-pin, 8-bit A/D converter, see the ADC0808, ADC0809 data sheet. (See AN-258 for more information.)

#### **Features**

- Easy interface to all microprocessors

- Operates ratiometrically or with 5 V<sub>DC</sub> or analog span adjusted voltage reference

- 16-channel multiplexer with latched control logic

- Outputs meet TTL voltage level specifications

- 0V to 5V analog input voltage range with single 5V supply

- No zero or full-scale adjust required

- Standard hermetic or molded 40-pin DIP package

- Temperature range -40°C to +85°C or -55°C to +125°C

- Latched TRI-STATE output

- Direct access to "comparator in" and "multiplexer out" for signal conditioning

- ADC0816 equivalent to MM74C948

- ADC0817 equivalent to MM74C948-1

### **Key Specifications**

- Resolution 8 Bits

- Total Unadjusted Error ±½ LSB and ±1 LSB

- Single Supply

5 V<sub>DC</sub> 15 mW

Low PowerConversion Time

100 µs

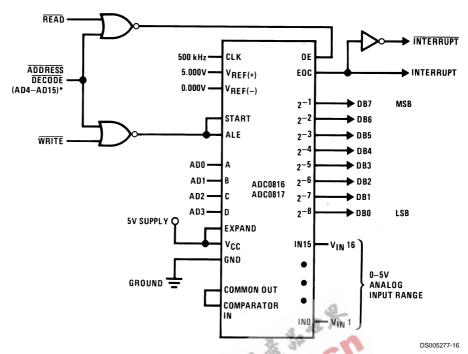

## **Block Diagram**

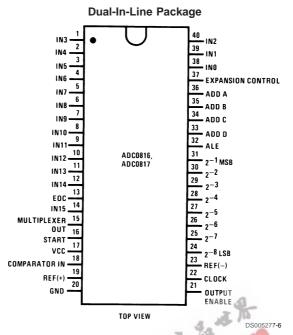

# **Connection Diagram**

Order Number ADC0816CCN or ADC0817CCN See NS Package Number N40A

# **Ordering Information**

| TEMPERATURE RANGE |                     | -40°C to +85°C  |                   |  |

|-------------------|---------------------|-----------------|-------------------|--|

| Error             | ±1/2 Bit Unadjusted | ADC0816CCN      | ADC0816CCJ        |  |

|                   | ±1 Bit Unadjusted   | ADC0817CCN      |                   |  |

| Package Outline   |                     | N40A Molded DIP | J40A Hermetic DIP |  |

### Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage ( $V_{CC}$ ) (Note 3) 6.5V Voltage at Any Pin -0.3V to ( $V_{CC}$ +0.3V) Except Control Inputs

Voltage at Control Inputs -0.3V to 15V (START, OE, CLOCK, ALE, EXPANSION CONTROL,

ADD A, ADD B, ADD C, ADD D)

Storage Temperature Range  $-65^{\circ}$ C to + 150 $^{\circ}$ C Package Dissipation at  $T_A = 25^{\circ}$ C 875 mW

Dual-In-Line Package (Plastic) 260°C

Molded Chip Carrier Package

Vapor Phase (60 seconds) 215°C

Infrared (15 seconds) 220°C

ESD Susceptibility (Note 9) 400V

### Operating Conditions (Notes 1, 2)

Lead Temp. (Soldering, 10 seconds)

$\begin{array}{lll} \text{Temperature Range (Note 1)} & & & & & & & \\ \text{ADC0816CCN, ADC0817CCN} & & & & & & \\ \text{Range of V}_{\text{CC}} \text{ (Note 1)} & & & & & \\ \text{Voltage at Any Pin} & & & & & \\ \end{array}$

Except Control Inputs

Voltage at Control Inputs 0V to 15V (START, OE, CLOCK, ALE, EXPANSION CONTROL, ADD A, ADD B, ADD C, ADD D)

### **Electrical Characteristics**

Converter Specifications:  $V_{CC}$ =5  $V_{DC}$ =  $V_{REF(+)}$ ,  $V_{REF(-)}$ =GND,  $V_{IN}$ = $V_{COMPARATOR\ IN}$ ,  $T_{MIN}$ ≤ $T_{MAX}$  and  $f_{CLK}$  = 640 kHz unless otherwise stated.

| Symbol                    | Parameter                  | Conditions                           | Min 🦺                  | Тур                | Max                    | Units    |

|---------------------------|----------------------------|--------------------------------------|------------------------|--------------------|------------------------|----------|

|                           | ADC0816                    |                                      | 2 15 10                | _                  |                        |          |

|                           | Total Unadjusted Error     | 25°C                                 | 30                     | 0                  | ±1/2                   | LSB      |

|                           | (Note 5)                   | T <sub>MIN</sub> to T <sub>MAX</sub> | -0.0                   |                    | ±3/4                   | LSB      |

|                           | ADC0817                    | 132                                  | 144.                   |                    |                        |          |

|                           | Total Unadjusted Error     | 0°C to 70°C                          |                        |                    | ±1                     | LSB      |

|                           | (Note 5)                   | T <sub>MIN</sub> to T <sub>MAX</sub> |                        |                    | ±11/4                  | LSB      |

|                           | Input Resistance           | From Ref(+) to Ref(-)                | 1.0                    | 4.5                |                        | kΩ       |

|                           | Analog Input Voltage Range | (Note 4) V(+) or V(-)                | GND-0.10               |                    | V <sub>CC</sub> +0.10  | $V_{DC}$ |

| V <sub>REF(+)</sub>       | Voltage, Top of Ladder     | Measured at Ref(+)                   |                        | V <sub>CC</sub>    | V <sub>CC</sub> +0.1   | V        |

| $V_{REF(+)} + V_{REF(-)}$ | Voltage, Center of Ladder  |                                      | V <sub>CC</sub> /2-0.1 | V <sub>CC</sub> /2 | V <sub>CC</sub> /2+0.1 | V        |

| 2                         |                            |                                      |                        |                    |                        |          |

| V <sub>REF(-)</sub>       | Voltage, Bottom of Ladder  | Measured at Ref(-)                   | -0.1                   | 0                  |                        | V        |

|                           | Comparator Input Current   | f <sub>c</sub> =640 kHz, (Note 6)    | -2                     | ±0.5               | 2                      | μΑ       |

#### **Electrical Characteristics**

Digital Levels and DC Specifications: ADC0816CCN, ADC0817CCN— $4.75V \le V_{CC} \le 5.25V$ ,  $-40^{\circ}C \le T_{A} \le +85^{\circ}C$  unless otherwise noted.

| Symbol              | Parameter                   | Conditions                                | Min  | Тур | Max | Units |

|---------------------|-----------------------------|-------------------------------------------|------|-----|-----|-------|

| ANALOG M            | ULTIPLEXER                  |                                           |      | 1   |     |       |

| R <sub>ON</sub>     | Analog Multiplexer ON       | (Any Selected Channel)                    |      |     |     |       |

|                     | Resistance                  | $T_A = 25^{\circ}C, R_L = 10k$            |      | 1.5 | 3   | kΩ    |

|                     |                             | T <sub>A</sub> =85°C                      |      |     | 6   | kΩ    |

|                     |                             | T <sub>A</sub> =125°C                     |      |     | 9   | kΩ    |

| $\Delta R_{ON}$     | ΔON Resistance Between Any  | (Any Selected Channel)                    |      | 75  |     | Ω     |

|                     | 2 Channels                  | R <sub>L</sub> =10k                       |      |     |     |       |

| I <sub>OFF+</sub>   | OFF Channel Leakage Current | V <sub>CC</sub> =5V, V <sub>IN</sub> =5V, |      |     |     |       |

|                     |                             | T <sub>A</sub> =25°C                      |      | 10  | 200 | nA    |

|                     |                             | T <sub>MIN</sub> to T <sub>MAX</sub>      |      |     | 1.0 | μΑ    |

| I <sub>OFF(-)</sub> | OFF Channel Leakage Current | V <sub>CC</sub> =5V, V <sub>IN</sub> =0,  |      |     |     |       |

|                     |                             | T <sub>A</sub> =25°C                      | -200 |     |     | nA    |

|                     |                             | T <sub>MIN</sub> to T <sub>Max</sub>      | -1.0 |     |     | μA    |

3

#### **Electrical Characteristics** (Continued)

$\textbf{Digital Levels and DC Specifications:} \ \ ADC0816CCN, \ \ ADC0817CCN-4.75V \\ \leq V_{CC} \\ \leq 5.25V, \ \ -40°C \\ \leq T_A \\ \leq +85°C \ \ \text{unless other-points} \\ \text{Constants} \\ \text{Constants}$ wise noted.

| Symbol              | Parameter                      | Conditions                                     | Min                  | Тур | Max  | Units |

|---------------------|--------------------------------|------------------------------------------------|----------------------|-----|------|-------|

| CONTROL I           | NPUTS                          |                                                |                      | •   |      |       |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage      |                                                | V <sub>CC</sub> -1.5 |     |      | V     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage      |                                                |                      |     | 1.5  | V     |

| I <sub>IN(1)</sub>  | Logical "1" Input Current      | V <sub>IN</sub> =15V                           |                      |     | 1.0  | μΑ    |

|                     | (The Control Inputs)           |                                                |                      |     |      |       |

| I <sub>IN(0)</sub>  | Logical "0" Input Current      | V <sub>IN</sub> =0                             | -1.0                 |     |      | μΑ    |

|                     | (The Control Inputs)           |                                                |                      |     |      |       |

| I <sub>cc</sub>     | Supply Current                 | f <sub>CLK</sub> =640 kHz                      |                      | 0.3 | 3.0  | mA    |

| DATA O              | UTPUTS AND EOC (INTERRUPT)     |                                                |                      |     |      |       |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage     | I <sub>O</sub> =-360 μA, T <sub>A</sub> =85°C  | V <sub>CC</sub> -0.4 |     |      | V     |

|                     |                                | I <sub>O</sub> =-300 μA, T <sub>A</sub> =125°C |                      |     |      |       |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage     | I <sub>O</sub> =1.6 mA                         |                      |     | 0.45 | V     |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage EOC | I <sub>O</sub> =1.2 mA                         |                      |     | 0.45 | V     |

| I <sub>OUT</sub>    | TRI-STATE Output Current       | V <sub>O</sub> =V <sub>CC</sub>                |                      |     | 3.0  | μΑ    |

|                     |                                | V <sub>O</sub> =0                              | -3.0                 |     |      | μΑ    |

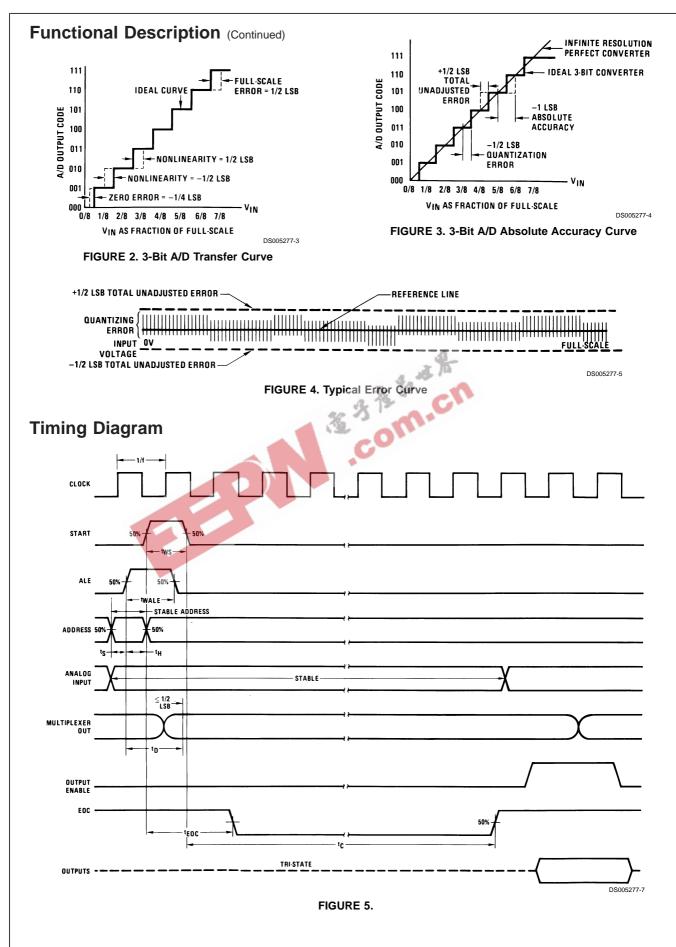

Electrical Characteristics

Timing Specifications:  $V_{CC} = V_{REF(+)} = 5V$ ,  $V_{REF(-)} = GND$ ,  $t_r = t_f = 20$  ns and  $T_A = 25$ °C unless otherwise noted.

| Symbol                            | Parameter                   | Conditions                                                     | Min | Тур | Max   | Units   |

|-----------------------------------|-----------------------------|----------------------------------------------------------------|-----|-----|-------|---------|

| t <sub>WS</sub>                   | Minimum Start Pulse Width   | (Figure 5) (Note 7)                                            |     | 100 | 200   | ns      |

| t <sub>WALE</sub>                 | Minimum ALE Pulse Width     | (Figure 5)                                                     |     | 100 | 200   | ns      |

| t <sub>s</sub>                    | Minimum Address Set-Up Time | (Figure 5)                                                     |     | 25  | 50    | ns      |

| T <sub>H</sub>                    | Minimum Address Hold Time   | (Figure 5)                                                     |     | 25  | 50    | ns      |

| t <sub>D</sub>                    | Analog MUX Delay Time       | $R_S = O\Omega$ (Figure 5)                                     |     | 1   | 2.5   | μs      |

|                                   | from ALE                    |                                                                |     |     |       |         |

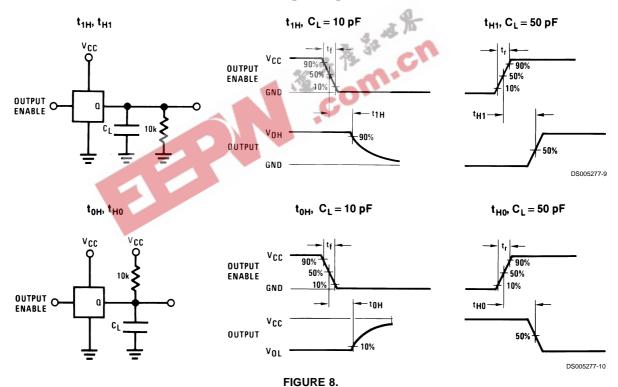

| t <sub>H1</sub> , t <sub>H0</sub> | OE Control to Q Logic State | C <sub>L</sub> =50 pF, R <sub>L</sub> =10k ( <i>Figure 8</i> ) |     | 125 | 250   | ns      |

| t <sub>1H,</sub> t <sub>0H</sub>  | OE Control to Hi-Z          | C <sub>L</sub> =10 pF, R <sub>L</sub> =10k ( <i>Figure 8</i> ) |     | 125 | 250   | ns      |

| t <sub>C</sub>                    | Conversion Time             | f <sub>c</sub> =640 kHz, (Figure 5) (Note 8)                   | 90  | 100 | 116   | μs      |

| f <sub>c</sub>                    | Clock Frequency             |                                                                | 10  | 640 | 1280  | kHz     |

| t <sub>EOC</sub>                  | EOC Delay Time              | (Figure 5)                                                     | 0   |     | 8+2µs | Clock   |

|                                   |                             |                                                                |     |     |       | Periods |

| C <sub>IN</sub>                   | Input Capacitance           | At Control Inputs                                              |     | 10  | 15    | pF      |

| C <sub>OUT</sub>                  | TRI-STATE Output            | At TRI-STATE Outputs (Note 8)                                  |     | 10  | 15    | pF      |

|                                   | Capacitance                 |                                                                |     |     |       |         |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified.

Note 3: A zener diode exists, internally, from  $V_{CC}$  to GND and has a typical breakdown voltage of 7  $V_{DC}$ .

Note 4: Two on-chip diodes are tied to each analog input which will forward conduct for analog input voltages one diode drop below ground or one diode drop greater than the V<sub>CC</sub> supply. The spec allows 100 mV forward bias of either diode. This means that as long as the analog V<sub>IN</sub> does not exceed the supply voltage by more than 100 mV, the output code will be correct. To achieve an absolute 0 V<sub>DC</sub> to 5 V<sub>DC</sub> input voltage range will therefore require a minimum supply voltage of 4.900 V<sub>DC</sub> over temperature variations, initial tolerance and loading.

Note 5: Total unadjusted error includes offset, full-scale, and linearity errors. See Figure 3. None of these A/Ds requires a zero or full-scale adjust. However, if an all zero code is desired for an analog input other than 0.0V, or if a narrow full-scale span exists (for example: 0.5V to 4.5V full-scale) the reference voltages can be adjusted to achieve this. See Figure 13.

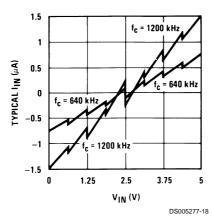

Note 6: Comparator input current is a bias current into or out of the chopper stabilized comparator. The bias current varies directly with clock frequency and has little temperature dependence (Figure 6). See paragraph 4.0.

Note 7: If start pulse is asynchronous with converter clock or if f<sub>c</sub> > 640 kHz, the minimum start pulse width is 8 clock periods plus 2 μs. For synchronous operation at  $f_{\text{c}} \le 640$  kHz take start high within 100 ns of clock going low.

Note 8: The outputs of the data register are updated one clock cycle before the rising edge of EOC.

**Note 9:** Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

### **Functional Description**

**Multiplexer:** The device contains a 16-channel single-ended analog signal multiplexer. A particular input channel is selected by using the address decoder. *Table 1* shows the input states for the address line and the expansion control line to select any channel. The address is latched into the decoder on the low-to-high transition of the address latch enable signal.

TABLE 1.

| Selected         | Address Line |   |   |   | Expansion |

|------------------|--------------|---|---|---|-----------|

| Analog Channel   | D            | С | В | Α | Control   |

| IN0              | L            | L | L | L | Н         |

| IN1              | L            | L | L | Н | Н         |

| IN2              | L            | L | Н | L | Н         |

| IN3              | L            | L | Н | Н | Н         |

| IN4              | L            | Н | L | L | Н         |

| IN5              | L            | Н | L | Н | Н         |

| IN6              | L            | Н | Н | L | Н         |

| IN7              | L            | Н | Н | Н | Н         |

| IN8              | Н            | L | L | L | Н         |

| IN9              | Н            | L | L | Н | Н         |

| IN10             | Н            | L | Н | L | Н         |

| IN11             | Н            | L | Н | Н | Н         |

| IN12             | Н            | Н | L | L | Н         |

| IN13             | Н            | Н | L | Н | H         |

| IN14             | Н            | Н | Н | L | Н         |

| IN15             | Н            | Н | Н | Н | Н         |

| All Channels OFF | Х            | Х | X | Х | L         |

Additional single-ended analog signals can be multiplexed to the A/D converter by disabling all the multiplexer inputs using the expansion control. The additional external signals are connected to the comparator input and the device ground. Additional signal conditioning (i.e., prescaling, sample and hold, instrumentation amplification, etc.) may also be added between the analog input signal and the comparator input.

#### **CONVERTER CHARACTERISTICS**

#### The Converter

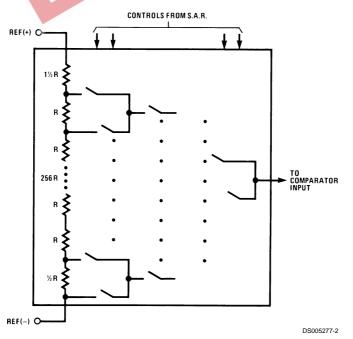

The heart of this single chip data acquisition system is its 8-bit analog-to-digital converter. The converter is designed to give fast, accurate, and repeatable conversions over a wide range of temperatures. The converter is partitioned into 3 major sections: the 256R ladder network, the successive approximation register, and the comparator. The converter's digital outputs are positive true.

The 256R ladder network approach *Figure 1* was chosen over the conventional R/2R ladder because of its inherent monotonicity, which guarantees no missing digital codes. Monotonicity is particularly important in closed loop feedback control systems. A non-monotonic relationship can cause oscillations that will be catastrophic for the system. Additionally, the 256R network does not cause load variations on the reference voltage.

The bottom resistor and the top resistor of the ladder network in *Figure 1* are not the same value as the remainder of the network. The difference in these resistors causes the output characteristic to be symmetrical with the zero and full-scale points of the transfer curve. The first output transition occurs when the analog signal has reached + ½ LSB and succeeding output transitions occur every 1 LSB later up to full-scale.

X=don't care

FIGURE 1. Resistor Ladder and Switch Tree

#### Timing Diagram (Continued)

The successive approximation register (SAR) performs 8 iterations to approximate the input voltage. For any SAR type converter, n-iterations are required for an n-bit converter. *Figure 2* shows a typical example of a 3-bit converter. In the ADC0816, ADC0817, the approximation technique is extended to 8 bits using the 256R network.

The A/D converter's successive approximation register (SAR) is reset on the positive edge of the start conversion (SC) pulse. The conversion is begun on the falling edge of the start conversion pulse. A conversion in process will be interrupted by receipt of a new start conversion pulse. Continuous conversion may be accomplished by tying the end-of-conversion (EOC) output to the SC input. If used in this mode, an external start conversion pulse should be applied after power up. End-of-conversion will go low between 0 and 8 clock pulses after the rising edge of start conversion.

The most important section of the A/D converter is the comparator. It is this section which is responsible for the ulimate accuracy of the entire converter. It is also the comparator drift which has the greatest influence on the repeatability of the device. A chopper-stabilized comparator provides the most effective method of satisfying all the converter requirements.

The chopper-stabilized comparator converts the DC input signal into an AC signal. This signal is then fed through a high gain AC amplifier and has the DC level restored. This technique limits the drift component of the amplifier since the drift is a DC component which is not passed by the AC amplifier. This makes the entire A/D converter extremely insensitive to temperature, long term drift and input offset errors.

Figure 4 shows a typical error curve for the ADC0816 as measured using the procedures outlined in AN-179.

### **Typical Performance Characteristics**

FIGURE 6. Comparator  $I_{IN}$  vs  $V_{IN}$  ( $V_{CC}$ = $V_{REF}$ =5V)

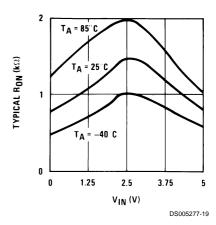

FIGURE 7. Multiplexer  $R_{ON}$  vs  $V_{IN}$  ( $V_{CC}=V_{REF}=5V$ )

### **TRI-STATE Test Circuits and Timing Diagrams**

8

# **Applications Information**

#### **OPERATION**

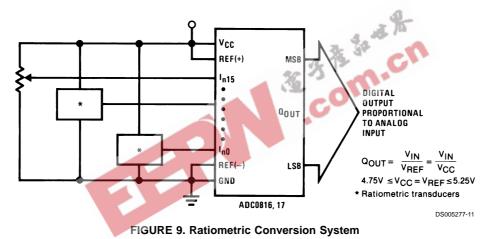

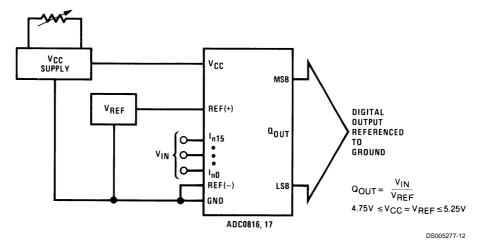

#### 1.0 RATIOMETRIC CONVERSION

The ADC0816, ADC0817 is designed as a complete Data Acquisition System (DAS) for ratiometric conversion systems. In ratiometric systems, the physical variable being measured is expressed as a percentage of full-scale which is not necessarily related to an absolute standard. The voltage input to the ADC0816 is expressed by the equation

$$\frac{V_{IN}}{V_{fs} - V_Z} = \frac{D_X}{D_{MAX} - D_{MIN}}$$

(1)

$V_{IN}$  = Input voltage into the ADC0816

V<sub>fs</sub> = Full-scale voltage

$V_Z$  = Zero voltage

$D_X$  = Data point being measured

$D_{MAX}$  = Maximum data limit

D<sub>MIN</sub> = Minimum data limit

### **Applications Information** (Continued)

A good example of a ratiometric transducer is a potentiometer used as a position sensor. The position of the wiper is directly proportional to the output voltage which is a ratio of the full-scale voltage across it. Since the data is represented as a proportion of full-scale, reference requirements are greatly reduced, eliminating a large source of error and cost for many applications. A major advantage of the ADC0816, ADC0817 is that the input voltage range is equal to the supply range so the transducers can be connected directly across the supply and their outputs connected directly into the multiplexer inputs, (*Figure 9*).

Ratiometric transducers such as potentiometers, strain gauges, thermistor bridges, pressure transducers, etc., are suitable for measuring proportional relationships; however, many types of measurements must be referred to an absolute standard such as voltage or current. This means a system reference must be used which relates the full-scale voltage to the standard volt. For example, if  $\rm V_{CC} = \rm V_{REF} = 5.12V$ , then the full-scale range is divided into 256 standard steps. The smallest standard step is 1 LSB which is then 20 mV.

#### 2.0 RESISTOR LADDER LIMITATIONS

The voltages from the resistor ladder are compared to the selected input 8 times in a conversion. These voltages are coupled to the comparator via an analog switch tree which is referenced to the supply. The voltages at the top, center and bottom of the ladder must be controlled to maintain proper operation.

The top of the ladder, Ref(+), should not be more positive than the supply, and the bottom of the ladder, Ref(-), should not be more negative than ground. The center of the ladder voltage must also be near the center of the supply because the analog switch tree changes from N-channel switches to P-channel switches. These limitations are automatically satisfied in ratiometric systems and can be easily met in ground referenced systems.

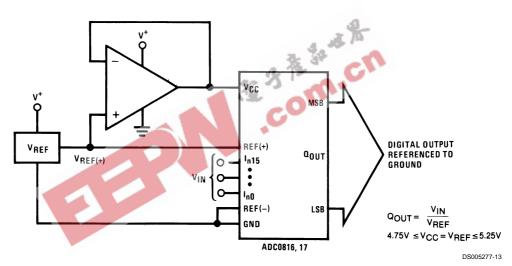

Figure 10 shows a ground referenced system with a separate supply and reference. In this system, the supply must be trimmed to match the reference voltage. For instance, if a 5.12V reference is used, the supply should be adjusted to the same voltage within 0.1V.

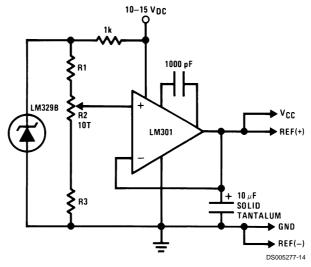

The ADC0816 needs less than a milliamp of supply current so developing the supply from the reference is readily accomplished. In *Figure 11* a ground references system is shown which generates the supply from the reference. The buffer shown can be an op amp of sufficient drive to supply the millliamp of supply current and the desired bus drive, or if a capacitive bus is driven by the outputs a large capacitor will supply the transient supply current as seen in *Figure 12*. The LM301 is overcompensated to insure stability when loaded by the 10  $\mu F$  output capacitor.

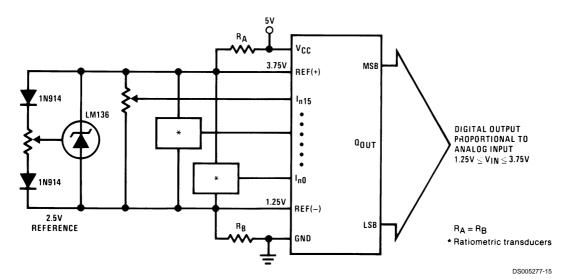

The top and bottom ladder voltages cannot exceed  $V_{\rm CC}$  and ground, respectively, but they can be symmetrically less than  $V_{\rm CC}$  and greater than ground. The center of the ladder voltage should always be near the center of the supply. The sensitivity of the converter can be increased, (i.e., size of the LSB steps decreased) by using a symmetrical reference system. In *Figure 13*, a 2.5V reference is symmetrically centered about  $V_{\rm CC}/2$  since the same current flows in identical resistors. This system with a 2.5V reference allows the LSB to be half the size of the LSB in a 5V reference system.

# Applications Information (Continued)

FIGURE 10. Ground Referenced Conversion System Using Trimmed Supply

FIGURE 11. Ground Referenced Conversion System with Reference Generating  $V_{CC}$  Supply

FIGURE 12. Typical Reference and Supply Circuit

### **Applications Information** (Continued)

FIGURE 13. Symmetrically Centered Reference

#### 3.0 CONVERTER EQUATIONS

The transition between adjacent codes N and N + 1 is given by:

$$V_{IN} = \left\{ (V_{REF(+)} - V_{REF(-)}) \left[ \frac{N}{256} + \frac{1}{512} \right] \pm V_{TUE} \right\} + V_{REF(-)}$$

(2

The center of an output code N is given by:

$$V_{IN} = \left\{ (V_{REF(+)} - V_{REF(-)}) \left[ \frac{N}{256} \right] \pm V_{TUE} \right] + V_{REF(-)}$$

(3)

The output code N for an arbitrary input are the integers within the range:

$$N = \frac{V_{IN} - V_{REF(-)}}{V_{REF(+)} - V_{REF(-)}} \times 256 \pm \text{Absolute Accuracy}$$

(4)

where:  $V_{IN}$  = Voltage at comparator input

V<sub>REF</sub> = Voltage at Ref(+)

$V_{REF} = Voltage at Ref(-)$

$V_{TUE}$  = Total unadjusted error voltage (typically

V<sub>REF</sub>(+) ÷512)

#### 4.0 ANALOG COMPARATOR INPUTS

The dynamic comparator input current is caused by the periodic switching of on-chip stray capacitances These are connected alternately to the output of the resistor ladder/switch tree network and to the comparator input as part of the operation of the chopper stabilized comparator.

The average value of the comparator input current varies directly with clock frequency and with  $V_{\rm IN}$  as shown in *Figure* 6.

If no filter capacitors are used at the analog or comparator inputs and the signal source impedances are low, the comparator input current should not introduce converter errors, as the transient created by the capacitance discharge will die out before the comparator output is strobed.

If input filter capacitors are desired for noise reduction and signal conditioning they will tend to average out the dynamic comparator input current. It will then take on the characteristics of a DC bias current whose effect can be predicted conventionally. See AN-258 for further discussion.

# **Typical Application**

\*Address latches needed for 8085 and SC/MP interfacing the ADC0816, 17 to a microprocessor

# **Microprocessor Interface Table**

| PROCESSOR | READ | WRITE                                    | INTERRUPT (COMMENT)            |

|-----------|------|------------------------------------------|--------------------------------|

| 8080      | MEMR | MEMW                                     | INTR (Thru RST Circuit)        |

| 8085      | RD   | WR                                       | INTR (Thru RST Circuit)        |

| Z-80      | RD   | WR                                       | INT (Thru RST Circuit, Mode 0) |

| SC/MP     | NRDS | NWDS                                     | SA (Thru Sense A)              |

| 6800      | VMA• | $VMA \bullet Q_2 \bullet \overline{R/W}$ | IRQA or IRQB (Thru PIA)        |

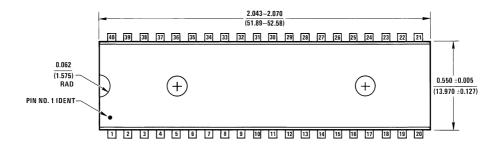

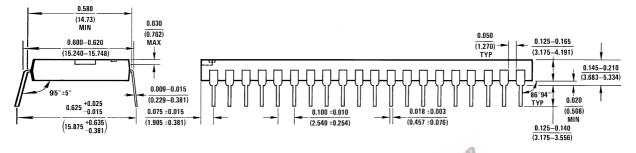

N40A (REV E)

### Physical Dimensions inches (millimeters) unless otherwise noted

Molded Dual-In-Line Package (N) NS Package Number N40A

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation

Americas Email: support@nsc.com

www.national.com

National Semiconductor

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

า

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466

Fax: 65-2504466 Email: ap.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560

Fax: 81-3-5639-7507