# 68HC05J5A 68HC05J5A 68HC705J5A 68HRC705J5A

SPECIFICATION (General Release)

July 16, 1999

Semiconductor Products Sector

# Semiconductor, Inc. Freescale

## **TABLE OF CONTENTS**

## **Section**

## **SECTION 1 GENERAL DESCRIPTION**

| 1.1                                                                   | FEATURES                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

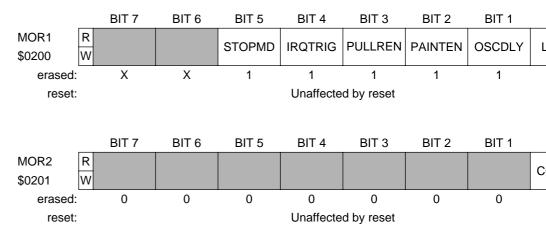

| 1.2                                                                   | MASK OPTIONS                                                                                                                                                                                                                                                                                                                |

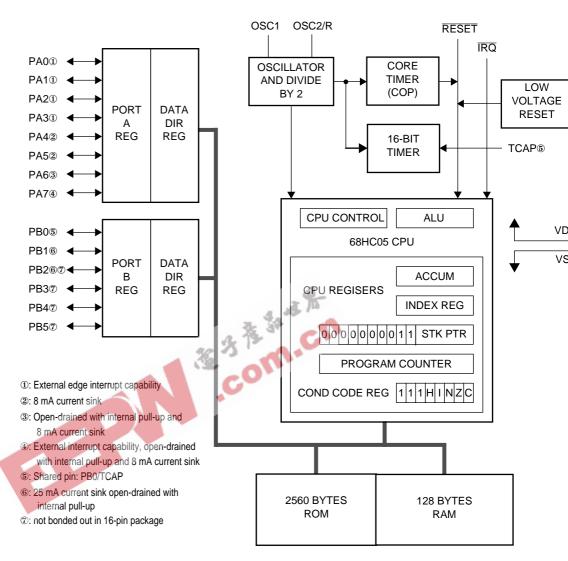

| 1.3                                                                   | MCU STRUCTURE                                                                                                                                                                                                                                                                                                               |

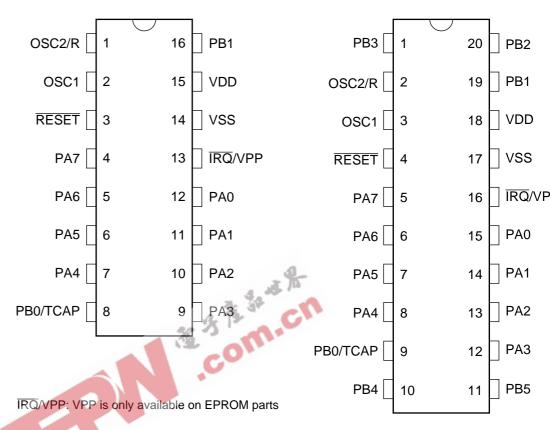

| 1.4                                                                   | PIN ASSIGNMENTS                                                                                                                                                                                                                                                                                                             |

| 1.5                                                                   | FUNCTIONAL PIN DESCRIPTION                                                                                                                                                                                                                                                                                                  |

| 1.5.1                                                                 | V <sub>DD</sub> AND V <sub>SS</sub>                                                                                                                                                                                                                                                                                         |

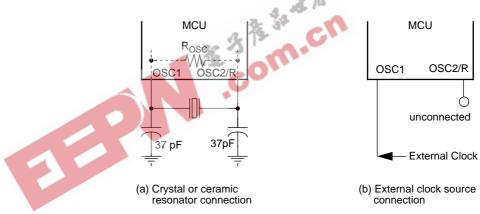

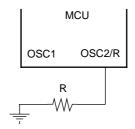

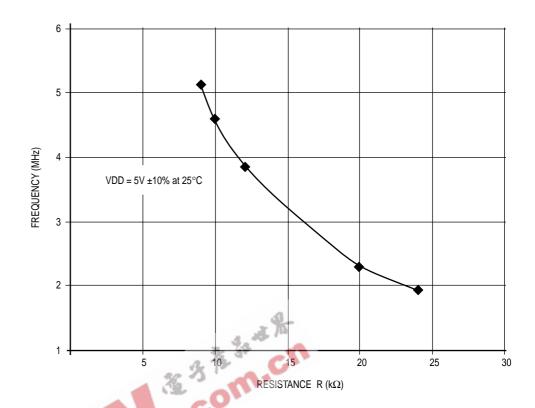

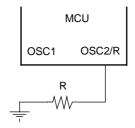

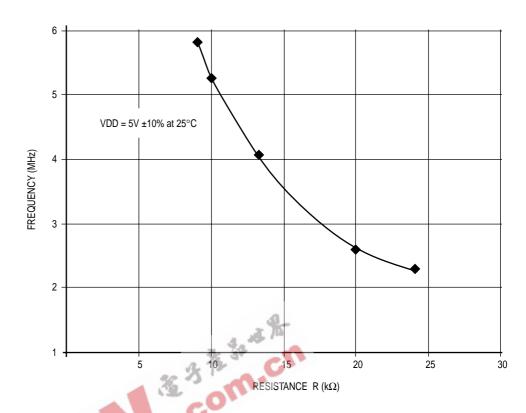

| 1.5.2                                                                 | OSC1, OSC2/R                                                                                                                                                                                                                                                                                                                |

| 1.5.3                                                                 | RESET                                                                                                                                                                                                                                                                                                                       |

| 1.5.4                                                                 | IRQ (MASKABLE INTERRUPT REQUEST)                                                                                                                                                                                                                                                                                            |

| 1.5.5                                                                 | PAN-PA7                                                                                                                                                                                                                                                                                                                     |

| 1.5.6                                                                 | PB0-PB5                                                                                                                                                                                                                                                                                                                     |

| 1.0.0                                                                 |                                                                                                                                                                                                                                                                                                                             |

|                                                                       | SECTION 2                                                                                                                                                                                                                                                                                                                   |

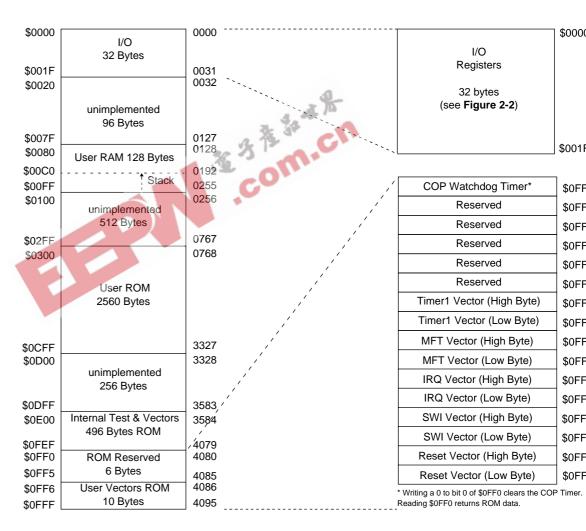

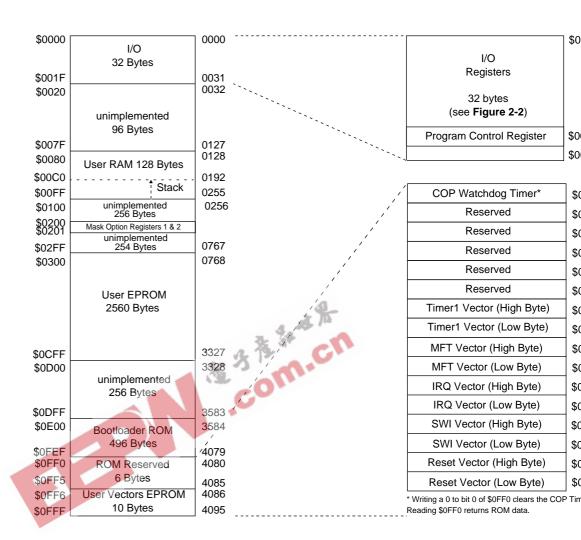

|                                                                       | MEMORY                                                                                                                                                                                                                                                                                                                      |

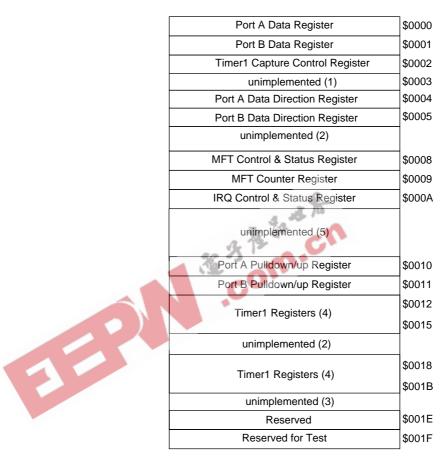

| 2.1                                                                   | I/O AND CONTROL REGISTERS                                                                                                                                                                                                                                                                                                   |

| 2.2                                                                   | RAM                                                                                                                                                                                                                                                                                                                         |

| 2.3                                                                   | RAM                                                                                                                                                                                                                                                                                                                         |

| 2.4                                                                   | I/O REGISTERS SUMMARY                                                                                                                                                                                                                                                                                                       |

|                                                                       |                                                                                                                                                                                                                                                                                                                             |

|                                                                       | SECTION 3 CENTRAL PROCESSING UNIT                                                                                                                                                                                                                                                                                           |

|                                                                       |                                                                                                                                                                                                                                                                                                                             |

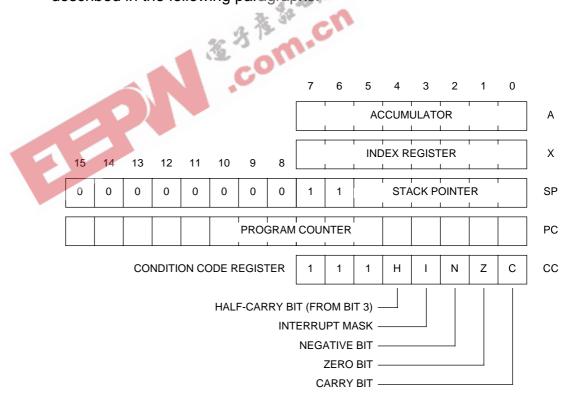

|                                                                       | REGISTERS                                                                                                                                                                                                                                                                                                                   |

| 2 2                                                                   |                                                                                                                                                                                                                                                                                                                             |

| 3.2                                                                   | ACCUMULATOR (A)                                                                                                                                                                                                                                                                                                             |

| 3.2                                                                   | INDEX REGISTER (X)                                                                                                                                                                                                                                                                                                          |

| _                                                                     | INDEX REGISTER (X)STACK POINTER (SP)                                                                                                                                                                                                                                                                                        |

| 3.3                                                                   | INDEX REGISTER (X)STACK POINTER (SP)                                                                                                                                                                                                                                                                                        |

| 3.3<br>3.4                                                            | INDEX REGISTER (X)                                                                                                                                                                                                                                                                                                          |

| 3.3<br>3.4<br>3.5                                                     | INDEX REGISTER (X)                                                                                                                                                                                                                                                                                                          |

| 3.3<br>3.4<br>3.5<br>3.6                                              | INDEX REGISTER (X)                                                                                                                                                                                                                                                                                                          |

| 3.3<br>3.4<br>3.5<br>3.6<br>3.6.1                                     | INDEX REGISTER (X)                                                                                                                                                                                                                                                                                                          |

| 3.3<br>3.4<br>3.5<br>3.6<br>3.6.1<br>3.6.2                            | INDEX REGISTER (X) STACK POINTER (SP) PROGRAM COUNTER (PC) CONDITION CODE REGISTER (CCR) Half Carry Bit (H-Bit) Interrupt Mask (I-Bit)                                                                                                                                                                                      |

| 3.3<br>3.4<br>3.5<br>3.6<br>3.6.1<br>3.6.2<br>3.6.3                   | INDEX REGISTER (X) STACK POINTER (SP) PROGRAM COUNTER (PC) CONDITION CODE REGISTER (CCR) Half Carry Bit (H-Bit) Interrupt Mask (I-Bit) Negative Bit (N-Bit)                                                                                                                                                                 |

| 3.3<br>3.4<br>3.5<br>3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4          | INDEX REGISTER (X) STACK POINTER (SP) PROGRAM COUNTER (PC) CONDITION CODE REGISTER (CCR) Half Carry Bit (H-Bit) Interrupt Mask (I-Bit) Negative Bit (N-Bit) Zero Bit (Z-Bit) Carry/Borrow Bit (C-Bit)                                                                                                                       |

| 3.3<br>3.4<br>3.5<br>3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4          | INDEX REGISTER (X) STACK POINTER (SP) PROGRAM COUNTER (PC) CONDITION CODE REGISTER (CCR) Half Carry Bit (H-Bit) Interrupt Mask (I-Bit) Negative Bit (N-Bit) Zero Bit (Z-Bit) Carry/Borrow Bit (C-Bit) SECTION 4                                                                                                             |

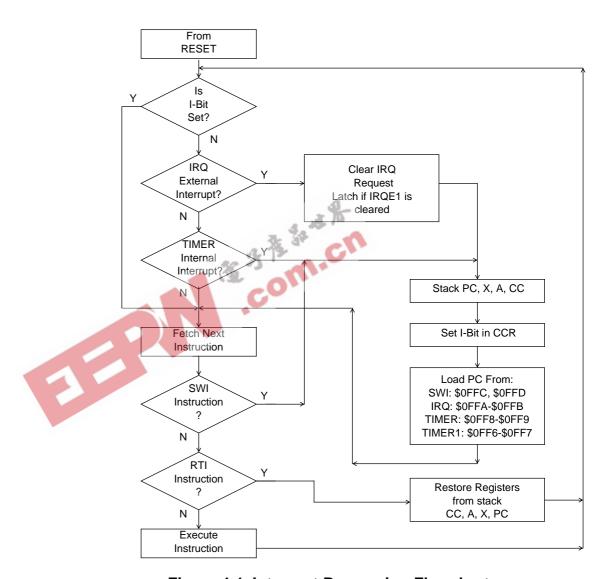

| 3.3<br>3.4<br>3.5<br>3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5 | INDEX REGISTER (X) STACK POINTER (SP) PROGRAM COUNTER (PC) CONDITION CODE REGISTER (CCR) Half Carry Bit (H-Bit) Interrupt Mask (I-Bit) Negative Bit (N-Bit) Zero Bit (Z-Bit) Carry/Borrow Bit (C-Bit)  SECTION 4 INTERRUPTS                                                                                                 |

| 3.3<br>3.4<br>3.5<br>3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5 | INDEX REGISTER (X) STACK POINTER (SP) PROGRAM COUNTER (PC) CONDITION CODE REGISTER (CCR) Half Carry Bit (H-Bit) Interrupt Mask (I-Bit) Negative Bit (N-Bit) Zero Bit (Z-Bit) Carry/Borrow Bit (C-Bit)  SECTION 4 INTERRUPTS  CPU INTERRUPT PROCESSING                                                                       |

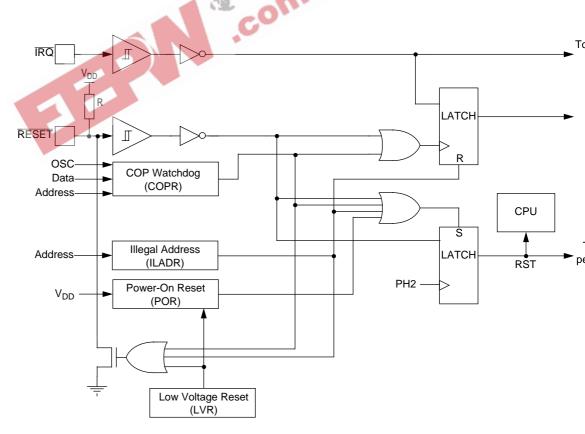

| 3.3<br>3.4<br>3.5<br>3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5 | INDEX REGISTER (X) STACK POINTER (SP) PROGRAM COUNTER (PC) CONDITION CODE REGISTER (CCR) Half Carry Bit (H-Bit) Interrupt Mask (I-Bit) Negative Bit (N-Bit) Zero Bit (Z-Bit) Carry/Borrow Bit (C-Bit)  SECTION 4 INTERRUPTS  CPU INTERRUPT PROCESSING RESET INTERRUPT SEQUENCE                                              |

| 3.3<br>3.4<br>3.5<br>3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5 | INDEX REGISTER (X) STACK POINTER (SP) PROGRAM COUNTER (PC) CONDITION CODE REGISTER (CCR) Half Carry Bit (H-Bit) Interrupt Mask (I-Bit) Negative Bit (N-Bit) Zero Bit (Z-Bit) Carry/Borrow Bit (C-Bit)  SECTION 4 INTERRUPTS  CPU INTERRUPT PROCESSING RESET INTERRUPT SEQUENCE SOFTWARE INTERRUPT (SWI)                     |

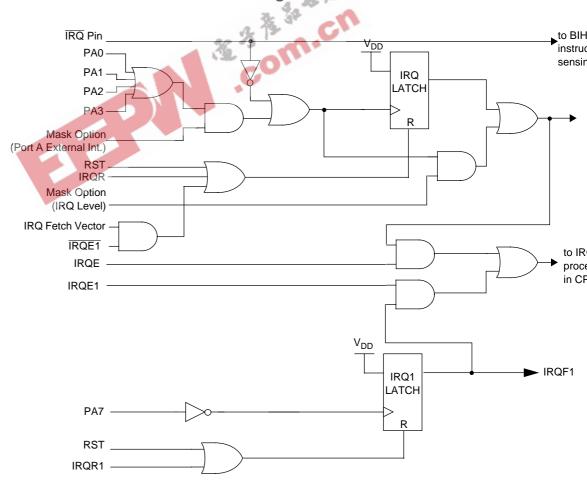

| 3.3<br>3.4<br>3.5<br>3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5 | INDEX REGISTER (X) STACK POINTER (SP) PROGRAM COUNTER (PC) CONDITION CODE REGISTER (CCR) Half Carry Bit (H-Bit) Interrupt Mask (I-Bit) Negative Bit (N-Bit) Zero Bit (Z-Bit) Carry/Borrow Bit (C-Bit)  SECTION 4 INTERRUPTS  CPU INTERRUPT PROCESSING RESET INTERRUPT SEQUENCE SOFTWARE INTERRUPT (SWI) HARDWARE INTERRUPTS |

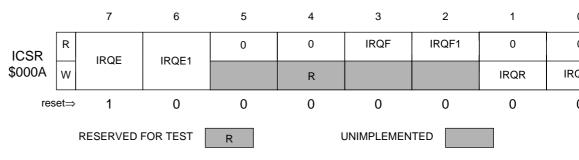

| 3.3<br>3.4<br>3.5<br>3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5 | INDEX REGISTER (X) STACK POINTER (SP) PROGRAM COUNTER (PC) CONDITION CODE REGISTER (CCR) Half Carry Bit (H-Bit) Interrupt Mask (I-Bit) Negative Bit (N-Bit) Zero Bit (Z-Bit) Carry/Borrow Bit (C-Bit)  SECTION 4 INTERRUPTS  CPU INTERRUPT PROCESSING RESET INTERRUPT SEQUENCE SOFTWARE INTERRUPT (SWI)                     |

**TABLE OF CONTENTS**

| Inc.       |  |  |

|------------|--|--|

| conductor, |  |  |

| e Semic    |  |  |

| Freescal   |  |  |

|            |  |  |

| Section                                                 | on                                                                                                                                                                                 |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.5.2<br>4.5.3<br>4.5.4                                 | OPTIONAL EXTERNAL INTERRUPTS (PA0-PA3) TIMER INTERRUPT (MFT) TIMER1 INTERRUPT (16-BIT TIMER)                                                                                       |

|                                                         | SECTION 5 RESETS                                                                                                                                                                   |

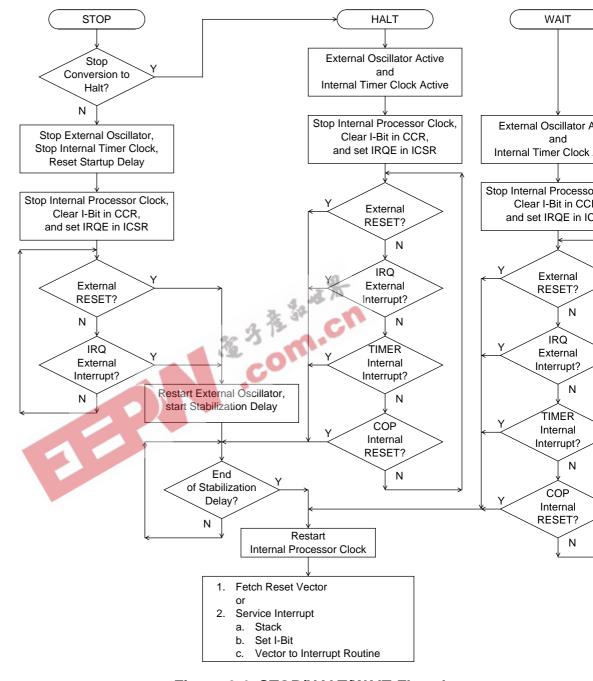

| 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4          | EXTERNAL RESET (RESET)                                                                                                                                                             |

|                                                         | SECTION 6 LOW POWER MODES                                                                                                                                                          |

| 6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.3<br>6.4              | STOP INSTRUCTION STOP Mode HALT Mode. WAIT INSTRUCTION DATA-RETENTION MODE COP WATCHDOG TIMER CONSIDERATIONS                                                                       |

|                                                         | SECTION 7<br>INPUT/OUTPUT PORTS                                                                                                                                                    |

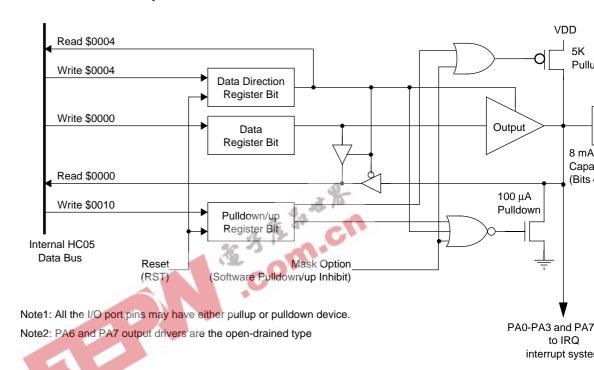

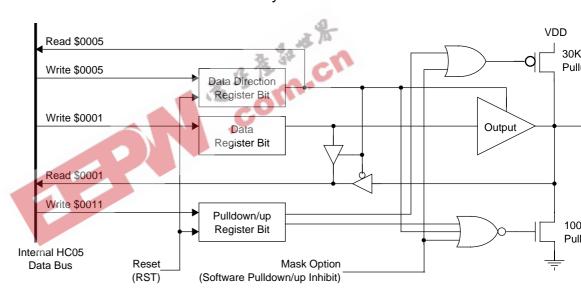

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5 | SLOW OUTPUT FALLING-EDGE TRANSITION  PORT A  Port A Data Register  Port A Data Direction Register  Port A Pulldown/up Register  Port A Drive Capability  Port A I/O Pin Interrupts |

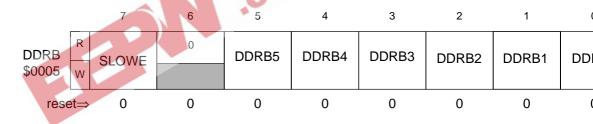

| 7.3<br>7.3.1<br>7.3.2<br>7.3.3<br>7.4                   | PORT B  Port B Data Register  Port B Data Direction Register  Port B Pulldown/up Register  I/O PORT PROGRAMMING                                                                    |

| 7.4.1<br>7.4.2<br>7.4.3<br>7.4.4                        | Pin Data Direction Output Pin Input Pin I/O Pin Transitions                                                                                                                        |

| 7.4.5                                                   | I/O Pin Truth Tables                                                                                                                                                               |

July 16, 1999 GENERAL RELEASE SPECIFIC

## **TABLE OF CONTENTS**

## **Section**

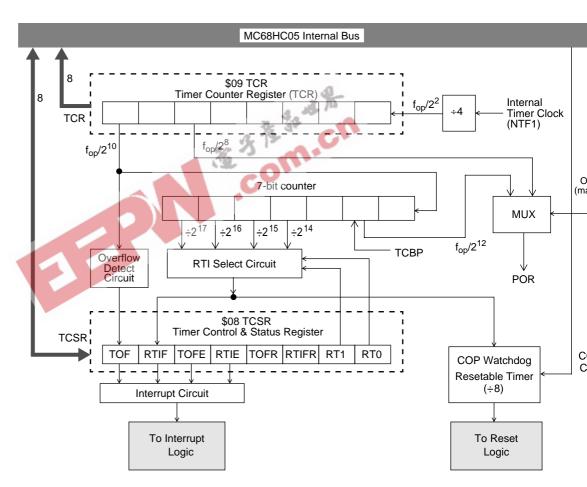

## SECTION 8 MULTI-FUNCTION TIMER

| 8.1                                                                                  | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

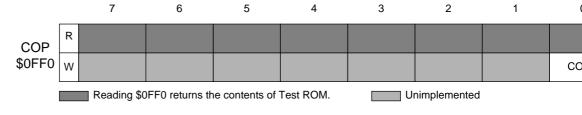

| 8.2                                                                                  | COMPUTER OPERATING PROPERLY (COP) WATCHDOG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8.3                                                                                  | MFT REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

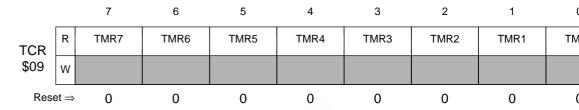

| 8.3.1                                                                                | Timer Counter Register (TCR) \$09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

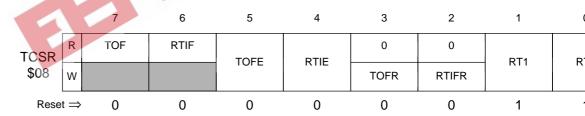

| 8.3.2                                                                                | Timer Control/Status Register (TCSR) \$08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8.4                                                                                  | OPERATION DURING STOP MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8.5                                                                                  | OPERATION DURING WAIT/HALT MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                      | SECTION 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                      | 16-BIT TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

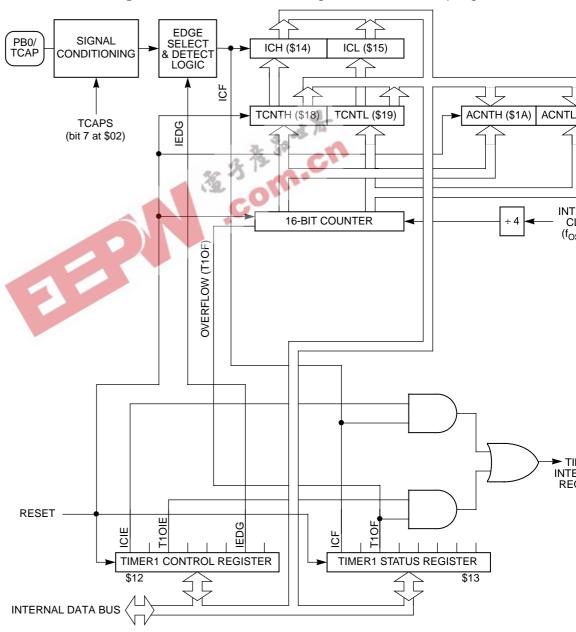

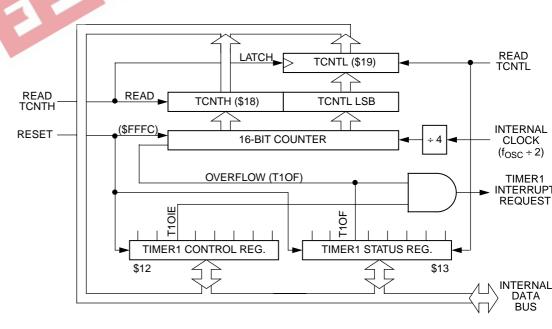

| 9.1                                                                                  | TIMER1 COUNTER REGISTERS (TCNTH, TCNTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

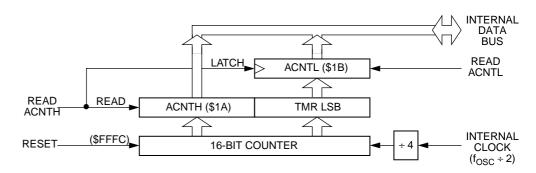

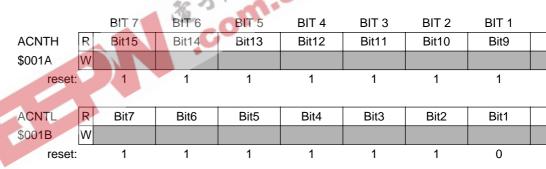

| 9.2                                                                                  | ALTERNATE COUNTER REGISTERS (ACNTH, ACNTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

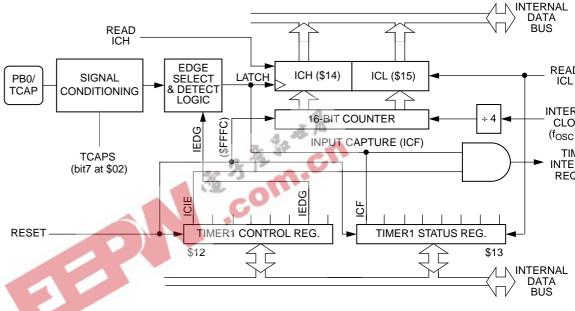

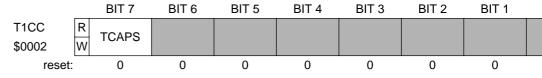

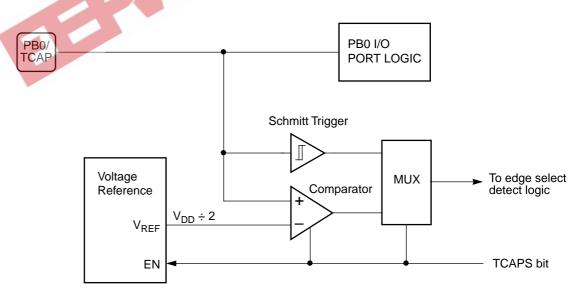

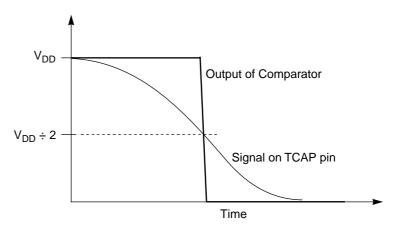

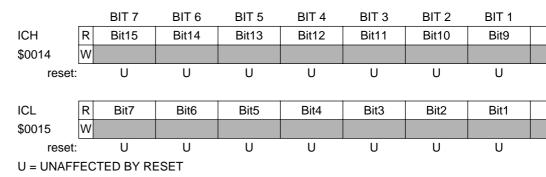

| 9.3                                                                                  | INPUT CAPTURE REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

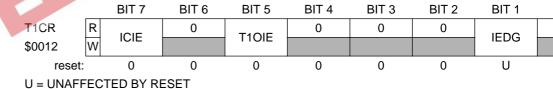

| 9.4                                                                                  | TIMER1 CONTROL REGISTER (T1CR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

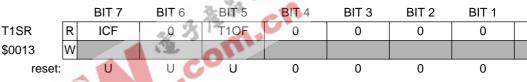

| 9.5                                                                                  | TIMER1 STATUS REGISTER (T1SR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9.6                                                                                  | TIMER1 OPERATION DURING WAIT MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9.7                                                                                  | TIMER 1 OPERATION DURING STOP MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 9.7                                                                                  | TIMER1 OPERATION DURING STOP MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9.7                                                                                  | SECTION 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                      | SECTION 10<br>INSTRUCTION SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10.1                                                                                 | SECTION 10 INSTRUCTION SET ADDRESSING MODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10.1<br>10.1.1                                                                       | SECTION 10 INSTRUCTION SET ADDRESSING MODESInherent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10.1<br>10.1.1<br>10.1.2                                                             | SECTION 10 INSTRUCTION SET  ADDRESSING MODES Inherent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10.1<br>10.1.1                                                                       | SECTION 10 INSTRUCTION SET  ADDRESSING MODES Inherent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10.1<br>10.1.1<br>10.1.2                                                             | SECTION 10 INSTRUCTION SET  ADDRESSING MODES Inherent Immediate B Direct Extended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10.1<br>10.1.1<br>10.1.2<br>10.1.3                                                   | SECTION 10 INSTRUCTION SET  ADDRESSING MODES Inherent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |