# **Enhanced GSM Processor**

**Preliminary Technical Information**

## AD6426

#### FEATURES

**Complete Single Chip GSM Processor Channel Codec Subsystem including Channel Coder/Decoder** Interleaver/De-interleaver **Encryption/Decryption Control Processor Subsystem including** 16-bit Control Processor (H8/300H) Parallel and Serial Display Interface **Keypad Interface EEPROM Interface** SIM-Interface **Universal System Connector Interface** Interface to AD6425 **Control of Radio Subsystem** Programmable backlight duty cycle **Real Time Clock with Alarm Battery ID Chip Interface DSP Subsystem including** 16-bit DSP with ROM coded firmware for Full rate Speech Encoding/Decoding (GSM 06.10) Enhanced Full Rate Speech Encoding/Decoding (GSM 06.60) Equalization with 16-state Viterbi (Soft Decision) **DTMF and Call Progress Tone Generation** Power Management of Mobile Radio Slow Clocking scheme for low Idle Mode current Ultra Low Power Design On-chip GSM Data Services up to 14.4 kbit/s **JTAG Test Interface** 2.4V to 3.3V Operating Voltage 144-Lead LQFP and 144-Lead PBGA packages

**ANALOG DEVICES**

#### **APPLICATIONS**

GSM 900 / DCS1800 / PCS1900 Mobile Stations (MS) Compliant to Phase 1 and Phase 2 specifications

#### GENERAL DESCRIPTION

The AD6426 Enhanced GSM Processor (EGSMP) is the central component of the highly integrated AD20msp425 GSM Chipset. Offering a low total chip count, low bill of materials cost and long talk and standby times, the chipset offers designers a straightforward route to a highly competitive product in the GSM/DCS1800 market.

The EGSMP performs all the baseband functions of the Layer 1 processing of the GSM air interface. This includes all data encoding and decoding processes as well as timing and radio sub-system control functions.

The EGSMP supports full rate and enhanced full rate speech traffic as well as a full range of data services including F14.4.

In addition, the EGSMP supports both A5/1 and A5/2 encryption algorithms as well as operation in non-encrypted mode.

The EGSMP integrates a high performance 16-bit microprocessor (Hitachi H8/300H), that supports all the GSM terminal software, including Layer 1, 2 and 3 of the GSM protocol stack, the MMI and applications software such as data services, test and maintenance.

The use of the standard H8 processor allows the use of HIOS, the Hitachi real time kernel, as well as a full range of software development tools including C compilers, debuggers and incircuit emulators. The EGSMP also integrates a high performance 16-bit Digital Signal Processor (DSP), which provides speech transcoding and supports all audio functions in both transmit and receive. In receive it equalizes the received signal using a 16-state (Viterbi) soft decision equalizer.

The EGSMP interfaces with all the peripheral sub-systems of the terminal, including the keypad, memories, display driver, SIM, DTE and DTA data services interface and radio. It also has a general purpose interface that can be used to support an external connection to a car kit or battery charger.

The EGSMP interfaces with the AD6425 or the AD6421 Voiceband/Baseband Codec through a dedicated serial port.

#### **ORDERING GUIDE**

| Model     | Temperature Range                | Package       |

|-----------|----------------------------------|---------------|

| AD6426XST | -25°C to +85°C                   | 144-Lead LQFP |

| AD6426XB  | $-25^{\circ}C$ to $+85^{\circ}C$ | 144-Lead PBGA |

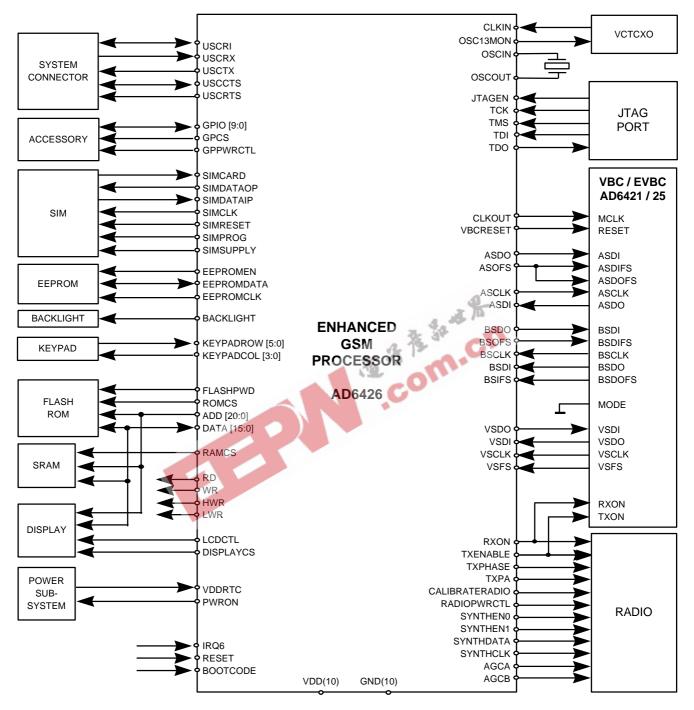

Figure 2. External Interfaces of the AD6426

This Information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing. No responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

## AD6426

#### Table of Contents

| GENERAL DESCRIPTION1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN FUNCTIONALITY (Normal Mode)4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| OVERVIEW7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| FUNCTIONAL PARTITIONING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Channel Codec Sub-System7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Processor Sub-System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DSP Sub-System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Speech Transcoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Equalization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Audio Control8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Tone Generation8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Automatic Frequency Control (AFC)8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Automatic Gain Control (AGC)8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GENERAL CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Slow Clocking14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Real Time Clock and Alarm14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Interrupts15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Wait16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Automatic Booting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Power Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| INTERFACES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Memory Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EEPROM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SIM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SIM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Accessory Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Accessory Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Accessory Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Accessory Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Accessory Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19                                                                                                                                                                                                                                                                                                                                                               |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20                                                                                                                                                                                                                                                                                                                                         |

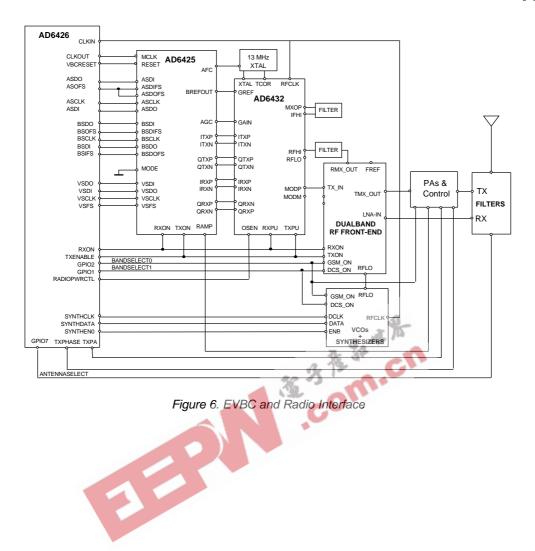

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20                                                                                                                                                                                                                                                                                                                         |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22                                                                                                                                                                                                                                                                                                        |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22Dual Band Control22                                                                                                                                                                                                                                                                                     |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22Dual Band Control22Tx Timing Control23                                                                                                                                                                                                                                                                  |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22Dual Band Control22Tx Timing Control23Rx Timing Control24                                                                                                                                                                                                                                               |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22Dual Band Control22Tx Timing Control23Rx Timing Control24Synthesizer Control24                                                                                                                                                                                                                          |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22Dual Band Control22Tx Timing Control23Rx Timing Control24Synthesizer Control24AGC Control25                                                                                                                                                                                                             |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22Dual Band Control22Tx Timing Control23Rx Timing Control24Synthesizer Control24AGC Control25TEST INTERFACE27JTAG Port.27                                                                                                                                                                                 |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22Dual Band Control22Tx Timing Control23Rx Timing Control24Synthesizer Control24AGC Control25TEST INTERFACE27                                                                                                                                                                                             |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22Dual Band Control22Tx Timing Control23Rx Timing Control24Synthesizer Control24AGC Control25TEST INTERFACE27JTAG Port27Debug Port Interface29                                                                                                                                                            |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22Dual Band Control22Tx Timing Control23Rx Timing Control24Synthesizer Control24AGC Control25TEST INTERFACE27JTAG Port.27Debug Port Interface29MODES OF OPERATION29                                                                                                                                       |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22Dual Band Control22Tx Timing Control23Rx Timing Control24Synthesizer Control24AGC Control25TEST INTERFACE27JTAG Port.27Debug Port Interface29MODES OF OPERATION.29Normal Mode (Mode A)29                                                                                                                |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22Dual Band Control22Tx Timing Control23Rx Timing Control24Synthesizer Control24AGC Control25TEST INTERFACE27JTAG Port.27Debug Port Interface29MODES OF OPERATION.29Normal Mode (Mode A)29Emulation Mode (Mode D)29                                                                                       |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22Dual Band Control22Tx Timing Control23Rx Timing Control24Synthesizer Control24AGC Control25TEST INTERFACE27JTAG Port.27Debug Port Interface29MODES OF OPERATION.29Emulation Mode (Mode A)29FEATURE MODES.30                                                                                             |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22Dual Band Control22Tx Timing Control23Rx Timing Control24Synthesizer Control24AGC Control25TEST INTERFACE27JTAG Port.27Debug Port Interface29MODES OF OPERATION29Normal Mode (Mode A)29Emulation Mode (Mode D)29FEATURE MODES30DAI Mode30                                                               |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface20Radio Interface22Dual Band Control22Tx Timing Control23Rx Timing Control24Synthesizer Control24AGC Control25TEST INTERFACE27JTAG Port.27Debug Port Interface29MODES OF OPERATION29Normal Mode (Mode A)29Emulation Mode (Mode D)29FEATURE MODES30DAI Mode30High Speed Logging30SPECIFICATIONS32General32 |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface22Dual Band Control22Tx Timing Control23Rx Timing Control24AGC Control25TEST INTERFACE27JTAG Port27Debug Port Interface29MODES OF OPERATION29Emulation Mode (Mode A)29Emulation Mode (Mode D)29FEATURE MODES30DAI Mode30High Speed Logging30SPECIFICATIONS32                                              |

| Accessory Interface17Universal System Connector Interface18Operating modes of the USC18Buffered UART Mode (Booting/Data Services)18Keypad / Backlight / Display Interface19Battery ID Interface20EVBC Interface20Radio Interface20Radio Interface22Dual Band Control22Tx Timing Control23Rx Timing Control24Synthesizer Control24AGC Control25TEST INTERFACE27JTAG Port.27Debug Port Interface29MODES OF OPERATION29Normal Mode (Mode A)29Emulation Mode (Mode D)29FEATURE MODES30DAI Mode30High Speed Logging30SPECIFICATIONS32General32 |

| Memory Interface             |    |

|------------------------------|----|

| Radio Interface              | 35 |

| High Speed Logging Interface |    |

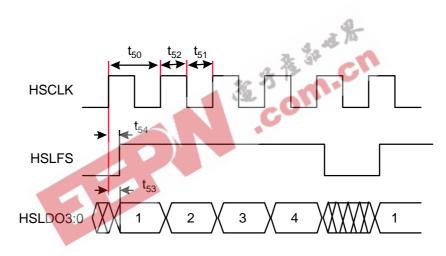

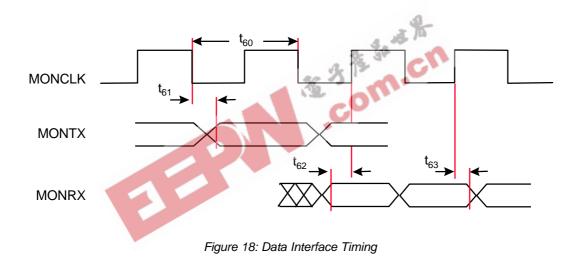

| Data Interface               |    |

| Test Interface               |    |

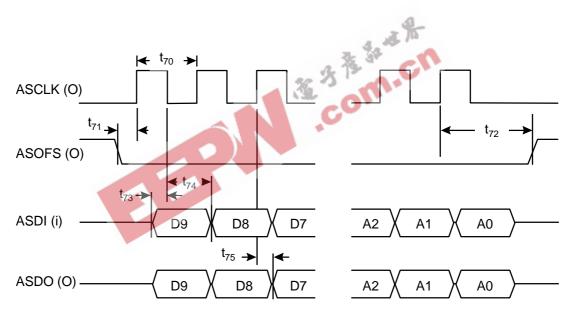

| EVBC Interface ASPORT        |    |

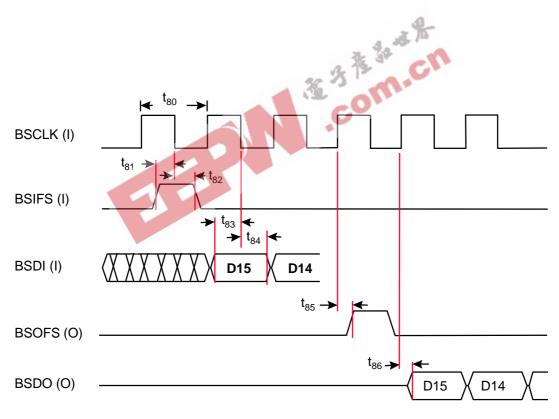

| EVBC Interface BSPORT        | 40 |

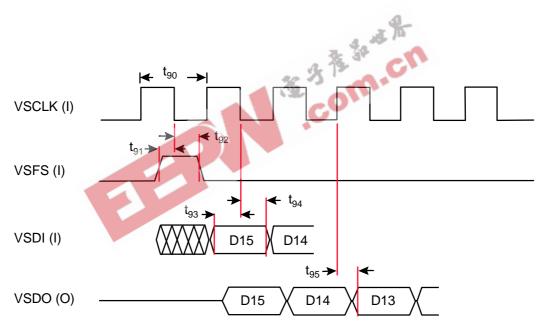

| EVBC Interface VSPORT        | 41 |

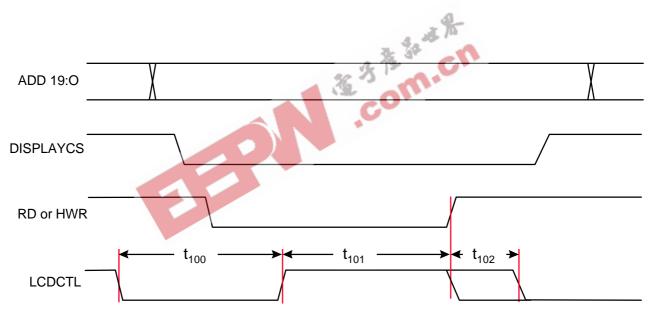

| Parallel Display Interface   | 42 |

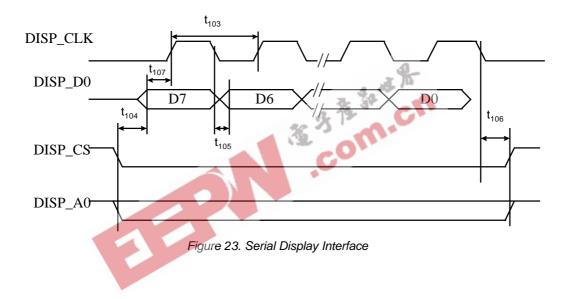

| Serial Display Interface     |    |

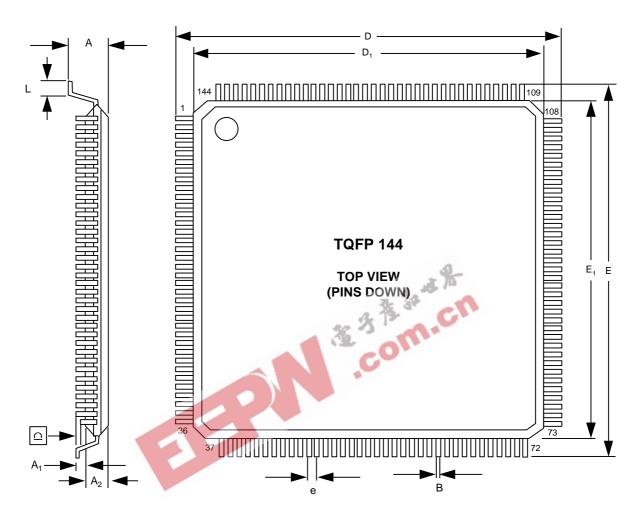

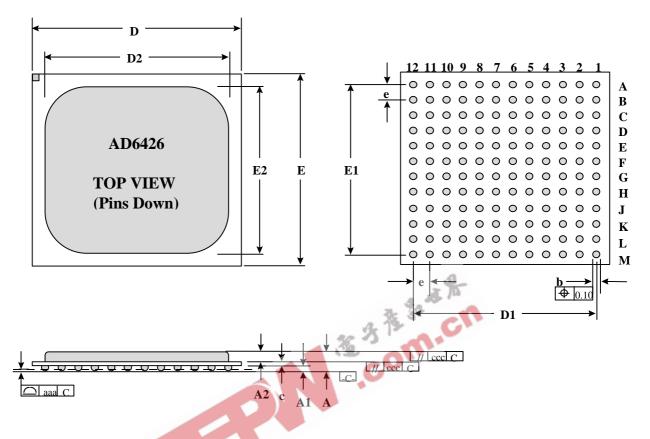

| PACKAGING                    |    |

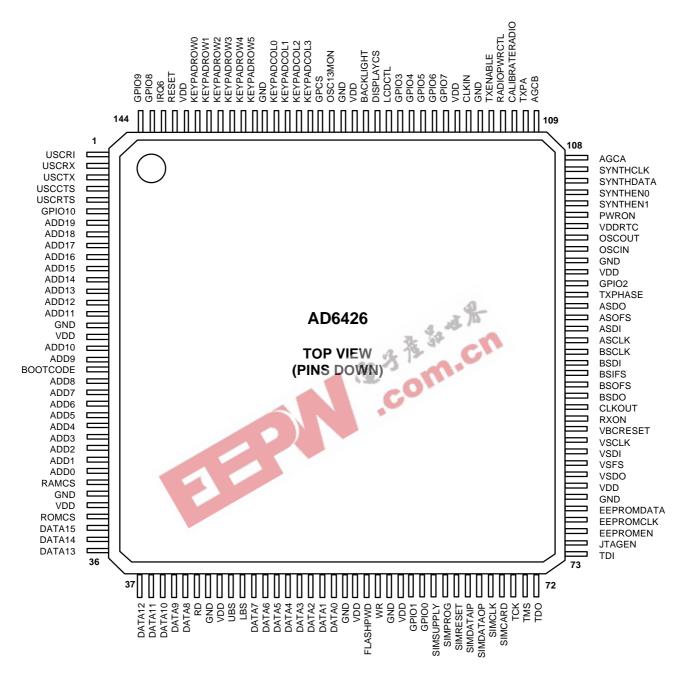

| LQFP Pin Locations           | 44 |

| PBGA Pin Locations           |    |

| LQFP Outline Dimensions      | 47 |

| PBGA Outline Dimensions      |    |

|                              |    |

## AD6426

| Group       | Pin Name     | Pins | I/O        | Default / Alternative Function(s) *                    |

|-------------|--------------|------|------------|--------------------------------------------------------|

| General     | CLKIN        | 1    | Ι          | 13 MHz Clock Input                                     |

|             | RESET        | 1    | Ι          | Reset input                                            |

|             | IRQ6         | 1    | I / I      | Interrupt Request # 6 / Non-Maskable Interrupt (NMI) * |

|             | OSC13MON     | 1    | 0          | 13 MHz Oscillator Power Control Signal                 |

|             | BOOTCODE     | 1    | Ι          | Boot Code Enable                                       |

|             | VDD          | 10   |            | Supply Voltage                                         |

|             | GND          | 10   |            | Ground                                                 |

| Memory      | ADD19:0      | 20   | 0          | Processor Address Bus                                  |

| Interface   | GPO10        | 1    | O / O      | General Purpose Output 10 / Address (20) *             |

|             | DATA15:0     | 16   | I/O        | Processor Data Bus                                     |

|             | RD           | 1    | 0          | Processor Read Strobe                                  |

|             | HWR          | 1    | 0          | Processor High Write Strobe / Upper Byte Strobe        |

|             | LWR          | 1    | 0          | Processor Low Write Strobe / Lower Byte Strobe         |

|             | WR           | 1    | 0          | Processor Write Strobe                                 |

|             | FLASHPWD     | 1    | O/I/<br>O  | FLASH Power Down / WAIT / General Purpose Output       |

|             | RAMCS        | 1    | 0          | External RAM Chip Select                               |

|             | ROMCS        | 1    | Ο          | External ROM Chip Select                               |

| SIM         | SIMCARD      |      | I /<br>I/O | SIM Card Detect / General Purpose I/O 16 *             |

| Interface   | SIMDATAOP    | 1    | 0          | SIM Data Output                                        |

|             | SIMDATAIP    | 1    | Ι          | SIM Data Input                                         |

|             | SIMCLK       | 1    | 0          | SIM Clock                                              |

|             | SIMRESET     | 1    | 0          | SIM Reset                                              |

|             | SIMPROG      | 1    | O /<br>I/O | SIM Program Enable / General Purpose I/O 15 *          |

|             | SIMSUPPLY    | 1    | 0          | SIM Supply Enable                                      |

| EEPRROM     | EEPROMDATA   | 1    | I/O        | EEPROM Data                                            |

| Interface   | EEPROMCLK    | 1    | 0          | EEPROM Clock / High Speed Logger Clock                 |

|             | EEPROMEN     | 1    | 0          | EEPROM Enable / High Speed Logger Frame Sync           |

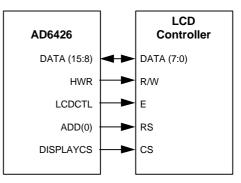

| Display /   | DISPLAYCS    | 1    | 0          | Display Controller Chip Select / Chip Enable           |

| Backlight / | LCDCTL       | 1    | 0          | LCD Control / Serial Display Data Output               |

| Keypad      | BACKLIGHT    | 1    | 0          | Backlight Control                                      |

| Interface   | KEYPADROW5:0 | 6    | Ι          | Keypad Row Inputs                                      |

|             | KEYPADCOL3:0 | 4    | 0          | Keypad Column Strobes (open drain, pull low)           |

PIN FUNCTIONALITY (Normal Mode)

\* Note: Functionality of these pins can be changed under software control.

This Information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing. No responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

## AD6426

| Group           | Pin Name       | Pins | I/O   | Default / Alternative Function(s) *                  |

|-----------------|----------------|------|-------|------------------------------------------------------|

| EVBC Interface  | CLKOUT         | 1    | 0     | Clock Output to EVBC                                 |

|                 | EVBCRESET      | 1    | 0     | EVBC Reset Output (also for Display reset)           |

| ASPORT          | ASDO           | 1    | 0     | EVBC Auxiliary Serial Port Data Output               |

|                 | ASOFS          | 1    | 0     | EVBC Auxiliary Serial Port Output Framing Signal     |

|                 | ASCLK          | 1    | 0     | EVBC Auxiliary Serial Port Clock Output              |

|                 | ASDI           | 1    | Ι     | EVBC Auxiliary Serial Port Data Input                |

| BSPORT          | BSDO           | 1    | 0     | EVBC Baseband Serial Port Data Output                |

|                 | BSOFS          | 1    | 0     | EVBC Baseband Serial Port Output Framing Signal      |

|                 | BSCLK          | 1    | Ι     | EVBC Baseband Serial Port Clock Input                |

|                 | BSDI           | 1    | Ι     | EVBC Baseband Serial Port Data Input                 |

|                 | BSIFS          | 1    | Ι     | EVBC Baseband Serial Port Input Framing Signal       |

| VSPORT          | VSDO           | 1    | 0     | EVBC Voiceband Serial Port Data Output               |

|                 | VSDI           | 1    | Ι     | EVBC Voiceband Serial Port Data Input                |

|                 | VSCLK          | 1    | Ι     | EVBC Voiceband Serial Port Clock Input               |

|                 | VSFS           | 1    | Ι     | EVBC Voiceband Serial Port Framing Signal            |

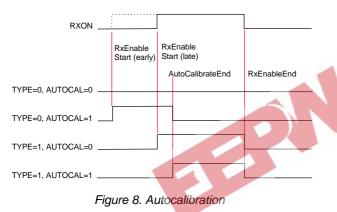

| Radio Interface | RXON           | 1    | 0 🦔   | Receiver On                                          |

|                 | TXPHASE        | 1    | 0 🕄   | Switches between Rx and Tx                           |

|                 | TXENABLE       | 1    | Ο     | Transmit Enable / General Purpose Output 14 *        |

|                 | ТХРА           | 1    | O / O | Power Amplifier Enable / General Purpose Output 12 * |

|                 | CALIBRATERADIO | 1    | 0/0   | Radio Calibration / General Purpose Output 13 *      |

|                 | RADIOPWRCTL    | 1    | 0     | Radio Power-Down Control                             |

|                 | SYNTHEN0       | 1    | 0     | Synthesizer 1 Enable                                 |

|                 | SYNTHEN1       | 1    | 0     | Synthesizer 2 Enable / General Purpose Output 17 *   |

|                 | SYNTHDATA      | 1    | 0     | RF Serial Port Data                                  |

|                 | SYNTHCLK       | 1    | 0     | RF Serial Port Clock                                 |

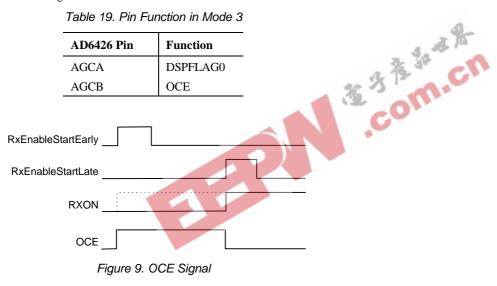

|                 | AGCA           | 1    | 0     | AGC Gain Select / General Purpose Output 18          |

|                 | AGCB           | 1    | 0     | AGC Gain Select / General Purpose Output 19          |

| Universal       | USCRI          | 1    | 1/O   | USC Ring Indicator / Serial Clock / GPO20            |

| System          | USCRX          | 1    | Ι     | USC Receive Data                                     |

| Connector       | USCTX          | 1    | 0     | USC Transmit Data / Baseband Serial Port Data Input  |

| Interface       | USCCTS         | 1    | I/O   | USC Clear to Send / Serial Frame Sync / GPI22        |

|                 | USCRTS         | 1    | 0     | USC Ready to Send / GPO21                            |

#### **Pin Functionality ( NORMAL MODE)**

\* Note: Functionality of these pins can be changed under software control.

## AD6426

| Group           | Pin Name | Pins | I/O                                                   | <b>Default / Alternative Function(s) *</b>                            |

|-----------------|----------|------|-------------------------------------------------------|-----------------------------------------------------------------------|

| Accessory       | GPIO0    | 1    | I/O                                                   | General Purpose Inputs/Output 0                                       |

| Interface GPIO1 |          |      | I/O                                                   | General Purpose Inputs/Output 1 / Radio BANDSELECT1 *                 |

|                 | 1        | I/O  | General Purpose Inputs/Output 2 / Radio BANDSELECT0 * |                                                                       |

|                 | GPIO3    | 1    | I/O                                                   | General Purpose Inputs/Outputs 3 / Serial Display Address<br>Output * |

|                 | GPIO4    | 1    | I/O                                                   | General Purpose Inputs/Outputs 4 / Serial Display Clock<br>Output *   |

|                 | GPIO5    | 1    | I/O                                                   | General Purpose Inputs/Outputs 5 / Battery ID Interface *             |

|                 | GPIO6    | 1    | I/O                                                   | General Purpose Inputs/Output 6 / VBIAS *                             |

|                 | GPIO7    | 1    | I/O                                                   | General Purpose Inputs/Output 7 / Antenna Select *                    |

|                 | GPIO8    | 1    | I/O                                                   | General Purpose Inputs/Output 8 / DEBUG UART<br>Transmit Data *       |

|                 | GPIO9    | 1    | I/O                                                   | General Purpose Inputs/Output 9 / DEBUG UART<br>Receive Data *        |

|                 | GPCS     | 1    | 0                                                     | General Purpose Chip Select                                           |

| Real Time       | OSCIN    | 1    | I                                                     | 32.768 kHz Crystal Input                                              |

| Clock           | OSCOUT   | 1    | 0                                                     | 32.768 kHz Oscillator Output and Feedback to Crystal                  |

| Interface       | VDDRTC   | 1    |                                                       | RTC Supply Voltage                                                    |

|                 | PWRON    | 1    | 0                                                     | Power ON/OFF Control                                                  |

| Test Interface  | JTAGEN   | 1    | I                                                     | JTAG Enable                                                           |

|                 | ТСК      | 1    | Ι                                                     | JTAG Test Clock / HSL Data 0                                          |

|                 | TMS      | 1    | Ι                                                     | JTAG Test Mode Select / HSL Data 1 / DAI Reset                        |

|                 | TDI      | 1    | Ι                                                     | JTAG Test Data Input / HSL Data 3 / DAI Data 1                        |

|                 | TDO      | 1    | 0                                                     | JTAG Test Data Output / HSL Data 2 / DAI Data 0                       |

#### **Pin Functionality ( NORMAL MODE)**

\* Note: Functionality of these pins can be changed under software control.

#### **OVERVIEW**

The GSM air interface has been formulated to provide high quality digital mobile communication. As well as supporting the traffic channels (speech and/or data), the air interface specifies a number of signaling channels that are used for call set up and communications between the network infrastructure and the mobile. These signaling channels provide the mobile specific features such as handover, as well as a number of other intelligent features.

The GSM system closely follows the OSI 7-layer model for communications. Specifically, GSM defines Layers 1, 2 and 3 of the protocols. The lowest level being Layer 1, or the Physical Layer. It is this part of the network processing for which the EGSMP is responsible, performing some of the Layer 1 functions in dedicated hardware for minimum power consumption and some in software for increased flexibility.

Layer 1 covers those signal processing functions required to format the speech/data for transmission on the physical medium. Data must be structured to allow for identification, recovery and error correction so that the information can be supplied error free to the layer 2 sub-systems and to the traffic sources. In addition, the physical layer processing includes the timing of both transmit and receive data, the encryption of data for security purposes and the control of the Radio subsystem to provide timing and to optimize the radio frequency characteristics. An object code license to Layer 1 software is supplied with the AD20msp425 chipset.

#### FUNCTIONAL PARTITIONING

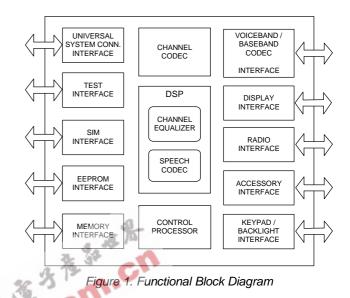

This datasheet gives only an overview about the functionality of the EGSMP. The EGSMP consists of three main elements; the Channel Codec and the Control Processor Sub-System including several interfaces and the DSP as shown in Figure 1. The Channel Codec is responsible for the Layer 1 channel coding and decoding of traffic and control information. The Processor Sub-system supports the software functions of the protocol stack and interfaces with the bus peripheral subsystems of the terminal. The DSP performs the channel equalization and speech transcoding.

#### Channel Codec Sub-System

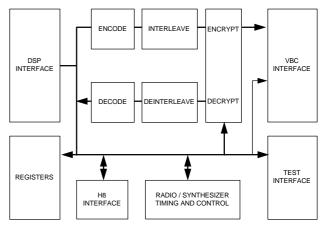

The Channel Codec processes data from two principal sources; traffic and signaling. The former is normally continuous and the latter determined on demand. Traffic comes in two forms; speech and user data. The various traffic sources and the signaling sources are all processed differently at the physical layer. Speech traffic data is supplied by the speech transcoder and the remaining data types are sourced from the Control Processor and interfaced via a dedicated data interface. The Channel Codec subsystem functional block diagram is shown in Figure 3.

Figure 3. Channel Codec Subsystem

The transmit and receive functions of the Channel Codec are timed by an internal timebase that maintains accurate timing of all sub-systems. This timebase is aligned with the on-air receive signal and all system control signals, both internal and external, are derived from it.

The physical layer processing can be divided into 4 phases, two each for up- and downlink. The data in the transmit path undergoes an ENCODE phase and then a TRANSMIT phase. Similarly, data in the downlink path is termed the receive data and it undergoes a RECEIVE phase followed by a DECODE phase. The buffer between the ENCODE and TRANSMIT functions is the INTERLEAVE module that holds the data and permits the building of the transmit burst structure. Similarly the DEINTERLEAVE module forms the buffer between the RECEIVE and the DECODE processes.

Each of these four phases is controlled explicitly by the Control Processor via control registers that define the mode of operation of each sub-module and the data source they should process. Typically these control values are updated every TDMA frame in response to interrupts from the internal timebase.

The ENCODE process involves the incorporation of error protection codes. All data is sourced in packets and two forms of error coding applied; block coding (parity or Fire code) and convolution coding. The resultant data block is then written to the INTERLEAVE module where it is buffered in a RAM. Data is read from the interleave buffer memories contiguously but written in non-contiguous manner, thereby implementing the interleaving function. The TRANSMIT process uses a different time structure now associated with the on-air TDMA structure. The data is read from the INTERLEAVE module and formatted into bursts with the requisite timing. This involves adding fixed patterns such as the tail bits and training sequence code. The resultant burst is written to the external Baseband Converter where the modulation is performed and the output timed to the system timebase before transmission.

This Information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing. No responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

A feature of the GSM system is the application, as part of the TRANSMIT process, of data encryption for the purpose of link security. After the INTERLEAVE module the data may be encrypted using the prescribed A5/1 or A5/2 encryption algorithm.

The RECEIVE function requires unmodulated baseband data from the equalizer. As necessary the data is decrypted and written to the DEINTERLEAVE module. This is conducted at TDMA frame rate, although precise timing is not necessary at this stage.

The DECODING process reads data from the DEINTERLEAVE module, inverting the interleave algorithm and decodes the error control codes, correcting and flagging errors as appropriate. The data also includes a measure of confidence expressed as two additional bits per received symbol. These are used in the convolution decoder to improve the error decoding performance. The resultant data is then presented to the original sources as determined by the control programming. The Channel Codec interfaces with the speech transcoder for speech traffic data and with an equalizer for recovered receive data. In the AD6426 the equalizer and speech transcoder are implemented in the DSP.

#### Processor Sub-System

The Processor Sub-System consists of a high performance 16bit microcontroller together with a selection of peripheral elements. The processor is a version of the Hitachi H8/300H that has been developed to support GSM applications and which is well suited to support the Protocol Stack and Application Layer software.

#### **DSP Sub-System**

The DSP Sub-System consists of a high performance 16-bit digital signal processor (DSP) with integrated RAM and ROM memories. The DSP performs two major tasks: speech transcoding and channel equalization. Additionally several support functions are performed by the DSP. The instruction code, which advises the DSP to perform these tasks, is stored in the internal ROM. The DSP sub-system is completely self-contained, no external memory or user-programming is necessary.

#### Speech Transcoding

In Full Rate mode the DSP receives the speech data stream from the EVBC and encodes the data from 104 kbit/s to 13 kbit/s. The algorithm used is Regular Pulse Excitation, with Long Term Prediction (RPE-LTP) as specified in the 06-series GSM Recommendations.

In Enhanced Full Rate mode, the DSP encodes the 104 kbit/s speech data into 12.2 kbit/s (speech) +0.8 kbit/s (CRC and repetition bits) as additionally specified in the Phase 2 version of the 06-series GSM Recommendations. In both modes, the DSP also performs the appropriate voice activity detection and discontinuous transmission (VAD/DTX) functions.

## AD6426

Alternatively the DSP receives encoded speech data from the channel codec sub-system including the Bad Frame Indicator (BFI). The Speech decoder supports a Comfort Noise Insertion (CNI) function that inserts a predefined silence descriptor into the decoding process. The resulting data, at 104 kbit/s, is transferred to the EVBC.

#### Equalization

The Equalizer recovers and demodulates the received signal and establishes local timing and frequency references for the mobile terminal as well as RSSI calculation. The equalization algorithm is a version of the Maximum Likelihood Sequence Estimation (MLSE) using the Viterbi algorithm. Two confidence bits per symbol provide additional information about the accuracy of each decision to the channel codec's convolutional decoder. The equalizer outputs a sequence of bits including the confidence bits to the channel codec subsystem.

#### **Audio Control**

The DSP subsystem is also responsible for the control of the audio path. The EVBC provides two audio inputs and two audio outputs, as well as a separate buzzer output, which are switched and controlled by the DSP. Furthermore the EVBC provides for variable gain and sensitivity which is also controlled by the DSP under command of the Layer 1 software.

#### **Tone Generation**

All alert signals are generated by the DSP and output to the EVBC. These alerts can be used for the buzzer or for the earpiece. The tones used for alert signals can be fully defined by the user by means of a description which provides all the parameters required such as frequency content and duration of components of the tone. The tone descriptions are provided by the Layer 1 software.

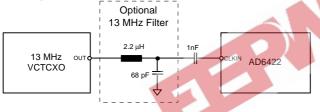

#### Automatic Frequency Control (AFC)

The detection of the frequency correction burst provides the frequency offset between the mobile terminal and the received signal. This measure is supplied to the Layer 1 software which then requests a correction of the master clock oscillator frequency via the AFC-DAC in the EVBC. In order to do so the Layer 1 software includes a transfer function for the oscillator frequency against the voltage applied. The DSP provides the measurements for the AFC.

#### Automatic Gain Control (AGC)

The DSP is also responsible for making measurements of the power in the received signal. This is used for a number of functions including RSSI measurement, adjacent channel monitoring and AGC. The Layer 1 software passes the requested gain level to the DSP, which then analyzes the received signal and generates an AGC control signal. Depending on the radio architecture, this control signal will be used in digital form or, converted by the AD6425 in analog form.

#### REGISTERS

The AD6426 contains 88 Channel Codec Control Registers, 69 H8 Peripheral Registers mapped into the Channel Codec address space starting at 8000h. All registers are normally accessed by the Layer 1 software provided with the AD20msp425 chipset. The user is not expected to read or write to any registers other than through the Layer 1 software. Therefore only a limited description of these registers is given here to ease the understanding of the functional behavior of the AD6426. Only registers which can be modified or monitored by the user under control of the Layer 1 software are shown. The Channel Codec Control Registers are listed in Table 1, and the H8 Peripheral Control Registers in Table 3

A description of the Channel Codec Control Register contents is shown in Table 2, and of the H8 Peripheral Registers in Table 4.

| 72 | 48 H | SYNTHESIZER PROGRAM | R/W |

|----|------|---------------------|-----|

| 73 | 49 H | TXPA OFFSET 1       | R/W |

| 74 | 4A H | TXPA OFFSET 2       | R/W |

| 75 | 4B H | TXPA WIDTH 1        | R/W |

| 76 | 4C H | TXPA WIDTH 2        | R/W |

| 77 | 4D H | IRQ ENABLE          | R/W |

| 78 | 4E H | IRQ LATCH           | RMW |

| 79 | 4F H | CC GPIO             | R/W |

| 88 | 58 H | ccGPO               | R/W |

Address

Name

AD6426

Table 1. CC Control Registers

|    |       | Table 1. CC Control Registers | T   |

|----|-------|-------------------------------|-----|

| Ad | dress | Name                          |     |

| 0  | 00 H  | SYSTEM                        | R/W |

| 2  | 02 H  | RADIO CONTROL                 | R/W |

| 4  | 04 H  | BSIC                          | R/W |

| 5  | 05 H  | TSC                           | R/W |

| 6  | 06 H  | TRAFFIC MODE                  | R/W |

| 7  | 07 H  | DAI                           | R/W |

| 8  | 08 H  | EEPROM                        | R/W |

| 9  | 09 H  | KEYPAD COLUMN                 | R/W |

| 10 | 0A H  | KEYPAD ROW                    | RD  |

| 28 | 1C H  | EVBC SERIAL 1                 | RMW |

| 29 | 1D H  | EVBC SERIAL 2                 | RMW |

| 30 | 1E H  | EVBC IF CONTROL               | R/W |

| 35 | 23 H  | RESET                         | R/W |

| 37 | 25 H  | SYNTH BIT COUNT               | R/W |

| 38 | 26 H  | SYNTH CONTROL                 | R/W |

| 39 | 27 H  | ERROR COUNT                   | RMW |

| 40 | 28 H  | SYNTHESIZER 1                 | WR  |

| 41 | 29 H  | SYNTHESIZER 2                 | WR  |

| 42 | 2A H  | SYNTHESIZER 3                 | WR  |

| 43 | 2B H  | SYNTHESIZER 4                 | WR  |

| 44 | 2C H  | POWER CONTROL INT             | R/W |

| 45 | 2D H  | POWER CONTROL EXTERNAL        | R/W |

| 46 | 2E H  | SWRESET 1                     | R/W |

| 47 | 2F H  | SWRESET 2                     | R/W |

| 48 | 30 H  | INTERRUPT COUNTER             | R/W |

| 49 | 31 H  | BBC TX ADDRESS                | R/W |

| 50 | 32 H  | BACKLIGHT                     | WR  |

| 51 | 33 H  | VERSION CONTROL               | RD  |

#### # 5 4 3 2 7 6 1 0 0 Autocalibrate Backlight 1 Test Data Enable Calibrate Radio Encryption Type Encrypt Key Load Tx Monitor Tx Phase Rx Radio Control Tx Radio Control Tx PHASE Monitor Receive Transmit 2 Enable Polarity Polarity Polarity Fnable Enable Enable Enable 4 Base Station Identity Code 5 Training Sequence Code Autocalibration TxPA INT COUNT[8] OCE OVERRIDE Interrupt Counter Traffic Frame Encryption Decryption 6 Polarity Override Enable Enable Enable Туре 7 BAND ENABLE NMI Select GPO10 Data GPO10 Select Data Ser. Select DAIRESET **FFPROM** Data FFRPOM FFPROM FFRPOM 8 Output Enable Clock Enable Data 9 Keypad Column 10 Keypad Row 28 EVBC Serial Port (15:8) 29 EVBC Serial Port (7:0) 30 Tx Data Delay EVBC Rx-Buff. full EVBC Tx-Buf.empty DSP Reset 35 EVBC Reset CC Reset Isolate Config. Dynam. Synthesizer 37 Synthesizer Bit Count Synthesizer Synthesizer Interface active Synthesizer Synthesizer Synthesizer Synthesizer Synthesizer Synthesizer 38 20 Enable Polarity Enable Type Clock Polarity oad Dynamic 1 Load Dynamic 2 Clock 39 Error Count 40 Synthesizer (31: 24) 41 Synthesizer (23: 16) 42 Synthesizer (15: 8) 43 Synthesizer (7:0) Synth. Interface DSP Interface Encryption Power Backlight Duty Cycle 44 Power Enable Power Enable Enable GP Power DSP Power Output Clock Radio Power Coprocessor 45 Power Control Enable Control Control Control EVBC Interface Encryption DSP Interface Synthes. Interface 46 SW-Reset SW-Reset SW-Reset SW-Reset INT CNT RST Decode Deinterleave interleave Encode 47 SW-Reset SW-Reset SW-Reset SW-Reset 48 Interrupt Counter 49 FVBC Read EVBC Tx Address 50 Modulate 1 Backlight LED Control 51 Version 72 Disable Synth.1 Disable Synth. 0 Synt. Enable Sel. Synt. Mode Pin Mode 73 TD(9:8) 74 TD(7:0) 75 TW(9:8) 76 TW(7:0)77 GPO11 Data GPO11 Select IRQ5 Enable IRQ4 Enable IRQ2 Enable FLASHPWD dis. NMI Edge Pol. IRQ3 Enable 78 IRQ5 active IRQ4 active IRO3 active IRQ2 active 79 GPIO9 OP En GPIO8 OP En GPIO9 Data GPIO8 Data 88 GPO19 Sel GPO18 Sel GPO17 Sel GP019 GP018 GP017

#### Table 2. CC Control Register Contents

This Information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing. No responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

## AD6426

Table 3. H8 Peripheral Control Registers

| A  | ddress | Name       |     |

|----|--------|------------|-----|

| 0  | 8000h  | SMSMR      | R/W |

| 1  | 8001h  | SMBRR      | R/W |

| 2  | 8002h  | SMSCR      | R/W |

| 3  | 8003h  | SMDR       | w   |

| 4  | 8004h  | SMSSR      | R/W |

| 5  | 8005h  | SMDR       | R   |

| 6  | 8006h  | SMSCMR     | R/W |

| 10 | 8010h  | BUFRBR     | R   |

| 10 | 8010h  | BUFTHR     | W   |

| 10 | 8010h  | BUFDLL     | R/W |

| 11 | 8011h  | BUFIER     | R/W |

| 11 | 8011h  | BUFDLM     | R/W |

| 12 | 8012h  | BUFIIR     | R   |

| 12 | 8012h  | BUFFCR     | W   |

| 13 | 8013h  | BUFLCR     | R/W |

| 14 | 8014h  | BUFMCR     | R/W |

| 15 | 8015h  | BUFLSR     | R/W |

| 16 | 8016h  | BUFMSR     | R/W |

| 17 | 8017h  | BUFSCR     | R/W |

| 18 | 8018h  | UIBRBR     | R   |

| 18 | 8018h  | UIBTHR     | W   |

| 19 | 8019H  | UIBSSR     | R/W |

| 26 | 801AH  | UIBER      | R   |

| 27 | 801BH  | UIBTSR     | R   |

| 28 | 801CH  | UIBTLR     | R/W |

| 29 | 801Dh  | UIBBLR     | R   |

| 32 | 8020h  | FIXRBR     | R   |

| 32 | 8020h  | FIXTHR     | W   |

| 32 | 8020h  | FIXDLL     | R/W |

| 33 | 8021h  | FIXIER     | R/W |

| 33 | 8021h  | FIXDLM     | R/W |

| 34 | 8022h  | FIXIIR     | R   |

| 35 | 8023h  | FIXLCR     | R/W |

| 36 | 8024h  | FIXMCR     | R/W |

| 37 | 8025h  | FIXLSR     | R/W |

| 38 | 8026h  | FIXMSR     | R/W |

| 39 | 8027h  | FIXSCR     | R/W |

| 48 | 8030h  | SCCR       | R/W |

| 49 | 8031h  | SPSSR      | R/W |

| 50 | 8032h  | SDIR1 (MS) | R   |

| 51 | 8033h  | SDIR0 (LS) | R   |

| 52 | 8034h  | SDOR1 (MS) | W   |

| 53 | 8035h  | SDOR0 (LS) | W   |

|     | Address       |       | Name           |     |

|-----|---------------|-------|----------------|-----|

|     | 64/65 8040/1h |       | DISPDDR        | W   |

|     | 66 8042h      |       | DISPCR         | R/W |

|     | 67            | 8043h | DDOR           | W   |

|     | 68            | 8044h | DDIR           | R   |

|     | 69            | 8045h | DRR            | R/W |

|     | 72            | 8048h | WDTR           | W   |

|     | 80            | 8050h | MEM IF         | R/W |

|     | 81            | 8051h | PERST          | R/W |

|     | 82            | 8052h | PERCR          | R/W |

|     | 84            | 8054h | TAR            | R/W |

|     | 85            | 8055h | PERCLK         | R/W |

|     | 96            | 8060h | RTCTR1         | R/W |

|     | 97            | 8061h | RTCTR2         | R/W |

|     | 98            | 8062h | RTCTR3         | R/W |

|     | 99            | 8063h | RTCTR4         | R/W |

|     | 100           | 8064h | RTCTR5         | R/W |

|     | 101           | 8065h | RTCAR1         | R/W |

|     | 102           | 8066h | RTCAR2         | R/W |

| 6   | 103           | 8067h | RTCAR3         | R/W |

| 3.0 | 104           | 8068h | RTCCR          | R/W |

|     | 105           | 8069h | RTCSRZ         | R/W |

|     | 106           | 8074h | SERDISPLAY/NMI | R/W |

This Information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing. No responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

| #        | 7                | 6              | 5            | 4                      | 3                | 2                    | 1                  | 0                 |

|----------|------------------|----------------|--------------|------------------------|------------------|----------------------|--------------------|-------------------|

|          | //               | 0              |              |                        | 3                | 2                    | 1                  | 0                 |

| 0        |                  |                |              | ODD                    |                  | DDDI                 | 2.01               |                   |

| 1 2      | TIE              | RIE            | TE           | RE                     | AE               | BRR[3<br>DATEN       | CLKPOL             | CLKEN             |

| 3        | TIE              | KIE            | IL           | Transmit[7:            |                  | DATEN                | CLKPOL             | CLKEN             |

| 4        | TDRE             | RDRF           | ORER         | ERS                    | PER              | TEND                 |                    |                   |

| 5        | IDRE             | KDKI           | OKEK         | Receive[7:0            |                  | TEND                 |                    |                   |

| 6        |                  |                |              | Receive[7.0            |                  |                      |                    |                   |

| 10       |                  |                |              | RxData[7:0             | )]               |                      |                    |                   |

| 10       |                  |                |              | TxData[7:0             |                  |                      |                    |                   |

| 10       |                  |                |              | BRR[7:0]               |                  |                      |                    |                   |

| 11       |                  |                |              |                        | EDSSI            | ELSI                 | ETBEI              | ERBFI             |

| 11       |                  |                |              | BRR[15:8               |                  |                      |                    |                   |

| 12       | FIFO ST          | FIFO ST        |              |                        |                  | nterruptID[2:0]      |                    | Int Pend          |

| 12       | RxLevel          | [1:0]          |              |                        | DMA              | TX FIFO              | RX FIFO            | FIFO EN           |

| 13       | DLAB             | SET BRK        | Stick Par.   | Ev. Parity             | Parity EN        | Stop Bits            | WLS                |                   |

| 14       |                  |                |              | Loop                   | Out2             | Out1                 | RTS                | DTR               |

| 15       | Error Rx FIFO    | TEMT           | THRE         | Break Interrupt        | Framing Error    | Parity Error         | Overrun Error      | Data Ready        |

| 16       | DCD              | RI             | DSR          | CTS                    | DDCD             | TERI                 | DDSR               | DCTS              |

| 17       |                  | •              | •            | SCR[7:0]               | 3.12             | 5 A.                 | •                  |                   |

| 18       |                  |                |              | RxData[7:0             |                  |                      |                    |                   |

| 18       |                  |                |              | TxData[7:0             |                  |                      |                    |                   |

| 19       |                  |                | 1            |                        | 6                | MRESET               | UIB Enable         | PROC              |

| 26       |                  |                | TE           | RE                     | FE               | PE                   | BI                 | OE                |

| 27       |                  |                |              |                        | MODEM            | TX Level             | RX Time            | RX Level          |

| 28       |                  | Tx Trigger I   |              |                        |                  |                      | Trigger Level [3:  |                   |

| 29       |                  | Chars in TX I  | Buffer [3:0] |                        |                  | Cha                  | rs in Rx Buffer [3 | 3:0]              |

| 32       |                  |                |              | RxData[7:0             |                  |                      |                    |                   |

| 32       |                  |                |              | TxData[7:0             |                  |                      |                    |                   |

| 32       |                  |                |              | BRR[7:0]               |                  | 1                    | 1                  |                   |

| 33       |                  |                |              |                        | EDSSI            | ELSI                 | ETBEI              | ERBFI             |

| 33       |                  | <b>EVEO 6E</b> |              | BRR[15:8               |                  |                      |                    |                   |

| 34       | FIFO ST          | FIFO ST        | Crit D       |                        | InterruptID[2:0] | Int Pend             | R                  | D /III            |

| 35       | DLAB             | SET BRK        | Stick Par.   | Ev. Parity             | Parity EN        | Stop Bits            | WLS[1:0]           | R/W               |

| 36       | Errer & Der EIEO | TEMT           | TUDE         | Loop                   | Out2             | Out1                 | RTS                | DTR<br>Data Baada |

| 37<br>38 | Error Rx FIFO    | TEMT           | THRE         | Break Interrupt<br>CTS | Framing Error    | Parity Error<br>TERI | Overrun Error      | Data Ready        |

| 38<br>39 | DCD              | RI             | DSR          | SCR[7:0]               | DDCD             | IEKI                 | DDSR               | DCTS              |

| 48       | TEST             | RX MODE        | CLOCK        | TX ENABLE              | CROSSPOINT       | UCONN                | R/W                |                   |

| 40       | 1651             | KA WODE        | CLUCK        | IA ENADLE              | SWITCH           | SWITCH               | N/ W               |                   |

| 49       |                  | SDORIE         | SDIROE IE    | SDIRIE                 |                  | SDOR EMT             | SDIR OE            | SDIR FULL         |

| 50       |                  |                |              | Receive[15:            | 8]               |                      |                    |                   |

| 51       |                  |                |              | Receive[7:0            | )]               |                      |                    |                   |

| 52       |                  |                |              | Transmit[15            | :8]              |                      |                    |                   |

| 53       |                  |                |              | Transmit[7:            | 0]               |                      |                    |                   |

| 64/65    |                  |                |              | Data[7:0]              |                  |                      |                    |                   |

Table 4. H8 Peripheral Register Contents

This Information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing. No responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

| #          | 7        | 6                   | 5         | 4               | 3         | 2          | 1           | 0       |  |  |  |

|------------|----------|---------------------|-----------|-----------------|-----------|------------|-------------|---------|--|--|--|

| 66         |          |                     |           |                 | SDISP POL | DISP CLKEN | CLK FREQ    | DDREMT  |  |  |  |

| 67         |          | Transmit Data [7:0] |           |                 |           |            |             |         |  |  |  |

| 68         |          | Receive Data [7:0]  |           |                 |           |            |             |         |  |  |  |

| 69         |          |                     |           | Reset Data [7   | /:0]      |            |             |         |  |  |  |

| 72         |          |                     |           | WDT[7:0]        |           |            |             |         |  |  |  |

| 80         | TEST CLK | Unused              | Unused    | UART SEL        | DALLAS EN | RAM SEL7   | DISP        | SRAM16  |  |  |  |

| 81         | WDT INT  | RTC INT             | KEYINT    | DALLAS INT      | FA INT    | UA INT     | SSINT       | MONINT  |  |  |  |

| 82         | WDT IE   | RTC IE              | KEY IE    | DALLAS IE       | FA IE     | UA IE      | SS IE       | MONIE   |  |  |  |

| 84         |          |                     |           | Test Key[7:     |           |            |             |         |  |  |  |

| 85         |          |                     | USCCLK EN | BUCLK EN        | FUCLK EN  |            | DSPPLL[2:0] |         |  |  |  |

| 96         |          |                     |           | TR[1]           |           |            |             |         |  |  |  |

| 97         |          |                     |           | TR[2]           |           |            |             |         |  |  |  |

| 98         |          |                     |           | TR[3]           |           |            |             |         |  |  |  |

| 99         |          |                     |           | TR[4]           |           | _          |             |         |  |  |  |

| 100        |          |                     |           | TR[5]           |           | 0          |             |         |  |  |  |

| 101        |          |                     |           | AR[1]           |           | 11         |             |         |  |  |  |

| 102        |          |                     |           | AR[2]           | 4.10      |            |             |         |  |  |  |

| 103<br>104 | INTEN    | TIMWEN              | ALAWEN    | AR[3]<br>PWRUEN | AGCENN    | FBENN      | Unused      | Unused  |  |  |  |

| 104        | INT      | TIMER               | ALAWEN    | IWKOEN          | APWRUP    | OSCFAIL    | 32K PRESENT | TESTOUT |  |  |  |

| 105        |          | TIVILK              | TXENABLE  | SERDISP MODE    | AI WKOI   | OSCIAL     | 52KTRESERT  | ILSIOUI |  |  |  |

| 100        |          |                     | NMI       | SERDISI MODE    | CO        |            |             |         |  |  |  |

|            |          |                     |           |                 |           |            |             |         |  |  |  |

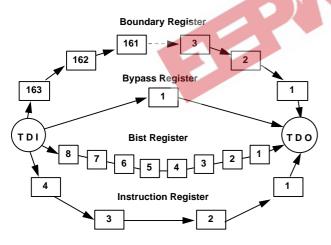

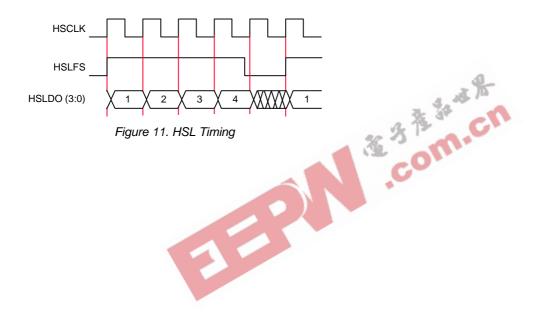

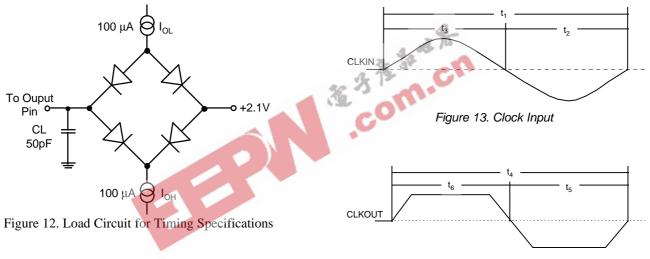

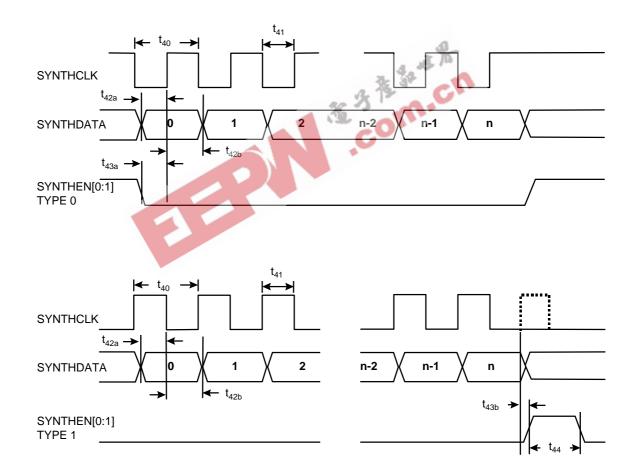

H8 Peripheral Register Contents (Continued)