## Microprocessor Supervisory Circuit

### ADM1232

### **FEATURES**

Superior Upgrade for MAX1232 and Dallas DS1232 Low Power Consumption (500  $\mu$ A max) Adjustable Precision Voltage Monitor with +4.5 V and +4.75 V Options Adjustable STROBE Monitor with 150 ms, 600 ms or

1.2 sec Options

No External Components

APPLICATIONS

Microprocessor Systems

Portable Equipment

Computers

Controllers

Intelligent Instruments

Automotive Systems

Protection Against Damage Caused by µP Failure

### **GENERAL DESCRIPTION**

The ADM1232 is a superior, pin-compatible upgrade for the MAX1232 and the DS1232LP and DS1232. The Analog Devices ADM1232 is a microprocessor monitoring circuit that can monitor:

- 1. Microprocessor Supply Voltage.

- 2. Whether a Microprocessor has locked-up.

- 3. An External Interrupt.

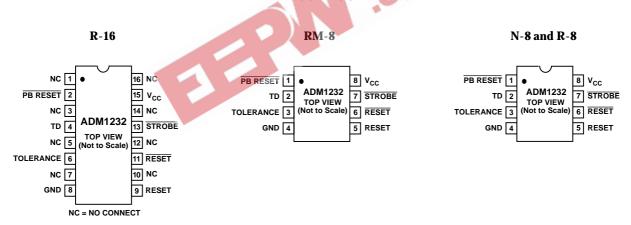

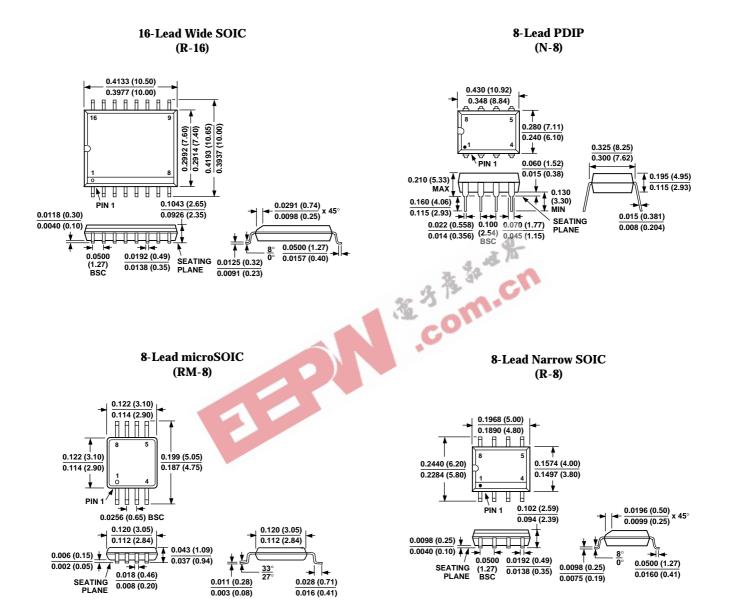

The ADM1232 is available in four different packages:

- 1. The ADM1232ARM in an 8-lead microSOIC (RM-8).

- 2. The ADM1232AN in an 8-lead PDIP (N-8).

- 3. The ADM1232ARW in a 16-lead wide SOIC (R-16).

- 4. The ADM1232ARN is an 8-lead narrow SOIC (R-8).

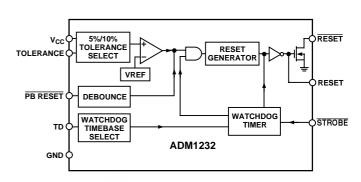

### FUNCTIONAL BLOCK DIAGRAM

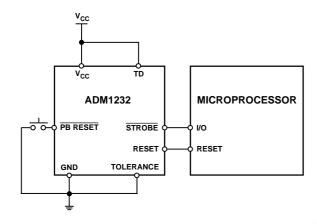

Figure 1. Typical Supply Monitoring Application

#

| Parameter                                                                               | Min                      | Тур                   | Max                           | Units                    | Test Conditions/Comments                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------|--------------------------|-----------------------|-------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEMPERATURE                                                                             | -40                      |                       | +85                           | °C                       | $T_A = T_{MIN}$ to $T_{MAX}$                                                                                                                                                                                                                        |

| POWER SUPPLY<br>Voltage<br>Current                                                      | 4.5                      | 5.0<br>20<br>200      | 5.5<br>50<br>500              | V<br>μΑ<br>μΑ            | $V_{IL}$ , $V_{IH}$ = CMOS Levels $V_{IL}$ , $V_{IH}$ = TTL Levels                                                                                                                                                                                  |

| STROBE AND PB RESET INPUTS Input High Level Input Low Level                             | 2.0<br>-0.3              |                       | V <sub>CC</sub> + 0.3<br>+0.8 | V<br>V                   |                                                                                                                                                                                                                                                     |

| INPUT LEAKAGE CURRENT<br>(STROBE, TOLERANCE)<br>TD                                      | -1.0                     | 1.6                   | +1.0                          | μ <b>Α</b><br>μ <b>Α</b> |                                                                                                                                                                                                                                                     |

| OUTPUT CURRENT RESET RESET, RESET                                                       | 8<br>-8                  | 10<br>-12             |                               | mA<br>mA                 | When $V_{\rm CC}$ Is at 4.5 V–5.5 V When $V_{\rm CC}$ Is at 4.5 V–5.5 V                                                                                                                                                                             |

| OUTPUT VOLTAGE RESET/RESET  RESET/RESET High Level RESET/RESET Low Level                | V <sub>CC</sub> - 0.5    | V <sub>CC</sub> - 0.1 | 0.4                           | V                        | While sourcing less than 500 $\mu A,$ RESET remains within 0.5 V of $V_{CC}$ on power-down until $V_{CC}$ drops below 2.0 V. While sinking less than 500 $\mu A,$ RESET remains within 0.5 V of GND on power-down until $V_{CC}$ drops below 2.0 V. |

| 1 V OPERATION RESET Output Voltage RESET Output Voltage                                 | 2.4                      | V <sub>CC</sub> - 0.1 | 36.3                          | V<br>V                   | While Sourcing Less than 50 μA<br>While Sinking Less than 50 μA                                                                                                                                                                                     |

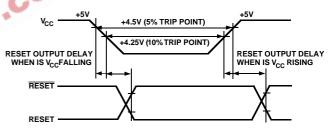

| V <sub>CC</sub> TRIP POINT 5% 10%                                                       | 4.5<br>4.25              | 4.62<br>4.37          | 4.74<br>4.49                  | V<br>V                   |                                                                                                                                                                                                                                                     |

| CAPACITANCE Input (STROBE, TOLERANCE) Output (RESET, RESET)                             | X                        |                       | 5<br>7                        | pF<br>pF                 | $T_A = +25$ °C $T_A = +25$ °C                                                                                                                                                                                                                       |

| PB RESET Time Delay                                                                     | 20<br>1                  | 4                     | 20                            | ms<br>ms                 | PB RESET Must Be Held Low for a Minimum of 20 ms to Guarantee a Reset                                                                                                                                                                               |

| RESET ACTIVE TIME  STROBE  Pulse Width  Timeout Period                                  | 70<br>62.5<br>250<br>500 | 150<br>600<br>1200    | 250<br>1000<br>2000           | ns<br>ns<br>ms<br>ms     | TD = 0 V<br>TD = Floating<br>TD = V <sub>CC</sub>                                                                                                                                                                                                   |

| V <sub>CC</sub><br>Fall Time<br>Rise Time                                               | 10<br>0                  |                       |                               | μs<br>μs                 | Guaranteed by Design<br>Guaranteed by Design                                                                                                                                                                                                        |

| V <sub>CC</sub> FAIL DETECT TO RESET OUTPUT DELAY RESET AND RESET Are Logically Correct | 950                      | 610                   | 50                            | μs                       | After V <sub>CC</sub> Falls Below the Set Tolerance Voltage (Figure 5)                                                                                                                                                                              |

| _                                                                                       | 250                      | 610                   | 1000                          | ms                       | After V <sub>CC</sub> Rises Above the Set Tolerance Voltage                                                                                                                                                                                         |

-2-

Specifications subject to change without notice.

REV. B

### ADM1232

| <b>ABSOLUTE MAXIMUM RATINGS*</b> (T <sub>A</sub> = +25°C unless otherwise noted) |

|----------------------------------------------------------------------------------|

| V <sub>CC</sub> +5.5 V                                                           |

| Logic Inputs0.3 V to $V_{CC}$ + 0.3 V                                            |

| Storage Temperature Range65°C to +150°C                                          |

| Lead Temperature (Soldering, 10 sec)+300°C                                       |

| Vapor Phase (60 sec) +215°C                                                      |

| Infrared (15 sec) +220°C                                                         |

| N-8                                                                              |

| Power Dissipation                                                                |

| Derate by 13.5 mW/°C above 25°C                                                  |

| $\theta_{JA}$ Thermal Impedance                                                  |

| R-16                                                                             |

| Power Dissipation 900 mW                                                         |

| Derate by 12 mW/°C above 25°C                                                    |

| $\theta_{JA}$ Thermal Impedance (Still Air)                                      |

| RM-8                                                  |

|-------------------------------------------------------|

| Power Dissipation 900 mW                              |

| Derate by 12 mW/°C above 25°C                         |

| θ <sub>JA</sub> Thermal Impedance (Still Air) 206°C/W |

| R-8                                                   |

| Power Dissipation                                     |

| Derate by 12 mW/°C above 25°C                         |

| $\theta_{JA}$ Thermal Impedance (Still Air)           |

| * * * * * * * * * * * * * * * * * * * *               |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods of time may affect device reliability.

### **ORDERING GUIDE**

| Model      | Temperature<br>Range   | Package<br>Options* |

|------------|------------------------|---------------------|

| ADM1232ARM | -40°C to +85°C         | RM-8                |

| ADM1232AN  | -40°C to +85°C         | N-8                 |

| ADM1232ARW | <b>-4</b> 0°C to +85°C | R-16                |

| ADM1232ARN | -40°C to +85°C         | R-8                 |

\*N= Plastic DIP; R = Small Outline; RM = microSOIC.

### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADM1232 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. B \_3\_

### ADM1232

### PIN FUNCTION DESCRIPTIONS

| Mnemonic  | Function                                                                                                                                                                                                                                                                                                                           |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB RESET  | Push Button Reset Input. This debounced input will ignore pulses of less than 1 ms and is guaranteed to respond to pulses greater than 20 ms.                                                                                                                                                                                      |

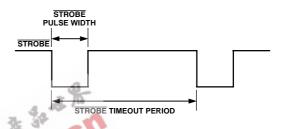

| TD        | Time Delay Set allows the user to select the maximum amount of time the ADM1232 will allow the STROBE input to remain inactive (i.e., STROBE is not receiving any high-to-low transitions), without forcing the ADM1232 to generate a RESET pulse. (See STROBE specifications, Figure 4 and the note on STROBE timeout selection.) |

| TOLERANCE | Tolerance Input. This input will determine how much the supply voltage will be allowed to decrease (as a percentage tolerance) before a RESET is asserted. Connect to $V_{\rm CC}$ for 10% and GND for 5%.                                                                                                                         |

| GND       | 0 V ground reference for all signals.                                                                                                                                                                                                                                                                                              |

| RESET     | Active high logic output. Will be asserted when:  1. V <sub>CC</sub> decreases below the amount specified by the TOLERANCE input or,  2. PB RESET is forced low or,  3. If there are no high-to-low transitions within the limits set by TD at STROBE or,  4. During power-up.                                                     |

| RESET     | Inverse of RESET, with an open drain output.                                                                                                                                                                                                                                                                                       |

| STROBE    | The STROBE input is used to monitor the activity of a microprocessor. If there are no high-to-low transitions within the time specified by TD, a reset will be asserted.                                                                                                                                                           |

| $V_{CC}$  | Power supply input +5 V.                                                                                                                                                                                                                                                                                                           |

### PIN CONFIGURATIONS

-4- REV. B

ADM1232

### CIRCUIT INFORMATION

### **PB RESET**

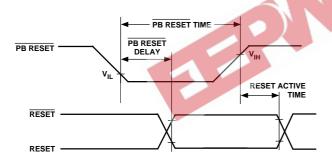

The PB RESET input makes it possible to manually reset a system using either a standard push-button switch or a logic low input. An internal debounce circuit provides glitch immunity when used with a switch, reducing the effects of glitches on the line. The debounce circuit is guaranteed to cause the ADM1232 to assert a reset if PB RESET is brought low for more than 20 ms and is guaranteed to ignore low inputs of less than 1 ms.

Figure 2. Typical Push Button Reset Application

Figure 3. PB RESET

### **STROBE** Timeout Selection

TD or time delay set is used to set the Strobe Timeout Period. The Strobe Timeout Period is defined as being the maximum time between high-to-low transitions (Figure 4) that  $\overline{STROBE}$  will accept before a reset will be asserted. The Strobe timeout settings are listed in Table I.

Table I.

| Condition                 | Min         | Тур        | Max         | Units    |

|---------------------------|-------------|------------|-------------|----------|

| TD = 0 V<br>TD = Floating | 62.5<br>250 | 150<br>600 | 250<br>1000 | ms<br>ms |

| $TD = V_{CC}$             | 500         | 1200       | 2000        | ms       |

Figure 4. STROBE Parameters

Figure 5. Reset Output Delay

### **TOLERANCE**

The TOLERANCE input is used to determine the level  $V_{\rm CC}$  can vary below 5 V without the ADM1232 asserting a reset. Connecting TOLERANCE to ground will select a –5% tolerance level and will cause the ADM1232 to generate a reset if  $V_{\rm CC}$  falls below 4.75 V (typical). If TOLERANCE is connected to  $V_{\rm CC}$  a –10% tolerance level is selected and will cause the ADM1232 to generate a reset if  $V_{\rm CC}$  falls below 4.5 V (typical). Check the parameters for the  $V_{\rm CC}$  trip point in the ADM1232 Specifications for more information.

### RESET AND RESET OUTPUTS

While RESET is capable of sourcing and sinking current, RESET is an open drain MOSFET which sinks current only. Therefore, it is necessary to pull this output high.

REV. B \_5\_

### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

-6-