# **CXA2055P**

# **Preamplifier for High Resolution Computer Display**

#### **Description**

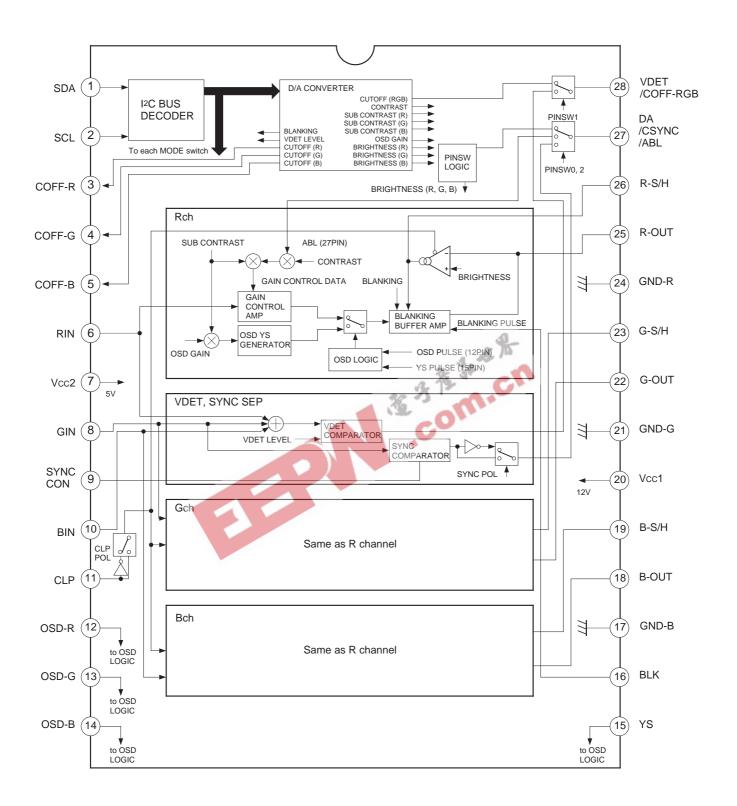

The CXA2055P is a bipolar IC developed for high resolution computer displays.

#### **Features**

- Built-in wide band amplifier (130 MHz/–3 dB typ.@4 Vp-p)

- Input dynamic range: 1.0 Vp-p (typ.)

- R, G and B in a single package

- I2C bus control

Contrast control

Subcontrast control

Brightness control

OSD contrast control

Power save function

Input clamp pulse polarity selection

Output composite sync polarity selection

5-channel, 8-bit D/A

Blanking level control

- Built-in sync separator (G channel only)

- Built-in blanking mixing function

- · Built-in OSD mixing function

- Built-in ABL function

- Video interval detection function

#### **Applications**

High resolution computer displays

#### Structure

Bipolar silicon monolithic IC

## **Absolute Maximum Ratings** (Ta=25 °C)

- Supply voltage Vcc 14 V

- Operating temperature

Topr –20 to +75 °C

- Storage temperature Tstg —65 to +150 °C

- Allowable power dissipation

Pp 1794 mW

(when mounted on a 11.5 cm  $\times$  12.0 cm substrate)

# **Operating Conditions**

Recommended supply voltage

6 RIN

8 GIN

Vcc2

Vcc1 12±0.5 V

Vcc2 5±0.25 V

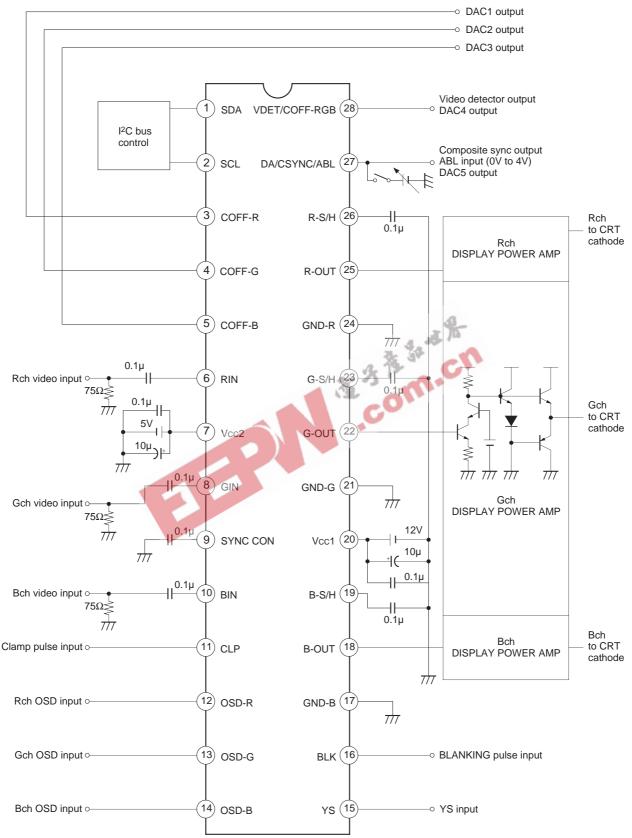

1 SDA VDET/COFF-RGB (28)

(2) SCL DA/CSYNC/ABL (27)

(3) COFF-R R-S/H (26)

(4) COFF-G R-OUT (25)

(5) COFF-B GND-R (24)

G-S/H (23)

G-OUT (22)

GND-G (21)

9 SYNC CON Vcc1 (20)

(10) BIN B-S/H (19)

(11) CLP B-OUT (18)

(12) OSD-R GND-B (17)

(13) OSD-G BLK (16)

(14) OSD-B YS (15)

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

# **Pin Description**

| Pin<br>No. | Symbol | Pin<br>voltage | Equivalent circuit                           | Description                                                                     |

|------------|--------|----------------|----------------------------------------------|---------------------------------------------------------------------------------|

| 1          | SDA    | _              | Vcc2  50μA  4k  7.5k  7.5k  7.5k  7.5k  815k | I <sup>2</sup> C bus address and data input.                                    |

| 2          | SCL    | _              | Vcc2  50μA  4k  10k  10k  10k  15k           | I <sup>2</sup> C bus clock signal input.                                        |

| 3          | COFF-R |                | Vcc2                                         | D/A converter outputs.                                                          |

| 4          | COFF-G | -              | 60k 3<br>\$50k                               | The variable range is 1 to 4 V. Use as cut-off control voltages is recommended. |

| 5          | COFF-B |                | 100 (5) GND                                  | recommended.                                                                    |

| 6          | RIN    |                | Vcc1<br>Vcc2<br>  1k ≥ 1k ≥                  | R, G and B inputs. When clamped, the input                                      |

| 8          | GIN    | _              | 6 124 5 k 2k 2k 2k 3                         | voltage black level is approximately 3.2 V. Connect 0.1 µF or more in           |

| 10         | BIN    |                | 50μA 1mA 1k                                  | series as a clamp capacitor.                                                    |

| 7          | Vcc2   | 5 V            |                                              | 5 V power supply.                                                               |

| Pin<br>No. | Symbol      | Pin<br>voltage | Equivalent circuit                          | Description                                                                                                               |

|------------|-------------|----------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 9          | SYNC<br>CON |                | Vcc2  24k   70k  10k  50µA 50µA  \$1k       | Sync signal separation circuit block during sync-on-video signal input. Connect a sample-and-hold capacitor.              |

| 11         | CLP         | _              | Vcc1 22μA 330k                              | Clamp pulse input. The polarity can be switched via the I <sup>2</sup> C bus. The threshold level is approximately 1.3 V. |

| 12         | OSDR        |                | Vcc1 150μA                                  | CU                                                                                                                        |

| 13         | OSDG        | _              | 124<br>(13)<br>(13)                         | R, G and B OSD pulse inputs. The threshold level is approximately 1 V.                                                    |

| 14         | OSDB        |                | GND T                                       |                                                                                                                           |

| 15         | YS          | _              | 150μA<br>150μA<br>1.25V                     | OSD-BLK pulse input. The threshold level is approximately 1.7 V.                                                          |

| 16         | BLK         | _              | Vcc1<br>124<br>16<br>100μA<br>100μA<br>1.5V | BLK pulse input. The threshold level is approximately 1.5 V.                                                              |

| Pin<br>No. | Symbol               | Pin<br>voltage | Equivalent circuit                                        | Description                                                                                                                                                                                                                                                          |

|------------|----------------------|----------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17         | GND-B                |                |                                                           |                                                                                                                                                                                                                                                                      |

| 21         | GND-G                | 0 V            |                                                           | R, G and B independent GND.                                                                                                                                                                                                                                          |

| 24         | GND-R                |                |                                                           |                                                                                                                                                                                                                                                                      |

| 18         | B-OUT                |                | Vcc1                                                      |                                                                                                                                                                                                                                                                      |

| 22         | G-OUT                | _              | 200 (22)                                                  | R, G and B outputs.                                                                                                                                                                                                                                                  |

| 25         | R-OUT                |                | GND                                                       |                                                                                                                                                                                                                                                                      |

| 19         | B-S/H                |                | 1k                                                        | A-                                                                                                                                                                                                                                                                   |

| 23         | G-S/H                | _              | 19 23                                                     | Connection for external sample-<br>and-hold capacitor (0.1 µF).                                                                                                                                                                                                      |

| 26         | R-S/H                |                | 225µA 2.5V (26)                                           |                                                                                                                                                                                                                                                                      |

| 21         | Vcc1                 | 12 V           |                                                           | 12 V power supply.                                                                                                                                                                                                                                                   |

| 27         | DA<br>/CSYNC<br>/ABL |                | Vcc2  5k \$ 100  4k 7.4k 7.4k 7.4k 7.4k 7.4k 7.4k 7.4k 7. | General-purpose D/A converter output. Composite sync output. TTL drive is possible.  VL=0.5 V or less, VH=4.0 V or more RGB output amplitude gain compensation input.  (common for all three channels) Function switching is performed via the I <sup>2</sup> C bus. |

| 28         | VDET<br>/COF-RGB     | _              | Vcc2 \$100 \$5k  Vcc2  \$100 \$5k  GND                    | Video signal detection output.  VL=0.5 V or less, VH=4.0 V or more General-purpose D/A converter output.  The variable range is 1 to 4 V. Function switching is performed via the I <sup>2</sup> C bus.                                                              |

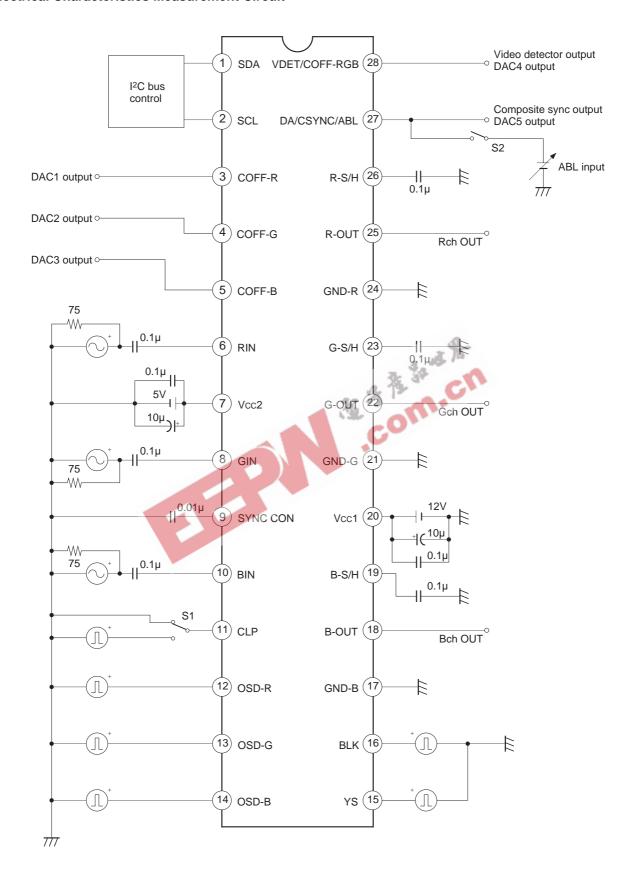

#### **Electrical Characteristics Measurement Circuit**

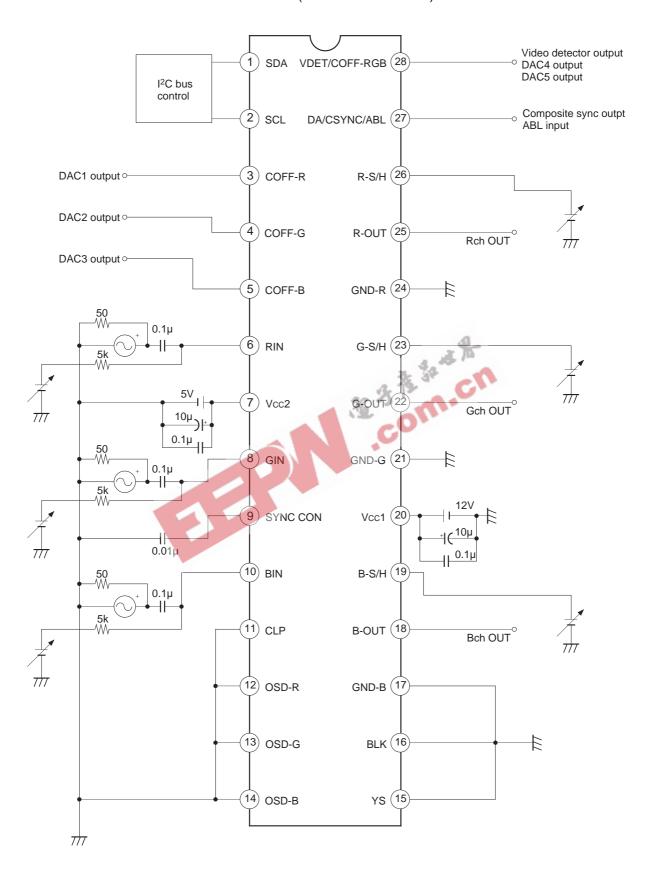

# **Electrical Characteristics Measurement Circuit** (For AC Measurement)

# **Electrical Characteristics**

Ta=25 °C Vcc1=12 V Vcc2=5 V

| No. | Measurement item       | Symbol      | Measurement contents                                                                                                                                                                                                                                                                | Min. | Тур. | Max. | Unit |

|-----|------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|     | Current                | Icc1 (12 V) | S1 : GND, S2 : OFF<br>Input signal : none                                                                                                                                                                                                                                           | _    | 82   | 115  | mA   |

| 1   | consumption Icc2 (5 V) |             |                                                                                                                                                                                                                                                                                     | _    | 40   | 55   | mA   |

| 2   | Frequency response     | f 130 MHz   | Input continuous 1 MHz and 130 MHz sine waves at 0.7 Vp-p.  Measure the output amplitude gain difference at this time.  Gain difference [dB] =20log (Vout 130M)  RGB input signal (RGB input pins)  RGB input signal (RGB input pins)  O.7Vp-p  CLP potential (approximately 3.2 V) |      | -3.0 | _    | dB   |

| 3   | Contrast               | CONTMAX     | S1: Pulse, S2: OFF  Measure the output signal amplitude Vout when a 0.7 Vp-p video signal is input.  Calculate the contrast gain from this Vout.  CONTMAX [dB] =20log (Vout / 0.7)  RGB input signal  0.7Vp-p  Either with or without sync-on-green (sync signal)                   | 16.0 | 16.5 |      | dB   |

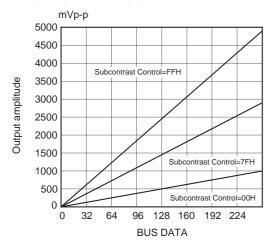

| 4   | Subcontrast<br>gain    | SUBgain     | S1: Pulse, S2: OFF  Measure the variable width of the output signal amplitude Vout when a 0.7 Vp-p video signal is input.  Gain difference [dB]=  CONTMAX [dB] -20log (Voutsubmin 0.7)  RGB output signal  SUBmax SUBmin  Either with or without sync-on-green (sync signal)        | 10.5 | 13.5 | _    | dB   |

| No. | Measurement item                | Symbol  | Measurement contents                                                                                                                                         | Min. | Тур. | Max. | Unit |

|-----|---------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| 5   | Brightness                      | BRTmax  | S1 : Pulse, S2 : OFF CLP pulse width: 350 ns Measure the black level of the RGB output signal.  RGB output signal                                            | 3.4  | 3.7  | _    | V    |

| 3   | control                         | BRTmin  | Black level  Either with or without sync-on-green (sync signal)                                                                                              | 1    | 0.5  | 0.7  | V    |

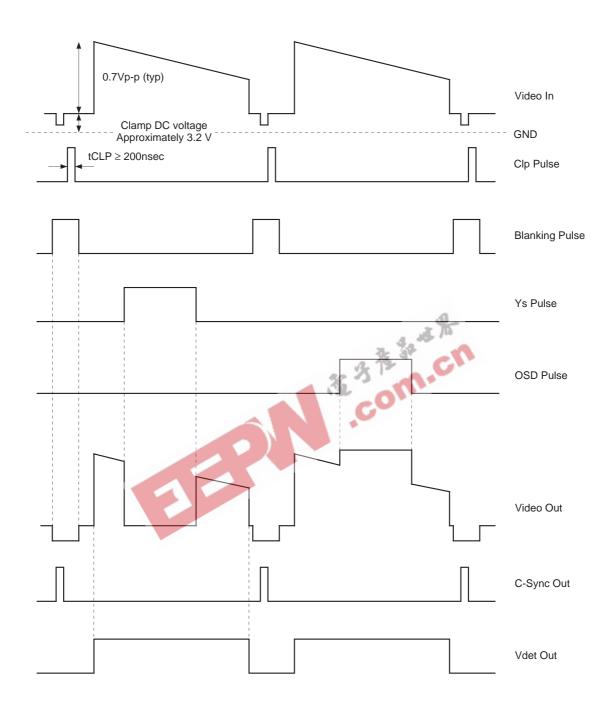

| 6   | Input dynamic range             | Drang   | S1: Pulse, S2: OFF  Measure the level at which the output gain can be secured when the input video signal level is varied.                                   | 0.9  | 1    | 1.2  | Vp-p |

| 7   | Minimum<br>clamp pulse<br>width | CLPmin  | S1: Pulse, S2: OFF  Measure the clamp pulse width over which the black level of the output signal Vout does not change.  Video input  Pulse width  CLP pulse | 200  |      | -    | nsec |

| 8   | OSD<br>control range            | OSDcont | S1: Pulse, S2: OFF  Measure the variable width of the output signal Vout when a 0.7 Vp-p video signal is input.  Gain difference [dB] =20log (OSDmax OSDmin) | 4.0  | 5.0  | _    | dB   |

| 9   | BLK control                     | BLKmax  | S1 : Pulse, S2 : OFF  Measure the BLK level of the output signal when a 5.0 Vp-p BLK signal is input                                                         | 1.7  | 1.9  |      | V    |

| 9   |                                 | BLKmin  | VBLK GND                                                                                                                                                     | _    | 0.1  | 0.4  | v    |

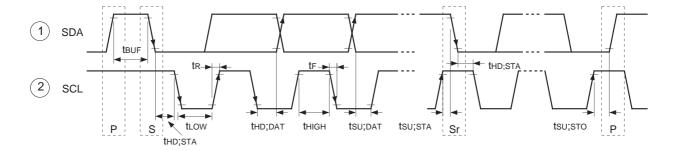

# (I<sup>2</sup>C BUS Logic System)

| No. | ltem                                                        | Symbol    | Min. | Тур. | Max. | Unit |

|-----|-------------------------------------------------------------|-----------|------|------|------|------|

| 1   | High level input voltage                                    | Vıн       | 3.0  | _    | 5.0  | V    |

| 2   | Low level input voltage                                     | VıL       | 0    | _    | 1.5  | V    |

| 3   | Low level output voltage SDA, during current inflow of 3 mA | Vol       | 0    | _    | 0.4  | V    |

| 4   | Maximum clock frequency                                     | fscL      | 0    | _    | 100  | kHz  |

| 5   | Minimum waiting time for data change                        | tBUF      | 4.7  | _    | _    | μs   |

| 6   | Minimum waiting time for data transfer start                | thd; STA  | 4.0  | _    | _    | μs   |

| 7   | Low level clock pulse width                                 | tLOW      | 4.7  | _    | _    | μs   |

| 8   | High level clock pulse width                                | thigh     | 4.0  | 西西   | _    | μs   |

| 9   | Minimum waiting time for start preparation                  | tsu; sta  | 4.7  | GU   | _    | μs   |

| 10  | Minimum data hold time                                      | thd; dat  | 5    | _    | _    | μs   |

| 11  | Minimum data preparation time                               | tsu; dat  | 250  | _    | _    | ns   |

| 12  | Rise time                                                   | tr        | _    | _    | 1000 | ns   |

| 13  | Fall time                                                   | tF        | _    | _    | 300  | ns   |

| 14  | Minimum waiting time for stop preparation                   | tsu ; sto | 4.0  | _    | _    | μs   |

# I<sup>2</sup>C BUS Control Signal

#### 1. Application

The CXA2055P is a preamplifier for computer displays, and combines three R, G and B channels into a single package. All controls such as the contrast and black level for each channel are performed via I<sup>2</sup>C bus control.

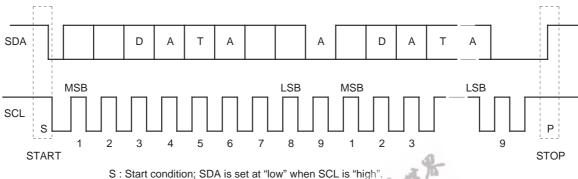

#### 1) I2C bus

Two wires (SDA, SCL) provide control over start, stop, data transfer, synchronization and collision avoidance. The IC outputs are either open collector or open drain, forming a bus line in the wired OR format. The bus signal configuration is as follows.

P: Stop condition; SDA is set at "high" when SCL is "high"

A: Acknowledge; Signal sent from the slave.

Data is transmitted by MSB-first. One data unit consists of 8 bits, to which the acknowledge signal, which indicates that the data has been accepted by the slave, is attached at the end. Normally, the slave \*1 IC receives data at the rising edge of SCL and the master \*2 IC changes data at the falling edge of SCL. The actual data format is as follows.

|   | Slave address |   | Subaddress |   | DATAG | _ | DATA  | _ | DATAG |   | В |

|---|---------------|---|------------|---|-------|---|-------|---|-------|---|---|

| 8 | 40H           | A | **H        | A | DATA0 | A | DATA1 | A | DATA2 | A |   |

#### Slave address configuration

| BIT8 | BIT7          | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 |  |

|------|---------------|------|------|------|------|------|------|--|

|      | Slave address |      |      |      |      |      |      |  |

The slave address is an address unique to each IC, and is assigned according to the IC functions. The upper 7 of the 8 bits are the unique address and the final bit is the R/W bit. The R/W bit indicates read \*3 when 1 and write \*4 when 0. 40H is allotted as the slave address for the CXA2055P. (This is write only and there is no read mode.)

The subaddress is the assigned address within the IC, and is used for the various IC adjustments. The subaddress is sent just once following the slave address, and is automatically incremented thereafter until a stop condition is sent.

\*1 Slave : An IC that is placed under the control of the master.

In a normal system, all devices excluding the central microcomputer are slaves.

\*2 Master: A central microcomputer or other controlling IC.

\*3 Read : Mode where data is read from master to slave.

\*4 Write : Mode where data is written from master to slave.

# 2) Register map

• Slave address : 40H

• "\*" indicates undefined.

• Values inside parentheses ( ) are the initial setting values (during power-on reset) (undetermined when not indicated)

# Slave address configuration

| BIT8 | BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 |

|------|------|------|------|------|------|------|------|

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | R/W  |

| SUB ADDRESS | BIT7    | BIT6         | BIT5     | BIT4     | BIT3       | BIT2      | BIT1       | BIT0    |

|-------------|---------|--------------|----------|----------|------------|-----------|------------|---------|

| 00н         |         | CONTRAST     |          |          |            |           |            |         |

| 01н         |         |              |          | SUB CON  | ITRAST R   |           |            |         |

| 02н         |         |              |          | SUB CON  | ITRAST G   |           |            |         |

| 03н         |         |              |          | SUB CON  | ITRAST B   |           |            |         |

| 04н         | *       | *            |          | OSD      | GAIN       |           | BRT MO     | ODE (2) |

| 05н         |         |              |          | BRIGHTNE | ESS R (DA) | 2_        |            |         |

| 06н         |         |              |          | BRIGHT   | NESS G     | 3.70      |            |         |

| 07н         |         | BRIGHTNESS B |          |          |            |           |            |         |

| 08н         |         | CUT OFF RGB  |          |          |            |           |            |         |

| 09н         |         |              |          | CUT      | OFF R      |           |            |         |

| ОАн         |         |              |          | CUT (    | OFF G      |           |            |         |

| 0Вн         |         |              |          | CUT (    | OFF B      |           |            |         |

| 0Сн         | BLK (0) | *            |          |          |            | LEVEL (0) |            |         |

| UCH         | MODE    | *            |          |          | DLAINNING  | LEVEL (U) |            |         |

| 0Dн         | BRT     | SYNC         | VDET     | POWER    | *          | CLP (O)   | VDET       | I E\/EI |

| UDH         | SW (0)  | POL (0)      | MODE (0) |          |            | CLF (U)   | VDET LEVEL |         |

| 0Ен         |         |              | *        | ale.     | D/A        | PINSW2    | PINSW1     | PINSW0  |

| UEH         | *       | *            | 本        | *        | TEST (0)   | (0)       | (0)        | (0)     |

SONY CXA2055P

3) Description of registers (Numbers inside parentheses ( ) indicate the number of bits.)

CONTRAST (8) : Adjusts the R, G and B-OUT (Pins 25, 22 and 18) output amplitude gain

commonly for all three channels.

SUB CONTRAST (8) : Adjusts the R, G and B-OUT (Pins 25, 22 and 18) output amplitude gain

independently for each channel.

OSD GAIN (4) : Adjusts the OSD R, G and B (Pins 12, 13 and 14) OSD interval output signal

gain commonly for all three channels.

BRTMODE (2) : This register changes the output dynamic range.

The 2H setting is recommended.

0H : Output dynamic range 0.5 V to 4.5 V 1H : Output dynamic range 0.5 V to 5.5 V

2H : Output dynamic range 1.0 V to 6.5 V (recommended)

3H: Output dynamic range 2.0 V to 7.5 V

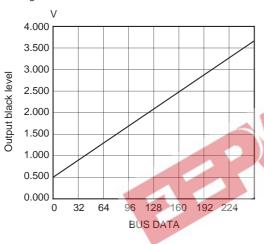

BRIGHTNESS (8) : Controls the output black level potential.

(Three-channel independent and common control can be selected by BRTSW. During three-channel common mode, control is performed by the G channel.)

CUT OFF (8) : This is a general-purpose DAC. Use as a cut-off control is recommended.

BLK MODE (1) : Switches the blanking level mode

OH: BLK LEVEL=fixed

1H: BLK LEVEL=variable

BLANKING LEVEL (6) : Sets the blanking level when BLK MODE is set to 1H.

BRTSW (1) : Switches the brightness control between three-channel independent and

three-channel common control. When using three-channel common mode, the

BRIGHTNESS G channel is valid.

0H: Three-channel independent mode

1H: Three-channel common mode

SYNC POL (1) : Switches the sync separator output polarity during sync-on-green input.

0H : Positive polarity1H : Negative polarity

VDET MODE (1) : Switches the video signal detection mode.

0H: B channel only is detected

1H: Signal obtained by adding R, G and B signals is detected

POWER SAVE (1) : Power save mode selector switch.

0H : Power save not performed1H : Power save performed

SONY CXA2055P

CLP (1) : Selects the input clamp pulse polarity.

0H : Positive polarity input1H : Negative polarity input

VDET LEVEL (2) : Threshold level selector switch for video interval detection. The threshold level

changes as follows.

(An input pulse width of as narrow as 10 ns can be detected.)

When VDET MOD=0H

0H: 300 mV or more

1H: Undetectable

2H: Undetectable

2H: 300 mV or more

3H: Undetectable

3H: 600 mV or more

Note) The threshold level when VDET MOD=1H is the total of the three

channel inputs.

D/A TEST (1) : DA TEST switch for IC measurement. Set to 0H.

PINSW : Switches the Pins 27 and 28 functions. ("\*" indicates don't care.)

| F | PINSV | V | 40            | X 12            |

|---|-------|---|---------------|-----------------|

|   |       |   | Pin 28 output | Pin 27 output   |

| 2 | 1     | 0 | 1.3           | -0"             |

| 0 | 0     | 0 | DA (COFF_RGB) | C-SYNC          |

| 1 | 0     | 0 | DA (COFF_RGB) | ABL (CONTRAST)  |

| 0 | 1     | 0 | VDET          | C-SYNC          |

| 1 | 1     | 0 | VDET          | ABL (CONTRAST)  |

| * | 0     | 1 | DA (COFF_RGB) | DA (BRIGHTNESS) |

| * | 1     | 1 | VDET          | DA (BRIGHTNESS) |

**Note)** When the Pin 27 output is set to DA (BRIGHTNESS), BRIGHTNESS is forcibly set to the three-channel common mode.

#### 2. Blanking addition function

The output is blanked while the BLK pin (Pin 16) is high level.

The BLK pin threshold level is approximately 1.5 V.

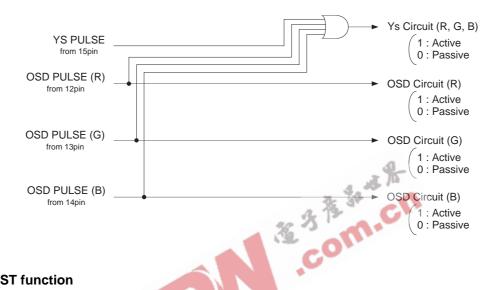

#### 3. OSD addition function and OSD contrast control

OSD can be added to the video signal while the OSD-R, G and B pins (Pins 12, 13 and 14) are high level. OSD blanking is added when any of these three channels is high level.

OSD blanking is also added to all three channels while the YS pin (Pin 15) is high level. See the following logic.

#### 4. CONTRAST function

The CONTRAST function performs gain control for the R, G and B-OUT output amplitudes.

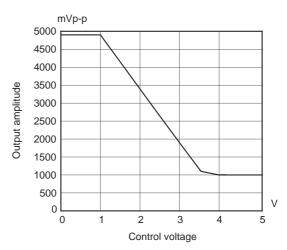

# 5. ABL function

ABL control can be performed by Pin 27 by setting PINSW. The variable range is approximately 13.7 dB.

See the characteristics diagrams hereafter for the control characteristics.

# I/O Signal Example

## **Application Circuit**

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

#### **Notes on Board Pattern and Layout**

- 1. When not using the OSD, YS or BLK pins, connect these pins to GND.

- 2. Care should be taken for the following items regarding the output signals from R, G and BOUT.

- 1) Connect these signal lines so that they are high impedance to external circuits.

- 2) Do not allow current to flow into the IC side.

- 3) Arrange the signal lines so that the distance to the power amplifier is as short as possible.

- 3. The Vcc1 and Vcc2 decoupling capacitors should consist of ceramic capacitors and electrolytic capacitors connected in parallel, and should be connected as close to the IC as possible.

- 4. The R, G and BIN clamp capacitors should be located as close to the IC as possible.

- 5. The sample-and-hold capacitors connected to the R, G and B-S/H pins should be connected as close to the IC as possible.

- 6. The output signals from COFF-R, G and B should be arranged so that capacitance of 20 pF or more is not applied to the pins or the pattern.

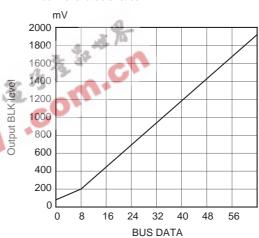

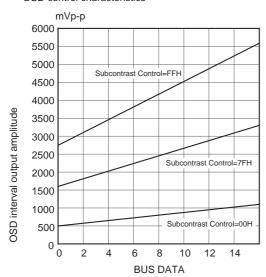

Contrast control characteristics, subcontrast control characteristics Input amplitude 700mVp-p

ABL characteristics

Brightness control characteristics

BLK control characteristics

OSD control characteristics

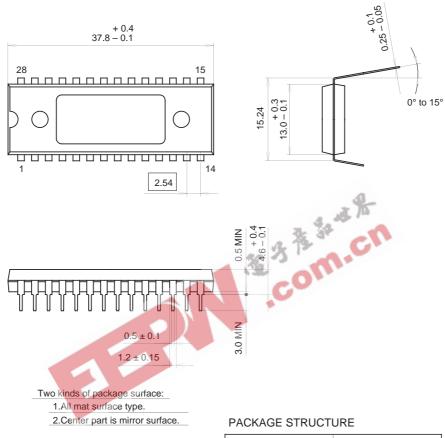

# Package Outline Unit: mm

# 28PIN DIP (PLASTIC)

| SONY CODE  | DIP-28P-03    |

|------------|---------------|

| EIAJ CODE  | DIP028-P-0600 |

| JEDEC CODE |               |

| PACKAGE MATERIAL | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | COPPER ALLOY   |

| PACKAGE MASS     | 4.2g           |