SONY

# CXA1951AQ

# **GPS Down Converter**

# Description

The CXA1951AQ is an IC developed as a GPS down converter, featuring low current consumption and small package. This IC is suitable for the mobile GPS (Global Positioning System).

# Features

- Includes all functions required for the GPS converter

- Total gain: 100 dB or more

- Operating supply voltage range: 2.7 to 5.5 V

- Low current consumption:

- Icc = 30 mA (Typ. at Vcc = 3 V)

- Excellent temperature characteristics

# Applications

GPS (Global Positioning System)

#### Structure

Bipolar silicon monolithic IC

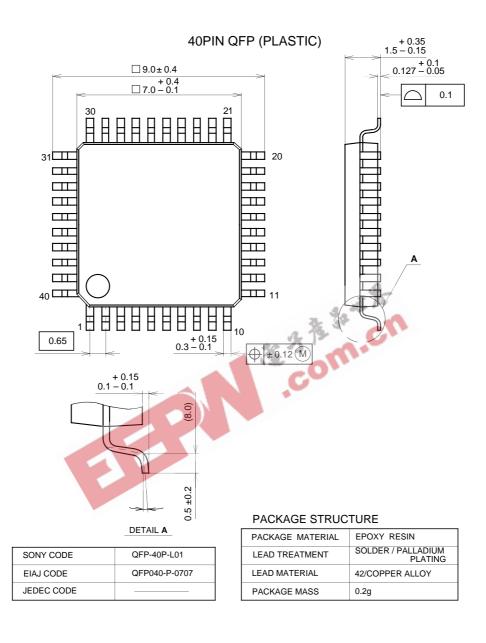

| 40 pin QFP (Plastic) |                      |

|----------------------|----------------------|

| $\sim$               | 40 pin QFP (Plastic) |

|                      |                      |

#### **Absolute Maximum Ratings** (Ta = 25 °C)

| <b>.</b> .    |                                         |       | ,           |    |

|---------------|-----------------------------------------|-------|-------------|----|

| ):<br>        | <ul> <li>Supply voltage</li> </ul>      | Vcc   | 7.0         | V  |

| = 3 V)        | • Operating temperature                 | Topr  | -40 to +85  | °C |

| aracteristics | <ul> <li>Storage temperature</li> </ul> | Tstg  | -65 to +150 | °C |

|               | Allowable power dissipation             | ation |             |    |

| System)       | 3 th                                    | Po    | 200         | mW |

|               | Operating Conditions                    |       |             |    |

| IC            | Supply voltage                          | Vcc   | 2.7 to 5.5  | V  |

|               |                                         |       |             |    |

|               |                                         |       |             |    |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

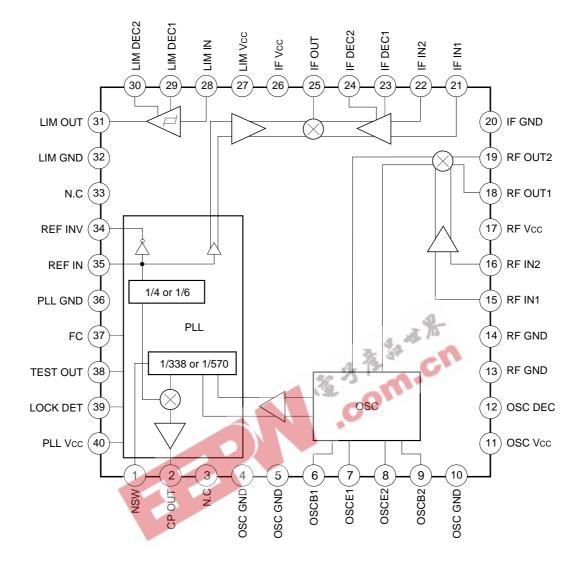

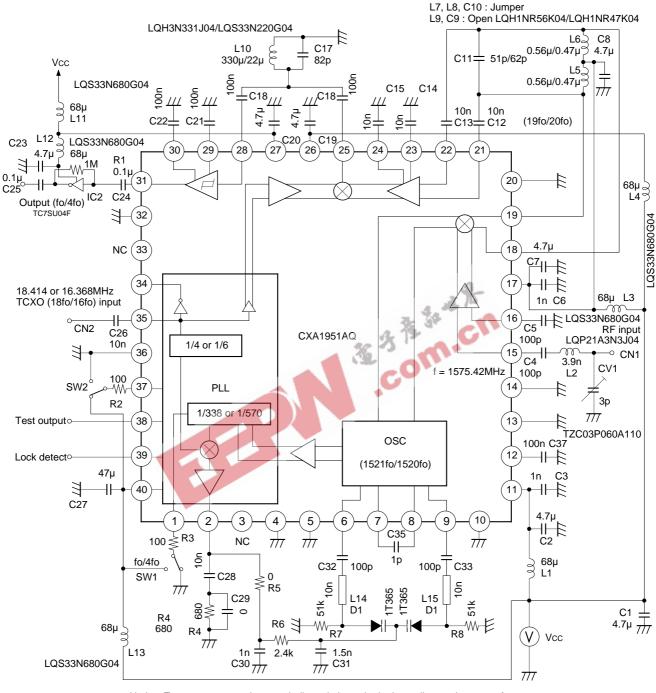

### **Block Diagram and Pin Configuration**

#### **Pin Description**

| Pin<br>No.       | Symbol                           | Pinvoltage                       | Equivalent circuit                                                                    | Description                                                                                                     |

|------------------|----------------------------------|----------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 1                | NSW                              |                                  | Vcc<br>40k<br>200<br>20k<br>20k<br>40k<br>40k<br>40k<br>40k<br>40k<br>40k<br>40k<br>4 | Internal PLL frequency<br>division value switching                                                              |

| 2                | CPOUT                            |                                  | Vcc<br>200<br>Q<br>M<br>GND                                                           | Charge pump output                                                                                              |

| 3, 33            | NC                               |                                  |                                                                                       | Not connected                                                                                                   |

| 4, 5,<br>10      | OSC GND                          | 0 V                              | a som.                                                                                | Ground for the internal oscillator                                                                              |

| 6<br>9<br>7<br>8 | OSCB1<br>OSCB2<br>OSCE1<br>OSCE2 | 2.5 V<br>1.7 V<br>1.7 V<br>2.5 V | Vcc $1.6k$ $1k$ $1k$ $9$ $9$ $8$ $12k$ $12k$ $12k$                                    | Connects the internal<br>oscillator resonator.<br>Connects to main<br>counter input via the<br>internal buffer. |

| 11               | OSC Vcc                          | 3 V                              |                                                                                       | Internal oscillator power supply                                                                                |

| 12               | OSC DEC                          | 1.7 V                            |                                                                                       | Connects decoupling<br>capacitor for the internal<br>oscillator bias power<br>supply                            |

| 13, 14           | RF GND                           | 0 V                              |                                                                                       | RF amplifier ground                                                                                             |

| 15, 16           | RF IN1<br>RF IN2                 | 1.6 V<br>1.6 V                   | Vcc<br>15<br>16<br>12k<br>12k<br>12k<br>12k<br>12k<br>12k<br>12k<br>12k               | RF amplifier input.<br>When using as a single<br>input, ground Pin 16 via<br>the capacitor.                     |

—3—

| Pin<br>No. | Symbol               | Pinvoltage     | Equivalent circuit                                                                                                                        | Description                  |

|------------|----------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 17         | RF Vcc               | 3 V            |                                                                                                                                           | RF amplifier power supply    |

| 18, 19     | RF OUT1<br>RF OUT2   |                | CND                                                                                                                                       | RF amplifier mixer<br>output |

| 20         | IF GND               | 0 V            |                                                                                                                                           | IF amplifier ground          |

| 21, 22     | IF IN1<br>IF IN2     | 1.9 V<br>1.9 V | Vcc<br>21<br>(22)<br>(22)<br>(22)<br>(22)<br>(22)<br>(22)<br>(22)<br>(                                                                    | IF amplifier input           |

| 23, 24     | IF DEC1<br>IF DEC2   | 1.9 V<br>1.9 V | 990<br>200<br>GND<br>23<br>24                                                                                                             | IF amplifier decoupling      |

| 25         | IF OUT               | 2.7 V          | Vcc<br>990 \$ (25)<br>(SND                                                                                                                | IF amplifier mixer<br>output |

| 26         | IF Vcc               | 3 V            |                                                                                                                                           | IF amplifier power           |

|            |                      |                |                                                                                                                                           | supply                       |

| 27         | LIM Vcc              | 3 V            |                                                                                                                                           | Limiter buffer power supply  |

| 28         | LIM IN               | 2.1 V          | Vcc<br>28<br>28<br>28<br>200<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29                                                              | Limiter input                |

| 29, 30     | LIM DEC1<br>LIM DEC2 | 2.1 V<br>2.1 V | $30 \qquad \qquad$ | Limiter decoupling           |

—4—

| Pin<br>No. | Symbol   | Pinvoltage                | Equivalent circuit                                  | Description                                                                                                                                                                                     |

|------------|----------|---------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31         | LIM OUT  |                           | Vcc<br>GND                                          | Limiter buffer output                                                                                                                                                                           |

| 32         | LIM GND  | 0 V                       |                                                     | Limiter buffer ground                                                                                                                                                                           |

| 34         | REF INV  | High: 2.2 V<br>Low: 2.0 V | Vcc<br>39.6k<br>35<br>35<br>30.6k<br>39.6k<br>39.6k | Reference frequency<br>signal output.<br>The reference frequency<br>signal can also be made<br>by connecting this pin<br>and Pin 35 with a crystal<br>oscillator to configure an<br>oscillator. |

| 35         | REF IN   | 2.1 V                     | GND                                                 | Reference frequency<br>input and reference<br>counter input                                                                                                                                     |

| 36         | PLL GND  | 0 V                       |                                                     | PLL ground                                                                                                                                                                                      |

| 37         | FC       |                           | Vcc                                                 | Switching for the charge<br>pump output status and<br>for the signal output to<br>Pin 38                                                                                                        |

| 38         | TEST OUT | High: 2.2 V<br>Low: 2.0 V | Vcc<br>Vcc<br>GND                                   | Output of the frequency<br>division signal by the<br>counter                                                                                                                                    |

—5—

| Pin<br>No. | Symbol   | Pinvoltage                | Equivalent circuit | Description                     |

|------------|----------|---------------------------|--------------------|---------------------------------|

| 39         | LOCK DET | High: 2.2 V<br>Low: 0.1 V | Vcc                | Lock detection signal<br>output |

| 40         | PLL Vcc  | 3 V                       |                    | PLL power supply                |

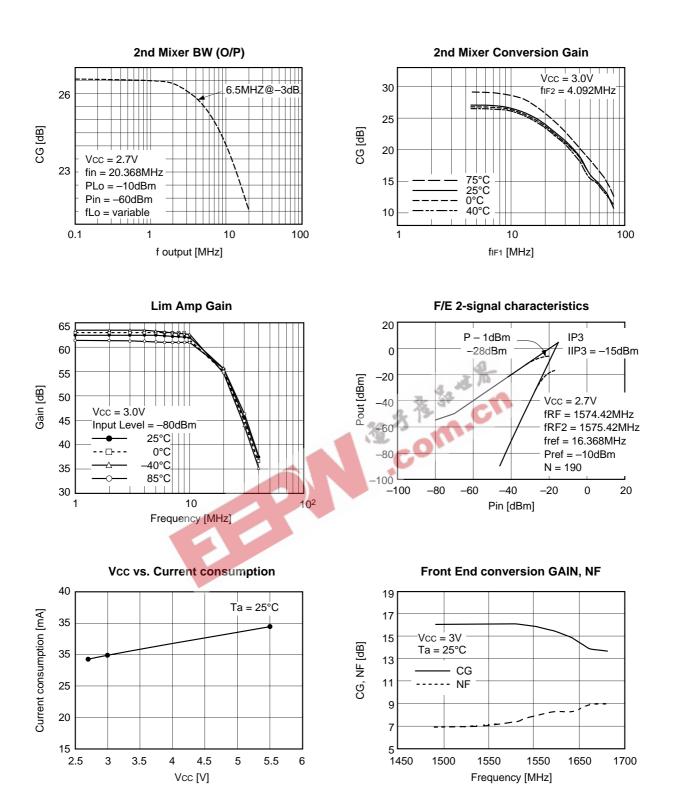

# **Electrical Characteristics**

(Vcc = 3 V, Ta = 25 °C)

| Item                       |                             | Symbol | Measurement conditions | Min.                        | Тур.  | Max.  | Unit |      |

|----------------------------|-----------------------------|--------|------------------------|-----------------------------|-------|-------|------|------|

| Currer                     | nt consumption              |        | Icc                    |                             |       | 30    | 40   | mA   |

| Frant                      |                             |        |                        | fin = 1575.42 MHz, -60 dBm  |       |       |      |      |

|                            | end conversion              |        | CGmix1                 | fout = 20.46 MHz            | 14    | 16    |      | dB   |

| gain                       |                             |        |                        | fosc = 1554.96 MHz, -10 dBm |       |       |      |      |

| 2nd m                      | ixer conversion             |        |                        | fin = 20 MHz, –60 dBm       |       |       |      |      |

| gain                       |                             |        | CGmix2                 | fref = 16  MHz, -10  dBm    | 24.5  | 26.5  |      | dB   |

| gain                       |                             |        |                        |                             |       |       |      |      |

| Limite                     | r gain                      |        | PGlim                  | fin = 4 MHz, –80 dBm        | 59    | 63    |      | dB   |

| Limite                     | r output level              |        | Volim                  | fin = 4 MHz, -30 dBm        | 0.7   | 0.75  | 0.8  | Vp-р |

| 50                         | Input High curre            | ent    | Ін                     | Pin = Vcc                   |       | 9.5   | 14   | μA   |

| FC                         | Input Low curre             | nt     | lı∟                    | PIN = GND                   | -16.5 | -11.5 |      | μA   |

|                            | SW Input High current       |        | IFCin                  | Pin = Vcc                   |       | 25    | 36   | μA   |

| INOVV                      |                             |        | IFCin                  | PIN = GND                   | -36   | -25   |      | μA   |

| Charg                      | e pump output               | Н      | Іон                    | Vcpout = Vcc/2              | -3    | -2    |      | mA   |

| curren                     | nt                          | L      | lo∟                    | Vcpout = Vcc/2              |       | 2     | 3    | mA   |

| LOCK                       | DET output                  | Н      | Vон                    | Load current = 0.1 mA       | 2     |       |      | V    |

| voltage L                  |                             | Vol    | Load current = 0.1 mA  | A P                         |       | 500   | mV   |      |

| 1st IF output resistance F |                             | Romix1 | Balanced output        | 1.4                         | 2     | 2.6   | kΩ   |      |

| 1st IF input resistance R  |                             | Rimix2 | Single input 💦 👷 🐴 🖌   | 0.84                        | 1.2   | 1.56  | kΩ   |      |

| 2nd IF                     | 2nd IF output resistance Ro |        | Romix2                 | Single output               | 0.69  | 1     | 1.3  | kΩ   |

| Limite                     | r input resistance          | Э      | Rilim                  | Single input                | 0.84  | 1.2   | 1.56 | kΩ   |

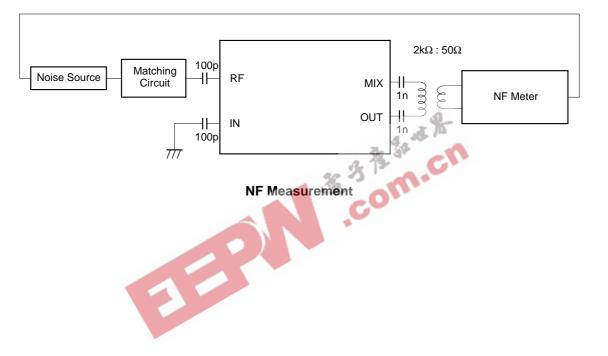

# **Design Reference Values**

(Vcc = 3 V, Ta = 25 °C)

| Item                      | Symbol | Measurement conditions | Min. | Тур. | Max. | Unit |

|---------------------------|--------|------------------------|------|------|------|------|

| Noise figure              | NF     | f = 1.58 GHz           |      | 7    |      | dB   |

|                           |        | DBS measurement        |      |      |      | uВ   |

| 1st IF output capacitance |        | Balanced output        |      | 2    |      | pF   |

| 1st IF input capacitance  |        | Single input           |      | 2    |      | pF   |

| 2nd IF output capacitance |        | Single output          |      | 2    |      | pF   |

| Limiter input capacitance |        | Single input           |      | 2    |      | pF   |

| IF amplifier band width   | BWif   | Input Level = -60 dBm  |      | 41   |      | MHz  |

#### **Electrical Characteristics Measurement Circuit**

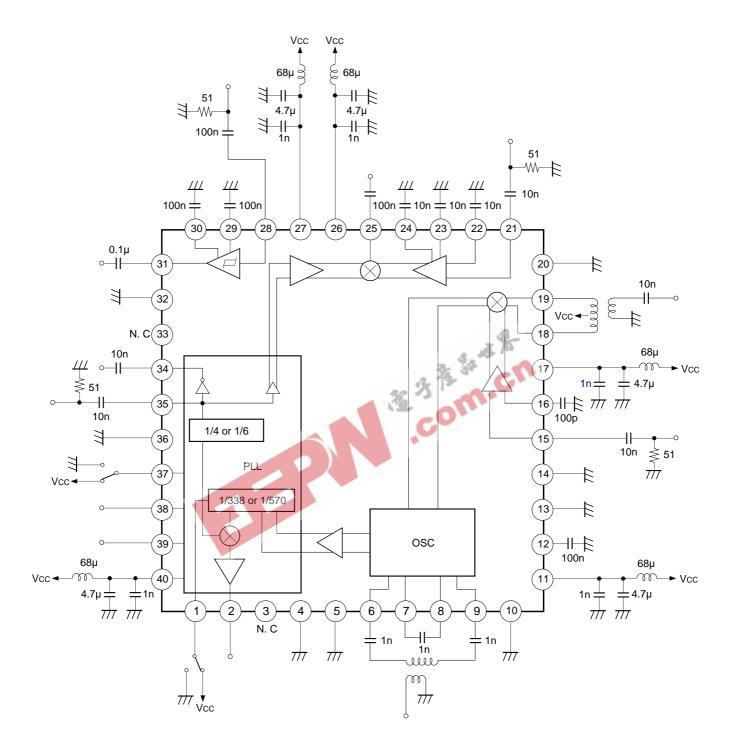

#### **Application Circuit**

Notice: Two component values are indicated, the order is depending on the output frequency. The first value is as for 'fo output' and the second value is as for '4fo output'.

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

#### **Description of Operation**

This IC down-converts the GPS (Global Positioning System) frequency of 1.57542 GHz to fo (fo: 1.023 MHz) or 4fo.

The internal configuration is divided into the analog block, consisting of the amplifier and mixer, and the digital block (including limiter), which forms the PLL.

The two-stage analog block has an external filter; it converts the frequency and amplifies the signal. The PLL frequency division ratio can be switched in the digital block in order to down-convert the output signal to fo or 4fo.

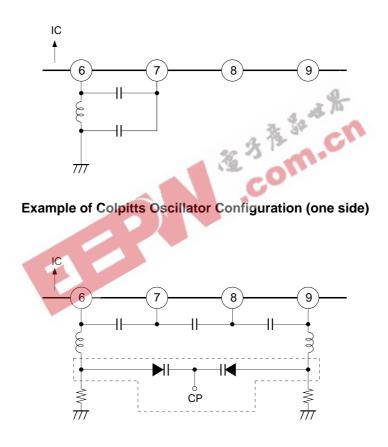

#### 1. Oscillator

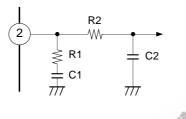

Transistor and bias circuits are incorporated in this IC. A Colpitts or Hartley oscillator can be configured by adding an external resonator. Also, the oscillator is a paired circuit so as to enable balanced output.

**Example of Balanced Configuration**

A varactor (variable capacitance) diode, as shown by the dotted line, is added to this IC to configure a VCO, and the resonant frequency is varied depending on the control voltage of Pin 2 (charge pump output) to CP.

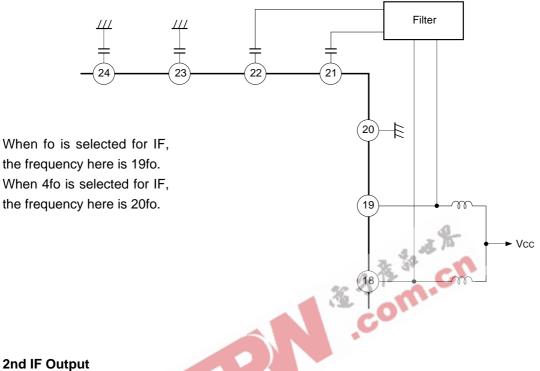

#### 2. 1st IF Output

Pins 18 and 19 are open collector outputs.

The bias signal is supplied by the coils, and the output is connected to the 2nd mixer input Pins 21 and 22 via the filter. Use a capacitor to cut direct current. Decoupling for Pins 23 and 24 should be done as close to the IC as possible.

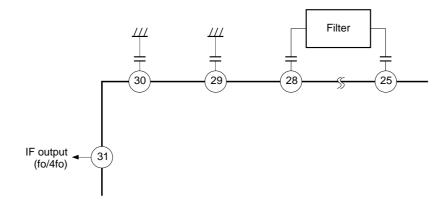

#### 3. 2nd IF Output

Pin 25 is emitter follower output.

After passing via the filter, the direct current is cut, and input is to the limiter input Pin 28. fo or 4fo is output from the limiter output Pin 31. (Pin 31 is emitter follower output.)

Decoupling for Pins 29 and 30 must be done as close to the IC as possible.

#### 4. NSW (Pin 1)

The internal counter frequency division value is determined by connecting this pin to Vcc or GND when selecting fo or 4 fo for IF, as shown in the table below.

| IF                          | fo                     | 4fo                    |

|-----------------------------|------------------------|------------------------|

| NSW                         | Vcc                    | GND                    |

| VCO counter                 | 338 frequency division | 570 frequency division |

| Reference frequency counter | 4 frequency division   | 6 frequency division   |

#### 5. CPOUT (Pin 2)

A current output charge pump configures an external loop filter for VCO control voltage.

#### 6. FC (Pin 37)

This pin performs two functions when connected to Vcc or GND; CPOUT (Pin 2) output status switching and TEST OUT (Pin 38) selector switch. (See Table 1)

#### 7. TEST OUT (Pin 38)

This is the monitor pin for the internal counter frequency division output. The frequency division signals for VCO counter and reference frequency counter can be switched depending on FC status. (See Table 1)

|         | FC to | o Vcc   | FC to | GND     |

|---------|-------|---------|-------|---------|

|         | CPOUT | TESTOUT | CPOUT | TESTOUT |

| fr > fm | L     | fr      | Н     | fm      |

| fr = fm | Z     | fr      | Z     | fm      |

| fr < fm | Н     | fr      | L     | fm      |

#### Table 1

| Z: High-impedance | fr: Reference frequency counter output frequency |

|-------------------|--------------------------------------------------|

| H: High           | fm: VCO counter output frequency                 |

|                   |                                                  |

#### L: Low

#### 8. LOCK DET (Pin 39)

This pin detects PLL lock status. When PLL is not locked, the pin voltage is not set; when locked, it is 2V DC.

Note) • The voltages mentioned are for supply voltage of 3 V, load current of 100  $\mu$ A.

• A thin pulse will be observed on monitoring this pin with an oscilloscope, but this is normal.

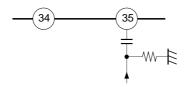

#### 9. REF IN (Pin 35) and REF INV (Pin 34)

The signal input from the external oscillator to REF IN can be used as the reference signal. Further, a reference signal can be generated by connecting a crystal oscillator between Pin 35 and Pin 34.

Example of reference signal generated by the external oscillator

As shown in the figure below, input to RFIN via the capacitor to use the external oscillator signal as

the reference signal.

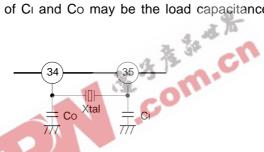

(2) Example of reference signal generated by the crystal oscillator

As shown below, connect the crystal oscillator between Pin 34 and Pin 35, making sure that the oscillation stability, etc. is satisfactory.

Further, the capacitance ratio of  $C_1$  and  $C_0$  should be 1 to 2 : 1 ( $C_1$  :  $C_0$ ). Select the capacitance values so that the serial capacitance of  $C_1$  and  $C_0$  may be the load capacitance specified by the crystal oscillator.

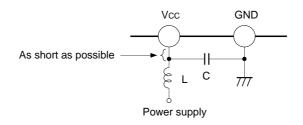

#### 10. Power supply pin and OSC DEC (Pin 12) decoupling

This IC has five power supply and ground systems, due to the following reasons:

- 1) It handles high frequency signals.

- 2) The total gain is high. (100 dB or more)

- 3) It combines analog and digital blocks.

Therefore, it is absolutely necessary to decouple these power supply lines as close to the IC as possible. When necessary, insert the inductor (about  $6.8 \mu$ ) in series in the power supply line.

OSC DEC is the internal reference voltage decoupling pin, and must be grounded with a capacitor (about 100 nF).

#### Notes on Operation

Make sure to take measures for static electric damage because the high frequency signals are handled so that protection elements are omitted from this IC.

#### Package Outline Unit : mm