# **CXA3106AQ**

# PLL IC for LCD Monitor/Projector

# **Description**

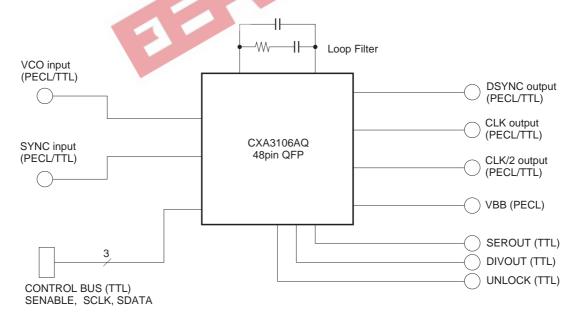

The CXA3106AQ is a PLL IC for LCD monitors/ projectors with built-in phase detector, charge pump, VCO and counter.

The various internal settings are performed by serial data via a 3-line bus.

Applicable LCD monitor/projector resolution are NTSC, PAL, VGA, SVGA, XGA, and SXGA etc.

#### **Features**

Supply voltage: 5V ± 10% single power supply

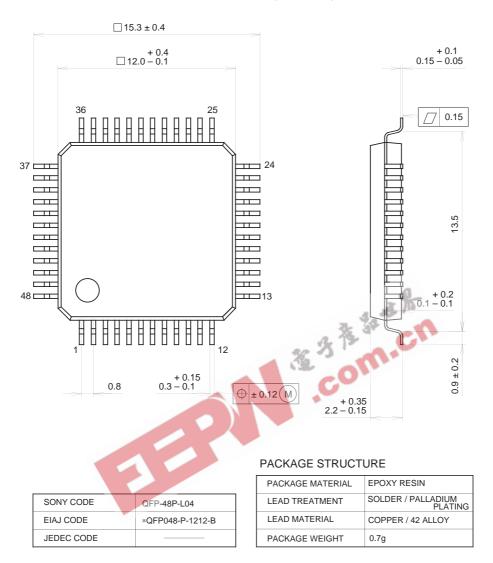

• Package: 48-pin QFP

• Power consumption: 350mW

• Sync input frequency: 10 to 100kHz

• Clock output signal frequency: 10 to 160MHz

Clock delay: 1/16 to 20/16 CLK

Sync delay: 1/16 to 20/16 CLK

• I/O level: TTL, PECL (complementary)

Low clock jitter1/2 clock output

#### **Functions**

- Phase detector enable

- UNLOCK output

- Output TTL disable function

- Power save function (2 steps)

# **Applications**

- CRT displays

- LCD projectors

- LCD monitors

- Multi-media

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

# **Absolute Maximum Ratings** (Ta = 25°C)

| <ul> <li>Supply voltage</li> </ul>      | IOVcc, DVcc, TTLVcc, PECLVcc, PLLVcc,   |                            |    |

|-----------------------------------------|-----------------------------------------|----------------------------|----|

|                                         | VCOVcc, IRVcc,                          | -0.5 to +7.0               | V  |

|                                         | IOGND, DGND, TTLGND, VCOHGND, PLLGND,   |                            |    |

|                                         | VCOGND, IRGND                           | -0.5 to +0.5               | V  |

| <ul> <li>Input voltage</li> </ul>       | VCOH, VCOL, SYNCH, SYNCL, VCO, HOLD,    |                            |    |

|                                         | SYNC, SENABLE, SCLK, SDATA, TLOAD, CS   | IOGND - 0.5 to IOVcc + 0.5 | V  |

|                                         | RC2                                     | IRGND - 0.5 to IRVcc + 0.5 | V  |

| <ul> <li>Output current</li> </ul>      | SEROUT, DIVOUT, UNLOCK, CLK/2N, CLK/2,  |                            |    |

|                                         | CLKN, CLK, DSYNC, CLK/2L, CLK/2H, CLKL, |                            |    |

|                                         | CLKH, DSYNCH, DSYNCL, VBB               | -30 to +30                 | mΑ |

|                                         | IREF, RC1                               | −2 to +2                   | mA |

| Storage temperature                     | e Tstg                                  | -65 to +150                | °C |

| <ul> <li>Operating ambient t</li> </ul> | emperature                              |                            |    |

|                                         | Та                                      | -25 to +75                 | °C |

| <ul> <li>Allowable power dis</li> </ul> | sipation                                |                            |    |

|                                         | Po                                      | 750                        | mW |

|                                         | A. A.                                   | A 10                       |    |

|                                         | ***                                     | -10                        |    |

| Recommended Ope                         | rating Conditions                       | 0.0                        |    |

|                                         | rating Conditions                       | Typ. Max.                  |    |

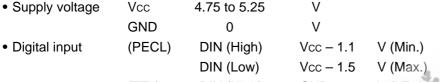

# **Recommended Operating Conditions**

|                                    |                               | Min.        | Тур. | Max.        |    |

|------------------------------------|-------------------------------|-------------|------|-------------|----|

| <ul> <li>Supply voltage</li> </ul> | IOVcc, DVcc, TTLVcc, PECLVcc, | C           |      |             |    |

|                                    | PLLVcc, VCOVcc, IRVcc         | 4.75        | 5.00 | 5.25        | V  |

|                                    | IOGND, DGND, TTLGND, VCOHG    | ND,         |      |             |    |

|                                    | PLLGND, VCOGND, IRGND         | -0.05       | 0    | 0.05        | V  |

| <ul> <li>Digital input</li> </ul>  | DIN (PECL) *1 H level         | IOVcc - 1.1 |      |             |    |

|                                    | DIN (PECL) *1 L level         |             |      | IOVcc - 1.5 | V  |

|                                    | DIN (TTL) *2 H level          | 2.0         |      |             | V  |

|                                    | DIN (TTL) *2 L level          |             |      | 0.8         | V  |

| • SYNC, SYNCH, SY                  | NCL input jitter              |             |      | 1.0         | ns |

| Operating temperate                | ure                           |             |      |             |    |

|                                    | Та                            | -20         |      | +75         | °C |

<sup>\*1</sup> VCOH, VCOL, SYNCH, SYNCL

<sup>\*2</sup> VCO, HOLD, SYNC, SENABLE, SCLK, SDATA, TLOAD, CS

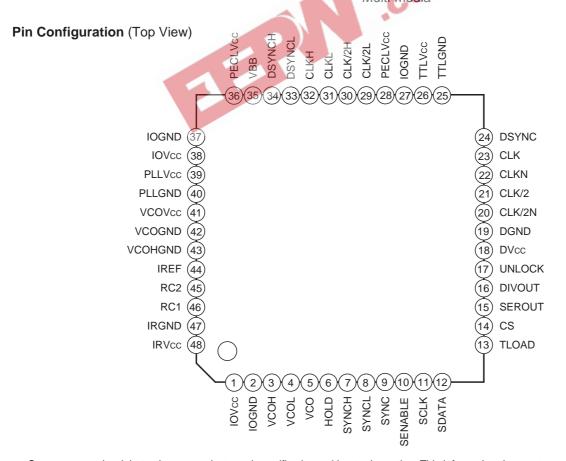

| Pin No.  | Symbol      | Description                                                                                                                             | Reference voltage level |

|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 1        | IOVcc       | Digital power supply                                                                                                                    | 5V                      |

| 2        | IOGND       | Digital GND                                                                                                                             | 0V                      |

| 3        | VCOH        | External VCO input                                                                                                                      | PECL                    |

| 4        | VCOL        | External inverted VCO input                                                                                                             | PECL                    |

| 5        | VCO         | External VCO input                                                                                                                      | TTL                     |

| 6        | HOLD        | Phase detector disable signal input                                                                                                     | TTL                     |

| 7        | SYNCH       | Sync input                                                                                                                              | PECL                    |

| 8        | SYNCL       | Inverted sync input                                                                                                                     | PECL                    |

| 9        | SYNC        | Sync input                                                                                                                              | TTL                     |

| 10       | SENABLE     | Control signal (enable)                                                                                                                 | TTL                     |

| 11       | SCLK        | Control signal (clock)                                                                                                                  | TTL                     |

| 12       | SDATA       | Control signal (data)                                                                                                                   | TTL                     |

| 13       | TLOAD       | Programmable counter test input                                                                                                         | TTL                     |

| 14       | CS          | Chip select                                                                                                                             | TTL                     |

| 15       | SEROUT      | Register read output                                                                                                                    | TTL                     |

| 16       | DIVOUT      | Programmable counter test output                                                                                                        | TTL                     |

| 17       | UNLOCK      | Unlock signal output                                                                                                                    | TTL                     |

| 18       | DVcc        | Digital power supply                                                                                                                    | 5V                      |

| 19       | DGND        | Digital GND                                                                                                                             | 0V                      |

| 20       | CLK/2N      | Digital power supply Digital GND Inverted 1/2 clock output 1/2 clock output Inverted clock output Clock output Delay sync signal output | THE                     |

| 21       | CLK/2       | 1/2 clock output                                                                                                                        | 111                     |

| 22       | CLKN        | Inverted clock output                                                                                                                   | TTI                     |

| 23       | CLK         | Clock output                                                                                                                            | TTI                     |

| 24       | DSYNC       | Delay sync signal output                                                                                                                | TTL                     |

| 25       | TTLGND      | TTL output GND                                                                                                                          | 0V                      |

| 26       | TTLVcc      | TTL output power supply                                                                                                                 | 5V                      |

| 27       | IOGND       | Digital GND                                                                                                                             | 0V                      |

| 28       | PECLVcc     | PECL output power supply                                                                                                                | 5V                      |

| 29       | CLK/2L      | Inverted 1/2 clock output                                                                                                               | PECL                    |

| 30       | CLK/2H      | 1/2 clock output                                                                                                                        | PECL                    |

| 31       | CLKL        | Inverted clock output                                                                                                                   | PECL                    |

| 32       | CLKH        | Clock output                                                                                                                            | PECL                    |

| 33       | DSYNCL      | Delay sync signal output                                                                                                                | PECL                    |

| 34       | DSYNCH      | Inverted delay sync signal output                                                                                                       | PECL                    |

| 35       | VBB         | PECL reference voltage                                                                                                                  | PECLVcc – 1.3V          |

| 36       | PECLVcc     | PECL output power supply                                                                                                                | 5V                      |

| 37       | IOGND       | Digital GND                                                                                                                             | 0V                      |

| 38       | IOVcc       | Digital power supply                                                                                                                    | 5V                      |

| 39       | PLLVcc      | PLL circuit analog power supply                                                                                                         | 5V                      |

| 40       | PLLGND      | PLL circuit analog GND                                                                                                                  | 0V                      |

| 41       | VCOVcc      | VCO circuit analog gower supply                                                                                                         | 5V                      |

| 42       | VCOGND      |                                                                                                                                         | 0V                      |

| 42       | VCOGND      | VCO circuit analog GND VCO SUB analog GND                                                                                               | 0V<br>0V                |

|          |             | _                                                                                                                                       |                         |

| 44<br>45 | IREF<br>BC2 | Charge pump current preparation                                                                                                         | 1.3V                    |

| 45<br>46 | RC2         | External pin for LPF                                                                                                                    | 1.7 to 4.4V             |

| 46<br>47 | RC1         | External pin for LPF                                                                                                                    | 2.1V                    |

| 47       | IRGND       | IREF analog GND                                                                                                                         | 0V                      |

| 48       | IRVcc       | IREF analog power supply                                                                                                                | 5V                      |

# Pin Description and I/O Pin Equivalent Circuit

| Pin<br>No. | Symbol  | I/O | Reference voltage level | Equivalent circuit | Description                                                                                                                                 |

|------------|---------|-----|-------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | IOVcc   | _   | 5V                      |                    | Digital power supply. Ground this pin to the ground pattern with a 0.1µF ceramic chip capacitor as close to the pin as possible.            |

| 2          | IOGND   | _   | 0V                      |                    | Digital GND.                                                                                                                                |

| 18         | DVcc    | _   | 5V                      |                    | Digital power supply.                                                                                                                       |

| 19         | DGND    | _   | 0V                      |                    | Digital GND.                                                                                                                                |

| 25         | TTLGND  | _   | 0V                      |                    | TTL output GND.                                                                                                                             |

| 26         | TTLVcc  | _   | 5V                      |                    | TTL output power supply. Ground this pin to the ground pattern with a 0.1µF ceramic chip capacitor as close to the pin as possible.         |

| 27         | IOGND   | _   | 0V                      |                    | Digital GND.                                                                                                                                |

| 28         | PECLVcc | _   | 5V                      | 36                 | PECL output power supply. Ground this pin to the ground pattern with a 0.1µF ceramic chip capacitor as close to the pin as possible.        |

| 36         | PECLVcc | _   | 5V                      | i co               | PECL output power supply. Ground this pin to the ground pattern with a 0.1µF ceramic chip capacitor as close to the pin as possible.        |

| 37         | IOGND   | _   | 0V                      |                    | Digital GND.                                                                                                                                |

| 38         | IOVcc   | _   | 5V                      |                    | Digital power supply. Ground this pin to the ground pattern with a 0.1µF ceramic chip capacitor as close to the pin as possible.            |

| 39         | PLLVcc  | _   | 5V                      |                    | PLL circuit analog power supply. Ground this pin to the ground pattern with a 0.1µF ceramic chip capacitor as close to the pin as possible. |

| 40         | PLLGND  | _   | 0V                      |                    | PLL circuit analog GND.                                                                                                                     |

| 41         | VCOVcc  | _   | 5V                      |                    | VCO circuit analog power supply. Ground this pin to the ground pattern with a 0.1µF ceramic chip capacitor as close to the pin as possible. |

| 42         | VCOGND  | _   | 0V                      |                    | VCO circuit analog GND.                                                                                                                     |

| 43         | VCOHGND | _   | 0V                      |                    | VCO SUB analog GND.                                                                                                                         |

| 47         | IRGND   | _   | 0V                      |                    | IREF analog GND.                                                                                                                            |

| 48         | IRVcc   | _   | 5V                      |                    | IREF analog power supply. Ground this pin to the ground pattern with a 0.1µF ceramic chip capacitor as close to the pin as possible.        |

| Pin<br>No. | Symbol | I/O | Reference voltage level | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description                                                                                                                                                                                                                                                     |

|------------|--------|-----|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3          | VCOH   | I   | PECL                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | External VCO input. Programmable counter test input (switchable by a control register). When using the VCO PECL input, open the Pin 5 VCO TTL input.                                                                                                            |

| 4          | VCOL   | I   | PECL                    | IOVcc r s s r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | External inverted VCO input. When open, this pin goes to the PECL threshold voltage (IOVcc – 1.3V). Only the pin 3 VCOH input with VCOL input open can be also operated but complementary input is recommended in order to realize stable high-speed operation. |

| 7          | SYNCH  | I   | PECL                    | (4)(8)<br>  (4) | Sync input. When using the SYNCH PECL input, open the Pin 9 SYNC TTL input. The sync signal can be switched between positive/negative polarity by an internal register.                                                                                         |

| 8          | SYNCL  | ı   | PECL                    | IOGND TO THE PARTY OF THE PARTY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Inverted sync input. When open, this pin goes to the PECL threshold voltage (IOVcc – 1.3V). Only the Pin 7 SYNCH input with SYNCL input open can be also operated but complementary input is recommended in order to realize stable high-speed operation.       |

| Pin<br>No. | Symbol  | I/O | Reference voltage level | Equivalent circuit         | Description                                                                                                                                                                                                                                                                                             |

|------------|---------|-----|-------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5          | vco     | I   | TTL                     |                            | External VCO input. Programmable counter test input (controlled by a control register). When using the VCO TTL input, open the Pin 3 VCOH and Pin 4 VCOL PECL inputs.                                                                                                                                   |

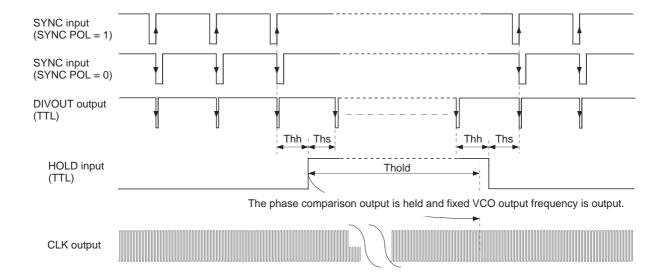

| 6          | HOLD    | I   | TTL                     |                            | Phase detector disable signal. Active high. When this pin is high, the phase detector output is held. This pin goes to high level when open. (See the HOLD Timing Chart.)                                                                                                                               |

| 9          | SYNC    | I   | TTL                     | IOVcc ↓ ↓ ↓ ≤ r/2          | Sync input. When using the SYNC TTL input, open the Pin 7 SYNCH and Pin 8 SYNCL PECL inputs. The sync signal can be switched between positive/negative polarity by a control register.                                                                                                                  |

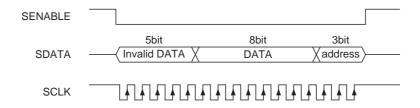

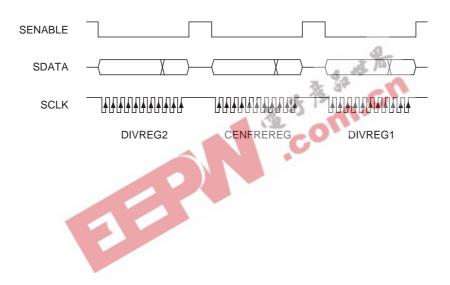

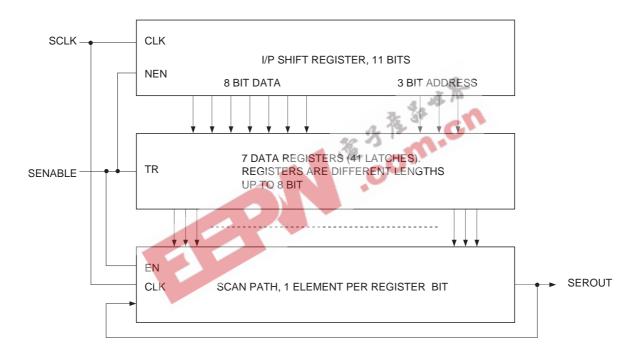

| 10         | SENABLE | I   | TTL                     | 5 10<br>6 11<br>9 12<br>13 | Control signal (enable) for setting the internal registers. When SENABLE is low, registers can be written; when high, registers can be read. (See the Control Register Table and Control Timing Chart.)                                                                                                 |

| 11         | SCLK    | I   | TTL                     | IOGND -                    | Control signal (clock) for setting the internal registers. When SENABLE is low, SDATA is loaded to the registers at the rising edge of SCLK. When SENABLE is high, the register contents are output from SEROUT at the falling edge of SCLK. (See the Control Register Table and Control Timing Chart.) |

| 12         | SDATA   | I   | TTL                     |                            | Control signal (data) for setting the internal registers. (See the Control Register Table and Control Timing Chart.)                                                                                                                                                                                    |

| 13         | TLOAD   | I   | TTL                     |                            | Programmable counter test input. This pin is normally open status and high. Register contents can be loaded immediately to Programmable counter by setting TLOAD low during the programmable counter test mode.                                                                                         |

| Pin<br>No. | Symbol | I/O | Reference voltage level | Equivalent circuit                     | Description                                                                                                                                                                                                                            |

|------------|--------|-----|-------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14         | cs     | I   | TTL                     | IOVcc IOGND                            | Chip select. When low, all circuits including the register circuit are set to the power save mode. When high, all circuits are set to operating mode.                                                                                  |

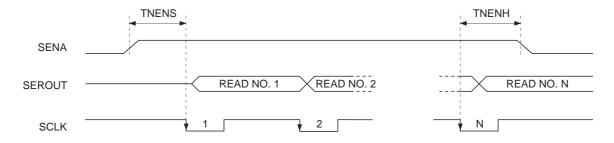

| 15         | SEROUT | 0   | TTL                     |                                        | Register read output. When SENABLE is high, the register contents are output from SEROUT at the falling edge of SCLK. (See the Control Register Timing Chart.) TTL output can be turned ON/OFF (high impedance) by a control register. |

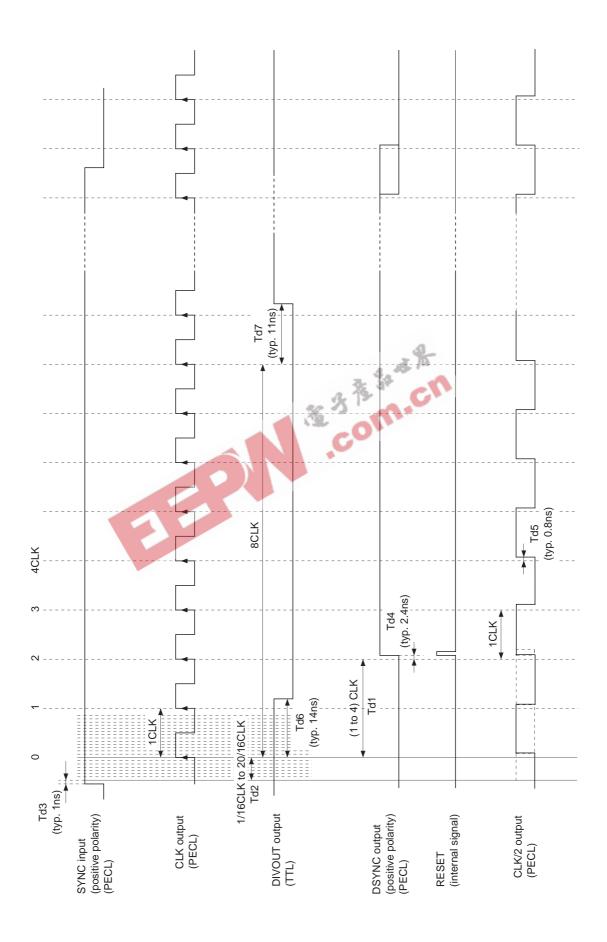

| 16         | DIVOUT | 0   | TTL                     | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1  | Programmable counter test output. (See the I/O Timing Chart.) TTL output can be turned ON/OFF (high impedance) by a control register.                                                                                                  |

| 20         | CLK/2N | 0   | TTL                     | IOVcc TTLVcc 15(22)                    | Inverted 1/2 clock output. (See the I/O Timing Chart.) TTL output can be turned ON/OFF (high impedance) by a control register.                                                                                                         |

| 21         | CLK/2  | 0   | TTL                     | (16)(23)<br>(20)(24)<br>(21)<br>TTLGND | 1/2 clock output. (See the I/O Timing Chart.) TTL output can be turned ON/OFF (high impedance) by a control register.                                                                                                                  |

| 22         | CLKN   | 0   | TTL                     | IOGNE                                  | Inverted clock output. (See the I/O Timing Chart.) TTL output can be turned ON/OFF (high impedance) by a control register.                                                                                                             |

| 23         | CLK    | 0   | TTL                     |                                        | Clock output. (See the I/O Timing Chart.) TTL output can be turned ON/OFF (high impedance) by a control register.                                                                                                                      |

| 24         | DSYNC  | 0   | TTL                     |                                        | Delay sync signal output. (See the I/O Timing Chart.) TTL output can be turned ON/OFF (high impedance) and switched between positive/negative polarity by a control register.                                                          |

| Pin<br>No. | Symbol | I/O | Reference voltage level | Equivalent circuit       | Description                                                                                                                                                                                                                                                                                                                               |

|------------|--------|-----|-------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

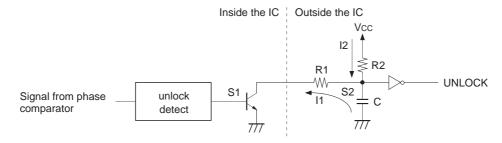

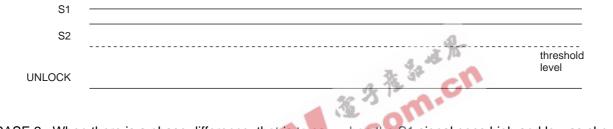

| 17         | UNLOCK | 0   | TTL                     | TTLVcc 17) IOGND TTLGND  | Unlock signal output. This pin is an open collector output, and pulls in the current when a phase difference occurs. The UNLOCK sensitivity can be adjusted by connecting a capacitor and resistors to this output as appropriate. (See the UNLOCK Timing Chart.) TTL output can be turned ON/OFF (high impedance) by a control register. |

| 29         | CLK/2L | 0   | PECL                    |                          | Inverted 1/2 clock output. (See the I/O Timing Chart.) This pin requires an external pull-down resistor. When not used, connect to PECLVcc without connecting a pull-down resistor.                                                                                                                                                       |

| 30         | CLK/2H | 0   | PECL                    | 道方等                      | 1/2 clock output. (See the I/O Timing Chart.) This pin requires an external pull-down resistor. When not used, connect to PECLVcc without connecting a pull-down resistor.                                                                                                                                                                |

| 31         | CLKL   | 0   | PECL                    | PECLVcc PECLVcc 30 32 34 | Inverted clock output. (See the I/O Timing Chart.) This pin requires an external pulldown resistor. When not used, connect to PECLVcc without connecting a pull-down resistor.                                                                                                                                                            |

| 32         | CLKH   | 0   | PECL                    | 293133<br>IOGND          | Clock output. (See the I/O Timing Chart.) This pin requires an external pull-down resistor. When not used, connect to PECLVcc without connecting a pull-down resistor.                                                                                                                                                                    |

| 33         | DSYNCL | 0   | PECL                    |                          | Delay sync signal output. (See the I/O Timing Chart.) This pin requires an external pulldown resistor. When not used, connect to PECLVcc without connecting a pull-down resistor.                                                                                                                                                         |

| 34         | DSYNCH | 0   | PECL                    |                          | Inverted delay sync signal output. (See the I/O Timing Chart.) This pin requires an external pulldown resistor. When not used, connect to PECLVcc without connecting a pull-down resistor.                                                                                                                                                |

| Pin<br>No. | Symbol | I/O | Reference voltage level | Equivalent circuit     | Description                                                                                                                                                                                                                                                      |

|------------|--------|-----|-------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35         | VBB    | 0   | PECLVcc<br>-1.3V        | PECLVcc 35             | PECL reference voltage. When used, ground this pin to the ground pattern with a 0.1µF ceramic chip capacitor as close to the pin as possible.                                                                                                                    |

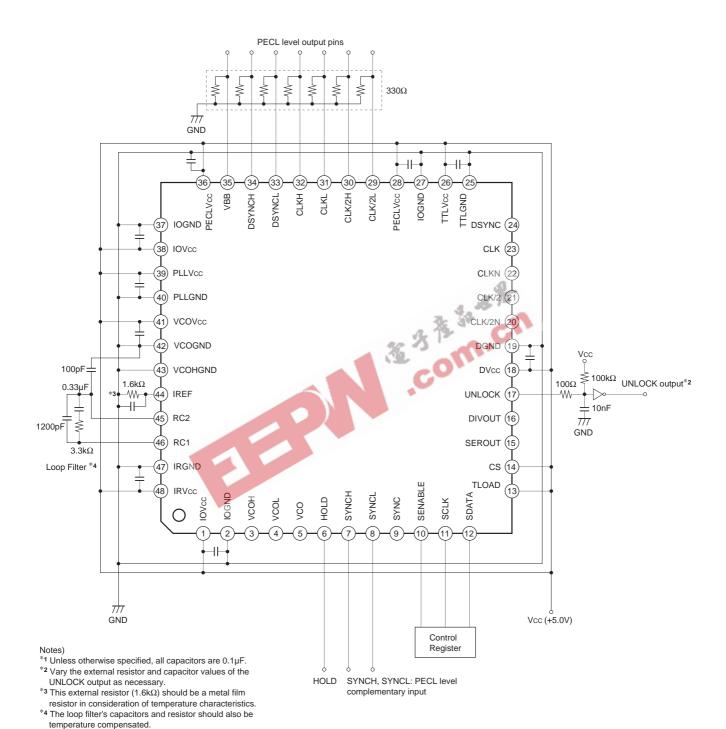

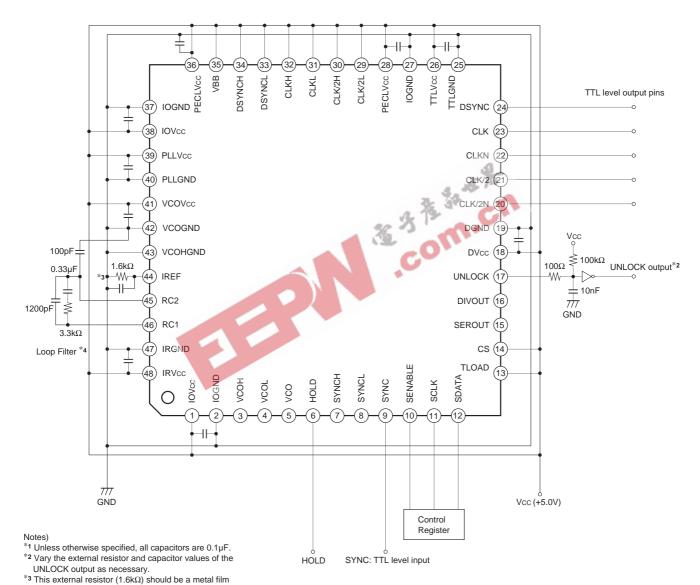

| 44         | IREF   | 0   | 1.3V                    | IRVcc IRGND IOGND      | Charge pump current preparation. Connect to GND via an external resistor (1.6k $\Omega$ ). Ground this pin to the ground pattern with a 0.1 $\mu$ F ceramic chip capacitor as close to the pin as possible.                                                      |

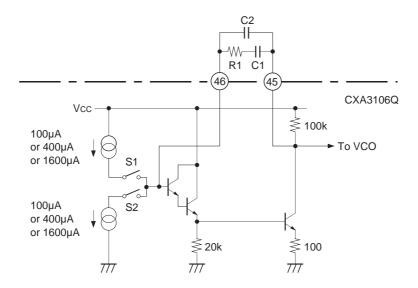

| 45         | RC2    | 0   | 1.7<br>to<br>4.4V       | IRVcc VCOVcc VCOVcc 46 | External pin for LPF. See the Recommended Operating Circuit for the external circuits. Note that external resistors and capacitors should be metal film resistors and temperature compensation capacitors which are relatively unaffected by temperature change. |

| 46         | RC1    | 0   | 2.1V                    | IRGND 100 VCOGND IOGND | External pin for LPF. See the Recommended Operating Circuit for the external circuits.                                                                                                                                                                           |

**Control Register Table**

|                               |                     |                |                               |                          | DATA                   | TA                     | -                      |                        |                        |              | ADDRESS |              |

|-------------------------------|---------------------|----------------|-------------------------------|--------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|--------------|---------|--------------|

| Register Name MSB MSB         | DATA7<br>MSB        |                | DAT6                          | DATA5                    | DATA4                  | DATA3                  | DATA2                  | DATA1                  | DATA0                  | ADDR2<br>MSB | ADDR1   | ADDR0<br>LSB |

| register read no              | 1                   |                | 2                             | 3                        | 4                      | 2                      | 9                      | 2                      | 8                      |              |         |              |

| VCO<br>DIVREG1 DIV<br>Bit 7   | VCO<br>DIV<br>Bit 7 |                | VCO<br>DIV<br>Bit 6           | VCO<br>DIV<br>Bit 5      | VCO<br>DIV<br>Bit 4    | VCO<br>DIV<br>Bit 3    | VCO<br>DIV<br>Bit 2    | VCO<br>DIV<br>Bit 1    | VCO<br>DIV<br>Bit 0    | 0            | 0       | -            |

| register read no              |                     |                |                               |                          |                        | 0                      | 10                     | 11                     | 12                     | -            |         |              |

| DIVREG2                       |                     |                |                               |                          |                        | VCO<br>DIV<br>Bit 11   | VCO<br>DIV<br>Bit 10   | VCO<br>DIV<br>Bit 9    | VCO<br>DIV<br>Bit 8    | 0            | -       | 0            |

| register read no              |                     |                | 13                            | 14                       | 15                     | 16                     | 17                     | 18                     | 19                     |              |         |              |

| CENFREREG DIV                 | VIQ                 |                | DIV 1, 2, 4 DIV 1<br>Bit 1 Bi | DIV 1, 2, 4<br>Bit 0     | N/A*1                  | N/A*1                  | N/A*1                  | N/A*1                  | N/A*1                  | 0            | _       | _            |

| register read no              |                     |                | 20                            | 21                       | 22                     | 23                     | 24                     | 25                     | 26                     |              |         |              |

| DELAYREG DE B                 | CO/<br>DE           | CO/<br>DE<br>B | COARSE<br>DELAY<br>Bit 1      | COARSE<br>DELAY<br>Bit 0 | FINE<br>DELAY<br>Bit 4 | FINE<br>DELAY<br>Bit 3 | FINE<br>DELAY<br>Bit 2 | FINE<br>DELAY<br>Bit 1 | FINE<br>DELAY<br>Bit 0 | ~            | 0       | 0            |

| register read no              |                     |                |                               |                          |                        | 0                      | 27                     | 28                     | 29                     |              |         |              |

| CPREG                         |                     |                |                               |                          |                        | W.                     | PD                     | C.Pump<br>Bit 1        | C.Pump<br>Bit 0        | 1            | 0       | 1            |

| register read no 30           | 30                  |                | 31                            | 32                       | 33                     | 34                     | 35                     | 36                     | 37                     |              |         |              |

| TTLPOLREG UNLOCK DS Enable EI |                     | DS<br>EI       | DSYNC<br>Enable               | NCLK/2<br>Enable         | CLK/2<br>Enable        | NCLK<br>Enable         | CLK<br>Enable          | DSYNC<br>POL           | SYNC                   | 1            | 1       | 0            |

| register read no              |                     |                |                               |                          |                        | 38                     | 39                     | 40                     | 41                     |              |         |              |

| TESTPOWREG                    |                     |                |                               |                          |                        | DIVOUT<br>Enable       | Read out<br>power      | Synth<br>power         | VCO<br>By-pass*2       | 1            | 1       | 1            |

|                               |                     |                |                               |                          |                        |                        |                        |                        |                        |              |         |              |

<sup>\*1</sup> Register read no. 15 to 19 are N/A. \*2 VCO By-pass at register read no. 41 is a MUX control bit in Block Diagram.

# **Electrical Characteristics**

(Ta = 25°C, Vcc = 5V, GND = 0V)

| Item                                     | Symbol      | Conditions              | Min.            | Тур.            | Max.            | Unit |

|------------------------------------------|-------------|-------------------------|-----------------|-----------------|-----------------|------|

| Current consumption (exclu               | ding output | current)                |                 |                 |                 |      |

| Current consumption 1                    | Icc1        | CS = H, Synth Power = 1 | 40              | 70              | 105             | mA   |

| Current consumption 2                    | Icc2        | CS = H, Synth Power = 0 | 5               | 19              | 38              | mA   |

| Current consumption 3                    | Icc3        | CS = L                  | 3               | 14              | 24              | mA   |

| Digital input                            |             |                         |                 |                 |                 |      |

| Digital high level input voltage (PECL)  | ViH1        |                         | IOVcc<br>-1.15  |                 |                 | V    |

| Digital low level input voltage (PECL)   | VıL1        |                         |                 |                 | IOVcc<br>-1.5   | V    |

| VCOL, SYNCL input open voltage (PECL)    | Vio         |                         |                 | IOVcc<br>-1.3   |                 | V    |

| Digital high level input current (PECL)  | IIH1        | VIH = IOVcc - 0.8V      | -100            |                 | 100             | μΑ   |

| Digital low level input current (PECL)   | Iı∟1        | VIL = IOVcc - 1.6V      | -200            | 2               | 0               | μA   |

| Digital high level input voltage (TTL)   | Vıн2        | 4                       | 2.0             | cn              |                 | V    |

| Digital low level input voltage (TTL)    | VıL2        | 3                       | ow.             |                 | 0.8             | V    |

| Digital high level input current (TTL)   | Ін2         | VIH = 2.7V              | -200            |                 | -20             | μA   |

| Digital low level input current (TTL)    | lıL2        | VIL = 0.5V              | -500            |                 | -100            | μA   |

| HOLD characteristics                     |             |                         |                 | •               |                 |      |

| RC1 input pin leak current               | lleak       |                         |                 |                 | 1.0             | nA   |

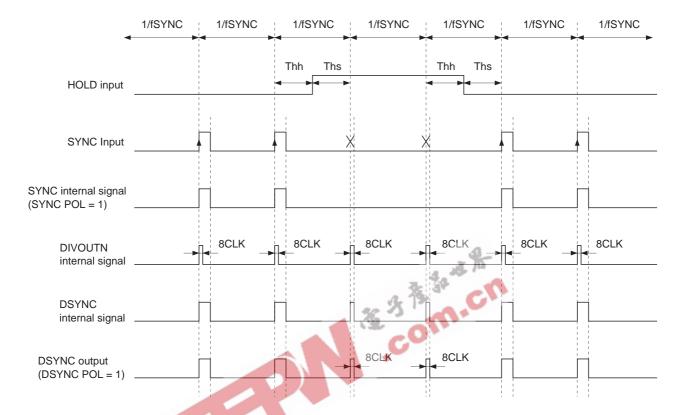

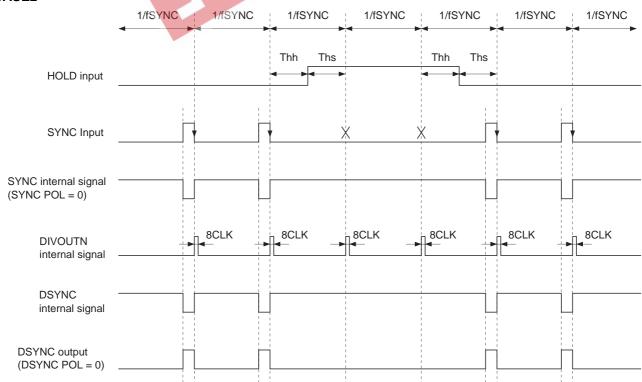

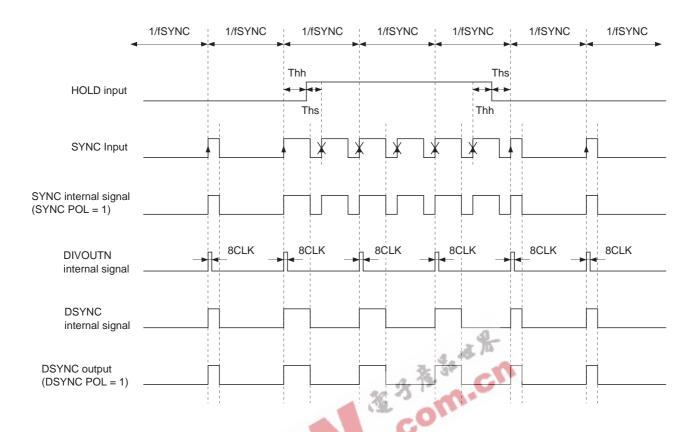

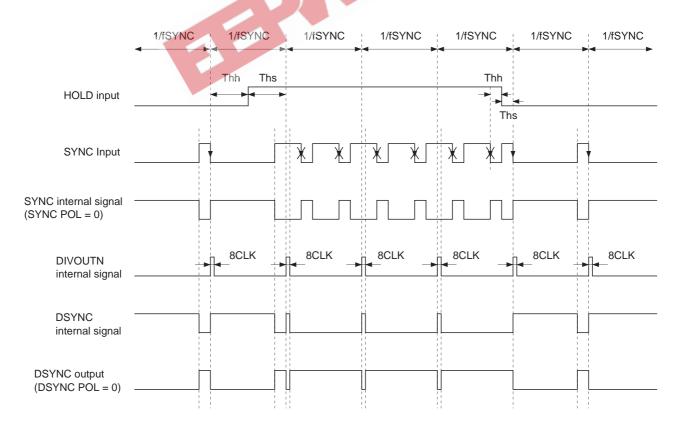

| HOLD signal set-up time                  | Ths         |                         | 20              |                 |                 | ns   |

| HOLD signal hold time                    | Thh         |                         | 20              |                 |                 | ns   |

| Digital output                           |             |                         |                 |                 |                 |      |

| Digital high level output voltage (PECL) | Vон1        | RL = 330Ω               | PECLVcc<br>-1.1 |                 |                 | V    |

| Digital low level output voltage (PECL)  | Vol1        | RL = 330Ω               |                 |                 | PECLVcc<br>-1.6 | V    |

| PECL output reference voltage            | VBB         | RL = 330Ω               |                 | PECLVcc<br>-1.3 |                 | V    |

| Digital high level output voltage (TTL)  | Vон2        | CL = 10pF               | 2.7             |                 |                 | V    |

| Digital low level output voltage (TTL)   | Vol2        | CL = 10pF               |                 |                 | 0.5             | V    |

| Item                                                       | Symbol  | Conditions                              | Min. | Тур. | Max.  | Unit    |

|------------------------------------------------------------|---------|-----------------------------------------|------|------|-------|---------|

| UNLOCK output                                              |         |                                         |      |      |       |         |

| UNLOCK output current                                      | lunlock |                                         | -30  |      |       | mA      |

| SYNC input                                                 |         |                                         |      |      |       | •       |

| SYNC input frequency range                                 | Fin     |                                         | 10   |      | 100   | kHz     |

| DSYNC output                                               |         |                                         |      |      |       |         |

| DSYNC output variable coarse delay time setting resolution | Rdsync1 |                                         |      | 2    |       | bit     |

| DSYNC output variable coarse delay time                    | Td1     |                                         | 1    |      | 4     | CLK     |

| DSYNC output variable fine delay time setting resolution   | Rdsync2 |                                         |      | 5    |       | bit     |

| DSYNC output variable fine delay time                      | Td2     |                                         | 1/16 |      | 20/16 | CLK     |

| VCO characteristics                                        |         |                                         |      | 4_   |       |         |

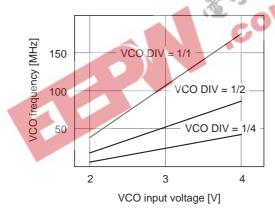

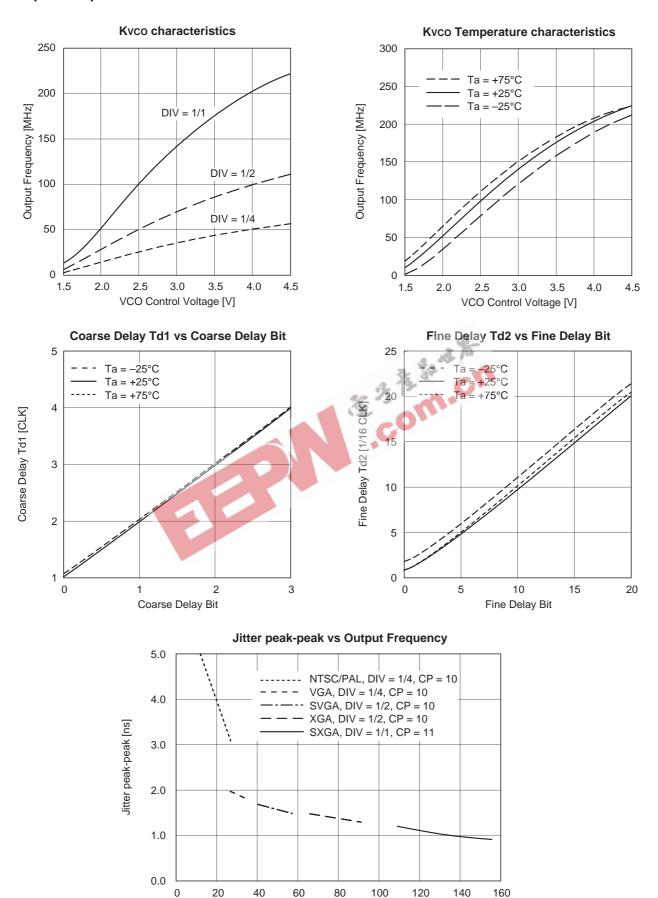

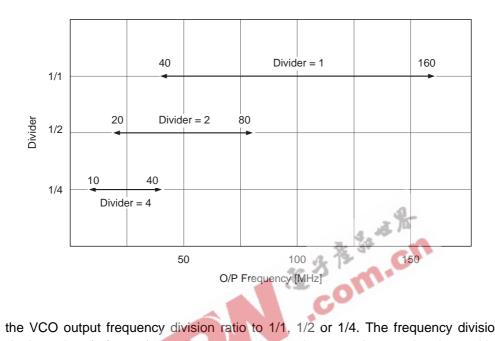

| DIV output frequency operation range 1                     | Fvco1   | DIV = 1/1                               | 40   | CIU  | 160   | MHz     |

| DIV output frequency operation range 2                     | Fvco2   | DIV = 1/2                               | 20   |      | 80    | MHz     |

| DIV output frequency operation range 3                     | Fvco3   | DIV = 1/4                               | 10   |      | 40    | MHz     |

| VCO lock range                                             | Vlock   |                                         | 1.7  |      | 4.4   | V       |

| VCO gain 1                                                 | Kvco1   | DIV = 1/1                               | 240  | 400  | 640   | Mrad/sv |

| VCO gain 2                                                 | Kvco2   | DIV = 1/2                               | 120  | 200  | 320   | Mrad/sv |

| VCO gain 3                                                 | Kvco3   | DIV = 1/4                               | 60   | 100  | 160   | Mrad/sv |

| Charge pump current 1                                      | Kpd1    | C.Pump Bit = 00,<br>IREF = $1.6k\Omega$ | 80   | 100  | 130   | μA      |

| Charge pump current 2                                      | Kpd2    | C.Pump Bit = 10,<br>IREF = $1.6k\Omega$ | 350  | 400  | 500   | μA      |

| Charge pump current 3                                      | Kpd3    | C.Pump Bit = 11,<br>IREF = 1.6kΩ        | 1350 | 1600 | 1800  | μA      |

| VCO counter bits                                           | Rdiv2   |                                         |      | 12   |       | bit     |

| Item                                                            | Symbol    | Conditions                   | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------------------|-----------|------------------------------|------|------|------|------|

| CLK (CLK, CLK/2) output                                         |           |                              |      | ,    |      |      |

| CLK output (PECL) frequency range 1                             | Fclk1PECL | DIV = 1/1                    | 40   |      | 160  | MHz  |

| CLK output (PECL) frequency range 2                             | Fclk2PECL | DIV = 1/2                    | 20   |      | 80   | MHz  |

| CLK output (PECL) frequency range 3                             | Fclk3PECL | DIV = 1/4                    | 10   |      | 40   | MHz  |

| CLK, CLK/2 output (PECL) rise time                              | TrPECL    | 10% to 90%, RL = $330\Omega$ | 1.0  | 1.5  | 2.0  | ns   |

| CLK, CLK/2 output (PECL) fall time                              | TfPECL    | 10% to 90%, RL = $330\Omega$ | 1.0  | 1.5  | 2.0  | ns   |

| CLK output (TTL) frequency range 1                              | Fclk1TTL  | DIV = 1/1                    | 40   |      | 80   | MHz  |

| CLK output (TTL) frequency range 2                              | Fclk2TTL  | DIV = 1/2                    | 20   |      | 80   | MHz  |

| CLK output (TTL) frequency range 3                              | Fclk3TTL  | DIV = 1/4                    | 10   | g    | 40   | MHz  |

| CLK, CLK/2 output (TTL) rise time                               | TrTTL     | 10% to 90%,<br>CL = 10pF     | 2.0  | 3.0  | 4.0  | ns   |

| CLK, CLK/2 output (TTL) fall time                               | TfTTL     | 10% to 90%,<br>CL = 10pF     | 2.0  | 3.0  | 4.0  | ns   |

| CLK output (PECL, TTL) duty                                     | Dclk2     | CL = 10pF                    | 40   | 50   | 60   | %    |

| SYNC input (PECL) and CLK output (PECL) delay offset            | Td3       | CL = 10pF                    |      | 1    |      | ns   |

| CLK output (PECL) and DSYNC output (PECL) phase difference      | Td4       | CL = 10pF                    | 1.5  | 2.4  | 3.0  | ns   |

| CLK output (PECL) and CLK/2 output (PECL) phase difference      | Td5       | CL = 10pF                    | 0.0  | 0.8  | 1.0  | ns   |

| CLK output (PECL) and DIVOUT output (TTL) rise phase difference | Td6       | CL = 10pF                    | 10   | 14   | 19   | ns   |

| CLK output (PECL) and DIVOUT output (TTL) fall phase difference | Td7       | CL = 10pF                    | 8    | 11   | 14   | ns   |

| DSYNC, CLK, CLK/2 PECL output and TTL output phase difference   | Td8       | CL = 10pF                    | 1.5  | 3.0  | 4.5  | ns   |

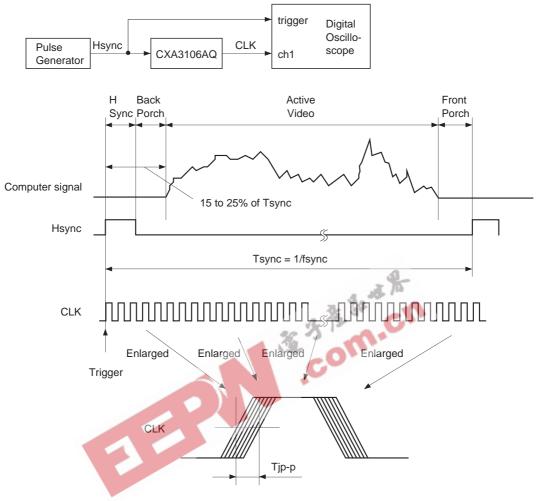

| Item                              | Symbol | Conditions                                                                        | Min. | Тур.          | Max. | Unit |

|-----------------------------------|--------|-----------------------------------------------------------------------------------|------|---------------|------|------|

| CLK (CLK, CLK/2) output           |        |                                                                                   |      |               |      |      |

| CLK vs. SYNC output jitter (NTSC) | Tj1p-p | triggered at SYNC Fsync = 15.73kHz (Crystal) Fclk = 12.27MHz N = 780              | 3.0  | 5.0           | 8.0  | ns   |

| CLK vs. SYNC output jitter (VGA)  | Tj2p-p | triggered at SYNC<br>Fsync = 31.47kHz<br>(Crystal)<br>Fclk = 25.18MHz<br>N = 800  | 1.0  | 2.0           | 3.0  | ns   |

| CLK vs. SYNC output jitter (SVGA) | Тј3р-р | triggered at SYNC<br>Fsync = 48.08kHz<br>(Crystal)<br>Fclk = 50.00MHz<br>N = 1040 | 0.9  | 1.6           | 2.5  | ns   |

| CLK vs. SYNC output jitter (XGA)  | Tj4p-p | triggered at SYNC<br>Fsync = 56.48kHz<br>(Crystal)<br>Fclk = 75.00MHz<br>N = 1328 | 0.8  | <b>%</b> -1.5 | 2.0  | ns   |

| CLK vs. SYNC output jitter (SXGA) | Тј5р-р | triggered at SYNC<br>Fsync = 80kHz<br>(Crystal)<br>Fclk = 136.00MHz<br>N = 1700   | 0.6  | 1.0           | 1.4  | ns   |

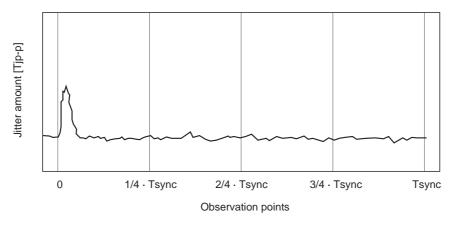

| CLK vs. DSYNC output jitter       | Тј6р-р | triggered at DSYNC                                                                |      |               | 0.1  | ns   |

| Control registers                 | 1      |                                                                                   |      |               |      |      |

| SCLK frequency                    | SCLK   | in write/read mode                                                                |      |               | 12   | MHz  |

| SENABLE setup time                | TENS   | in write mode                                                                     | 3    |               |      | ns   |

| SENABLE hold time                 | TENH   | in write mode                                                                     | 0    |               |      | ns   |

| SDATA setup time                  | TDS    | in write mode                                                                     | 3    |               |      | ns   |

| SDATA hold time                   | TDH    | in read mode                                                                      | 0    |               |      | ns   |

| SENABLE setup time                | TNENS  | in read mode                                                                      | 3    |               |      | ns   |

| SENABLE hold time                 | TNENH  | in read mode                                                                      | 0    |               |      | ns   |

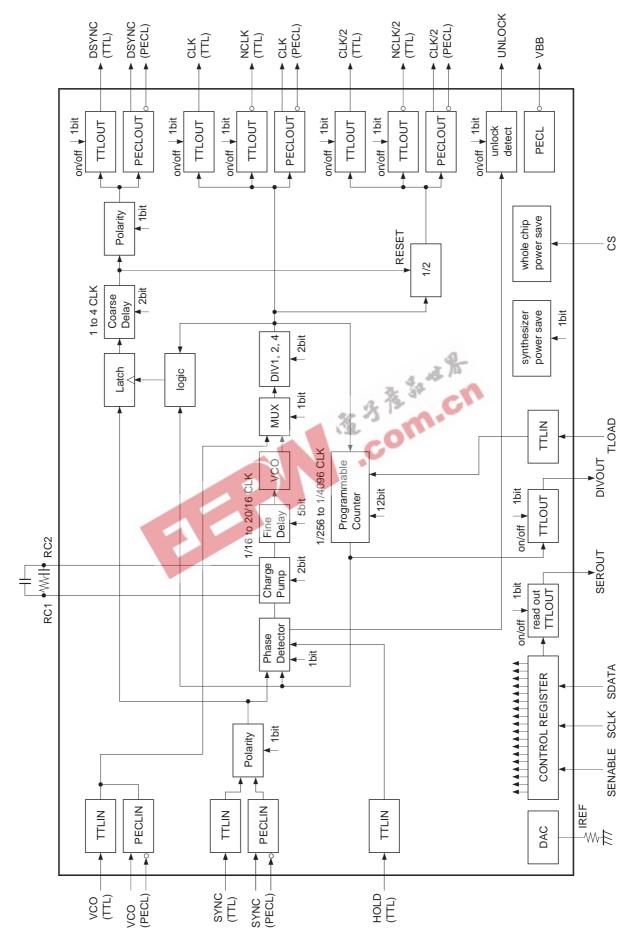

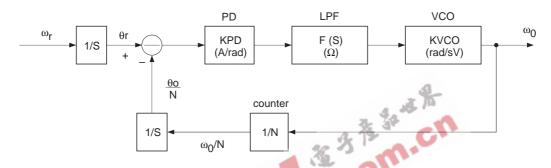

#### **Description of Block Diagram**

#### Sync Input

Sync signals in the range of 10 to 100kHz can be input. Input supports both positive and negative polarity. PECL input can also be a single input.

When SYNC is positive polarity, the clock is regenerated in synchronization with the rising edge of the sync signal. When SYNC is negative polarity, the clock is regenerated in synchronization with the falling edge of the sync signal. VCO oscillation stops when there is no sync input.

| Register: SYNC POL  | 1        | 0        |  |

|---------------------|----------|----------|--|

| SYNC input polarity | Positive | Negative |  |

#### **Phase Detector**

The phase detector operates at the sync input frequency of 10 to 100kHz. The PD input polarity should be set to the default PD POL = 1. Phase comparison is performed at the edges.

The input circuit of the phase detector does not contain a hysteresis circuit, so the waveform must be shaped at the front end of the CXA3106AQ when inputting a noisy signal.

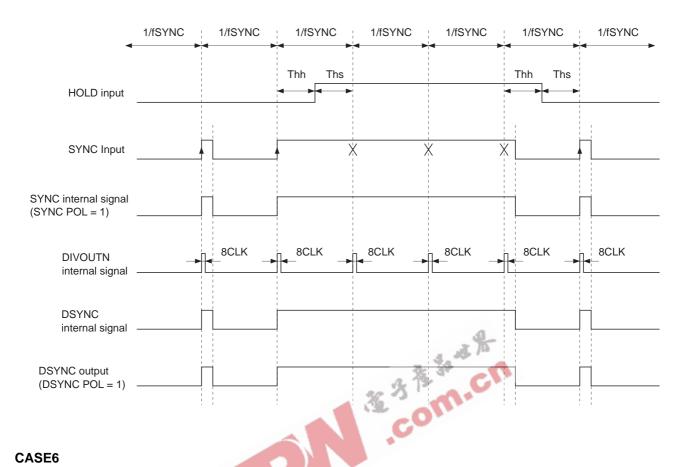

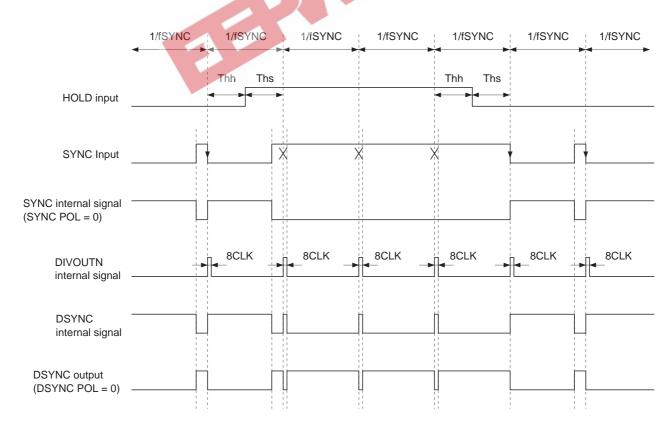

...ing Cha The phase detector HOLD signal is supplied by TTL. (See the HOLD Timing Chart.)

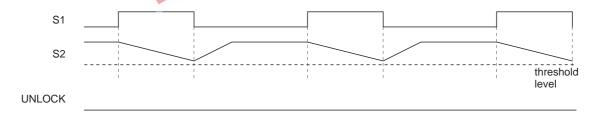

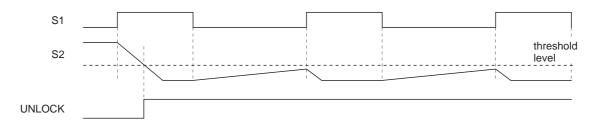

The PLL UNLOCK signal is output by an open collector. (See the UNLOCK Timing Chart.)

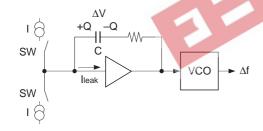

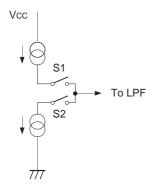

# **Charge Pump**

The gain (I, I/4, I/16) can be varied by changing the charge pump current using 2 bits of control register.

| Register: C.Pump bit 1 | 0     | 1     | 1      |

|------------------------|-------|-------|--------|

| Register: C.Pump bit 0 | 0     | 0     | 1      |

| Charge pump current    | 100µA | 400µA | 1600µA |

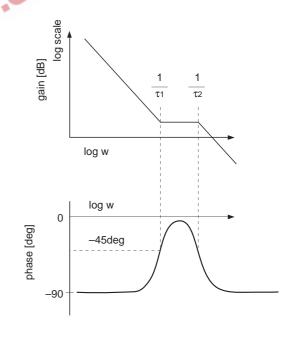

#### **LPF**

This is a loop filter comprised of the external capacitors and resistor.

Be sure to use metal film resistors with little temperature variation and a temperature-compensated capacitor. In particular, the 0.33µF capacitor should be equivalent to high dielectric constant series capacitor type B or better. (electrostatic capacitance change ratio  $\pm 10\%$ : T = -25 to +85°C)

#### **VCO**

The VCO oscillator frequency covers from 40 to 160MHz.

# **VCO Rear-end Counter**

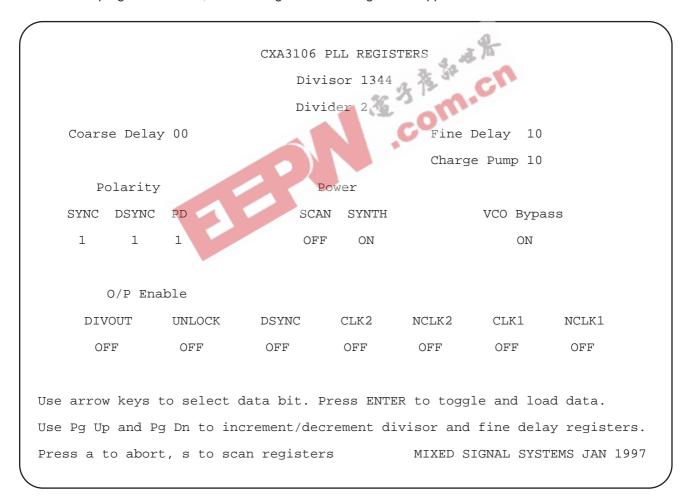

The VCO output is frequency divided to 1/1, 1/2 or 1/4 by switching 2 bits of control register.

The operating range can be expanded to 10 to 160MHz by combining the counter with a VCO frequency divider.

| Register: DIV 1, 2, 4 bit 1 | 0   | 1   | 1   |

|-----------------------------|-----|-----|-----|

| Register: DIV 1, 2, 4 bit 0 | 0   | 0   | 1   |

| Counter frequency divisions | 1/1 | 1/2 | 1/4 |

#### **Feedback Programmable Counter**

This counter can be set as desired from 256 to 4096 using 12 bits.

Frequency divisions =  $(m + 1) \times 8 + n$ , n: 3 bits (VCO DIV bits 0 to 2), m: 9 bits (VCO DIV bits 3 to 11)

When the register value is changed, the new setting is actually loaded to the counter when the counter value becomes "all 0".

#### **Clock Output**

When SYNC input is positive polarity, the clock is regenerated in synchronization with the rising edge of the sync signal.

The clock output delay time can be changed in the range of 1/16 to 20/16 CLK using 5 bits of control register. (See the I/O Timing Chart.)

Output is TTL and PECL (complementary), and supports both positive and negative polarity. Clock TTL output can also be turned off independently.

| Register: Clock Enable | 1  | 0   |

|------------------------|----|-----|

| Clock output status    | ON | OFF |

#### 1/2 Clock Output

Reset is performed at the delay sync timing and the clock output is frequency divided by 1/2. (See the I/O Timing Chart.)

Both odd and even output are TTL and PECL output. TTL output can also be turned off independently.

| Register: Clock Enable | 1  | 0   |

|------------------------|----|-----|

| Clock output status    | ON | OFF |

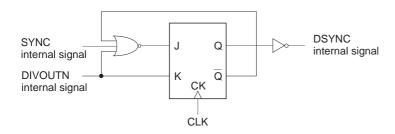

# **Delay Sync Output**

The front edge of the delay sync pulse is latched by the pulse obtained by frequency dividing the CLK regenerated by the PLL, so there is almost no jitter with respect to CLK. This front edge can be used as the reset signal for the system timing circuit.

The rear edge of the delay sync pulse is latched by the CLK regenerated by the PLL. This relationship is undefined for one clock as shown in the Timing Chart.

The delay sync output delay time can be varied in two stages. First, the delay time can be varied in the range of 1/16 to 20/16 CLK using 5 bits of control register, and then in the range of 1 to 4 CLK using 2 bits of control register. In other words, the total delay time is ((1/16 to 20/16) + (1 to 4)) CLK. (See the I/O Timing Chart.)

DSYNC output is TTL and PECL (complementary), and supports both positive and negative polarity. Clock TTL output can also be turned off.

| Register: Clock Enable | 1  | 0   |

|------------------------|----|-----|

| Clock output status    | ON | OFF |

| Lower delay line<br>FINE DELAY bits 0 to 4 | 00000   | 00001   | <br>10011    |

|--------------------------------------------|---------|---------|--------------|

| Delay time                                 | 1/16CLK | 2/16CLK | <br>20/16CLK |

| Upper delay line<br>COARSE DELAY bits 0 to 1 | 00   | 01   | 10   | 11   |

|----------------------------------------------|------|------|------|------|

| Delay time                                   | 1CLK | 2CLK | 3CLK | 4CLK |

| Register: DSYNC POL   | 1        | 0        |

|-----------------------|----------|----------|

| DSYNC output polarity | Positive | Negative |

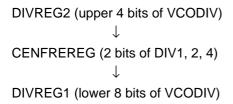

# Control Circuit (3-bit address, 8-bit data)

The timing and input methods are described hereafter.

| Feedback programmable counter control                   | REGISTER1, 2 | 12bit | VCO DIV Bit0 to 11      |

|---------------------------------------------------------|--------------|-------|-------------------------|

| VCO rear-end counter control                            | REGISTER3    | 2bit  | DIV1, 2, 4 Bit0, Bit1   |

| Fine delay line control                                 | REGISTER4    | 5bit  | FINE DELAY Bit0 to 4    |

| Coarse delay line control                               | REGISTER4    | 2bit  | COARSE DELAY Bit0, Bit1 |

| Charge pump current DAC control                         | REGISTER5    | 2bit  | C.Pump Bit0, Bit1       |

| Phase detector input positive/negative polarity control | REGISTER5    | 1bit  | PD POL                  |

| Sync input positive/negative polarity control           | REGISTER6    | 1bit  | SYNC POL                |

| Delay sync output positive/negative polarity control    | REGISTER6    | 1bit  | DSYNC POL               |

| Clock TTL output OFF function                           | REGISTER6    | 1bit  | CLK Enable              |

| Inverted clock TTL output OFF function                  | REGISTER6    | 1bit  | NCLK Enable             |

| 1/2 clock TTL output OFF function                       | REGISTER6    | 1bit  | CLK/2 Enable            |

| Inverted 1/2 clock TTL output OFF function              | REGISTER6    | 1bit  | NCLK/2 Enable           |

| Delay sync TTL output OFF function                      | REGISTER6    | 1bit  | DSYNC Enable            |

| UNLOCK output OFF function                              | REGISTER6    | 1bit  | UNLOCK Enable           |

| Programmable counter input switching                    | REGISTER7    | 1bit  | VCO By-pass             |

| Power save with register contents held                  | REGISTER7    | 1bit  | Synth power             |

| Register read function power ON/OFF                     | REGISTER7    | 1bit  | Read out power          |

| Programmable counter TTL output OFF function            | REGISTER7    | 1bit  | DIVOUT Enable           |

# **Power Save**

The CXA3106Q realizes 2-step power saving (all OFF, control registers only ON). This is controlled by a control register and the chip selector.

Step 1: Chip selector control

| CS                | Н        | L       |

|-------------------|----------|---------|

| Power save status | Power ON | All OFF |

Step 2: Control register control

| Register: Synth power | 1        | 0                         |  |  |  |  |

|-----------------------|----------|---------------------------|--|--|--|--|

| Power save status     | Power ON | Control registers only ON |  |  |  |  |

# Readout Circuit (during test mode)

The control register contents can be read by serial data from SEROUT. (See the Control Register Timing Chart.)

| Register: Read out power | 0            | 1           |

|--------------------------|--------------|-------------|

| Readout status           | Function OFF | Function ON |

# **Programmable Counter Output (during test mode)**

The programmable counter output is TTL output from the DIVOUT pin.

(See the I/O Timing Chart.)

This output is normally not used.

| Register: DIVOUT Enable | 0   | 1  |  |  |

|-------------------------|-----|----|--|--|

| DIVOUT output status    | OFF | ON |  |  |

# **TLOAD** input (during test mode)

This control signal forcibly loads the control register contents to the programmable counter.

This signal is normally not used.

| TLOAD                      | Н            | L           |  |  |

|----------------------------|--------------|-------------|--|--|

| Forced load control status | Function OFF | Function ON |  |  |

# VCO input (during test mode)

| oo input (during test mout    | -,               |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------|------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|