# LCD Driver

### **Description**

The CXA2112R is a driver IC developed for use in the 6-input/12-input Sony polysilicon TFT LCD panel (LCX016/017). It has a line invert amplifier and analog de-multiplexers, timing generator and output buffers required for these. CXA2112R can directly drive analog inputs of LCX016/017. It is used one IC with the LCX016, and two ICs with the LCX017. The VCOM setting circuit and pre-charge pulse waveform generator are also on-chip.

### **Features**

- High-speed signal processing supports XGA high refresh signal (dot clock to 100MHz)

- Overall wide band response

- · Low output deviation by on-chip output offset cancel circuit

- Small phase delay difference between inverted signal and non-inverted signal

On-chip timing generator with ECL

Dot clock phase adjustment function

VCOM voltage generation circuit

Pre-charge pulse waveform generation circuit

# **Absolute Maximum Ratings**

| Supply voltage                                  | Vcc | 16          | V    |                               |

|-------------------------------------------------|-----|-------------|------|-------------------------------|

| Supply voltage                                  | VDD | 5.5         | V    |                               |

| Operating temperature                           |     | -20 to +70  | °C   |                               |

| Storage temperature                             |     | -65 to +150 | °C   |                               |

| <ul> <li>Allowable power dissipation</li> </ul> | PD  | 2300        | mW ( | single layered board mounted) |

## **Operating Conditions**

| <ul> <li>Supply voltage</li> </ul> | Vcc | 15 to 15.5   | V |

|------------------------------------|-----|--------------|---|

| <ul> <li>Supply voltage</li> </ul> | Vdd | 4.75 to 5.25 | V |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

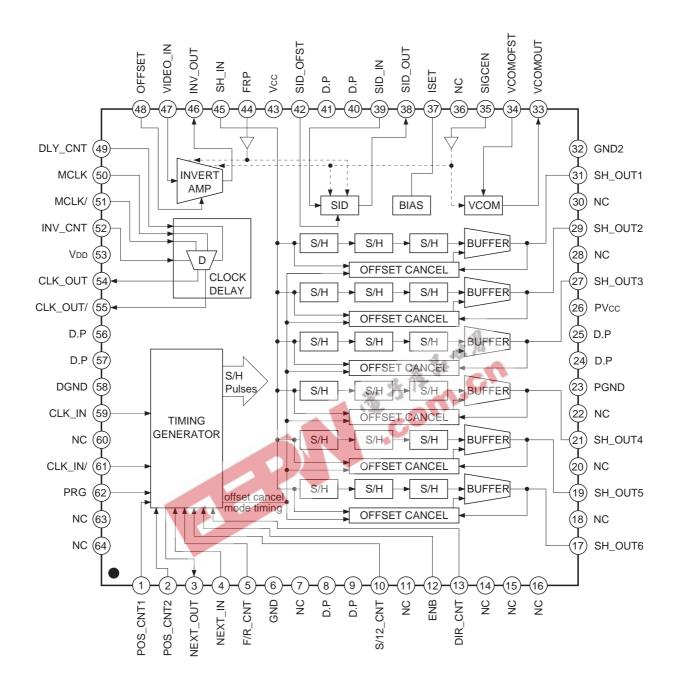

# **Block Diagram**

# **Pin Description**

| Pin<br>No. | Symbol   | I/O | Standard voltage level                   | Equivalent circuit                                                                                                                  | Description                                                                     |

|------------|----------|-----|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 1          | POS_CNT1 | . 1 | See<br>Table A-1.                        | VDD VDD 60k                                                                                                                         | Sample-and-hold position setting.                                               |

| 2          | POS_CNT2 |     | Table A-1.                               | 2k 20µ 777 1.6V 777 777 777 20µ 10µ                                                                                                 | See Tables A-1, A-2 and A-3.                                                    |

| 3          | NEXT_OUT | 0   | Approx. 4V                               | 3<br>7/// 600µ                                                                                                                      | Connect as closely as possible to NEXT_IN.                                      |

| 4          | NEXT_IN  | I   |                                          | VDD<br>VDD                                                                                                                          | Connect as closely as possible to NEXT_OUT.                                     |

| 5          | F/R_CNT  | I   | High; ≥ 2.5V<br>Low: ≤ 0.8V<br>OPEN High | V <sub>DD</sub> V <sub>DD</sub> V <sub>DD</sub> V <sub>DD</sub> 100k V <sub>DD</sub> 100k V <sub>DD</sub> 100k V <sub>DD</sub> 100k | Before/after decision for 12-output. See Table B.                               |

| 10         | S/12_CNT | ı   | High: ≥ 2.5V<br>Low: ≤ 0.8V<br>OPEN High | 5<br>10<br>7/7/<br>5<br>100k<br>7/7/<br>₹ 100k                                                                                      | 6-output/12-output switch.<br>High: 6-output<br>Low: 12-output.<br>See Table B. |

| 12         | ENB      | I   | High: ≥ 2.5V<br>Low: ≤ 0.8V              | VDD                                                                                                                                 | Horizontal sync signal ENB input.<br>Refer to Timing Chart.                     |

| Pin<br>No. | Symbol   | I/O | Standard voltage level                   | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Description                                                                                                                                |

|------------|----------|-----|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 13         | DIR_CNT  | I   | High: ≥ 2.5V<br>Low: ≤ 0.8V<br>OPEN High | VDD VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Scan direction switch. High: forward scan Low: reverse scan                                                                                |

| 6          | GND      |     | GND                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Analog GND.                                                                                                                                |

| 17         | SH_OUT6  |     |                                          | PVcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                            |

| 19         | SH_OUT5  |     |                                          | PVcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                            |

| 21         | SH_OUT4  | 0   | 2.5 to 11.5V                             | (17) (27)<br>(19) (29)<br>(19) (29)<br>(19) (29)<br>(17) (27)<br>(17) (27)<br>(19) (29)<br>(19) (29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29)<br>(29) | Output.                                                                                                                                    |

| 27         | SH_OUT3  | O   | 2.5 to 11.50                             | $ \begin{array}{c c} (21)(31) &                                   $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Cutput.                                                                                                                                    |

| 29         | SH_OUT2  |     |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                            |

| 31         | SH_OUT1  |     |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                            |

| 33         | VCOMOUT  | 0   | 5 to 8V                                  | Vcc 70µ Vcc 10µ Vcc 10µ Vcc \$500 Vcc 2k W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VCOM output. Can be set to Vsigcen to Vsigcen –2V by Pin 34 input. Vsigcen: voltage set by Pin 35.                                         |

| 34         | VCOMOFST | I   | 0 to 10V                                 | 34 200k 1p 500 500 500 777 777 777 777 777 777 777                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VCOM output setting. Deviation from SIGCEN input is 0 for input setting of 0V. VCOM is set at the minus side from VSIGCEN at high voltage. |

| 35         | SIGCEN   | I   | 7V                                       | Усс<br>10k<br>7/// 20µ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Center voltage of signal inversion setting. Output signal is inverted, centered around this voltage, by FRP high/low. Normally, set to 7V. |

| Pin<br>No. | Symbol   | I/O | Standard voltage level      | Equivalent circuit                                   | Description                                                                                     |

|------------|----------|-----|-----------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 37         | ISET     | I   | 1.35V                       | Vcc<br>45µ<br>Vcc<br>Vcc<br>10µ<br>145<br>2k<br>17/7 | Vcc circuit bias current setting. Normally, connect $27k\Omega$ (±1%) between this pin and GND. |

| 38         | SID_OUT  | 0   | 2.5 to 11.5V                | Vcc 75k 0.2p 0.2p 775k 0.2p 777                      | SID signal waveform output.<br>Connect to an external<br>buffer for panel.                      |

| 23         | PGND     |     | GND                         | 2 %                                                  | Power GND.                                                                                      |

| 26         | PVcc     |     | 15.5V                       | Tom.                                                 | Power Vcc. Connect directly to Vcc.                                                             |

| 32         | GND2     |     | GND                         |                                                      | Analog GND.                                                                                     |

| 39         | SID_IN   | 1   | 2.3 to 3.3V                 | 39 Yoc                                               | SID signal input.                                                                               |

| 42         | SID_OFST | I   | 3.3V                        | Vcc<br>30k<br>42 W 10μ                               | SID signal input offset setting.                                                                |

| 44         | FRP      | I   | High: ≥ 2.5V<br>Low: ≤ 0.8V | VDD VDD VDD 100k 100k 100k 100k 100k                 | Invert pulse input. High: inverse Low: non-inverse Refer to Timing Chart.                       |

| Pin<br>No. | Symbol   | I/O | Standard voltage level | Equivalent circuit                                         | Description                                                       |

|------------|----------|-----|------------------------|------------------------------------------------------------|-------------------------------------------------------------------|

| 45         | SH_IN    | ı   | 2.5 to 11.5V           | 45<br>1.9k<br>                                             | Sample-and-hold circuit common input. Should not be less than 2V. |

| 46         | INV_OUT  | 0   | 2.5 to 11.5V           | Усс Усс Усс Усс Усс Усс Усс — 560µ — 620µ — 7/// 7/// 7/// | Invert amplifier output.                                          |

| 47         | VIDEO_IN | I   | 2.0 to 3.3V            | Vсс<br>Vсс<br>300µ<br>47<br>777                            | Invert amplifier input.                                           |

| 48         | OFFSET   | I   | 3.3V                   | Vcc<br>30k<br>W 10μ                                        | Video signal input offset<br>setting.<br>Inputs 100% white level. |

| 49         | DLY_CNT  | I   | 3 to 5V                | VDD<br>VDD<br>2k<br>W√<br>7777<br>50µ                      | Dot clock phase adjustment.                                       |

| 43         | Vcc      |     | 15.5V                  |                                                            | 15V power supply.                                                 |

| Pin<br>No. | Symbol   | I/O | Standard voltage level      | Equivalent circuit                                               | Description                                                 |  |

|------------|----------|-----|-----------------------------|------------------------------------------------------------------|-------------------------------------------------------------|--|

| 50         | MCLK     | . 1 | PECL<br>differential        | V <sub>DD</sub><br>20k<br>1k  10μ                                | Dot clock input.                                            |  |

| 51         | MCLK/    |     | umerenuai                   | 777<br>VDD 100µ<br>777                                           |                                                             |  |

| 52         | INV_CNT  | I   | High: ≥ 2.5V<br>Low: ≤ 0.8V | VDD<br>VDD<br>10µ<br>52<br>W                                     | Dot clock phase invert control.                             |  |

| 54         | CLK_OUT  |     | VDD - 0.3V                  | VDD VDD                                                          | Phase adjusted dot clock output.                            |  |

| 55         | CLK_OUT/ |     | IO VDD                      | 55 Im 1m                                                         | ouiput.                                                     |  |

| 59         | CLK_IN   | ı   | Vpp – 0.3V                  | VDD VDD VDD 2k ≥ 2k                                              | On-chip timing generator clock input.                       |  |

| 61         | CLK_IN/  | I   | to VDD                      |                                                                  | Connect directly to Pins 54 and 55.                         |  |

| 62         | PRG      | I   | High: ≥ 2.5V<br>Low: ≤ 0.8V | VDD<br>VDD<br>VDD<br>↓ 150k<br>↓ 50k<br>↓ 145<br>↑ 7/7 7/7 ↓ 50k | Horizontal sync signal PRG input.<br>Refer to Timing Chart. |  |

| Pin<br>No.                                                              | Symbol | I/O | Standard voltage level | Equivalent circuit | Description                                                 |

|-------------------------------------------------------------------------|--------|-----|------------------------|--------------------|-------------------------------------------------------------|

| 53                                                                      | Vdd    |     | 5V                     |                    | 5V power supply.                                            |

| 58                                                                      | DGND   |     |                        |                    | Digital GND.                                                |

| 8, 9,<br>24, 25,<br>40, 41,<br>56, 57                                   | D.P    |     | GND                    |                    | Die pad. Used as thermal radiator on board. Connect to GND. |

| 7, 11,<br>14, 15,<br>16, 18,<br>20, 22,<br>28, 30,<br>36, 60,<br>63, 64 |        |     |                        |                    | No connection. Not connected to anything.                   |

# **Electrical Characteristics (See Electrical Characteristics Measurement Circuit.)**

$V_{DD} = 5V$ ,  $V_{CC} = 15.5V$ ,  $V_{SIGCEN} = 7V$ , Ta = 25°C

| No. | Item                                           | Symbol | Measurement points | Measurement contents                                                                                                                                                                           | Min.                | Тур. | Max. | Unit  |

|-----|------------------------------------------------|--------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|------|-------|

| 1   | VDD current consumption                        | IDD    | IVDD               | IDD = IVDD                                                                                                                                                                                     | 22                  | 32   | 42   | mA    |

| 2   | Vcc current consumption                        | Icc    | IVCC1<br>IVCC2     | Icc = Ivcc1 + Ivcc2                                                                                                                                                                            | 30                  | 41   | 52   | mA    |

| 3   | Invert amplifier gain                          | AINV   | VINV<br>VIN        | AINV = VINV (AC)/VIN                                                                                                                                                                           | _                   | 2.7  | _    | times |

| 4   | Invert amplifier slew rate                     | SRINV  | VINV               | Input a square wave from VIN so that VINV output amplitude is 3.5Vp-p. Measure slew rate at 10 to 90% of output waveform rise or fall. (for inverse or non-inverse)                            | _                   | 700  | _    | V/µs  |

| 5   | Invert amplifier output band width             | BWinv  | VINV               | Input 2.5V DC, 100mVp-p AC from Pin 47 (VIDEO_IN) and measure VINV. The frequency that is –3dB to 100kHz. (for inverse/non-inverse)                                                            |                     | 90   |      | MHz   |

| 6   | Output delay deviation for inverse/non-inverse | TDIFF  | VINV               | Invert amplifier delay time difference for inverse and non-inverse.                                                                                                                            | _                   | 2    | 4    | ns    |

| 7   | SID gain                                       | Asid   | VSID<br>VSID_IN    | ASID = VSID (AC)/VSID_IN                                                                                                                                                                       | _                   | 4    | _    | times |

| 8   | SID output slew rate                           | SRsid  | Vsid               | Input invert pulse to Pin 44 (FRP), load capacity C7 = 47pF, and apply DC input voltage to VSID_IN so that VSID is 2.5V/11.5V. Measure slew rate at 10 to 90% of output waveform rise or fall. | _                   | 30   | _    | V/µs  |

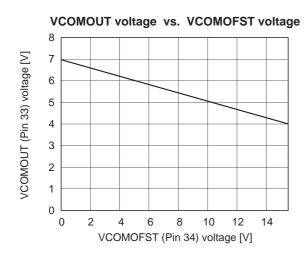

| 9   | VCOM adjustable range                          | Vсом   | Vсом               | VCOM output voltage when Pin 34 (VCOMOFST) is changed from 0 to 10V.                                                                                                                           | Vsig – 2<br>or less | _    | Vsig | V     |

| 10  | Farst stage S/H slew rate                      | SRSH1  | _                  | First stage S/H slew rate on Block Diagram.                                                                                                                                                    | _                   | 700  | _    | V/µs  |

| 11  | SH_OUT slew rate                               | SRout  | Vout1 to<br>Vout6  | Input a square wave from Vin so that VOUT1 to VOUT6 output amplitude is 3.5Vp-p. Measure slew rate at 10 to 90% of output waveform rise or fall. (load 270pF, for inverse or non-inverse)      | _                   | 150  | _    | V/µs  |

| 12  | Output deviation between channels *            | Douт   | Vout1 to<br>Vout6  | Apply DC voltage to VIN so that VINV (SH_IN) is 6V.                                                                                                                                            | _                   | 3    | 10   | mVp-p |

| 13  | Dot clock input highest frequency              | fclkh  | fclk               | Highest frequency for fclk output at correct timing.                                                                                                                                           | 100                 | 115  |      | MHz   |

| 14  | Dot clock input lowest frequency               | fclkl  | fclk               | Lowest frequency for fclk output at correct timing.                                                                                                                                            |                     | 12   | 20   | MHz   |

| 15  | Maximum output voltage                         | VMAX   | Vout1 to<br>Vout6  | Maximum voltage at which sample-and-hold output (SH_OUT1 to SH_OUT6) can be output.                                                                                                            | 13                  | 13.5 |      | V     |

| 16  | Minimum output voltage                         | Vmin   | Vout1 to<br>Vout6  | Minimum voltage at which sample-and-hold output (SH_OUT1 to SH_OUT6) can be output.                                                                                                            |                     | 2    | 2.5  | V     |

- \* Minimum VOUT1 to VOUT6 value subtracted from maximum VOUT1 to VOUT6 value. Unless otherwise specified, pin setting conditions are as follows.

- (48) OFFSET = 3.3V, (47) VIDEO\_IN = 2.0V, (42) SID\_OFST = 3.3V, (39) SID\_IN = 2.3V,

- (35) SIGCEN = 7.0V, (34) VCOMOFST = 0.0V, (1) POS\_CNT1 = 0.0V, (2) POS\_CNT2 = 0.0V,

- (5)  $F/R_CNT = 5.0V$ , (10)  $S/12_CNT = 5.0V$ , (13)  $DIR_CNT = 5.0V$ , (49)  $DLY_CNT = 4.0V$ ,

- (52)  $INV\_CNT = 5.0V$ , (44) FRP = 0.0V, fclk = 65MHz

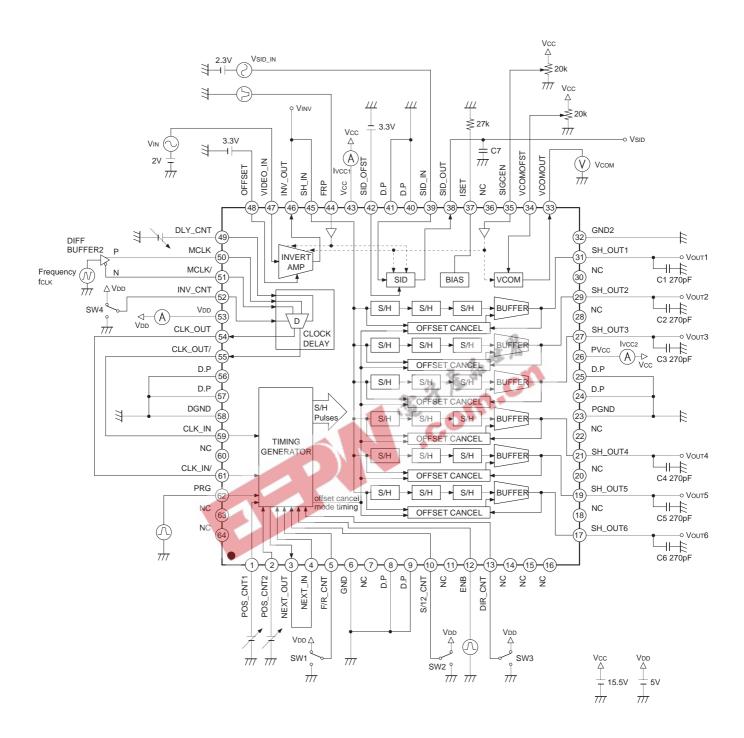

### **Electrical Characteristics Measurement Circuit**

### **Description of Operation**

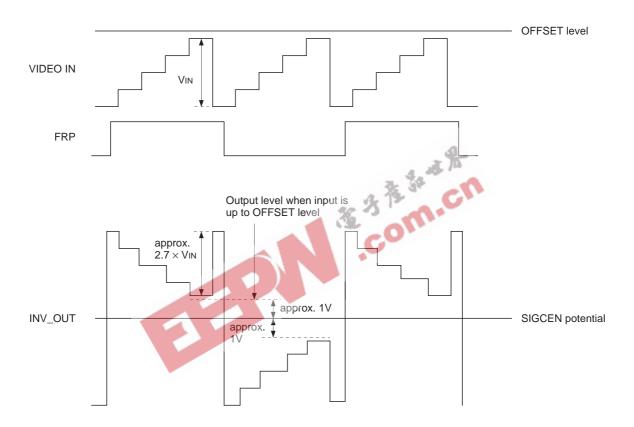

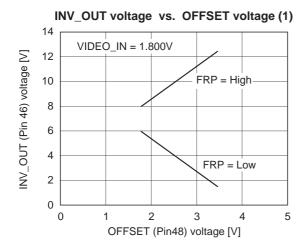

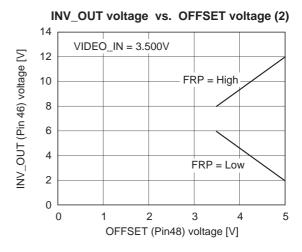

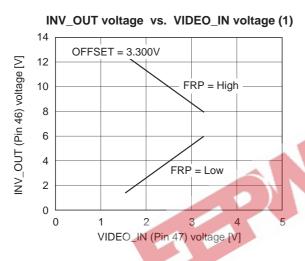

# 1. INVERT\_AMP

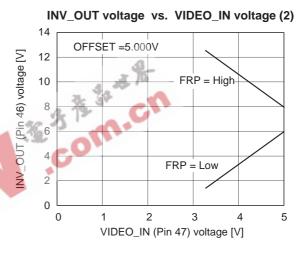

The VIDEO signal from VIDEO\_IN (Pin 47) is amplified about 2.7 times at INVERT\_AMP. Its output is INV\_OUT (Pin 46). Status of INVERT\_AMP is determined by FRP (Pin 44) input (high: inverse, low: non-inverse). Invert operation is carried out with SIGCEN (Pin 35) potential as center voltage of signal inversion. OFFSET (Pin 48) input voltage corresponds to 100% white level of the signal input to VIDEO\_IN.

When used in combination with the CXA2111R, connect the CXA2111R V33 (Pin 8) output to the CXA2112R OFFSET. When use DA converter output as the VIDEO signal, connect DA converter maximum output voltage (normally, DA converter's supply voltage).

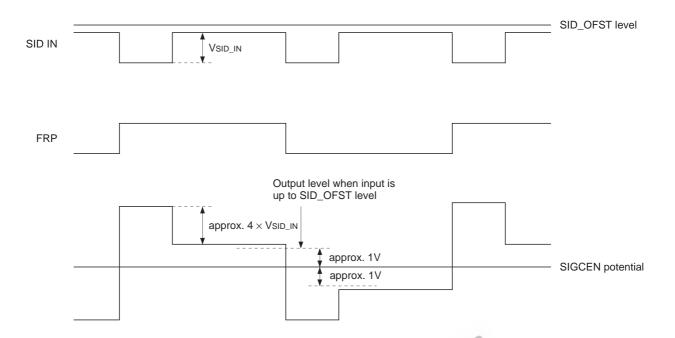

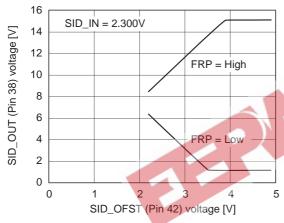

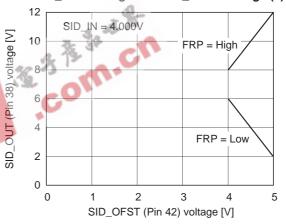

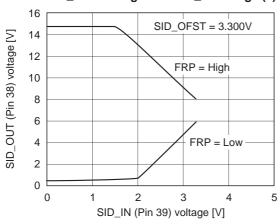

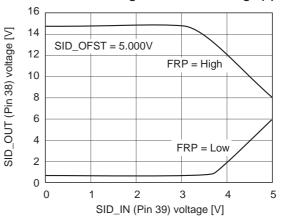

### 2. SID

The signal input to SID\_IN (Pin 39) is folded by SIGCEN potential, the same as for INVERT\_AMP operation, and outputs to SID\_OUT (Pin 38).

Gain is about 4 times. SID\_OFST (Pin 42) operates in the same way as OFFSET input for INVERT\_AMP. In combination with the CXA2111R, connect the CXA2111R SID\_OUT (Pin 6) to the CXA2112R SID\_IN, and CXA2111R V33 (Pin 8) to the CXA2112R SID\_OFST.

The SID output is prepared for the Sony LCD panel's (LCX017 and LCX016) uniformity improvement signal input (Psig input). SID\_OUT does not have the capability to drive those pins directly. Connect via a buffer.

### 3. VCOM

VCOM generates the DC voltage applied to the Sony LCD panel COM electrode. VCOMOUT (Pin 33) voltage is set as the deviation relative to SIGCEN voltage.

When VCOMOFST (Pin 34) is changed from 0 to 10V, VCOMOUT changes from (SIGCEN potential) to (SIGCEN potential) – 2V.

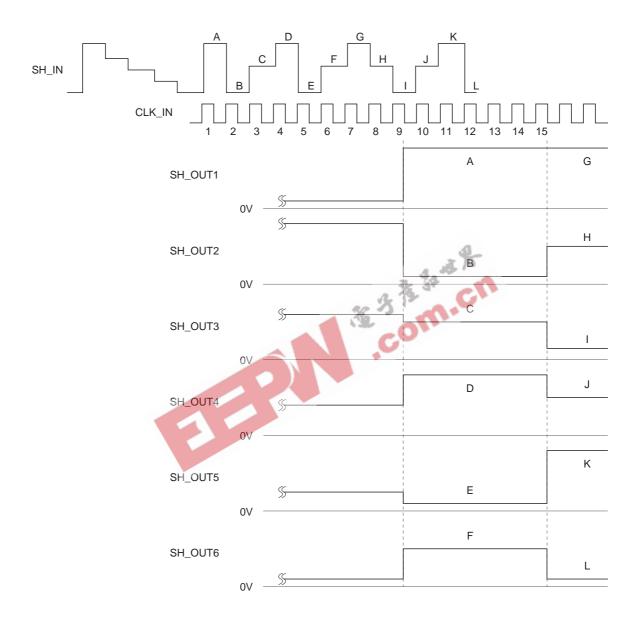

### 4. De-Multiplexer

SH\_IN (Pin 45) input is de-multiplexed in order from SH\_OUT1 (Pin 31) to SH\_OUT6 (Pin 17) according to internal timing generator setting, and then is output.

Output phase is made simultaneous by the 3-stage sample-and-hold circuit.

The waveform example below shows this operation for forward scan, 6-output de-multiplexing.

Depending on the operation mode setting, scan direction (SH\_OUT1  $\rightarrow$  SH\_OUT6 and SH\_OUT6  $\rightarrow$  SH\_OUT1), number of outputs (6-output/12-output) and sample-and-hold position (output phase) can be changed.

# 5. Operation Mode Setting

For each RGB channel, LCX016 requires demultiplexed 6 analog outputs (one CXA2112R), and LCX017 needs 12 (two CXA2112R). In either case, scan direction switching, sample-and-hold position and phase can be controlled. The mode input pin settings for each case are shown below.

### **Fixed Mode Setting**

|                   | LCX016    | LCX017                        |                             |  |

|-------------------|-----------|-------------------------------|-----------------------------|--|

|                   | 6-outputs | "FRONT" half of 12 outputs*2  | "REAR" half of 12 outputs*2 |  |

| S/12_CNT (Pin 10) | High      | Low                           | Low                         |  |

| F/R_CNT (Pin 5)   | X*1       | High                          | Low                         |  |

| NEXT_IN (Pin 4)   | Short     | Connect to the other NEXT_OUT |                             |  |

| NEXT_OUT (Pin 3)  | Short     | Connect to the other NEXT_IN  |                             |  |

\*2 "FRONT": input data sampling begins from "FRONT" chip for forward scan direction (DIR\_CNT high).

Table B

## 2) Scan direction switching

DIR\_CNT (Pin 13) high gives forward scan, and low gives reverse scan. For forward scan, the input signal level time series is output in descending order from SH\_OUT1, and for reverse scan, in descending order from SH\_OUT6.

For 12-output, SH\_OUT6 and SH\_OUT1 operated as if connected in order.

# 3) Sample-and-hold position setting

Output's phase can be changed by the voltage applied to POS\_CNT1 (Pin 1) and POS\_CNT2 (Pin 2). This setting is done for adjustment of the LCD panel input signal timing. Each input pin has 4 setting values, for a total of 16 settings.

POS\_CNT1 is lower, POS\_CNT2 is upper, and each setting values are as shown in Table A-1.

# **Setting Voltage Range for Sample-and-Hold Position**

| Setting value | Threshold     |

|---------------|---------------|

| 0             | GND to 0.75V  |

| 1             | 1.15 to 1.50V |

| 2             | 1.70 to 2.55V |

| 3             | 2.95 to VDD   |

Table A-1

<sup>\*1</sup> X: Don't Care

There are two ways to use these pins.

A. Connect directly to the CXA2111R.

Connect to the corresponding CXA2111R pins POS\_CNT1 and POS\_CNT2. This allows bit setting via the CXA2111R register controlled by I<sup>2</sup>C bus.

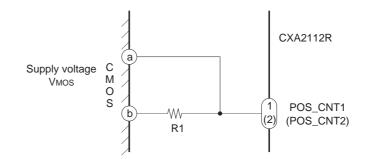

B. Connect to CMOS logic.

Connect CMOS logic as shown in the diagram. See Table A-2.

# **CMOS Logic Connection**

# **Setting Value and CMOS Output Pins**

| Setting value | а    | b |

|---------------|------|---|

| 0             | L    | L |

| 1             | Hi-Z | L |

| 2             | Hi-Z | Н |

| 3             | Н    | Н |

Table A-2

R1 sets the level for setting values 1 and 2. The appropriate resistance value changes depending on numbers of CXA2112R are driven by one CMOS logic (1-channel or RGB 3-channel drive, or one CXA2112R (6-outputs/ch) or two CXA2112R (12-outputs/ch)).

Recommended resistance values are given in Table A-3.

### **CMOS Logic Connection**

# Usage of CXA2112R and Threshold Setting Resistor R1

|          | RGB 1-channel drive |            | RGB 3-channel drive |            |

|----------|---------------------|------------|---------------------|------------|

|          | 6-outputs           | 12-outputs | 6-outputs           | 12-outputs |

| R1 value | 270kΩ               | 150kΩ      | 100kΩ               | 47kΩ       |

**Table A-3** Vmos = 3.3 to 5V

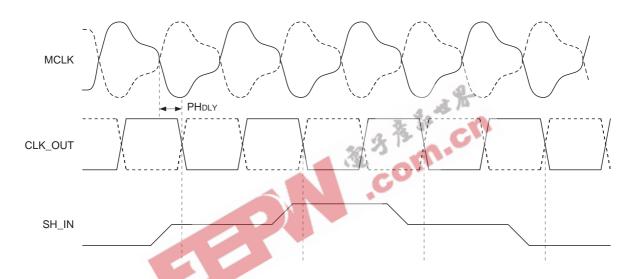

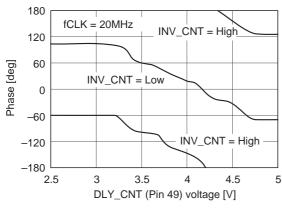

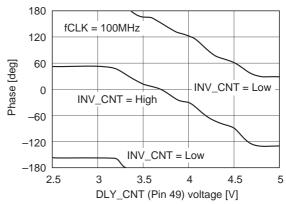

### 6. Dot Clock Phase Adjustment

The CXA2112R has phase adjustment function for input dot clock to achieve high precision and stable operation.

High definition images with no jitter and flicker can be reproduced by this adjustment.

De-multiplexer operation timing is generated from the clock input to CLK\_IN (Pin 59) and CLK\_IN/ (Pin 61) (ECL differential). By connecting CLK\_OUT (Pin 54) and CLK\_OUT/ (Pin 55) to CLK IN/, phase adjusted clock can be used for its timing generation.

The CLOCK DELAY block is a PLL clock generator that uses MCLK (Pin 50) and MCLK/ (Pin 51) ECL differential input clock as reference. The CLK\_OUT polarity, inverted/non-inverted can be switched by high/low of INV\_CNT (Pin 52) input.

Also, in the DLY\_CNT (Pin 49) input voltage range of 3 to 5V, CLK\_OUT phase relative to MCLK can be changed continuously 180deg. (PHDLY in the diagram below.)

It also has the advantage that an MCLK with noise can be shaped and used on the board.

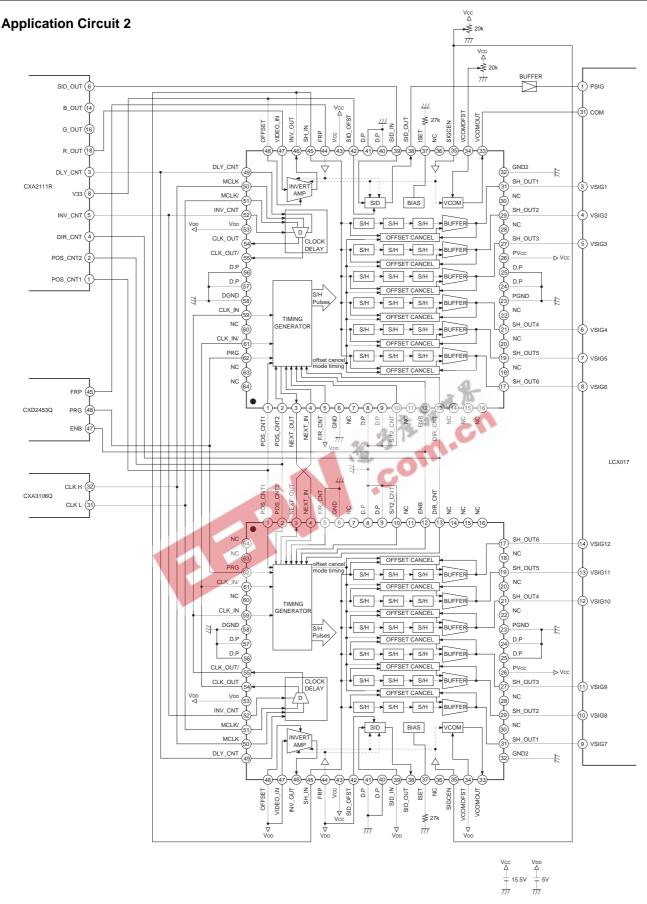

# 7. Usage of CXA2112R in 12-outputs

Two CXA2112Rs are required for 12-outputs, as shown in Application Circuit 2. Please note that the following precautions.

- Input the same clock to both ICs' timing generator clock input pins CLK\_IN and CLK\_IN/. To be concrete, connect one CLK\_OUT and CLK\_OUT/ to both ICs' CLK\_IN and CLK\_IN/. At this time, the other CLK\_OUT and CLK\_OUT/ are not used, but be sure to input the same clock to MCLK and MCLK/ inputs.

- Connect both ICs' SH\_INs to only one ICs' INV\_OUT. At that time, connect the other ICs' VIDEO\_IN and OFFSET to 5V. In the same way, connect the other ICs' SID\_IN and SID\_OFST to 5V.

- When only one IC is used for all of INVET\_AMP, SID and VCOM, the FRP input on the other IC does not have to be at the timing in the above paragraph, but can be connected to GND.

- Short ENB, PRG, POS\_CNT1, POS\_CNT2, DIR\_CNT, INV\_CNT and DLY\_CNT at both ICs, and apply the same signals.

### **Notes on Operation**

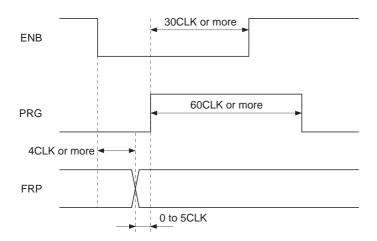

# 1. Signal input timings to the timing generator Input Signal Timing Chart

Maintain the relationship in the timing chart. While PRG is high, video input signal must not be changed. The same name output from Sony's LCD timing generators CXD2442Q and CXD2453Q satisfy the above conditions.

If the above timing does not be satisfied, timing violation may cause decay of characteristics or IC damage in some case. Especially do not input FRP pulse without ENB and PRG input.

We strongly recommend to verify the design on this timings and presence of ENB and PRG.

### 2. Notes on Mounting

- Please be sure that the wiring for internal timing generator link pins NEXT\_IN (Pin 4) and NEXT\_OUT (Pin 3) is as short as possible, in especially 12-outputs. Also, do not locate a large amplitude high-speed signal path (such as CMOS logic) near the wiring.

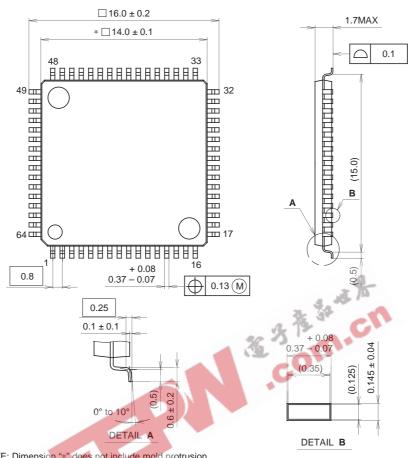

- The eight pins 8, 9, 24, 25, 40, 41, 56 and 57 are connected to the "die pad" inside the package. A good thermal radiation effect can be achieved by a thick connection to GND plane.

- Be sure to short PVcc (Pin 26) and Vcc (Pin 43) so that they go on and off simultaneously.

### 3. Input Video Signal

• Please be sure that the video signal amplitude (0% black level to 100% white level) which inputs to sample and hold (SH\_IN (Pin 45)) does not exceed 3.5Vpp.

Also, as for inputting to sample and hold, do not apply DC level of 2V or lower during operation.

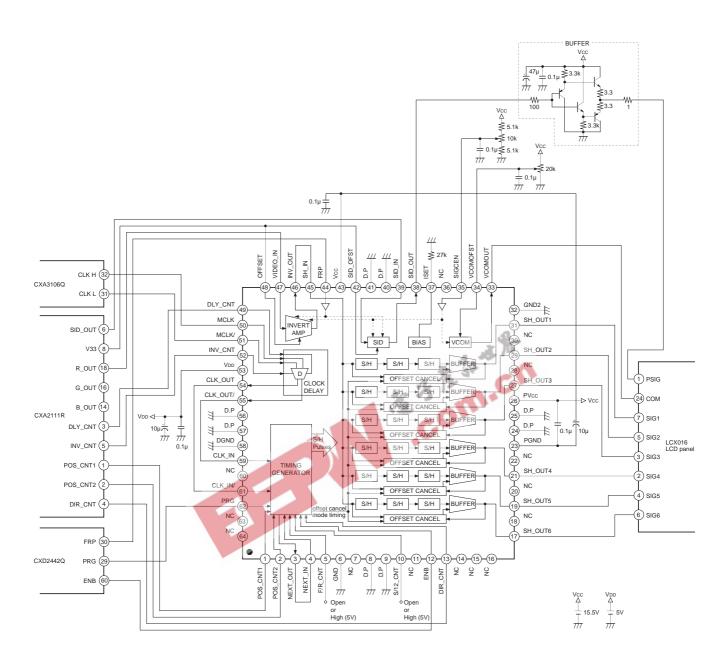

# **Application Circuit 1**

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

Example of Representative Characteristics (Vcc = 15.5V, Vdd = 5.0V, SIGCEN = 7.0V, Ta = 25°C)

# CLK\_OUT phase to MCLK vs. DLY\_CNT voltage (1) CLK\_OUT phase to MCLK vs. DLY\_CNT voltage (2)

SID\_OUT voltage vs. SID\_OFST voltage (1)

SID\_OUT voltage vs. SID\_OFST voltage (2)

SID\_OUT voltage vs. SID\_IN voltage (1)

SID\_OUT voltage vs. SID\_IN voltage (2)

# **Package Outline**

Unit: mm

# 64PIN LQFP (PLASTIC)

NOTE: Dimension "\*" does not include mold protrusion.

# PACKAGE STRUCTURE

|            |                | PACKAGE MATERIAL | EPOXY RESIN       |

|------------|----------------|------------------|-------------------|

| SONY CODE  | LQFP-64P-L02   | LEAD TREATMENT   | PALLADIUM PLATING |

| EIAJ CODE  | LQFP064-P-1414 | LEAD MATERIAL    | COPPER ALLOY      |

| JEDEC CODE |                | PACKAGE MASS     | 0.7g              |

|            |                |                  |                   |

**NOTE: PALLADIUM PLATING**

This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).