# Pentium/SDRAM Clock Generator with Integrated Buffers

#### **FEATURES**

- Generates all clock frequencies for Pentium (II), AMD and Cyrix system requiring multiple CPU clocks.

- Supports up to 16 Synchronous CPU clocks (4 CPU and 12 SDRAM) and 7 Synchronous PCI BUS clocks.

- Two 14.318Mhz reference clocks and one 2.5V IOAPIC

- One 24Mhz floppy clock and one 48Mhz USB clock.

- Power management control pins to stop CPU, SDRAM or PCI BUS clocks.

- Supports 2-wire I2C serial bus interface.

- 50% duty cycle with low jitter

- Mixed voltage support from 3.0 to 5V or (VDDq2=2.5V)

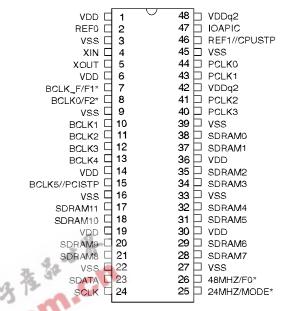

- Available in 300mil 48 pin SSOP.

## FREQUENCY SELECTION (MHz)

| F2 | F1 | F0 | PCLK/SDRAM | BCLK         |

|----|----|----|------------|--------------|

| 0  | 0  | 0  | 50         | 25           |

| 0  | 0  | 1  | 100        | 50           |

| 0  | 1  | 0  | 83.3       | 41.6         |

| 0  | 1  | 1  | 68.5       | 34.2         |

| 1  | 0  | 0  | 55         | <b>27</b> .5 |

| 1  | 0  | 1  | 75         | 37.5         |

| 1  | 1  | 0  | 60         | 30           |

| 1  | 1  | 1  | 66.6       | 33.3         |

#### PIN INFORMATION

PLL52C63-01

Note: F2,F1,F0 and MODE are selectable only during power-on. They are HIGH by default and LOW when 10K  $\Omega$  Pull down is attached.

#### I/O MODE CONFIGURATION

| MODE       | PIN15  | PIN46  |

|------------|--------|--------|

| 1 (OUTPUT) | BCLK5  | REF1   |

| 0 (INPUT)  | PCISTP | CPUSTP |

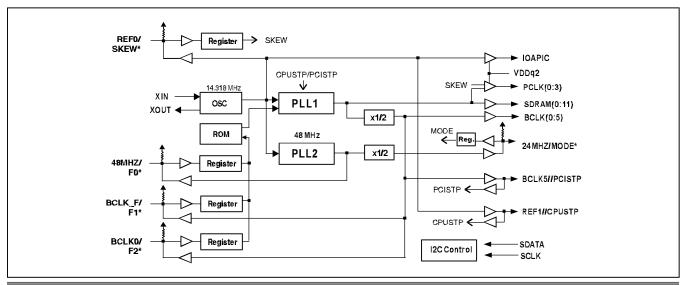

### **BLOCK DIAGRAM**