| FAI | RC | ы | LD |

|-----|----|---|----|

|     |    |   |    |

SEMICONDUCTOR®

November 2002 Revised November 2002

## FSTU32X800 20-Bit Bus Switch with Precharged Outputs and -2V Undershoot Protection

#### **General Description**

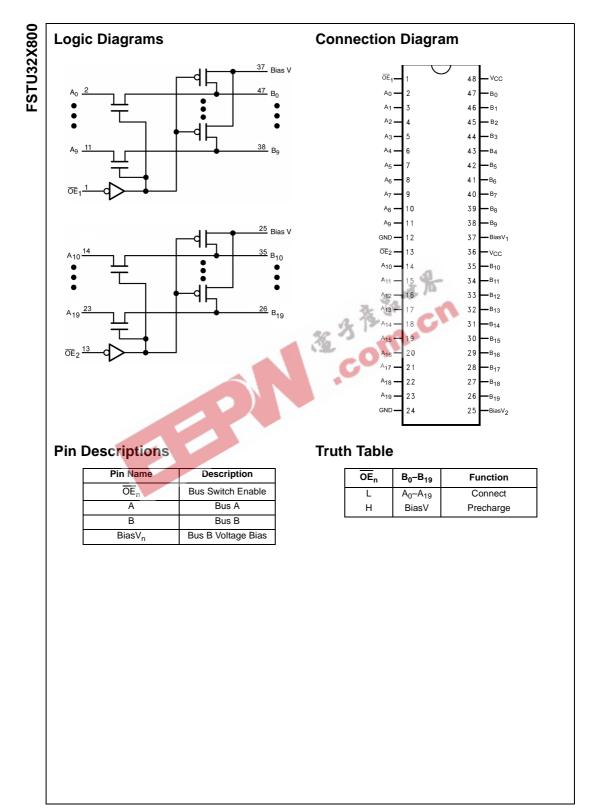

The Fairchild Switch FSTU32X800 provides 20-bits of high-speed CMOS TTL-compatible bus switching. The low On Resistance of the switch allows inputs to be connected to outputs without adding propagation delay or generating additional ground bounce noise. The A and B Ports are protected against undershoot to support an extended range to 2.0V below ground. Fairchild's integrated Undershoot Hardened Circuit (UHC™) senses undershoot at the I/O and responds by preventing voltage differentials from developing and turning the switch on. The device also precharges the B Port to a selectable bias voltage (BiasV) to minimize live insertion noise.

The device is organized as two 10-bit switches with a bus enable  $(\overline{OE}_n)$  signal. When  $\overline{OE}_n$  is LOW, the switch is ON and Port A is connected to Port B. When  $\overline{OE}_n$  is HIGH, the switch is OPEN and the B Port is precharged to BiasV through an equivalent 10-k $\Omega$  resistor.

#### **Ordering Code:**

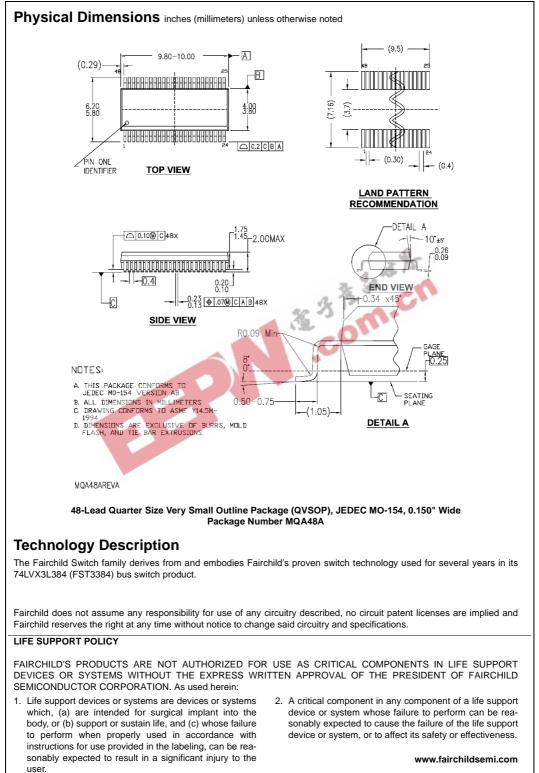

| Order Number                                                                                              | Package<br>Number | Package Description                                                                |  |  |

|-----------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------|--|--|

| FSTU32X800QSP                                                                                             | MQA48A            | 48-Lead Quarter Size Very Small Outline Package (QVSOP), JEDEC MO-154, 0.150" Wide |  |  |

| Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code. |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

|                                                                                                           |                   |                                                                                    |  |  |

| UHC <sup>™</sup> is a trademark of Fairchild Semiconductor Corporation.                                   |                   |                                                                                    |  |  |

**Features**

Low I<sub>CC</sub>

$\blacksquare$  4 $\Omega$  switch connection between two ports

■ Soft enable turn-on to minimize bus-to-bus charge

Output precharge to minimize live insertion noise

Undershoot Hardened to -2 0V

■ Zero bounce in flow-through mode

Control inputs compatible with TTL level

See Applications Note AN-5008 for details

...ons Note AN-

sharing during enable

www.fairchildsemi.com

#### Absolute Maximum Ratings(Note 1)

| Supply Voltage (V <sub>CC</sub> )                                    | -0.5V to +7.0V   |

|----------------------------------------------------------------------|------------------|

| DC Switch Voltage (V <sub>S</sub> )                                  | -2.0V to +7.0V   |

| Bias V Voltage Range                                                 | -0.5V to +7.0V   |

| DC Input Voltage (VIN) (Note 2)                                      | -0.5V to +7.0V   |

| DC Input Diode Current (I <sub>IK</sub> ) $V_{IN}$ < 0V              | –50 mA           |

| DC Output (I <sub>OUT</sub> ) Sink Current                           | 128 mA           |

| DC V <sub>CC</sub> /GND Current (I <sub>CC</sub> /I <sub>GND</sub> ) | +/- 100 mA       |

| Storage Temperature Range (T <sub>STG</sub> )                        | –65°C to +150 °C |

|                                                                      |                  |

# Recommended Operating Conditions (Note 3)

| Power Supply Operating ( $V_{CC}$ )    | 4.0V to 5.5V     |

|----------------------------------------|------------------|

| Precharge Supply (BiasV)               | 1.5V to $V_{CC}$ |

| Input Voltage (V <sub>IN</sub> )       | 0V to 5.5V       |

| Output Voltage (V <sub>OUT</sub> )     | 0V to 5.5V       |

| Input Rise and Fall Time $(t_r, t_f)$  |                  |

| Switch Control Input                   | 0 ns/V to 5 ns/V |

| Switch I/O                             | 0 ns/V to DC     |

| Free Air Operating Temperature $(T_A)$ | –40 °C to +85 °C |

Note 1: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The Recommended Operating Conditions tables will define the conditions for actual device operation.

Note 2: The input and output negative voltage ratings may be exceeded if the input and output diode current ratings are observed.

Note 3: Unused control inputs must be held HIGH or LOW. They may not float.

|                   |                                       |                        |                         |                                | A 196        |       |                                                                                            |

|-------------------|---------------------------------------|------------------------|-------------------------|--------------------------------|--------------|-------|--------------------------------------------------------------------------------------------|

| Symbol            | Parameter                             | V <sub>CC</sub><br>(V) | T <sub>A</sub> =<br>Min | 40 °C to +4<br>Typ<br>(Note 4) | 85 °C<br>Max | Units | Conditions                                                                                 |

| V <sub>IK</sub>   | Clamp Diode Voltage                   | 4.5                    |                         |                                | -1.2         | V     | I <sub>IN</sub> = -18 mA                                                                   |

| V <sub>IH</sub>   | HIGH Level Input Voltage              | 4.0 - 5.5              | 2.0                     |                                |              | V     |                                                                                            |

| V <sub>IL</sub>   | LOW Level Input Voltage               | 4.0 - 5.5              |                         |                                | 0.8          | V     |                                                                                            |

| I <sub>I</sub>    | Input Leakage Current                 | 5.5                    |                         |                                | ±1.0         | μA    | $0 \le V_{IN} \le 5.5V$                                                                    |

| I <sub>O</sub>    | Output Current                        | 4.5                    | 0.25                    |                                |              | mA    | BiasV = 2.4V, B = 0                                                                        |

| I <sub>OZ</sub>   | OFF-STATE Leakage Current             | 5.5                    |                         |                                | ±1.0         | μΑ    | $0 \leq A \leq V_{CC}, \ V_{IN} = V_{IH}$                                                  |

| R <sub>ON</sub>   | Switch On Resistance                  | 4.5                    |                         | 4.0                            | 7.0          | Ω     | $V_{S} = 0V$ , $I_{IN} = 64 \text{ mA}$                                                    |

|                   | (Note 5)                              | 4.5                    |                         | 4.0                            | 7.0          | Ω     | V <sub>S</sub> = 0V, I <sub>IN</sub> = 30 mA                                               |

|                   |                                       | 4.5                    |                         | 8.0                            | 15.0         | Ω     | $V_{S} = 2.4V, I_{IN} = 15 \text{ mA}$                                                     |

|                   |                                       | 4.0                    |                         | 11.0                           | 20.0         | Ω     | $V_S = 2.4V$ , $I_{IN} = 15 \text{ mA}$                                                    |

| I <sub>CC</sub>   | Quiescent Supply Current (Note 6)     | 5.5                    |                         |                                | 3.0          | μΑ    | $V_{S} = V_{CC}$ or GND, $I_{OUT} = 0$                                                     |

| $\Delta I_{CC}$   | Increase in I <sub>CC</sub> per Input | 5.5                    |                         |                                | 2.5          | mA    | OE Input at 3.4V                                                                           |

|                   | (Note 7)                              |                        |                         |                                |              |       | Other Inputs at $V_{CC}$ or GND                                                            |

| I <sub>BIAS</sub> | Bias Pin Leakage Current              | 5.5                    |                         |                                | ±1.0         | μA    | $\overline{\text{OE}} = 0\text{V}, \text{ B} = 0\text{V}, \text{ BiasV} = 5.5\text{V}$     |

| I <sub>OZU</sub>  | Switch Undershoot Current             | 5.5                    |                         |                                | 100.0        | μΑ    | $I_{IN} = -20 \text{ mA}, \overline{OE} = 5.5 \text{V}, \text{ V}_{OUT} \ge \text{V}_{IH}$ |

| V <sub>IKU</sub>  | Voltage Undershoot                    | 5.5                    |                         |                                | -2.0         | V     | 0.0 mA $\ge$ I <sub>IN</sub> $\ge$ -50 mA, $\overline{\text{OE}}$ = 5.5V                   |

### **DC Electrical Characteristics**

Note 4: Typical values are at  $V_{CC}=5.0V$  and  $T_{A}=+25^{\circ}C$

Note 5: Measured by the voltage drop between A and B pins at the indicated current through the switch. On Resistance is determined by the lower of the voltages on the two (A or B) pins.

Note 6: Per V<sub>CC</sub> pin.

Note 7: Per TTL driven inputs, control pins only.

#### FSTU32X800 **AC Electrical Characteristics** $T_A = -40 \ ^\circ C$ to +85 $^\circ C$ , $C_L = 50 \text{ pF}, \text{RU} = \text{RD} = 500\Omega$ Figure Number Symbol Parameter Units Conditions $V_{CC} = 4.5 - 5.5V$ $V_{CC} = 4.0V$ Min Max Min Max Propagation Delay Bus to Bus Figures 1, 2 t<sub>PHL</sub>, V<sub>I</sub> = OPEN 0.25 0.25 ns (Note 8) t<sub>PLH</sub> Output Enable Time $V_I = OPEN$ t<sub>PZH</sub> 7.0 30.0 35.0 ns $\overline{\text{OE}}_1$ , $\overline{\text{OE}}_2$ , to A<sub>n</sub>, B<sub>n</sub> BiasV = GND Figures 1, 2 t<sub>PZL</sub> $V_I = 7V$ 7.0 30.0 35.0 ns BiasV = 3V Output Disable Time $V_I = OPEN$ t<sub>PHZ</sub> 1.0 6.1 6.5 ns $\overline{\mathsf{OE}}_1, \overline{\mathsf{OE}}_2, \text{ to } \mathsf{A}_n, \mathsf{B}_n$ BiasV = GND Figures 1, 2 $V_I = 7V$ t<sub>PLZ</sub> 1.0 7.3 6.8 ns BiasV = 3V Note 8: This parameter is guaranteed by design but is not tested. The bus switch contributes no propagation delay other than the RC delay of the typical On Resistance of the switch and the 50 pF load capacitance, when driven by an ideal voltage the source (zero output impedance). Capacitance (Note 9) TA Symbol Parameter Тур Max Units Conditions pF 3.0 $V_{CC} = 5.0V$ CIN Control Pin Input Capacitance 1 C<sub>I/O</sub> Input/Output Capacitance 5.0 $V_{CC}, \overline{OE} = 5.0V$ pF Note 9: $T_A = +25^{\circ}C$ , f = 1 MHz, Capacitance is characterized but not tested. AC Loading and Waveforms FROM OUTPUT UNDER RD TEST Note: Input driven by $50\Omega$ source terminated in $50\Omega$ , RU = RD = $500\Omega$ Note: C1 includes load and stray capacitance, C1 = 50 pF Note: Input PRR = 1.0 MHz, $t_W = 500 \text{ ns}$ FIGURE 1. AC Test Circuit t<sub>f</sub> = 2.5 nS $t_{r} = 2.5 \, nS$ 3.0V 90% 90% $t_{r} = 2.5 \text{ nS}$ = 2.5 nS ENABLE 3.0V 1.5 INPUT 90% 00% SWITCH INPUT 10% 10% 1.5V --GND **Б**\ t<sub>PZL</sub> <sup>t</sup>PLZ 10% 10% GND <sup>t</sup>PLH -tPHL OUTPUT - - V<sub>OH</sub> 1.5V V<sub>OL</sub> + 0.3V \_ VOL OUTPUT 1.5V 1.5V t<sub>PHZ</sub> tPZH · VOH - -VOL V<sub>OH</sub> - 0.3V 1.5V OUTPUT FIGURE 2. AC Waveforms

www.fairchildsemi.com