## **DISCRETE SEMICONDUCTORS**

# DATA SHEET

1. Marian

J174; J175; J176; J177

P-channel silicon field-effect transistors

Product specification

File under Discrete Semiconductors, SC07

April 1995

## P-channel silicon field-effect transistors

J174; J175; J176; J177

#### **DESCRIPTION**

Silicon symmetrical p-channel junction FETs in a plastic TO-92 envelope and intended for application with analog switches, choppers, commutators etc.

A special feature is the interchangeability of the drain and source connections.

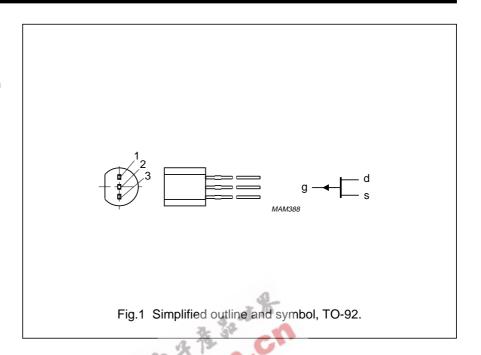

#### **PINNING**

1 = source

2 = gate

3 = drain

Note: Drain and source are interchangeable.

#### **QUICK REFERENCE DATA**

| Drain-source voltage                                      | ± V <sub>DS</sub>  | max.         |           | 30      |         |           | V        |

|-----------------------------------------------------------|--------------------|--------------|-----------|---------|---------|-----------|----------|

| Gate-source voltage                                       | V <sub>GSO</sub>   | max.         |           | 30      |         |           | V        |

| Gate current                                              | -I <sub>G</sub>    | max.         |           | 50      |         |           | mA       |

| Total power dissipation<br>up to T <sub>amb</sub> = 50 °C | P <sub>tot</sub>   | max.         |           | 400     |         |           | mW       |

|                                                           |                    |              | J174      | J175    | J176    | J177      |          |

| Drain current<br>$-V_{DS} = 15 \text{ V}; V_{GS} = 0$     | -I <sub>DSS</sub>  | min.<br>max. | 20<br>135 | 7<br>70 | 2<br>35 | 1.5<br>20 | mA<br>mA |

| Drain-source ON-resistance                                |                    |              |           |         |         |           |          |

| $-V_{DS} = 0.1 \text{ V}; V_{GS} = 0$                     | R <sub>DS on</sub> | max.         | 85        | 125     | 250     | 300       | Ω        |

#### J174; J175; P-channel silicon field-effect transistors J176; J177 **RATINGS** Limiting values in accordance with the Absolute Maximum System (IEC 134) $\pm\,V_{DS}$ Drain-source voltage 30 ٧ max. Gate-source voltage $V_{\text{GSO}}$ 30 ٧ max. V Gate-drain voltage $V_{GDO}$ 30 max. Gate current (DC) 50 $-I_G$ max. mA Total power dissipation up to $T_{amb} = 50 \, ^{\circ}C$ $P_{tot}$ 400 mW max. ٥С Storage temperature range $T_{stg}$ -65 to +150 ٥С Junction temperature $T_i$ 150 max. THERMAL RESISTANCE 250 K/W From junction to ambient in free air R<sub>th j-a</sub> STATIC CHARACTERISTICS J175 J176 J177 T<sub>i</sub> = 25 °C unless otherwise specified Gate cut-off current $V_{GS} = 20 \text{ V}; V_{DS} = 0$ 1 1 1 nA Drain cut-off current $-V_{DS} = 15 \text{ V}; V_{GS} = 10 \text{ V}$ max. 1 1 nA Drain current min. 20 7 2 1.5 mA $-V_{DS} = 15 \text{ V}; V_{GS} = 10 \text{ V}$ $-I_{DSS}$ 70 max. 135 35 20 mA Gate-source breakdown voltage $I_G = 1 \mu A; V_{DS} = 0$ $V_{(BR)GSS}$ min. 30 30 30 30 V Gate-source cut-off voltage min. 5 3 1 0.8 V $-I_D = 10 \text{ nA}; V_{DS} = -15 \text{ V}$ $V_{GS off}$ 6 2.25 V max. 10 4 Drain-source ON-resistance

R<sub>DSon</sub>

85

max.

125

250

300  $\Omega$

April 1995 3

$-V_{DS} = 0.1 \text{ V}; V_{GS} = 0$

## P-channel silicon field-effect transistors

J174; J175; J176; J177

#### **DYNAMIC CHARACTERISTICS**

T<sub>i</sub> = 25 °C unless otherwise specified

Input capacitance, f = 1 MHz

| $V_{GS} = 10 V;$ | $V_{DS} = 0 V$ |

|------------------|----------------|

|------------------|----------------|

$$V_{GS} = V_{DS} = 0$$

Feedback capacitance, f = 1 MHz

$$V_{GS} = 10 \text{ V}; V_{DS} = 0 \text{ V}$$

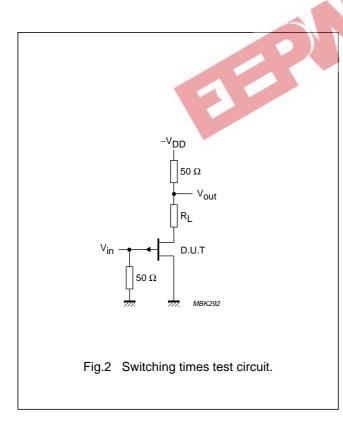

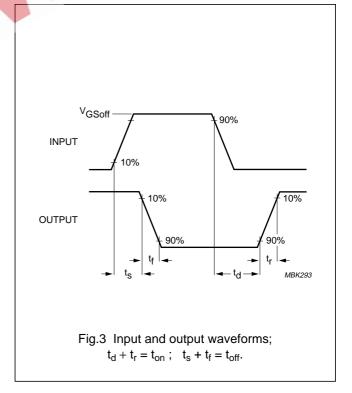

Switching times (see Fig.2 + 3)

Delay time

Rise time

Turn-on time

Storage time

Fall time

Turn-off time

Test conditions:

| $C_{is}$            | typ.   |      | 8    |      |      | рF |

|---------------------|--------|------|------|------|------|----|

| $C_{is}$            | typ.   |      | 30   |      |      | pF |

| $C_{rs}$            | typ.   | ,    | 4    |      |      | pF |

|                     |        | J174 | J175 | J176 | J177 |    |

| $t_d$               | typ.   | 2    | 5    | 15   | 20   | ns |

| t <sub>r</sub>      | typ.   | 5    | 10   | 20   | 25   | ns |

| ton                 | typ.   | 7    | 15   | 35   | 45   | ns |

| $t_s$               | typ.   | 5    | 10   | 15   | 20   | ns |

| $t_f$               | typ.   | 10   | 20   | 20   | 25   | ns |

| t <sub>off</sub>    | typ.   | 15   | 30   | 35   | 45   | ns |

| $-V_{DD}$           | n. 40  | 10   | 6    | 6    | 6    | V  |

| V <sub>GS off</sub> | 13     | 12   | 8    | 6    | 3    | V  |

| $R_L$               | 3 . 40 | 560  | 1200 | 2000 | 2900 | Ω  |

| V <sub>GS on</sub>  | 20,,   | 0    | 0    | 0    | 0    | V  |

## P-channel silicon field-effect transistors

J174; J175; J176; J177

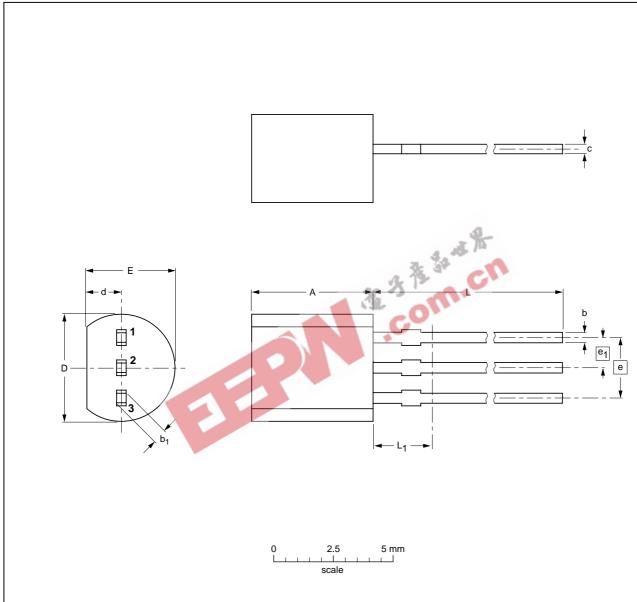

#### **PACKAGE OUTLINE**

### Plastic single-ended leaded (through hole) package; 3 leads

SOT54

#### **DIMENSIONS (mm are the original dimensions)**

|      | •          |              |                |              |            |            |            |      |                |              |                               |

|------|------------|--------------|----------------|--------------|------------|------------|------------|------|----------------|--------------|-------------------------------|

| UNIT | A          | b            | b <sub>1</sub> | С            | D          | d          | E          | е    | e <sub>1</sub> | L            | L <sub>1</sub> <sup>(1)</sup> |

| mm   | 5.2<br>5.0 | 0.48<br>0.40 | 0.66<br>0.56   | 0.45<br>0.40 | 4.8<br>4.4 | 1.7<br>1.4 | 4.2<br>3.6 | 2.54 | 1.27           | 14.5<br>12.7 | 2.5                           |

#### Note

1. Terminal dimensions within this zone are uncontrolled to allow for flow of plastic and terminal irregularities.

| OUTLINE REFERENCES |     |       |       | EUROPEAN | ISSUE DATE |            |

|--------------------|-----|-------|-------|----------|------------|------------|

| VERSION            | IEC | JEDEC | EIAJ  |          | PROJECTION | ISSUE DATE |

| SOT54              |     | TO-92 | SC-43 |          |            | 97-02-28   |

## P-channel silicon field-effect transistors

J174; J175; J176; J177

#### **DEFINITIONS**

| Data sheet status         |                                                                                                                                                                                |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | This data sheet contains target or goal specifications for product development.                                                                                                |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later.                                                                                          |

| Product specification     | This data sheet contains final product specifications.                                                                                                                         |

| Short-form specification  | The data in this specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook. |

#### Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### **Application information**

Where application information is given, it is advisory and does not form part of the specification.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.