## **Document Title**

## 128Kx36 & 256Kx18-Bit Pipelined NtRAM™

## **Revision History**

| Rev.No. | History                                                                                                                                                                                           | Draft Date     | <u>Remark</u> |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|

| 0.0     | 1. Initial document.                                                                                                                                                                              | May. 15. 2001  | Preliminary   |

| 0.1     | 1. Changed DC parameters  Icc; from 470mA to 400mA at -25, from 440mA to 360mA at -22, from 400mA to 330mA at -20, from 370mA to 310mA at -18,                                                    | June. 12. 2001 | Preliminary   |

|         | ISB; from 180mA to 160mA at -25,<br>from 170mA to 155mA at -22,<br>from 160mA to 150mA at -20,<br>from 150mA to 140mA at -18,<br>ISB1; from 100mA to 80mA                                         | A-             |               |

| 0.2     | Add x32 org. and industrial temperature                                                                                                                                                           | Aug. 11. 2001  | Preliminary   |

| 1.0     | from 150mA to 140mA at -18, ISB1; from 100mA to 80mA  1. Add x32 org. and industrial temperature  1. Final spec release 2. Changed Pin Capacitance - Cin; from 5pF to 4pF - Cout; from 7pF to 6pF | Nov. 15. 2001  | Final         |

| 2.0     | <ol> <li>Remove x32 organization.</li> <li>Remove -25/-22 speed bin</li> </ol>                                                                                                                    | Nov. 17. 2003  | Final         |

## **4Mb NtRAM Pipelined Ordering Information**

| Org.    | Part Number        | Mode      | VDD | Speed<br>FT ; Access Time(ns)<br>Pipelined ; Cycle Time(MHz) | PKG       | Temp                                       |

|---------|--------------------|-----------|-----|--------------------------------------------------------------|-----------|--------------------------------------------|

| 256Kx18 | K7N401801B-QC(I)13 | Pipelined | 3.3 | 133 MHz                                                      |           | 0                                          |

| 250KX10 | K7N401809B-QC(I)20 | Pipelined | 3.3 | 200 MHz                                                      |           | C<br>(Commercial                           |

|         | K7N403601B-QC(I)13 | Pipelined | 3.3 | 133 MHz                                                      |           | Temperature<br>Range)                      |

| 128Kx36 | K7N403609B-QC(I)20 | Pipelined | 3.3 | 200 MHz                                                      | Q:100TQFP | I:<br>(Industrial<br>Temperature<br>Range) |

#### **FEATURES**

- VDD=3.3V+0.165V/-0.165V Power Supply.

- VDDQ Supply Voltage 3.3V+0.165V/-0.165V for 3.3V I/O or 2.5V+0.4V/-0.125V for 2.5V I/O.

- Byte Writable Function.

- Enable clock and suspend operation.

- · Single READ/WRITE control pin.

- Self-Timed Write Cycle.

- Three Chip Enable for simple depth expansion with no datacontention

- · A interleaved burst or a linear burst mode.

- · Asynchronous output enable control.

- · Power Down mode.

- · TTL-Level Three-State Outputs.

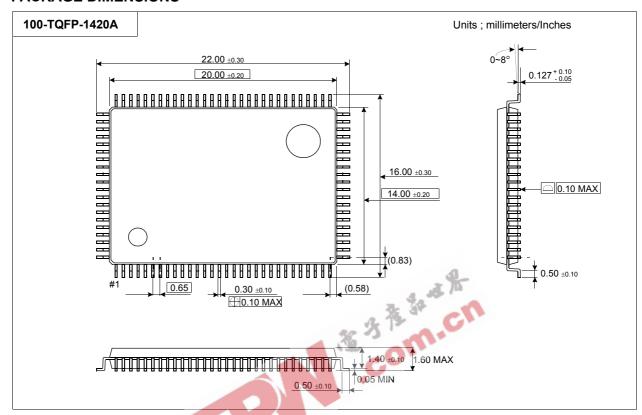

- 100-TQFP-1420A Package.

- · Operating in commeical and industrial temperature range.

#### **FAST ACCESS TIMES**

| PARAMETER                 | Symbol | -20 | Unit |

|---------------------------|--------|-----|------|

| Cycle Time                | tCYC   | 5.0 | ns   |

| Clock Access Time         | tCD    | 2.8 | ns   |

| Output Enable Access Time | tOE    | 2.8 | ns   |

#### **GENERAL DESCRIPTION**

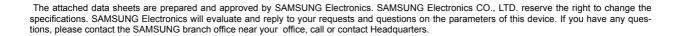

The K7N403609B and K7N401809B are 4,718,592 bits Synchronous Static SRAMs.

The NtRAMTM, or No Turnaround Random Access Memory utilizes all the bandwidth in any combination of operating cycles.

Address, data inputs, and all control signals except output enable and linear burst order are synchronized to input clock. Burst order control must be tied "High or Low".

Asynchronous inputs include the sleep mode enable(ZZ).

Output Enable controls the outputs at any given time.

Write cycles are internally self-timed and initiated by the rising edge of the clock input. This feature eliminates complex off-chip write pulse generation

and provides increased timing flexibility for incomming signals

For read cycles, pipelined SRAM output data is temporarily stored by an edge trigered output register and then released to the output bufferes at the next rising edge of clock.

The K7N403609B and K7N401809B are implemented with SAMSUNG's high performance CMOS technology and is available in 100pin TQFP packages. Multiple power and ground pins minimize ground bounce.

#### LOGIC BLOCK DIAGRAM

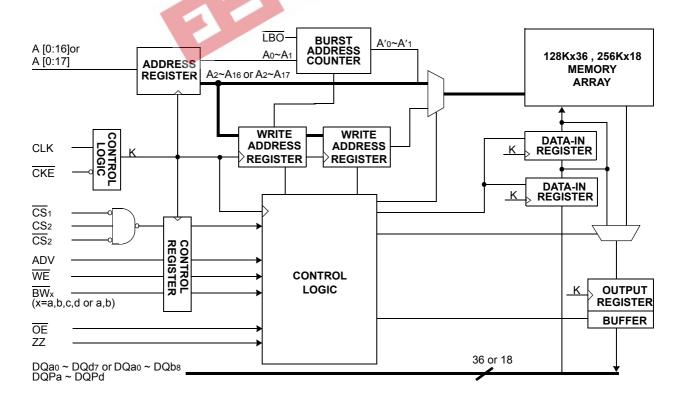

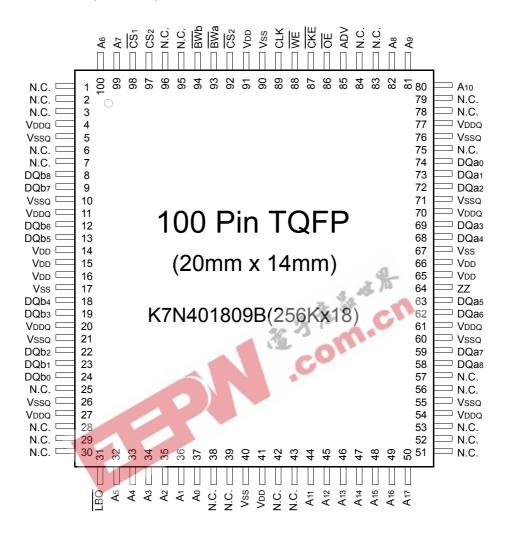

### PIN CONFIGURATION(TOP VIEW)

### **PIN NAME**

| SYMBOL                             | PIN NAME                 | TQFP PIN NO.      | SYMBOL          | PIN NAME            | TQFP PIN NO.            |

|------------------------------------|--------------------------|-------------------|-----------------|---------------------|-------------------------|

| A0 - A16                           | Address Inputs           | 32,33,34,35,36,37 | V <sub>DD</sub> | Power Supply(+3.3V) | 14,15,16,41,65,66,91    |

|                                    |                          | 44,45,46,47,48,49 | Vss             | Ground              | 17,40,67,90             |

|                                    |                          | 50,81,82,99,100   | N.C.            | No Connect          | 38,39,42,43,83,84       |

| ADV                                | Address Advance/Load     | 85                |                 |                     |                         |

| WE                                 | Read/Write Control Input | 88                | DQao~a7         | Data Inputs/Outputs | 52,53,56,57,58,59,62,63 |

| CLK                                | Clock                    | 89                | DQbo~b7         |                     | 68,69,72,73,74,75,78,79 |

| CLK<br>CKE                         | Clock Enable             | 87                | DQco~c7         |                     | 2,3,6,7,8,9,12,13       |

| CS <sub>1</sub>                    | Chip Select              | 98                | DQdo~d7         |                     | 18,19,22,23,24,25,28,29 |

| CS <sub>2</sub>                    | Chip Select              | 97                | DQPa~Pd         |                     | 51,80,1,30              |

| CS <sub>2</sub><br>CS <sub>2</sub> | Chip Select              | 92                |                 |                     |                         |

| $\overline{BW}x(x=a,b,c,d)$        | Byte Write Inputs        | 93,94,95,96       | VDDQ            | Output Power Supply | 4,11,20,27,54,61,70,77  |

| ŌĒ                                 | Output Enable            | 86                |                 | (2.5V or 3.3V)      |                         |

| ZZ<br>LBO                          | Power Sleep Mode         | 64                | Vssq            | Output Ground       | 5,10,21,26,55,60,71,76  |

| LBO                                | Burst Mode Control       | 31                |                 |                     |                         |

|                                    |                          |                   |                 |                     |                         |

Notes: 1. The pin 83 is reserved for address bit for the 8Mb NtRAM.

<sup>2.</sup> Ao and A₁ are the two least significant bits(LSB) of the address field and set the internal burst counter if burst is desired.

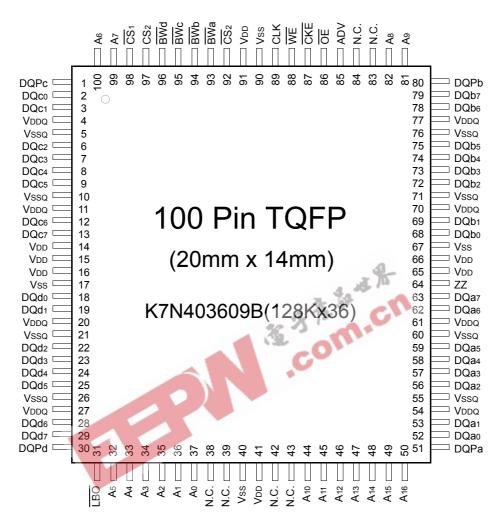

### PIN CONFIGURATION(TOP VIEW)

### **PIN NAME**

| SYMBOL                             | PIN NAME                 | TQFP PIN NO.       | SYMBOL  | PIN NAME            | TQFP PIN NO.               |

|------------------------------------|--------------------------|--------------------|---------|---------------------|----------------------------|

| A0 - A17                           | Address Inputs           | 32,33,34,35,36,37, | VDD     | Power Supply(+3.3V) | 14,15,16,41,65,66,91       |

|                                    |                          | 44,45,46,47,48,49  | Vss     | Ground              | 17,40,67,90                |

|                                    |                          | 50,80,81,82,99,100 | N.C.    | No Connect          | 1,2,3,6,7,25,28,29,30,     |

| ADV                                | Address Advance/Load     | 85                 |         |                     | 38,39,42,43,51,52,53,      |

| WE                                 | Read/Write Control Input | 88                 |         |                     | 56,57,75,78,79,83,84       |

| CLK                                | Clock                    | 89                 |         |                     | 95,96                      |

| CLK<br>CKE                         | Clock Enable             | 87                 |         |                     |                            |

| CS <sub>1</sub>                    | Chip Select              | 98                 | DQao~a8 | Data Inputs/Outputs | 58,59,62,63,68,69,72,73,74 |

| CS <sub>2</sub><br>CS <sub>2</sub> | Chip Select              | 97                 | DQbo~b8 |                     | 8,9,12,13,18,19,22,23,24   |

| CS <sub>2</sub>                    | Chip Select              | 92                 |         |                     |                            |

| $\overline{BW}x(x=a,b)$            | Byte Write Inputs        | 93,94              |         |                     |                            |

| ŌE                                 | Output Enable            | 86                 | VDDQ    | Output Power Supply | 4,11,20,27,54,61,70,77     |

| ZZ                                 | Power Sleep Mode         | 64                 |         | (2.5V or 3.3V)      |                            |

| ZZ<br>LBO                          | Burst Mode Control       | 31                 | Vssq    | Output Ground       | 5,10,21,26,55,60,71,76     |

|                                    |                          |                    |         |                     |                            |

Notes: 1. The pin 83 is reserved for address bit for the 8Mb NtRAM.

2. Ao and A1 are the two least significant bits(LSB) of the address field and set the internal burst counter if burst is desired.

#### **FUNCTION DESCRIPTION**

The K7N403609B and K7N401809B are NtRAM™ designed to sustain 100% bus bandwidth by eliminating turnaround cycle when there is transition from Read to Write, or vice versa.

All inputs (with the exception of  $\overline{OE}$ ,  $\overline{LBO}$  and ZZ) are synchronized to rising clock edges.

All read, write and deselect cycles are initiated by the ADV input. Subsequent burst addresses can be internally generated by the burst advance pin (ADV). ADV should be driven to Low once the device has been deselected in order to load a new address for next operation.

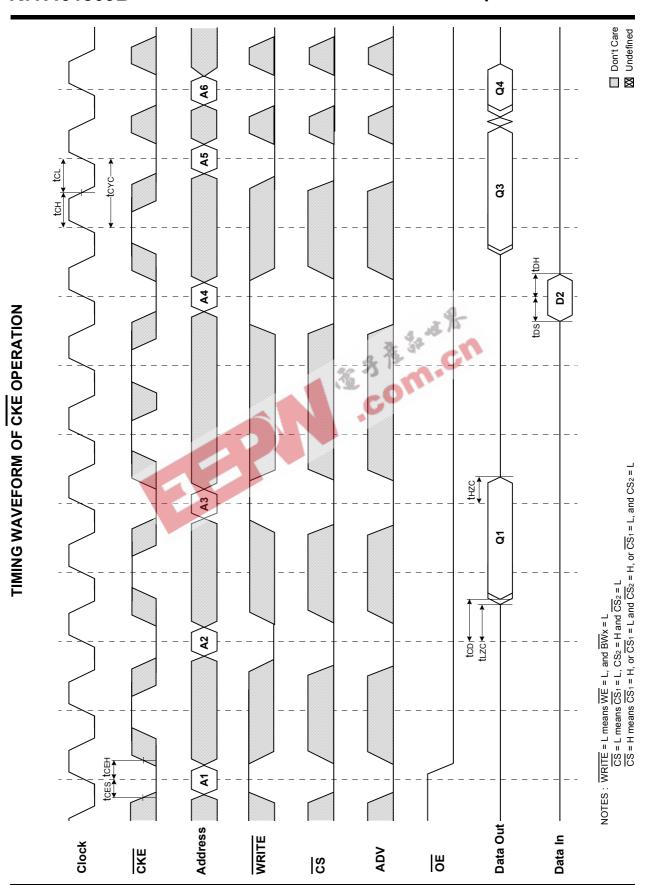

Clock Enable( $\overline{\text{CKE}}$ ) pin allows the operation of the chip to be suspended as long as necessary. When  $\overline{\text{CKE}}$  is high, all synchronous inputs are ignored and the internal device registers will hold their previous values.

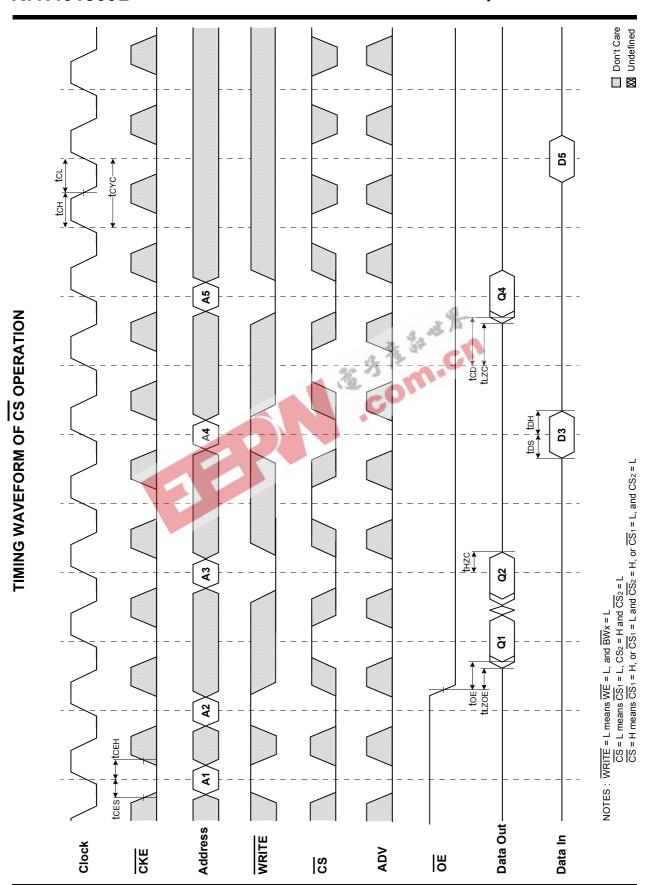

NtRAM™ latches external address and initiates a cycle, when  $\overline{CKE}$ , ADV are driven to low and all three chip enables( $\overline{CS}_1$ ,  $\overline{CS}_2$ ) are active .

Output Enable( $\overline{OE}$ ) can be used to disable the output at any given time.

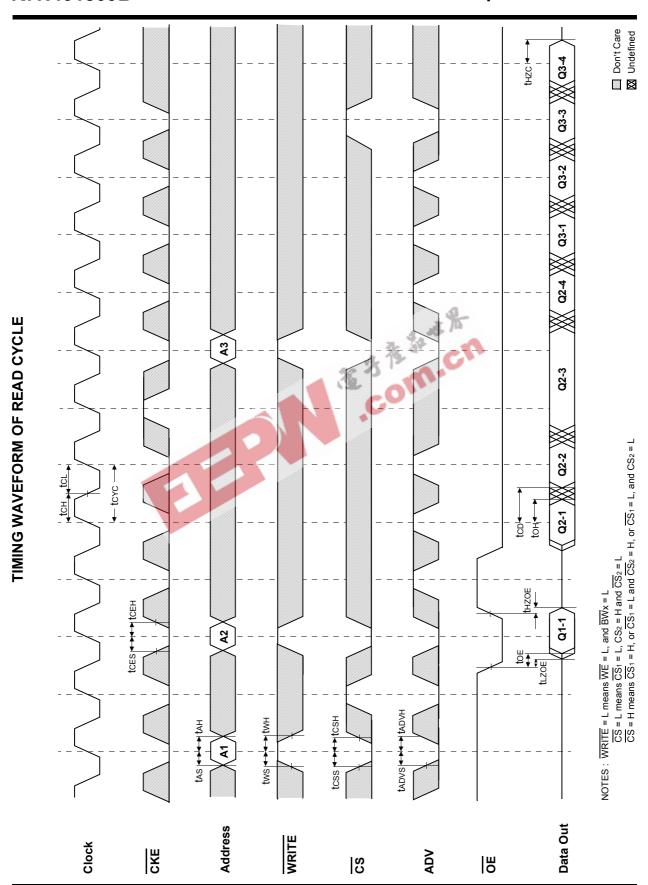

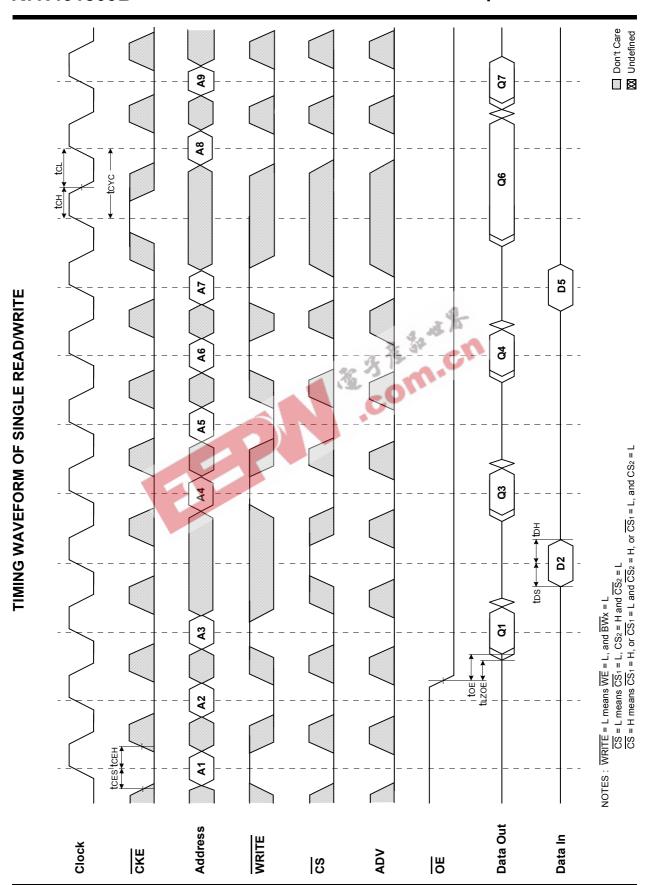

Read operation is initiated when at the rising edge of the clock, the address presented to the address inputs are latched in the address register,  $\overline{CKE}$  is driven low, all three chip enables( $\overline{CS}_1$ ,  $\overline{CS}_2$ ) are active, the write enable input signals  $\overline{WE}$  are driven high, and ADV driven low. The internal array is read between the first rising edge and the second rising edge of the clock and the data is latched in the output register. At the second clock edge the data is driven out of the SRAM. Also during read operation  $\overline{OE}$  must be driven low for the device to drive out the requested data.

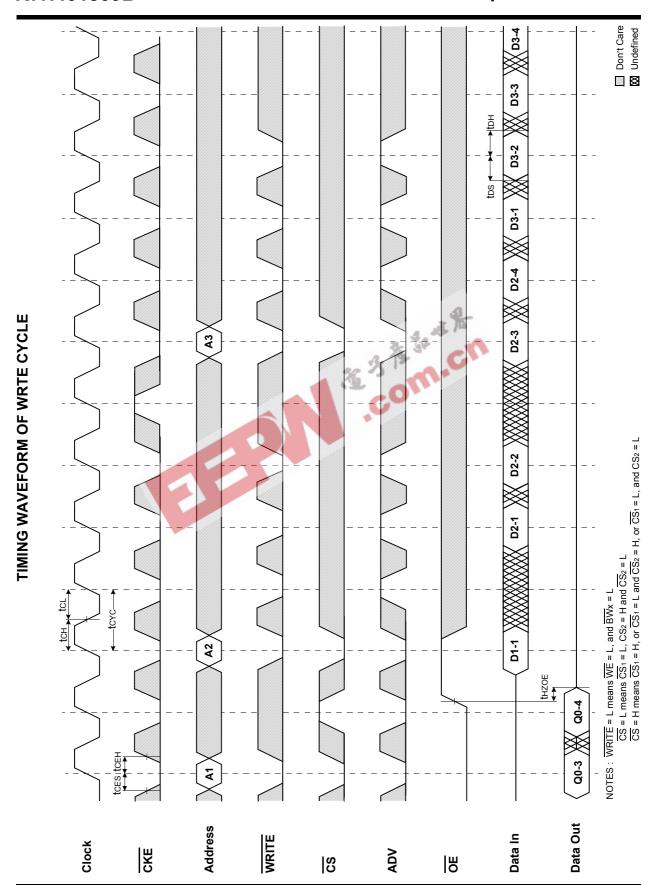

Write operation occurs when  $\overline{\text{WE}}$  is driven low at the rising edge of the clock.  $\overline{\text{BW}}[\text{d:a}]$  can be used for byte write operation. The pipelined NtRAM<sup>TM</sup> uses a late-late write cycle to utilize 100% of the bandwidth.

At the first rising edge of the clock, WE and address are registered, and the data associated with that address is required two cycle later.

Subsequent addresses are generated by ADV High for the burst access as shown below. The starting point of the burst seguence is provided by the external address. The burst address counter wraps around to its initial state upon completion.

The burst sequence is determined by the state of the LBO pin. When this pin is low, linear burst sequence is selected. And when this pin is high, Interleaved burst sequence is selected.

During normal operation, ZZ must be driven low. When ZZ is driven high, the SRAM will enter a Power Sleep Mode after 2 cycles. At this time, internal state of the SRAM is preserved. When ZZ returns to low, the SRAM normally operates after 2 cycles of wake up time.

#### **BURST SEQUENCE TABLE**

(Interleaved Burst, LBO=High)

| LBO PIN | HIGH         | Case 1     |                | Case 2     |                | Case 3     |                | Case 4     |                |

|---------|--------------|------------|----------------|------------|----------------|------------|----------------|------------|----------------|

| LBO FIN | IIIGII       | <b>A</b> 1 | A <sub>0</sub> |

| Fii     | rst Address  | 0          | 0              | 0          | 1              | 1          | 0              | 1          | 1              |

|         |              | 0          | 1              | 0          | 0              | 1          | 1              | 1          | 0              |

|         | $\downarrow$ | 1          | 0              | 1          | 1              | 0          | 0              | 0          | 1              |

| Fou     | urth Address | 1          | 1              | 1          | 0              | 0          | 1              | 0          | 0              |

Note: 1. LBO pin must be tied to High or Low, and Floating State must not be allowed.

(Linear Burst, LBO=Low)

| LBO PIN        | LOW          | Case 1     |                | Case 2     |                | Case 3     |                | Case 4     |                |

|----------------|--------------|------------|----------------|------------|----------------|------------|----------------|------------|----------------|

| LBOTIN         | LOW          | <b>A</b> 1 | A <sub>0</sub> |

| First Address  |              | 0          | 0              | 0          | 1              | 1          | 0              | 1          | 1              |

|                |              | 0          | 1              | 1          | 0              | 1          | 1              | 0          | 0              |

|                | $\downarrow$ | 1          | 0              | 1          | 1              | 0          | 0              | 0          | 1              |

| Fourth Address |              | 1          | 1              | 0          | 0              | 0          | 1              | 1          | 0              |

Note: 1. LBO pin must be tied to High or Low, and Floating State must not be allowed.

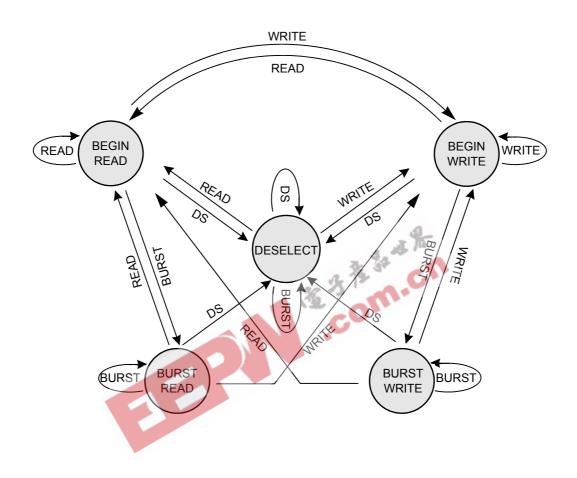

### STATE DIAGRAM FOR NtRAM™

| COMMAND | ACTION                                         |

|---------|------------------------------------------------|

| DS      | DESELECT                                       |

| READ    | BEGIN READ                                     |

| WRITE   | BEGIN WRITE                                    |

| BURST   | BEGIN READ<br>BEGIN WRITE<br>CONTINUE DESELECT |

Notes: 1. An IGNORE CLOCK EDGE cycle is not shown is the above diagram. This is because CKE HIGH only blocks the clock(CLK) input and does not change the state of the device.

2. States change on the rising edge of the clock(CLK)

### **TRUTH TABLES**

### **SYNCHRONOUS TRUTH TABLE**

| CS <sub>1</sub> | CS <sub>2</sub> | CS <sub>2</sub> | ADV | WE | BWx | OE | CKE | CLK      | ADDRESS ACCESSED | OPERATION                  |

|-----------------|-----------------|-----------------|-----|----|-----|----|-----|----------|------------------|----------------------------|

| Н               | Х               | Χ               | L   | Χ  | Х   | Χ  | L   | <b>↑</b> | N/A              | Not Selected               |

| Х               | L               | Χ               | L   | Χ  | Х   | Χ  | L   | <b>↑</b> | N/A              | Not Selected               |

| Х               | Х               | Н               | L   | Χ  | Х   | Χ  | L   | <b>↑</b> | N/A              | Not Selected               |

| Х               | Х               | Χ               | Н   | Χ  | Х   | Χ  | L   | <b>↑</b> | N/A              | Not Selected Continue      |

| L               | Н               | L               | L   | Н  | Х   | L  | L   | <b>↑</b> | External Address | Begin Burst Read Cycle     |

| Х               | Х               | Х               | Н   | Х  | Х   | L  | L   | <b>↑</b> | Next Address     | Continue Burst Read Cycle  |

| L               | Н               | L               | L   | Н  | Х   | Н  | L   | <b>↑</b> | External Address | NOP/Dummy Read             |

| Х               | Х               | Х               | Н   | Х  | Х   | Н  | L   | <b>↑</b> | Next Address     | Dummy Read                 |

| L               | Н               | L               | L   | L  | L   | Х  | L   | <b>↑</b> | External Address | Begin Burst Write Cycle    |

| Х               | Х               | Х               | Н   | Х  | L   | Х  | L   | <b>↑</b> | Next Address     | Continue Burst Write Cycle |

| L               | Н               | L               | L   | L  | Н   | Х  | L   | <b>↑</b> | N/A              | NOP/Write Abort            |

| Х               | Х               | Х               | Н   | Х  | Н   | Х  | L   | <b>↑</b> | Next Address     | Write Abort                |

| Х               | Х               | Х               | Х   | Х  | Х   | Х  | Н   | <b>↑</b> | Current Address  | Ignore Clock               |

- 3. A continue deselect cycle can only be enterd if a deselect cycle is executed first.

4. WRITE = L means Write operation in WRITE TRUTH TABLE.

WRITE = H means Read operation in WRITE TRUTH TABLE.

5. Operation finally depends on status of asynchronous input pins(ZZ and OE).

## WRITE TRUTH TABLE(x36)

| WE | BWa | BWb | BWc | BWd | OPERATION       |

|----|-----|-----|-----|-----|-----------------|

| Н  | X   | X   | X   | Х   | READ            |

| L  | L   | H   | Н   | Н   | WRITE BYTE a    |

| L  | Н   | L   | Н   | Н   | WRITE BYTE b    |

| L  | Н   | Н   | L   | Н   | WRITE BYTE c    |

| L  | Н   | Н   | Н   | L   | WRITE BYTE d    |

| L  | L   | L   | L   | L   | WRITE ALL BYTEs |

| L  | Н   | Н   | Н   | Н   | WRITE ABORT/NOP |

Notes: 1. X means "Don't Care".

2. All inputs in this table must meet setup and hold time around the rising edge of CLK(↑).

### WRITE TRUTH TABLE(x18)

| WE | BWa | BWb | OPERATION       |  |

|----|-----|-----|-----------------|--|

| Н  | X   | X   | READ            |  |

| L  | L   | Н   | WRITE BYTE a    |  |

| L  | Н   | L   | WRITE BYTE b    |  |

| L  | L   | L   | WRITE ALL BYTEs |  |

| L  | Н   | Н   | WRITE ABORT/NOP |  |

Notes: 1. X means "Don't Care".

2. All inputs in this table must meet setup and hold time around the rising edge of  $CLK(\uparrow)$ .

### **ASYNCHRONOUS TRUTH TABLE**

| OPERATION  | ZZ | OE | I/O STATUS  |

|------------|----|----|-------------|

| Sleep Mode | Н  | Х  | High-Z      |

| Read       | L  | L  | DQ          |

| Redu       | L  | Н  | High-Z      |

| Write      | L  | Х  | Din, High-Z |

| Deselected | L  | Х  | High-Z      |

#### Notes

- 1. X means "Don't Care".

- 2. Sleep Mode means power Sleep Mode of which stand-by current does not depend on cycle time.

- 3. Deselected means power Sleep Mode of which stand-by current depends on cycle time.

#### **ABSOLUTE MAXIMUM RATINGS\***

| PARAMETER                                                                       |            | SYMBOL | RATING           | UNIT |

|---------------------------------------------------------------------------------|------------|--------|------------------|------|

| Voltage on VDD Supply Relative to Vss<br>Voltage on VDDQ Supply Relative to Vss |            | Vdd    | -0.3 to 4.6      | V    |

|                                                                                 |            | VDDQ   | VDD              | V    |

| Voltage on Input Pin Relative to Vss                                            |            | Vin    | -0.3 to VDD+0.3  | V    |

| Voltage on I/O Pin Relative to Vss                                              |            | Vio    | -0.3 to VDDQ+0.3 | V    |

| Power Dissipation                                                               |            | PD     | 1.4              | W    |

| Storage Temperature                                                             |            | Тѕтѕ   | -65 to 150       | °C   |

| Operating Temperature                                                           | Commercial | Topr   | 0 to 70          | °C   |

| Operating Temperature                                                           | Industrial | Topr   | -40 to 85        | °C   |

| Storage Temperature Range Under Bias                                            |            | TBIAS  | -10 to 85        | °C   |

<sup>\*</sup>Note: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **OPERATING CONDITIONS at 3.3V I/O** $(0^{\circ}C \le TA \le 70^{\circ}C)$

| PARAMETER      | 1 | SYMBOL | MIN   | Тур. | MAX   | UNIT |

|----------------|---|--------|-------|------|-------|------|

| Supply Voltage |   | VDD    | 3.135 | 3.3  | 3.465 | V    |

| Supply Voltage |   | VDDQ   | 3.135 | 3.3  | 3.465 | V    |

| Ground         |   | Vss    | 0     | 0    | 0     | V    |

<sup>\*</sup> The above parameters are also guaranteed at industrial temperature range.

### **OPERATING CONDITIONS at 2.5V I/O** $(0^{\circ}C \le TA \le 70^{\circ}C)$

| PARAMETER      | SYMBOL | MIN   | Тур. | MAX   | UNIT |

|----------------|--------|-------|------|-------|------|

| Supply Valtage | VDD    | 3.135 | 3.3  | 3.465 | V    |

| Supply Voltage | VDDQ   | 2.375 | 2.5  | 2.9   | V    |

| Ground         | Vss    | 0     | 0    | 0     | V    |

<sup>\*</sup> The above parameters are also guaranteed at industrial temperature range.

## CAPACITANCE\*(TA=25°C, f=1MHz)

| PARAMETER          | SYMBOL | TEST CONDITION      | TYP | MAX | UNIT |

|--------------------|--------|---------------------|-----|-----|------|

| Input Capacitance  | Cin    | V <sub>IN</sub> =0V | -   | 4   | pF   |

| Output Capacitance | Соит   | Vout=0V             | -   | 6   | pF   |

<sup>\*</sup>Note: Sampled not 100% tested.

## DC ELECTRICAL CHARACTERISTICS(VDD=3.3V+0.165V/-0.165V, TA=0°C to +70°C)

| PARAMETER                        | SYMBOL                                                                              | TEST CONDITIONS                                                                              |      | MIN   | MAX       | UNIT | NOTES |

|----------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|-------|-----------|------|-------|

| Input Leakage Current(except ZZ) | lıL                                                                                 | VDD=Max ; VIN=Vss to VDD                                                                     |      | -2    | +2        | μА   |       |

| Output Leakage Current           | lol                                                                                 | Output Disabled,                                                                             |      | -2    | +2        | μА   |       |

| Operating Current                | Icc                                                                                 | VDD=Max , IOUT=0mA<br>ZZ≤VIL , Cycle Time ≥ tcyc Min                                         |      | -     | 330       | mA   | 1,2   |

|                                  | ISB                                                                                 | Device deselected, Iout=0mA, ZZ $\leq$ VIL, f=Max, All Inputs $\leq$ 0.2V or $\geq$ VDD-0.2V | -20  | -     | 150       | mA   |       |

| Standby Current                  | Tent Device deselected, lout=0mA, ZZ≤0.2V, f=0, All Inputs=fixed (VDD-0.2V or 0.2V) |                                                                                              | -    | 80    | mA        |      |       |

|                                  | ISB2                                                                                | Device deselected, lout=0mA, ZZ≥Vdd-0.2V, f=Max, All Inputs≤VlL or ≥VlH                      |      | -     | 50        | mA   |       |

| Output Low Voltage(3.3V I/O)     | Vol                                                                                 | IoL=8.0mA                                                                                    |      | -     | 0.4       | V    |       |

| Output High Voltage(3.3V I/O)    | Vон                                                                                 | Iон=-4.0mA                                                                                   |      | 2.4   | -         | V    |       |

| Output Low Voltage(2.5V I/O)     | Vol                                                                                 | IoL=1.0mA                                                                                    |      | -     | 0.4       | V    |       |

| Output High Voltage(2.5V I/O)    | Vон                                                                                 | Iон=-1.0mA                                                                                   |      | 2.0   | -         | V    |       |

| Input Low Voltage(3.3V I/O)      | VIL                                                                                 |                                                                                              |      | -0.3* | 0.8       | V    |       |

| Input High Voltage(3.3V I/O)     | VIH                                                                                 |                                                                                              | 4    | 2.0   | VDD+0.3** | V    | 3     |

| Input Low Voltage(2.5V I/O)      | VIL                                                                                 | 4                                                                                            | 3,35 | -0.3* | 0.7       | V    |       |

| Input High Voltage(2.5V I/O)     | VIH                                                                                 | . %.                                                                                         | 34   | 1.7   | VDD+0.3** | V    | 3     |

Notes: 1.The above parameters are also guaranteed at industrial temperature range.

2. Reference AC Operating Conditions and Characteristics for input and timing.

Data states are all zero.

In Case of I/O Pins, the Max. V<sub>IH</sub>=V<sub>DDQ</sub>+0.3V

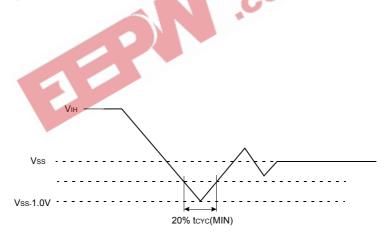

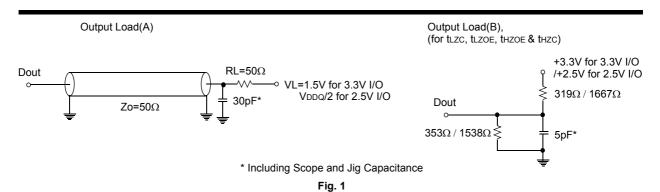

## **TEST CONDITIONS**

(VDD=3.3V+0.165V/-0.165V,VDDQ=3.3V+0.165/-0.165V, VDDQ=3.3V+0.165V,VDDQ=2.5V+0.4V/-0.125V, TA=0to70°C)

| PARAMETER                                                     | VALUE      |

|---------------------------------------------------------------|------------|

| Input Pulse Level(for 3.3V I/O)                               | 0 to 3.0V  |

| Input Pulse Level(for 2.5V I/O)                               | 0 to 2.5V  |

| Input Rise and Fall Time(Measured at 20% to 80% for 3.3V I/O) | 1.0V/ns    |

| Input Rise and Fall Time(Measured at 20% to 80% for 2.5V I/O) | 1.0V/ns    |

| Input and Output Timing Reference Levels for 3.3V I/O         | 1.5V       |

| Input and Output Timing Reference Levels for 2.5V I/O         | VDDQ/2     |

| Output Load                                                   | See Fig. 1 |

<sup>\*</sup> The above parameters are also guaranteed at industrial temperature range.

AC TIMING CHARACTERISTICS(VDD=3.3V+0.165V/-0.165V, TA=0°C to +70°C)

| DADAMETER                             | Complete I | _   | LIMIT |       |

|---------------------------------------|------------|-----|-------|-------|

| PARAMETER                             | Symbol     | Min | Max   | UNIT  |

| Cycle Time                            | tCYC       | 5.0 | -     | ns    |

| Clock Access Time                     | tCD        | 0 - | 2.8   | ns    |

| Output Enable to Data Valid           | tOE        | -0  | 2.8   | ns    |

| Clock High to Output Low-Z            | tLZC (     | 1.0 | -     | ns    |

| Output Hold from Clock High           | tOH        | 1.0 | -     | ns    |

| Output Enable Low to Output Low-Z     | tLZOE      | 0   | -     | ns    |

| Output Enable High to Output High-Z   | tHZOE      | -   | 2.8   | ns    |

| Clock High to Output High-Z           | tHZC       | -   | 2.8   | ns    |

| Clock High Pulse Width                | tCH        | 2.0 | -     | ns    |

| Clock Low Pulse Width                 | tCL        | 2.0 | -     | ns    |

| Address Setup to Clock High           | tAS        | 1.2 | -     | ns    |

| CKE Setup to Clock High               | tCES       | 1.2 | -     | ns    |

| Data Setup to Clock High              | tDS        | 1.2 | -     | ns    |

| Write Setup to Clock High (WE, BWX)   | tWS        | 1.2 | -     | ns    |

| Address Advance Setup to Clock High   | tADVS      | 1.2 | -     | ns    |

| Chip Select Setup to Clock High       | tCSS       | 1.2 | -     | ns    |

| Address Hold from Clock High          | tAH        | 0.4 | -     | ns    |

| CKE Hold from Clock High              | tCEH       | 0.4 | -     | ns    |

| Data Hold from Clock High             | tDH        | 0.4 | -     | ns    |

| Write Hold from Clock High (WE, BWEX) | tWH        | 0.4 | -     | ns    |

| Address Advance Hold from Clock High  | tADVH      | 0.4 | -     | ns    |

| Chip Select Hold from Clock High      | tCSH       | 0.4 | -     | ns    |

| ZZ High to Power Down                 | tPDS       | 2   | -     | cycle |

| ZZ Low to Power Up                    | tPUS       | 2   | -     | cycle |

Notes: 1. The above parameters are also guaranteed at industrial temperature range.

5. To avoid bus contention, At a given voltage and temperature tLzc is more than tHzc. The specs as shown do not imply bus contention because tLzc is a Min. parameter that is worst case at totally different test conditions (0°C,3.465V) than tHzc, which is a Max. parameter(worst case at 70°C,3.135V) It is not possible for two SRAMs on the same board to be at such different voltage and temperature.

<sup>2.</sup> All address inputs must meet the specified setup and hold times for all rising clock(CLK) edges when ADV is sampled low and  $\overline{\text{CS}}$  is sampled

low. All other synchronous inputs must meet the specified setup and hold times whenever this device is chip selected.

3. Chip selects must be valid <u>at ea</u>ch rising edge of CLK(when ADV is Low) to remain enabled.

4. A write cycle is defined by WE low having been registered into the device at ADV Low, A Read cycle is defined by WE High with ADV Low, Both cases must meet setup and hold times.

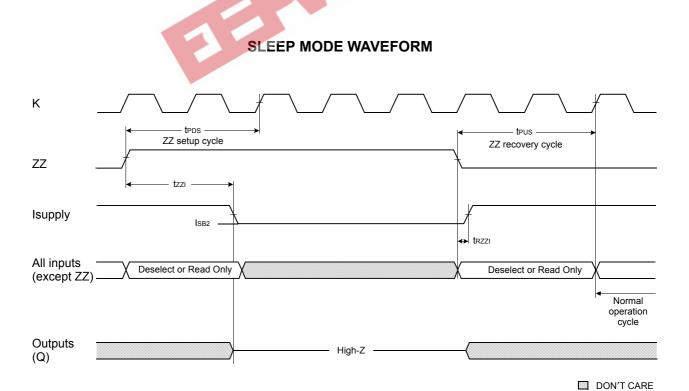

### **SLEEP MODE**

SLEEP MODE is a low current, power-down mode in which the device is deselected and current is reduced to IsB2. The duration of SLEEP MODE is dictated by the length of time the ZZ is in a High state.

After entering SLEEP MODE, all inputs except ZZ become disabled and all outputs go to High-Z

The ZZ pin is an asynchronous, active high input that causes the device to enter SLEEP MODE.

When the ZZ pin becomes a logic High, ISB2 is guaranteed after the time tzzı is met. Any operation pending when entering SLEEP MODE is not guaranteed to successful complete. Therefore, SLEEP MODE (READ or WRITE) must not be initiated until valid pending operations are completed. similarly, when exiting SLEEP MODE during tpus, only a DESELECT or READ cycle should be given while the SRAM is transitioning out of SLEEP MODE.

### **SLEEP MODE ELECTRICAL CHARACTERISTICS**

| DESCRIPTION                       | CONDITIONS   | SYMBOL | MIN | MAX | UNITS |

|-----------------------------------|--------------|--------|-----|-----|-------|

| Current during SLEEP MODE         | $ZZ \ge VIH$ | ISB2   |     | 10  | mA    |

| ZZ active to input ignored        | 38.          | tPDS   | 2   |     | cycle |

| ZZ inactive to input sampled      | a Ti         | tpus   | 2   |     | cycle |

| ZZ active to SLEEP current        | 36           | tzzı   |     | 2   | cycle |

| ZZ inactive to exit SLEEP current |              | trzzi  | 0   |     |       |

### **PACKAGE DIMENSIONS**