# **Document Title**

### 512Kx36 & 1Mx18 Synchronous Pipelined SRAM

# **Revision History**

| <u>Rev. No.</u> | <u>History</u>                                                                                                                                                                                                                                                                                                                           | Draft Date | <u>Remark</u> |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|

| Rev. 0.0        | - Initial Document                                                                                                                                                                                                                                                                                                                       | Dec. 2001  | Advance       |

| Rev. 0.1        | - Absolute maximum ratings are changed<br>VDD : 2.815 -> 3.13<br>VDDQ : 2.815 -> 2.4<br>VTERM : 2.815 -> VDDQ+0.5 (2.4V MAX)                                                                                                                                                                                                             | Oct. 2002  | Advance       |

|                 | - Recommended DC operating conditions are changed<br>VREF / VCM-CLK : 0.68 - > 0.6, 0.95 - > 0.9                                                                                                                                                                                                                                         |            |               |

|                 | - DC characteristics is changed<br>IsBzz : 150 - > 128                                                                                                                                                                                                                                                                                   |            |               |

|                 | - AC Characteristics are changed<br>Tavkh / Tdvkh / Twvkh / Tsvkh : 0.4 / 0.5 / 0.5 - > 0.3 / 0.3 / 0.3<br>Tkhax / Tkhdx / Tkhwx / Tkhsx : 0.5 / 0.5 / 0.5 - > 0.5 / 0.6 / 0.6                                                                                                                                                           | F          |               |

| Rev. 0.2        | <ul> <li>TAVKH / TDVKH / TWVKH / TSVKH : 0.4 / 0.5 / 0.5 -&gt; 0.3 / 0.3 / 0.3<br/>TKHAX / TKHDX / TKHWX / TKHSX : 0.5 / 0.5 / 0.5 -&gt; 0.5 / 0.6 / 0.6</li> <li>Recommended DC operating condition is changed<br/>Max VDIF-CLK : VDDQ+0.3 -&gt; VDDQ+0.6</li> <li>Correct typo<br/>VDD -&gt; VDDQ: in MODE CONTROL at page4</li> </ul> | Jan. 2003  | Advance       |

| Rev. 0.3        | - Correct typo<br>VDD -> VDDQ: in MODE CONTROL at page4                                                                                                                                                                                                                                                                                  | Sep. 2003  | Final         |

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions on the parameters of this device. If you have any questions, please contact the SAMSUNG branch office near your office, call or cortact Headquarters.

# 512Kx36 & 1Mx18 Synchronous Pipelined SRAM

# FEATURES

- 512Kx36 or 1Mx18 Organizations.

- 2.5V Core/1.5V Output Power Supply (1.9V max VDDQ).

- HSTL Input and Output Levels.

- Differential, HSTL Clock Inputs K,  $\overline{K}$ .

- Synchronous Read and Write Operation

- Registered Input and Registered Output

- Internal Pipeline Latches to Support Late Write.

- Byte Write Capability(four byte write selects, one for each 9bits)

- Synchronous or Asynchronous Output Enable.

- Power Down Mode via ZZ Signal.

- Programmable Impedance Output Drivers.

- JTAG 1149.1 Compatible Test Access port.

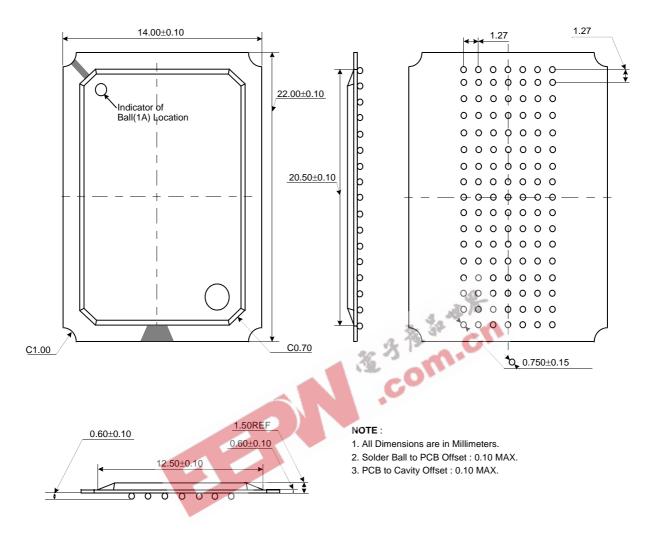

- 119(7x17)Pin Ball Grid Array Package(14mmx22mm).

| Organization | Part Number     | Maximum<br>Frequency | Access<br>Time |

|--------------|-----------------|----------------------|----------------|

| 512Kx36      | K7P163666A-HC33 | 333MHz               | 1.5            |

|              | K7P163666A-HC30 | 300MHz               | 1.6            |

|              | K7P163666A-HC25 | 250MHz               | 2.0            |

|              | K7P161866A-HC33 | 333MHz               | 1.5            |

| 1Mx18        | K7P161866A-HC30 | 300MHz               | 1.6            |

|              | K7P161866A-HC25 | 250MHz               | 2.0            |

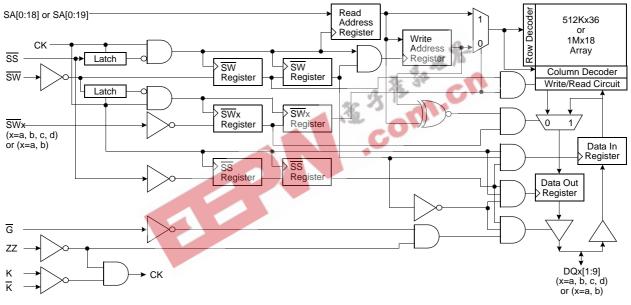

# FUNCTIONAL BLOCK DIAGRAM

## **PIN DESCRIPTION**

| Pin Name | Pin Description                 | Pin Name | Pin Description                           |

|----------|---------------------------------|----------|-------------------------------------------|

| К, К     | Differential Clocks             | Vref     | HSTL Input Reference Voltage              |

| SAn      | Synchronous Address Input       | M1, M2   | Read Protocol Mode Pins (M1=Vss, M2=VDDQ) |

| DQn      | Bi-directional Data Bus         | G        | Asynchronous Output Enable                |

| SW       | Synchronous Global Write Enable | SS       | Synchronous Select                        |

| SWa      | Synchronous Byte a Write Enable | тск      | JTAG Test Clock                           |

| SWb      | Synchronous Byte b Write Enable | TMS      | JTAG Test Mode Select                     |

| SWc      | Synchronous Byte c Write Enable | TDI      | JTAG Test Data Input                      |

| SWd      | Synchronous Byte d Write Enable | TDO      | JTAG Test Data Output                     |

| ZZ       | Asynchronous Power Down         | ZQ       | Output Driver Impedance Control           |

| Vdd      | Core Power Supply               | Vss      | GND                                       |

| Vddq     | Output Power Supply             | NC       | No Connection                             |

# PACKAGE PIN CONFIGURATIONS(TOP VIEW)

## K7P163666A(512Kx36)

|             | 1      | 2            | 3            | 4            | 5     | 6               | 7    |

|-------------|--------|--------------|--------------|--------------|-------|-----------------|------|

| А           | Vddq   | SA13         | <b>SA</b> 10 | NC           | SA7   | SA4             | Vddq |

| В           | NC     | SA18         | SA9          | NC           | SA8   | SA17            | NC   |

| С           | NC     | <b>SA</b> 12 | SA11         | Vdd          | SA6   | SA5             | NC   |

| D           | DQc8   | DQc9         | Vss          | ZQ           | Vss   | DQb9            | DQb8 |

| Е           | DQc6   | DQc7         | Vss          | SS           | Vss   | DQb7            | DQb6 |

| F           | Vddq   | DQc5         | Vss          | G            | Vss   | DQb5            | Vddq |

| G           | DQc3   | DQc4         | SWc          | NC           | SWb   | DQb4            | DQb3 |

| н           | DQc1   | DQc2         | Vss          | NC           | Vss   | DQb2            | DQb1 |

| J           | Vddq   | Vdd          | Vref         | Vdd          | Vref  | Vdd             | Vddq |

| к           | DQd1   | DQd2         | Vss          | к            | Vss   | DQa2            | DQa1 |

| L           | DQd3   | DQd4         | SWd          | ĸ            | SWa   | DQa4            | DQa3 |

| м           | Vddq   | DQd₅         | Vss          | SW           | Vss   | DQa5            | Vddq |

| N           | DQd6   | DQd7         | Vss          | SA0          | Vss   | DQa7            | DQa6 |

| Р           | DQd8   | DQd9         | Vss          | SA1          | Vss 🔬 | DQa9            | DQa8 |

| R           | NC     | SA15         | M1           | Vdd          | M2    | SA <sub>2</sub> | NC   |

| т           | NC     | NC           | SA14         | <b>SA</b> 16 | SA3   | NC              | ZZ   |

| U           | Vddq   | TMS          | TDI          | тск          | TDO   | NC              | Vddq |

| K7P161866A( | 1Mx18) |              |              | C            | our   |                 |      |

#### K7P161866A(1Mx18)

|   | - /  | 1    |            |                 |      |      | 1    |

|---|------|------|------------|-----------------|------|------|------|

|   | 1    | 2    | 3          | 4               | 5    | 6    | 7    |

| Α | Vddq | SA13 | SA10       | NC              | SA7  | SA4  | Vddq |

| В | NC   | SA19 | SA9        | NC              | SA8  | SA17 | NC   |

| С | NC   | SA12 | SA11       | Vdd             | SA6  | SA5  | NC   |

| D | DQb1 | NC   | Vss        | ZQ              | Vss  | DQa9 | NC   |

| Е | NC   | DQb2 | Vss        | SS              | Vss  | NC   | DQa8 |

| F | Vddq | NC   | Vss        | G               | Vss  | DQa7 | Vddq |

| G | NC   | DQb3 | SWb        | NC              | NC   | NC   | DQa6 |

| н | DQb4 | NC   | Vss        | NC              | Vss  | DQa5 | NC   |

| J | Vddq | Vdd  | Vref       | Vdd             | Vref | Vdd  | Vddq |

| к | NC   | DQb₅ | Vss        | к               | Vss  | NC   | DQa4 |

| L | DQb6 | NC   | NC         | ĸ               | SWa  | DQa3 | NC   |

| м | Vddq | DQb7 | Vss        | SW              | Vss  | NC   | Vddq |

| N | DQb8 | NC   | Vss        | SA <sub>0</sub> | Vss  | DQa2 | NC   |

| Р | NC   | DQb9 | Vss        | SA1             | Vss  | NC   | DQa1 |

| R | NC   | SA15 | <b>M</b> 1 | Vdd             | M2   | SA2  | NC   |

| Т | NC   | SA18 | SA14       | NC              | SA3  | SA16 | ZZ   |

| U | Vddq | TMS  | TDI        | тск             | TDO  | NC   | Vddq |

### FUNCTION DESCRIPTION

The K7P163666A and K7P161866A are 18,874,368 bit Synchronous Pipeline Mode SRAM. It is organized as 524,288 words of 36 bits(or 1,048,576 words of 18 bits)and is implemented in SAMSUNGs advanced CMOS technology.

Single differential HSTL level K clocks are used to initiate the read/write operation and all internal operations are self-timed. At the updated from output registers edge of the next rising edge of the K clock. An internal write data buffer allows write data to follow one cycle after addresses and controls. The package is 119(7x17) Ball Grid Array with balls on a 1.27mm pitch.

#### **Read Operation**

During reads, the address is registered during the frist clock edge, the internal array is read between this first edge and the second edge, and data is captured in the output register and driven to the CPU during the second clock edge.  $\overline{SS}$  is driven low during this cycle, signaling that the SRAM should drive out the data.

During consecutive read cycles where the address is the same, the data output must be held constant without any glitches. This characteristic is because the SRAM will be read by devices that will operate slower than the SRAM frequency and will require multiple SRAM cycles to perform a single read operation.

#### Write (Stire) Operation

All addresses and SW are sampled on the clock rising edge.  $\overline{SW}$  is low on the rising clock. Write data is sampled on the rising clock, one cycle after write address and  $\overline{SW}$  have been sampled by the SRAM.  $\overline{SS}$  will be driven low during the same cycle that the Address,  $\overline{SW}$  and  $\overline{SW}$ [a:d] are valid to signal that a valid operation is on the Address and Control Input.

Pipelined write are supported. This is done by using write data buffers on the SRAM that capture the write addresses on one write cycle, and write the array on the next write cycle. The "next write cycle" can actually be many cycles away, broken by a series of read cycles. Byte writes are supported. The byte write signals  $\overline{SW}$ [a:d] signal which 9-bit bytes will be writen. Timing of  $\overline{SW}$ [a:d] is the same as the  $\overline{SW}$  signal.

#### **Bypass Read Operation**

. z I

Since write data is not fully written into the array on first write cycle, there is a need to sense the address in case a future read is to be done from the location that has not been written yet. For this case, the address comparator check to see if the new read address is the same as the contents of the stored write address Latch. If the contents match, the read data must be supplied from the stored write data latch with standard read timing. If there is no match, the read data comes from the SRAM array. The bypassing of the SRAM array occurs on a byte by byte basis. If one byte is written and the other bytes are not, read data from the last written will have new byte data from the write data buffer and the other bytes from the SRAM array.

#### Programmable Impedance Output Buffer Operation

This HSTL Late Write SRAM has been designed with programmable impedance output buffers. The SRAMs output buffer impedance can be adjusted to match the system data bus impedance, by connecting a external resistor (RQ) between the ZQ pin of the SRAM and Vss. The value of RQ must be five times the value of the intended line impedance driven by the SRAM. For example, a  $250\Omega$  resistor will give an output buffer impedance of  $50\Omega$ . The allowable range of RQ is from  $175\Omega$  to  $350\Omega$ . Internal circuits evaluate and periodically adjust the output buffer impedance, as the impedance is affected by drifts in supply voltage and temperature. One evaluation occurs every 32 clock cycles, with each evaluation moving the output buffer impedance level only one step at a time toward the optimum level. Impedance updates occur when the SRAM is in High-Z state, and thus are triggered by write and deselect operations. Updates will also be triggered with G HIGH initiated High-Z state, providing the specified G setup and hold times are met. Impedance match is not instantaneous upon power-up. In order to guarantee optimum output driver impedance, the SRAM requires a minimum number of non-read cycles (1,024) after power-up. The output buffers can also be programmed in a minimum impedance configuration by connecting ZQ to Vss or Vpd.

#### **Mode Control**

There are two mode control select pins (M1 and M2) used to set the proper read protocol. This SRAM supports single clock pipelined operating mode. For proper specified device operation, M1 must be connected to Vss and M2 must be connected to Vbbq. These mode pins must be set at power-up and must not change during device operation.

#### Power-Up/Power-Down Supply Voltage Sequencing

The following power-up supply voltage application is recommended: Vss, VDD, VDDQ, VREF, then VIN. VDD and VDDQ can be applied simultaneously, as long as VDDQ does not exceed VDD by more than 0.5V during power-up. The following power-down supply voltage removal sequence is recommended: VIN, VREF, VDDQ, VDD, VSs. VDD and VDDQ can be removed simultaneously, as long as VDDQ does not exceed VDD by more than 0.5V during power-down.

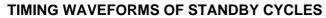

#### **Sleep Mode**

Sleep mode is a low power mode initiated by bringing the asynchronous ZZ pin high. During sleep mode, all other inputs are ignored and outputs are brought to a High-Impedance state. Sleep mode current and output High-Z are guaranteed after the specified sleep mode enable time. During sleep mode the memory array data content is preserved. Sleep mode must not be initiated until after all pending operations have completed, as any pending operation is not guaranteed to properly complete after sleep mode is initiated. Normal operations can be resumed by bringing the ZZ pin low, but only after the specified sleep mode recovery time.

### FUNCTION DESCRIPTION

The K7P163666A and K7P161866A are 18,874,368 bit Dual Mode (supports both Register Register and Late Select Mode) SRAM devices. They are organized as 524,288 words by 36 bits for K7P163666A and 1,048,576 words by 18 bits for K7P161866A, fabricated using Samsung's advanced CMOS technology. Late Write/Pipelined Read(RR) for x36/x18 organizations and Late Write/Late Select Read(LS) for x36 organization are supported.

The chip is operated with a single +2.5V power supply and is compatible with HSTL input and output. The package is 119(7x17) Plastic Ball Grid Array with balls on a 1.27mm pitch.

#### Read Operation for Register Register Mode(x36 and x18)

During read operations, addresses and controls are registered during the first rising edge of K clock and then the internal array is read between first and second edges of K clock. Data outputs are updated from output registers off the second rising edge of K clock.

#### Read Operation for Late Select Mode(x36)

During read operations, addresses(SA) and controls except the Way Select Address(SAS) are registered during the first rising edge of K clock. The internal array(x72 bit data) is read between the first edge and the second edge, and as the Way Select Address(SAS) is registered at the second clock edge, x36 bit data is mux selected before the output register.

#### Write Operation(Late Write)

During write operations, addresses including the Way Select Address(SAS) and controls are registered at the first rising edge of K clock and data inputs are registered at the following rising edge of K clock. Write addresses and data inputs are stored in the data in registers until the next write operation, and only at the next write operation are data inputs fully written into SRAM array. Byte write operation is supported using  $\overline{SW}$ [a:d] and the timing of  $\overline{SW}$ [a:d] is the same as the  $\overline{SW}$  signal.

#### **Bypass Read Operation**

Since write data is not fully written into the array on first write cycle, there is a need to sense the address in case a future read is to be done from the location that has not been written yet. For this case, the address comparator check to see if the new read address is the same as the contents of the stored write address Latch. If the contents match, the read data must be supplied from the stored write data latch with standard read timing. If there is no match, the read data comes from the SRAM array. The bypassing of the SRAM array occurs on a byte by byte basis. If one byte is written and the other bytes are not, read data from the last written will have new byte data from the write data buffer and the other bytes from the SRAM array.

#### Programmable Impedance Output Buffer Operation

This HSTL Late Write SRAM has been designed with programmable impedance output buffers. The SRAMs output buffer impedance can be adjusted to match the system data bus impedance, by connecting a external resistor (RQ) between the ZQ pin of the SRAM and Vss. The value of RQ must be five times the value of the intended line impedance driven by the SRAM. For example, a  $250\Omega$  resistor will give an output buffer impedance of  $50\Omega$ . The allowable range of RQ is from  $175\Omega$  to  $350\Omega$ . Internal circuits evaluate and periodically adjust the output buffer impedance, as the impedance is affected by drifts in supply voltage and temperature. One evaluation occurs every 32 clock cycles, with each evaluation moving the output buffer impedance level only one step at a time toward the optimum level. Impedance updates occur when the SRAM is in High-Z state, and thus are triggered by write and deselect operations. Updates will also be triggered with G HIGH initiated High-Z state, providing the specified G setup and hold times are met. Impedance match is not instantaneous upon power-up. In order to guarantee optimum output driver impedance, the SRAM requires a minimum number of non-read cycles (1,024) after power-up. The output buffers can also be programmed in a minimum impedance configuration by connecting ZQ to Vss or Vpd.

#### **Mode Control**

There are two mode control select pins (M1 and M2) used to set the proper read protocol. This SRAM supports single clock pipelined operating mode. For proper specified device operation, M1 must be connected to Vss and M2 must be connected to Vbb. These mode pins must be set at power-up and must not change during device operation.

#### Power-Up/Power-Down Supply Voltage Sequencing

The following power-up supply voltage application is recommended: Vss, VDD, VDDQ, VREF, then VIN. VDD and VDDQ can be applied simultaneously, as long as VDDQ does not exceed VDD by more than 0.5V during power-up. The following power-down supply voltage removal sequence is recommended: VIN, VREF, VDDQ, VDD, VSs. VDD and VDDQ can be removed simultaneously, as long as VDDQ does not exceed VDD by more than 0.5V during power-down.

#### Sleep Mode

Sleep mode is a low power mode initiated by bringing the asynchronous ZZ pin high. During sleep mode, all other inputs are ignored and outputs are brought to a High-Impedance state. Sleep mode current and output High-Z are guaranteed after the specified sleep mode enable time. During sleep mode the memory array data content is preserved. Sleep mode must not be initiated until after all pending operations have completed, as any pending operation is not guaranteed to properly complete after sleep mode is initiated. Normal operations can be resumed by bringing the ZZ pin low, but only after the specified sleep mode recovery time.

# K7P163666A K7P161866A

# 512Kx36 & 1Mx18 SRAM

# **TRUTH TABLE**

| к          | ZZ | G | SS | SW | SWa | SWb | SWc | SWd | DQa  | DQb  | DQc  | DQd  | Operation                     |

|------------|----|---|----|----|-----|-----|-----|-----|------|------|------|------|-------------------------------|

| Х          | Н  | Х | Х  | Х  | Х   | Х   | Х   | Х   | Hi-Z | Hi-Z | Hi-Z | Hi-Z | Power Down Mode. No Operation |

| Х          | L  | Н | Х  | Х  | Х   | Х   | Х   | Х   | Hi-Z | Hi-Z | Hi-Z | Hi-Z | Output Disabled.              |

| $\uparrow$ | L  | L | Н  | Х  | Х   | Х   | Х   | Х   | Hi-Z | Hi-Z | Hi-Z | Hi-Z | Output Disabled. No Operation |

| $\uparrow$ | L  | L | L  | Н  | Х   | Х   | Х   | Х   | Dout | Dout | Dout | Dout | Read Cycle                    |

| $\uparrow$ | L  | Х | L  | L  | Н   | Н   | Н   | н   | Hi-Z | Hi-Z | Hi-Z | Hi-Z | No Bytes Written              |

| $\uparrow$ | L  | Х | L  | L  | L   | Н   | Н   | н   | Din  | Hi-Z | Hi-Z | Hi-Z | Write first byte              |

| $\uparrow$ | L  | Х | L  | L  | Н   | L   | Н   | н   | Hi-Z | DIN  | Hi-Z | Hi-Z | Write second byte             |

| $\uparrow$ | L  | Х | L  | L  | н   | н   | L   | Н   | Hi-Z | Hi-Z | DIN  | Hi-Z | Write third byte              |

| $\uparrow$ | L  | Х | L  | L  | Н   | Н   | н   | L   | Hi-Z | Hi-Z | Hi-Z | DIN  | Write fourth byte             |

| $\uparrow$ | L  | Х | L  | L  | L   | L   | L   | L   | Din  | Din  | Din  | Din  | Write all bytes               |

NOTE : K & K are complementary

# ABSOLUTE MAXIMUM RATINGS

| Parameter                              | Symbol | Value                       | Unit |

|----------------------------------------|--------|-----------------------------|------|

| Core Supply Voltage Relative to Vss    | Vdd    | -0.5 to 3.13                | V    |

| Output Supply Voltage Relative to Vss  | Vddq   | -0.5 to 2.4                 | V    |

| Voltage on any I/O pin Relative to Vss | Vterm  | -0.5 to VDDQ+0.5 (2.4V MAX) | V    |

| Output Short-Circuit Current           | lout   | 25                          | mA   |

| Operating Temperature                  | TOPR   | 0 to 70                     | °C   |

| Storage Temperature                    | Тѕтд   | -55 to 125                  | °C   |

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **RECOMMENDED DC OPERATING CONDITIONS**

| Parameter                        | Symbol   | Min      | Тур  | Max      | Unit | Note |

|----------------------------------|----------|----------|------|----------|------|------|

| Core Power Supply Voltage        | Vdd      | 2.37     | 2.5  | 2.63     | V    |      |

| Output Power Supply Voltage      | Vddq     | 1.4      | 1.5  | 1.9      | V    |      |

| Input High Level                 | Vін      | Vref+0.1 | -    | Vddq+0.3 | V    |      |

| Input Low Level                  | VIL      | -0.3     | -    | Vref-0.1 | V    |      |

| Input Reference Voltage          | Vref     | 0.6      | 0.75 | 0.9      | V    |      |

| Clock Input Signal Voltage       | VIN-CLK  | -0.3     | -    | Vddq+0.3 | V    |      |

| Clock Input Differential Voltage | VDIF-CLK | 0.1      | -    | Vddq+0.6 | V    |      |

| Clock Input Common Mode Voltage  | Vсм-CLK  | 0.6      | 0.75 | 0.9      | V    |      |

# **PIN CAPACITANCE**

| Parameter               | Symbol | Test Condition | Min | Max | Unit |

|-------------------------|--------|----------------|-----|-----|------|

| Input Capacitance       | CIN    | VIN=0V         | -   | 4   | pF   |

| Data Output Capacitance | Соит   | Vout=0V        | -   | 5   | pF   |

NOTE : Periodically sampled and not 100% tested.(TA=25°C, f=1MHz)

# **DC CHARACTERISTICS**

| Parameter                                                                   | Symbol                  | Min      | Max               | Unit | Note |

|-----------------------------------------------------------------------------|-------------------------|----------|-------------------|------|------|

| Average Power Supply Operating Current-x36<br>(VIN=VIH or VIL, ZZ & SS=VIL) | IDD33<br>IDD30<br>IDD25 | -        | 700<br>620<br>550 | mA   | 1, 2 |

| Average Power Supply Operating Current-x18<br>(VIN=VIH or VIL, ZZ & SS=VIL) | IDD33<br>IDD30<br>IDD25 | -        | 650<br>570<br>500 | mA   | 1, 2 |

| Power Supply Standby Current<br>(VIN=VIH or VIL, ZZ=VIH)                    | Isbzz                   | -        | 128               | mA   | 1    |

| Active Standby Power Supply Current<br>(VIN=VIH or VIL, SS=VIH, ZZ=VIL)     | ISBSS                   | -        | 200               | mA   | 1    |

| Input Leakage Current<br>(VIN=Vss or VDDQ)                                  | Iц                      | -1       | 1 1               | μA   |      |

| Output Leakage Current<br>(Vout=Vss or Voda, DQ in High-Z)                  | ILO                     | 2 12 34  | CA                | μA   |      |

| Output High Voltage(Programmable Impedance Mode)                            | VOH1                    | VDDQ/2   | Vddq              | V    | 3,5  |

| Output Low Voltage(Programmable Impedance Mode)                             | VOL1                    | Vss      | Vddq/2            | V    | 4,5  |

| Output High Voltage(Iон=-0.1mA)                                             | Voh2                    | VDDQ-0.2 | Vddq              | V    | 6    |

| Output Low Voltage(IoL=0.1mA)                                               | VOL2                    | Vss      | 0.2               | V    | 6    |

| Output High Voltage(Iон=-6mA)                                               | <b>V</b> онз            | VDDQ-0.4 | Vddq              | V    | 6    |

| Output Low Voltage(IoL=6mA)                                                 | VOL3                    | Vss      | 0.4               | V    | 6    |

NOTE :1. Minimum cycle. Iout=0mA.

$\begin{array}{l} 2.50\% \mbox{ read cycles.} \\ 3. |IoH|=(VDDQ/2)/(RQ/5)\pm15\% @VOH=VDDQ/2 \mbox{ for } 175\Omega \leq RQ \leq 350\Omega. \\ 4. |IoL|=(VDDQ/2)/(RQ/5)\pm15\% @VOL=VDDQ/2 \mbox{ for } 175\Omega \leq RQ \leq 350\Omega. \\ \end{array}$

Frogrammable Impedance Output Buffer Mode. The ZQ pin is connected to Vss through RQ.

Minimum Impedance Output Buffer Mode. The ZQ pin is connected to Vss or Vbb.

## AC TEST CONDITIONS (TA=0 to 70°C, VDD=2.37 -2.63V, VDDQ=1.5V)

| Parameter                            | Symbol  | Value       | Unit |

|--------------------------------------|---------|-------------|------|

| Core Power Supply Voltage            | Vdd     | 2.37~2.63   | V    |

| Output Power Supply Voltage          | Vddq    | 1.5         | V    |

| Input High/Low Level                 | VIH/VIL | 1.25/0.25   | V    |

| Input Reference Level                | Vref    | 0.75        | V    |

| Input Rise/Fall Time                 | TR/TF   | 0.5/0.5     | ns   |

| Input and Out Timing Reference Level |         | 0.75        | V    |

| Clock Input Timing Reference Level   |         | Cross Point | V    |

NOTE : Parameters are tested with RQ=250  $\Omega$  and VDDQ=1.5V.

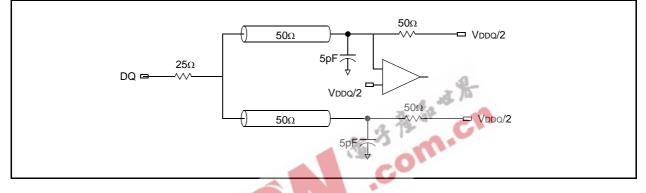

# AC TEST OUTPUT LOAD

# **AC CHARACTERISTICS**

| Parameter                         | Symbol        | -   | 33  | -3  | 30  | -2  | 25  | Unit | Note |

|-----------------------------------|---------------|-----|-----|-----|-----|-----|-----|------|------|

| Farameter                         | Symbol        | Min | Max | Min | Max | Min | Max | Unit | Note |

| Clock Cycle Time                  | ткнкн         | 3.0 | -   | 3.3 | -   | 4.0 | -   | ns   |      |

| Clock High Pulse Width            | <b>t</b> KHKL | 1.2 | -   | 1.3 | -   | 1.6 | -   | ns   |      |

| Clock Low Pulse Width             | <b>t</b> KLKH | 1.2 | -   | 1.3 | -   | 1.6 | -   | ns   |      |

| Clock High to Output Valid        | tĸhq∨         | -   | 1.5 | -   | 1.6 | -   | 2.0 | ns   |      |

| Clock High to Output Hold         | tкнqx         | 0.5 | -   | 0.5 | -   | 0.5 | -   | ns   |      |

| Address Setup Time                | <b>t</b> avkh | 0.3 | -   | 0.3 | -   | 0.3 | -   | ns   |      |

| Address Hold Time                 | tкнах         | 0.5 | -   | 0.6 | -   | 0.6 | -   | ns   |      |

| Write Data Setup Time             | tdvкн         | 0.3 | -   | 0.3 | -   | 0.3 | -   | ns   |      |

| Write Data Hold Time              | <b>t</b> KHDX | 0.5 | -   | 0.6 | -   | 0.6 | -   | ns   |      |

| SW, SW[a:d] Setup Time            | twvкн         | 0.3 | -   | 0.3 | -   | 0.3 | -   | ns   |      |

| SW, SW[a:d] Hold Time             | tкнwx         | 0.5 | -   | 0.6 | -   | 0.6 | -   | ns   |      |

| SS Setup Time                     | ts∨ĸн         | 0.3 | -   | 0.3 | -   | 0.3 | -   | ns   |      |

| SS Hold Time                      | tĸнsx         | 0.5 | -   | 0.6 | -   | 0.6 | -   | ns   |      |

| Clock High to Output Hi-Z         | tкнqz         | -   | 1.5 | -   | 1.6 | -   | 2.0 | ns   |      |

| Clock High to Output Low-Z        | tKHQX1        | 0.5 | -   | 0.5 | -   | 0.5 | -   | ns   |      |

| G High to Output High-Z           | tGHQZ         | -   | 1.5 | -   | 1.6 | -   | 2.0 | ns   |      |

| G Low to Output Low-Z             | tGLQX         | 0.5 | -   | 0.5 | -   | 0.5 | -   | ns   |      |

| G Low to Output Valid             | tGLQV         | -   | 1.5 | -   | 1.6 | -   | 2.0 | ns   |      |

| ZZ High to Power Down(Sleep Time) | tzze          | -   | 15  | -   | 15  | -   | 15  | ns   |      |

| ZZ Low to Recovery(Wake-up Time)  | tzzr          | -   | 20  | -   | 20  | -   | 20  | ns   |      |

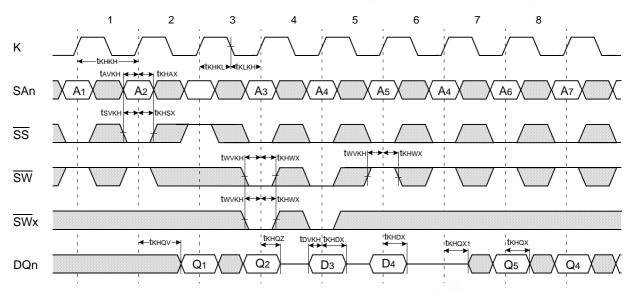

## TIMING WAVEFORMS OF NORMAL ACTIVE CYCLES (SS Controlled, G=Low)

NOTE

1. D<sub>3</sub> is the input data written in memory location A<sub>3</sub>.

2. Q<sub>4</sub> is the output data read from the write data buffer(not from the cell array), as a result of address A<sub>4</sub> being a match from the last write cycle address. last write cycle address. 1 4

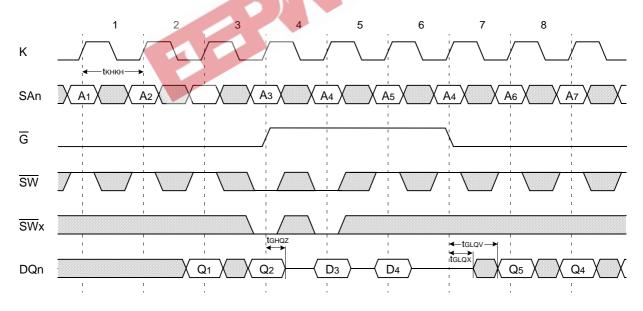

# TIMING WAVEFORMS OF NORMAL ACTIVE CYCLES (G Controlled, SS=Low)

#### NOTE

1. D3 is the input data written in memory location A3.

2. Q4 is the output data read from the write data buffer(not from the cell array), as a result of address A4 being a match from the last write cycle address.

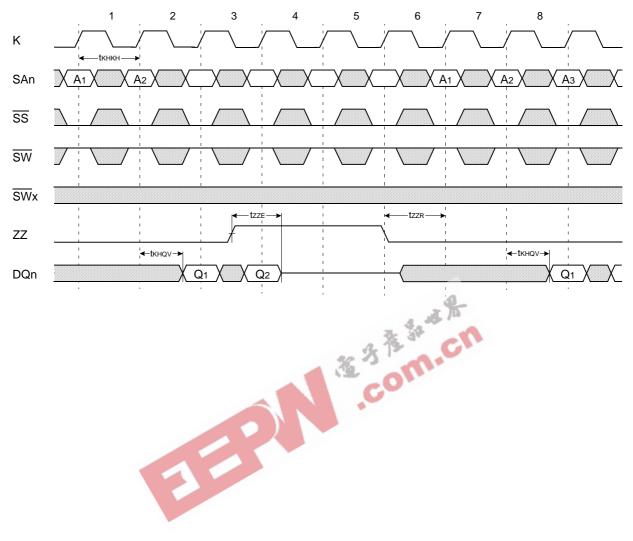

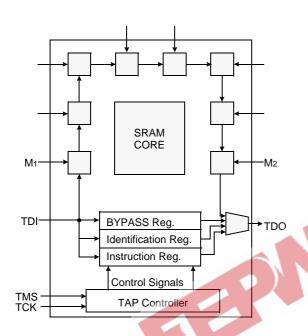

## IEEE 1149.1 TEST ACCESS PORT AND BOUNDARY SCAN-JTAG

The SRAM provides a limited set of IEEE standard 1149.1 JTAG functions. This is to test the connectivity during manufacturing between SRAM, printed circuit board and other components. Internal data is not driven out of SRAM under JTAG control. In conformance with IEEE 1149.1, the SRAM contains a TAP controller, Instruction Register, Bypass Register and ID register. The TAP controller has a standard 16-state machine that resets internally upon power-up, therefore, TRST signal is not required. It is possible to use this device without utilizing the TAP. To disable the TAP controller without interfacing with normal operation of the SRAM, TCK must be tied to Vss to preclude mid level input. TMS and TDI are designed so an undriven input will produce a response identical to the application of a logic 1, and therefore can be left unconnected. But they may also be tied to Vbp through a resistor. TDO should be left unconnected.

### JTAG Block Diagram

# JTAG Instruction Coding

| IR2 | IR1 | IR0 | Instruction | TDO Output              | Notes |

|-----|-----|-----|-------------|-------------------------|-------|

| 0   | 0   | 0   | SAMPLE-Z    | •                       | 1     |

| 0   | 0   | 1   | IDCODE      | Identification Register | 2     |

| 0   | 1   | 0   | SAMPLE-Z    | Boundary Scan Register  | 1     |

| 0   | 1   | 1   | BYPASS      | Bypass Register         | 3     |

| 1   | 0   | 0   | SAMPLE      | Boundary Scan Register  | 4     |

| 1   | 0   | 1   | BYPASS      | Bypass Register         | 3     |

| 1   | 1   | 0   | BYPASS      | Bypass Register         | 3     |

| 1   | 1   | 1   | BYPASS      | Bypass Register         | 3     |

NOTE :

1. Places DQs in Hi-Z in order to sample all input data regardless of other SRAM inputs.

2. TDI is sampled as an input to the first ID register to allow for the serial shift of the external TDI data.

Bypass register is initiated to Vss when BYPASS instruction is invoked. The Bypass Register also holds serially loaded TDI when exiting the Shift DR states.

4. SAMPLE instruction does not places DQs in Hi-Z.

**BOUNDARY SCAN EXIT ORDER(x18)**

### SCAN REGISTER DEFINITION

| Part    | Instruction Register | Bypass Register | ID Register | Boundary Scan |  |

|---------|----------------------|-----------------|-------------|---------------|--|

| 512Kx36 | 512Kx36 3 bits       |                 | 32 bits     | 70 bits       |  |

| 1Mx18   | 3 bits               | 1 bits          | 32 bits     | 51 bits       |  |

#### **ID REGISTER DEFINITION**

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

| Part    | Revision Number<br>(31:28) | Part Configuration (27:18) | Vendor Definition<br>(17:12) | Samsung JEDEC Code<br>(11: 1) | Start Bit(0) |

|---------|----------------------------|----------------------------|------------------------------|-------------------------------|--------------|

| 512Kx36 | 0000                       | 00111 00100                | XXXXXX                       | 00001001110                   | 1            |

| 1Mx18   | 0000                       | 01000 00011                | XXXXXX                       | 00001001110                   | 1            |

#### **BOUNDARY SCAN EXIT ORDER(x36)**

#### 3B SA<sub>9</sub> SA8 5B 35 26 3B SA<sub>9</sub> SA8 5B 25 2B SA18 SA17 6B 34 27 2B **SA**19 SA17 6B 24 ЗA **SA**10 SA7 5A 33 28 ЗA **SA**10 SA7 5A 23 3C SA11 5C 3C SA11 5C SA<sub>6</sub> 32 29 SA<sub>6</sub> 22 2C SA12 SA5 6C 31 30 2C SA12 SA5 6C 21 2A **SA**13 SA4 31 2A SA4 **SA**13 6A 30 6A 20 2D DQc9 DQb9 6D 29 DQa9 6D 19 DQb1 1D DQc8 DQb8 7D 28 32 1D 2E DQc7 DQb7 6E 27 33 2E DQb2 32 1E DQc6 DQb6 7E 26 DQa8 7E 18 4 2F DQc5 DQb5 6F 25 DQa7 6F 17 2G DQc4 DQb4 6G 24 34 2G DQb3 23 7G 1G DQc3 DQb3 7G DQa6 16 2H DQc2 DQb2 6H 22 DQa5 6H 15 DQb1 7H DQb4 1H DQc<sub>1</sub> 21 1H 35 3G SWc SWb 5G 20 36 3G SWb 4D ZQ G 4F 4D G 4F 14 19 37 ZQ 4E SS 4K SS K 18 38 4E Κ 4K 13 NC\* ĸ ĸ 4G 4L 39 4G NC 4L 12 17 NC\* 4H SWa 5L 16 40 4H NC SWa 5L 11 SW SW 4M DQa1 7K 15 41 4M DQa4 7K 10 SWd 6K 3L DQa2 14 1K DQd1 DQa<sub>3</sub> 7L 13 2K DQd2 DQa4 6L 2K DQb5 DQa3 6L 9 12 42 1L DQd3 DQa5 6M 11 43 1L DQb6 2L DQd4 DQa6 7N 10 2M DQd5 DQa7 6N 9 44 2M DQb7 DQa<sub>2</sub> 6N 8 1N DQd<sub>6</sub> DQa8 7P 8 45 1N DQb8 DQa1 7P 7 2N DQd7 DQa9 6P 7 1P DQd8 ΖZ 7T 6 ΖZ 7T 6 2P DQd9 5 2P DQb9 SA3 5 SA3 5T 46 5T ЗT SA<sub>2</sub> 4 ЗT SA14 SA<sub>2</sub> 6R 4 **SA**14 6R 47

NOTE :1. Pins 4G and 4H are no connection pin to internal chip. The scanned data are fixed to "0" and "1" respectively.

3

2

1

**SA**16

SA1

M2

4T

4P

5R

2R

4N

3R

**SA**15

SA<sub>0</sub>

M1

2R

4N

2T

3R

48

49

50

51

**SA**15

SA<sub>0</sub>

**SA**18

**M**1

SA1

**SA**16

M2

4P

6T

5R

3

2

1

## JTAG DC OPERATING CONDITIONS

| Parameter                     | Symbol | Min  | Тур | Max     | Unit | Note |

|-------------------------------|--------|------|-----|---------|------|------|

| Power Supply Voltage          | Vdd    | 2.37 | 2.5 | 2.63    | V    |      |

| Input High Level              | Vін    | 1.7  | -   | Vdd+0.3 | V    |      |

| Input Low Level               | VIL    | -0.3 | -   | 0.8     | V    |      |

| Output High Voltage(IOH=-2mA) | Vон    | 2.1  | -   | Vdd     | V    |      |

| Output Low Voltage(IoL=2mA)   | Vol    | Vss  | -   | 0.2     | V    |      |

$\ensuremath{\textbf{NOTE}}$  : 1. The input level of SRAM pin is to follow the SRAM DC specification.

# JTAG AC TEST CONDITIONS

| Parameter                               | Symbol  | Min     | Unit | Note |

|-----------------------------------------|---------|---------|------|------|

| Input High/Low Level                    | VIH/VIL | 2.5/0.0 | V    |      |

| Input Rise/Fall Time                    | TR/TF   | 1.0/1.0 | ns   |      |

| Input and Output Timing Reference Level |         | 1.25    | V    | 1    |

NOTE : 1. See SRAM AC test output load on page 7.

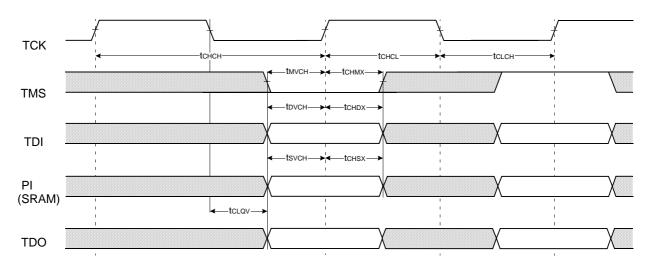

## **JTAG AC Characteristics**

| JTAG AC Characteristics   | e_            |     |          |      |      |

|---------------------------|---------------|-----|----------|------|------|

| Parameter                 | Symbol        | Min | Max      | Unit | Note |

| TCK Cycle Time            | tснсн         | 50  | 39 -     | ns   |      |

| TCK High Pulse Width      | <b>t</b> CHCL | 20  |          | ns   |      |

| TCK Low Pulse Width       | <b>t</b> CLCH | 20  | <u> </u> | ns   |      |

| TMS Input Setup Time      | tм∨сн         | 5   | -        | ns   |      |

| TMS Input Hold Time       | tснмх         | 5   | -        | ns   |      |

| TDI Input Setup Time      | tDVCH         | 5   | -        | ns   |      |

| TDI Input Hold Time       | <b>tCHDX</b>  | 5   | -        | ns   |      |

| SRAM Input Setup Time     | tsvcн         | 5   | -        | ns   |      |

| SRAM Input Hold Time      | tCHSX         | 5   | -        | ns   |      |

| Clock Low to Output Valid | tCLQV         | 0   | 10       | ns   |      |

# **JTAG TIMING DIAGRAM**

SAMSUNG ELECTRONICS

## **119 BGA PACKAGE DIMENSIONS**

# **119 BGA PACKAGE THERMAL CHARACTERISTICS**

| Parameter                         | Symbol   | Thermal Resistance | Unit | Note       |

|-----------------------------------|----------|--------------------|------|------------|

| Junction to Ambient(at still air) | Theta_JA | TBD                | °C/W | 1W Heating |

| Junction to Case                  | Theta_JC | TBD                | °C/W |            |

| Junction to Board                 | Theta_JB | TBD                | °C/W | 2W Heating |

**NOTE** : 1. Junction temperature can be calculated by :  $T_J = T_A + P_D x$  Theta\_JA.