## Microprocessor Reset circuits

### **General Description**

The KB809 is a power supply supervisor that provides under-voltage monitoring and power-on reset generation in an industry standard 3-pin SOT package and pinout. The reset output is asserted at power-on and any time the input voltage drops below the programmed threshold. It remains asserted for 180ms (typ.) after the input subsequently rises back above the threshold boundary. The KB809 has an active-low reset output. Hysteresis is included to prevent chattering due to noise, and the KB809 is inherently immune to brief power supply transients. Typical supply current is a low  $3\mu A$ . For those applications that require a manual reset function, see the KB811/812. For those applications that require a longer reset timeout, see the KB809. (The KB809 is identical to the industry-standard KB809 with the exception of a shorter reset timout.)

#### **Features**

- Under-voltage monitor

- Power-on reset generation (180ms Typ)

- Choice of threshold voltages (contact Kingbor regarding availability)

- Active-low reset output

- · No external components required

- · Rejects brief input transients

- · Industry standard package and pinout

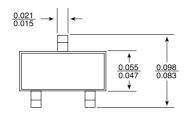

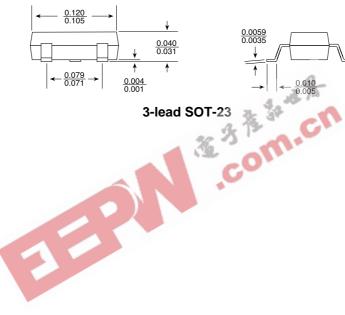

- · 3-pin SOT23-3 package

### **Applications**

- Monitoring processor, ASIC, or FPGA core and I/O voltages

- · PDAs, hand-held PCs

- Embedded controllers

- · Telecommunications systems

- Power supplies

- · Wireless / Cellular systems

- Networking hardware

### **Ordering Information**

| Part Number | Marking** | Typical Application Voltage*       | Nominal<br>Threshold<br>Voltage | T <sub>RST</sub> (ms) | Junction<br>Temperature<br>Range | Package |

|-------------|-----------|------------------------------------|---------------------------------|-----------------------|----------------------------------|---------|

| KB809-293   | ADAA C956 | 3.3V ±5%                           | 2.93                            | 180                   | –40°C to +85°C                   | SOT23-3 |

| Part Number | Marking** | Typical<br>Application<br>Voltage* | Nominal<br>Threshold<br>Voltage | T <sub>RST</sub> (ms) | Junction<br>Temperature<br>Range | Package |

2.63

Top Marking: ADAA & AFAA: To manufacture marking after 2007-3-15

C956 & C756: Before 2007-3-15

AFAA C756 3.3V±10%

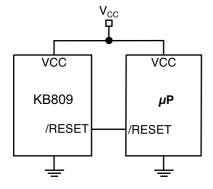

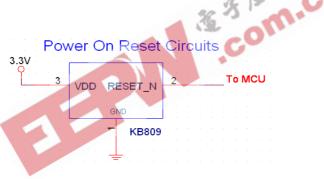

### **Typical Application**

KB809-263

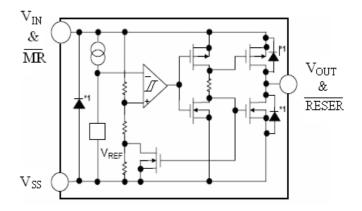

**Typical Operating Circuit**

### **Block Diagrams**

–40 °C to +85°C

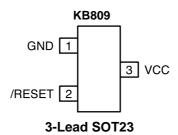

# **Pin Configuration**

# **Pin Description**

| Pin Description |          | A. A. The                                                                                                                                                                                               |

|-----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number      | Pin Name | Pin Function                                                                                                                                                                                            |

| 1               | GND      | Ground return for all IC functions.                                                                                                                                                                     |

| 2               | /RESET   | Digital Output. Active-low. Asserted whenever $V_{CC}$ falls below the threshold voltage. It will remain asserted for no less than 180ms and be de-asserted after $V_{CC}$ returns above the threshold. |

| 3               | VCC      | Analog Input. Power supply input to the IC.                                                                                                                                                             |

## **Absolute Maximum Ratings** (Note 1)

## **Operating Ratings** (Note 2)

| Terminal Voltage (V <sub>CC</sub> )   | –0.3V to 10V     |

|---------------------------------------|------------------|

| Lead Temperature (soldering, 10 sec.) | 300°C            |

| Storage Temperature (T <sub>S</sub> ) | . –65°C to 150°C |

| Rate of Rise (V <sub>CC</sub> )       | 100V/μs          |

| ESD Rating, Note 3                    |                  |

| Ambient Temperature (T <sub>A</sub> )      | 40°C to +85°C |

|--------------------------------------------|---------------|

| Power Dissipation (T <sub>A</sub> = +70°C) | 320mW         |

### **Electrical Characteristics**

$T_A = 25^{\circ}C$ ;  $V_{CC} = 3.3V$  for KB809 unless otherwise noted. Values in **bold** are for -40 °C to +85 °C; unless otherwise noted

| Symbol            | Parameter                  | Condition                                                             | Min                 | Тур  | Max  | Units |

|-------------------|----------------------------|-----------------------------------------------------------------------|---------------------|------|------|-------|

| $V_{CC}$          | Operating Voltage Range    | T <sub>A</sub> = 0°C to 70°C                                          | 0.95                |      | 8    | V     |

|                   |                            | T <sub>A</sub> = -40°C to 85°C                                        | 0.95                |      | 8    | V     |

| I <sub>CC</sub>   | Supply Current             | V <sub>CC</sub> = 3.3V                                                |                     | 1    | 3    | μА    |

| $V_{TH}$          | Reset Voltage Threshold    | S Voltage Options (KB809-293)                                         | 2.85                | 2.93 | 3.00 | V     |

|                   | Reset Voltage Threshold    | S Voltage Options (KB809-263)                                         | 2.55                | 2.63 | 2.70 | V     |

| V <sub>HYST</sub> | Typical hysteresis         | 275                                                                   |                     | 5    |      | mV    |

| T <sub>RST</sub>  | Reset Timeout Period       | 132 011                                                               | 140                 | 180  | 300  | ms    |

| T <sub>PROP</sub> | Propogation delay          | /RESET < V <sub>OL</sub> , 100mV Overdrive                            |                     | 9.3  |      | μs    |

| V <sub>OH</sub>   | /RESET Output Voltage High | I <sub>SOURCE</sub> = 500μA                                           | 0.8-V <sub>CC</sub> |      |      | V     |

| V <sub>OL</sub>   | /RESET Output Voltage Low  | V <sub>CC</sub> = V <sub>TH</sub> min., I <sub>SINK</sub> = 1.2mA     |                     |      | 0.3  | V     |

|                   |                            | $V_{CC} > 1.4V$ , $I_{SINK} = 50\mu A$ , $T_A = 0^{\circ}C$ to +70°C  |                     |      | 0.3  | V     |

|                   |                            | $V_{CC} > 1.6V$ , $I_{SINK} = 50\mu A$ , $T_A = -40^{\circ}$ to +85°C |                     |      | 0.3  | V     |

- Note 1. Exceeding the absolute maximum rating may damage the device.

- Note 2. The device is not guaranteed to function outside its operating rating.

- Note 3. Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5k in series with 100pF.

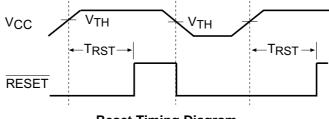

## **Timing Diagrams**

**Reset Timing Diagram**

March 2007 3

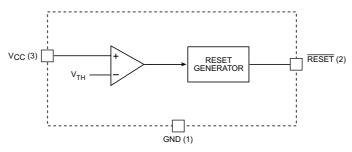

# **Functional Diagram**

**KB809 Block Diagram**

## **Standard Circuits**

## **Applications Information**

#### **Microprocessor Reset**

The /RESET pin is asserted whenever  $V_{CC}$  falls below the reset threshold voltage. The /RESET pin remains asserted for a period of 180ms after  $V_{CC}$  has risen above the reset threshold voltage. The reset function ensures the microprocessor is properly reset and powers up in a known condition after a power failure. /RESET will remain valid with  $V_{CC}$  as low as 0.95V.

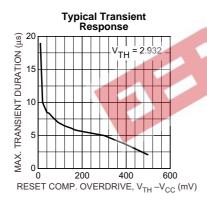

#### Transients on V<sub>CC</sub>

The KB809 is inherently immune to very short "glitches" on  $V_{CC}$ . In the case of very brief transients,  $V_{CC}$  may drop below the under-voltage threshold without triggering a reset. As shown in the graph of Figure 1, the narrower the transient, the deeper the threshold overdrive that will be ignored. The line on the graph represents the typical allowable transient duration for a given amount of threshold overdrive that will *not* generate a reset. The data from which Figure 1 is derived was taken by adding negative-going square-wave pulses to a DC input voltage set at 0.5V above the actual measured threshold for the part being characterized.

Figure 1. Comparator Overdrive vs. Duration

#### **Ensuring Proper Operation at Low V<sub>CC</sub>**

At levels of V $_{CC}$  below 1.4V, the KB809's output driver cannot always turn on sufficiently to produce a valid logic-low. In this situation, other circuits driven by /RESET could be allowed to float, causing undesired operation. (In most cases, however, it is expected that the circuits driven by the KB809 will be similarly inoperative at V $_{CC}$ =0.95V.)

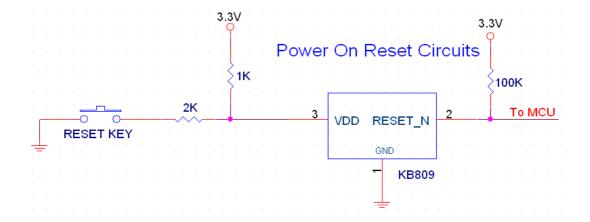

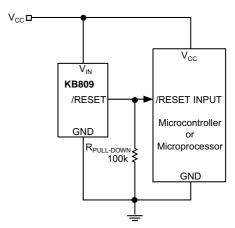

If a given application requires that /RESET be valid below  $V_{CC}$  =1.4V, this can be accomplished by adding a pull-down resistor to the output. A value of  $100k\Omega$  is recommended, as this is usually an acceptable compromise of leakage current and pull-down current. The resistor's value is not critical, however. See Figure 2.

Figure 2. Ensuring a Valid /RESET Signal at Low Voltage

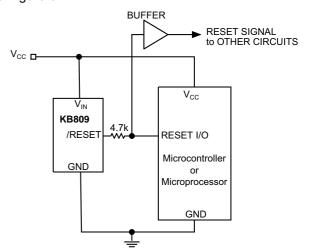

#### Interfacing to Processors with Bidirectional Reset Pins

Some microprocessors have reset signal pins that are bidirectional, rather than input only. The Motorola 68HC11 family is one example. To prevent excessive current flow when the processor asserts its reset output, a series resistor is employed between the KB809's output and the reset pin. This limits the current that will flow between the KB809 and the reset pin to a theoretical maximum of  $V_{\rm CC}/R_{\rm SERIES}$ . Because this resistor also limits the drive capability of the supervisor's output, a buffer may be required to drive additional circuitry. See Figure 3.

Figure 3. Interfacing to Processors with Bidirectional Reset Pins

March 2007 5

### **PACAGE DESCRIPTION**