No.2663A

LC7936A, 7936B

## 32-Bit PPC LED Erasing Head Driver

#### **Features**

- · High-speed, high-voltage silicon gate CMOS device

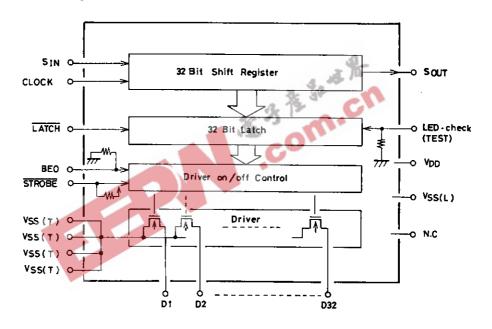

- Contains high-speed shiftable (5MHz max) 32-bit shift register, 32-bit latch, output driver on/off control circuit, 32-bit N-channel open drain output driver.

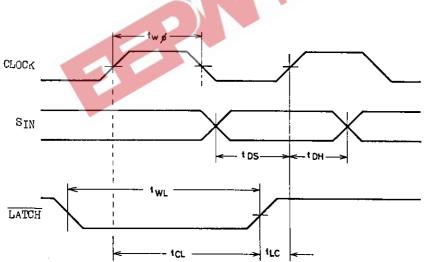

- Serial shift data is shifted on the positive transition of the clock signal (CLOCK).

- 32-bit latch data is changed on the negative transition of the LATCH pad signal and is held on the positive transition.

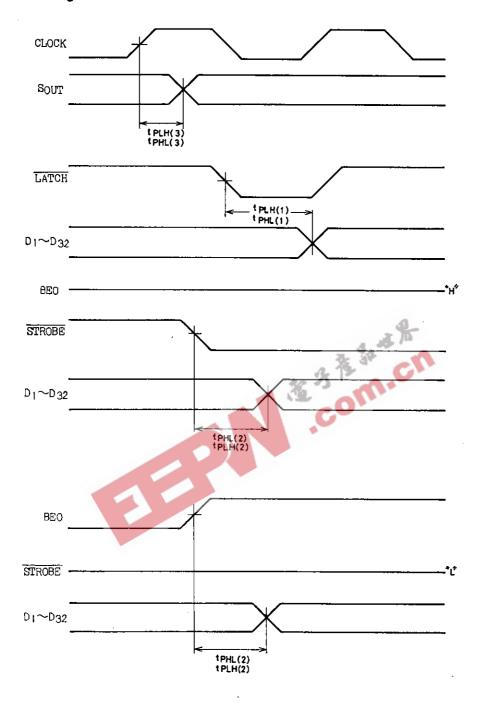

- The STROBE pad signal, BEO pad signal can be used to exercise on/off control of the output driver.

- All output drivers can be turned on by setting 32-bit latch regardless of shift register data. (TEST=Hi, STROBE=Lo, BEO=Hi)

- Complete separation of logic circuit GND (1 pad) and thermal driver GND (4 pads)

- Maximum ratings of driver output: V<sub>O</sub>=15V, I<sub>OL</sub>=30mA

- Logic unit operating voltage: V<sub>DD</sub>=4.5V to 5.5V

| Absolute Maximum Ratings at Ta<br>Maximum Supply Voltage | a=25°C<br>V <sub>DD</sub> | 4                               | +0.3 to +7.0                 | unit<br>V |

|----------------------------------------------------------|---------------------------|---------------------------------|------------------------------|-----------|

| Input Voltage                                            | $V_{I}$                   | * 3                             | -0.3 to V <sub>DD</sub> +0.3 | V         |

| Output Voltage                                           | $V_{O}(1)$                | S <sub>OUT</sub> output         | -0.3 to V <sub>DD</sub> +0.3 | V         |

|                                                          | V <sub>o</sub> (2)        | D1 to D32 output Output Tr off  | 15                           | V         |

| Output Circuit                                           | Io                        | D1 to D32 output,<br>per output | 30                           | mA        |

| Allowable Power Dissipation                              | Pd max                    | QIP-64 package at 70°C          | 450                          | mW        |

| Operating Temperature                                    | Topr                      | QIP-64 package                  | 0 to +70                     | °C        |

| Storage Temperature                                      | Tstg                      | QIP-64 package                  | -35 to +125                  | °C        |

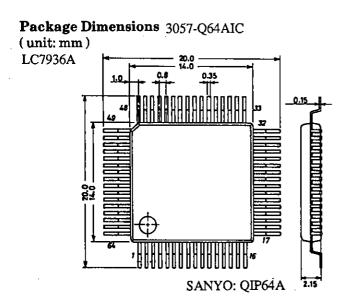

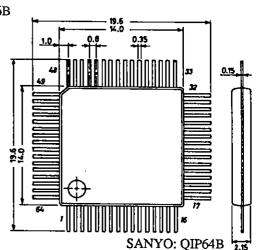

# Package Dimensions 3026B-Q64BIC (unit: mm) LC7936B

| Allowable Operating Co.                         | nditio            | ns at Ta             | =0 to +70°C                            |                   |                                                                    |                     |     |             | ,          |

|-------------------------------------------------|-------------------|----------------------|----------------------------------------|-------------------|--------------------------------------------------------------------|---------------------|-----|-------------|------------|

|                                                 |                   |                      | Pin Na                                 | me                |                                                                    | min                 | typ | max         | unit       |

| Supply Voltage                                  | $V_{DD}$          | $V_{DD}$             |                                        |                   |                                                                    | 4.5                 |     | 5.5         | v          |

| "H"-Level Input Voltage                         | $V_{IH}$          |                      | LOCK, <mark>LATC</mark><br>STROBE, LED |                   | (TEST)                                                             | $0.8V_{DD}$         |     | $V_{DD}$    | V          |

| "L"-Level Input Voltage                         | $V_{IL}$          |                      | LOCK, LATCI<br>STROBE, LED             |                   | (TEST)                                                             | V <sub>SS</sub> (L) |     | $0.2V_{DD}$ | Ÿ          |

| Clock Frequency                                 | $f_{CLK}$         | CLOC                 | CK Duty: 50%                           | )                 |                                                                    |                     |     | 5.0         | MHz        |

| Clock Pulse Width                               | $t_{\mathrm{We}}$ | CLOC                 | CK C                                   |                   |                                                                    | 75                  |     |             | ns         |

| Clock Rise/Fall Time                            | $t_r$ , $t_f$     | CLOC                 | K                                      |                   |                                                                    |                     |     | 200         | ns         |

| Data Setup Time                                 | $t_{DS}$          | S <sub>IN</sub> , C  | LOCK                                   |                   |                                                                    | 100                 |     |             | ns         |

| Data Hold Time                                  | $t_{DH}$          | $S_{IN}$ , $C$       | LOCK                                   |                   |                                                                    | 50                  |     |             | ns         |

| Latch Pulse Width                               | $t_{WL}$          | LATC                 | Ħ                                      |                   |                                                                    | 100                 |     |             | ns         |

| Electrical Characteristic                       | s at T            | a=25°C               | <b></b>                                |                   |                                                                    |                     |     |             |            |

| "H"-Level Input Current                         |                   | I <sub>IH</sub> (1)  | Pin Na<br>S <sub>IN</sub> , CLOCK      | me                |                                                                    | min                 | typ | max<br>10   | unit<br>µA |

| "U" I aval Input Current                        |                   | I (2)                | LATCH<br>PEOLED at                     | a ala /T          | EOT)                                                               | 10                  |     | 50          |            |

| "H"-Level Input Current "L"-Level Input Current |                   | $I_{IH}(2)$          | BEO, LED-ch                            | ieck (1           | ES1)                                                               | 12                  |     | 72          | μA         |

| L -Level Input Current                          |                   | I <sub>IL</sub> (1)  | S <sub>IN</sub> , CLOCK<br>LATCH       |                   | - 4                                                                | -10<br>-72          |     |             | μA         |

| "L"-Level Input Current                         |                   | $I_{IL}(2)$          | STROBE                                 |                   | 九海                                                                 | -72                 |     | -12         | μΑ         |

| "H"-Level Output Voltage                        |                   | $V_{OH}$             | Sout                                   | $V_{DD}=$         | :ΣY, 🌉                                                             | $V_{\rm DD}$ -0.5   |     |             | V          |

| "L"-Level Output Voltage                        |                   | V <sub>OL</sub> (1)  | S <sub>OUT</sub>                       | V <sub>DD</sub> = |                                                                    |                     |     | 0.5         | V          |

| h= h =                                          |                   |                      |                                        |                   | ).5m <b>A</b>                                                      |                     |     |             |            |

| "L"-Level Output Voltage                        |                   | V <sub>OL</sub> (2)  | D1 to D32                              | V <sub>DD</sub> = | :5V,<br>80 mA                                                      |                     |     | 0.5         | V          |

| Output Off-State Leakage                        |                   | I <sub>OFF</sub>     | D1 to D32                              | V <sub>O</sub> =1 |                                                                    |                     |     | 20          | μΑ         |

| Current                                         |                   |                      |                                        |                   |                                                                    |                     |     |             | •          |

| Input Capacitance                               |                   | $C_{IN}$             |                                        | CLO               | CK                                                                 |                     | 5.0 |             | рF         |

| Operating Current Dissipa                       | tion              | $I_{DD}$             | $V_{DD}$                               | V <sub>DD</sub> = | =5V,                                                               |                     |     | 5           | mA         |

|                                                 |                   |                      |                                        |                   | :5MHz,<br>itputs: no lo                                            | hec                 |     |             |            |

| Switching Characteristic                        | s at T            | a=25°C               |                                        | ųn ot             | ipais. no i                                                        | ,aa                 |     |             |            |

|                                                 |                   | •                    | Pin Nar                                | ne                |                                                                    |                     | min | typ m       | ax unit    |

| Clock Latch Delay Width                         |                   | $t_{CL}$             | CLOCK, LA                              | TCH               | $V_{DD}=5V$                                                        |                     | 100 |             | ns         |

| Latch Clock Delay Width                         |                   | t <sub>LC</sub>      | CLOCK, L                               | ATCH              | $V_{DD}=5V$                                                        |                     | 0   |             | ns         |

| "H"-Level Output                                |                   | t <sub>PLH</sub> (1) |                                        |                   | V <sub>DD</sub> =5V,                                               |                     |     | 40          | 00 ns      |

| Propagation Delay Time                          |                   |                      | D1 to D32                              |                   | Dn: R <sub>L</sub> =1<br>CL=1                                      |                     |     | •           |            |

|                                                 |                   | t <sub>PLH</sub> (2) | BEO, STRO                              | DBE               | V <sub>DD</sub> =5V,<br>Dn: R <sub>L</sub> =1<br>CL=1              |                     |     | 30          | 00 ns      |

|                                                 |                   | t <sub>PLH</sub> (3) | CLOCK, So                              | UT                | V <sub>DD</sub> =5V,<br>S <sub>OUT</sub> : C <sub>L</sub> =        | =15pF               |     | 20          | 00 ns      |

| "L"-Level Output<br>Propagation Delay Time      |                   | t <sub>PHL</sub> (1) | LATCH,<br>D1 to D32                    |                   | V <sub>DD</sub> =5V,<br>Dn: R <sub>L</sub> =1<br>C <sub>L</sub> =1 | .0kΩ                |     | 20          | 00 ns      |

|                                                 |                   | t <sub>PHL</sub> (2) | BEO, STRO<br>D1 to D32                 | BE                | V <sub>DD</sub> =5V,<br>Dn: R <sub>L</sub> =1<br>C <sub>L</sub> =1 |                     |     | 10          | 00 ns      |

|                                                 |                   | t <sub>PHL</sub> (3) | CLOCK, So                              | our               | V <sub>DD</sub> =5V,<br>S <sub>OUT</sub> : C <sub>L</sub> =        | =15pF               |     | 20          | 00 ns      |

### **LED Driver On/Off Truth Table**

| Latch Data<br>(Q) | BEO | STROBE | LED Driver |

|-------------------|-----|--------|------------|

| 0                 | 0   | 0      | OFF        |

| 1                 | 0   | 0      | OFF        |

| 0                 | 1   | 0      | OFF        |

| 1                 | 1   | 0      | ON LED on  |

| 0                 | 0   | 1      | OFF        |

| 1                 | 0   | 1      | OFF        |

| 0                 | 1   | 1      | OFF        |

| 1                 | 1   | 1      | OFF        |

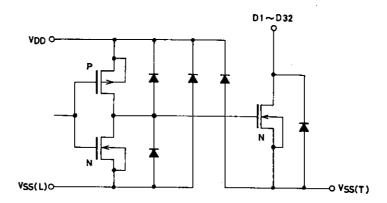

## **Equivalent Circuit Block Diagram**

## **Output Driver Section Equivalent Circuit**

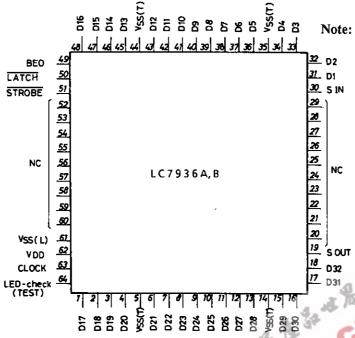

#### Pin Assignment

Note: Pins 24, 25 of NC pins are connected to the substrate (=V<sub>DD</sub>) and must be kept open. Other NC pins must be also kept open.

2 5 IN When the LED-check (TEST) pin is not in use, it must not be kept open, but must be connected to GND.

## Input Data Timing Chart

#### **Output Data Timing Chart**

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/orime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.