CMOS LSI

LC79400D

**Dot Matrix LCD Driver**

### **Overview**

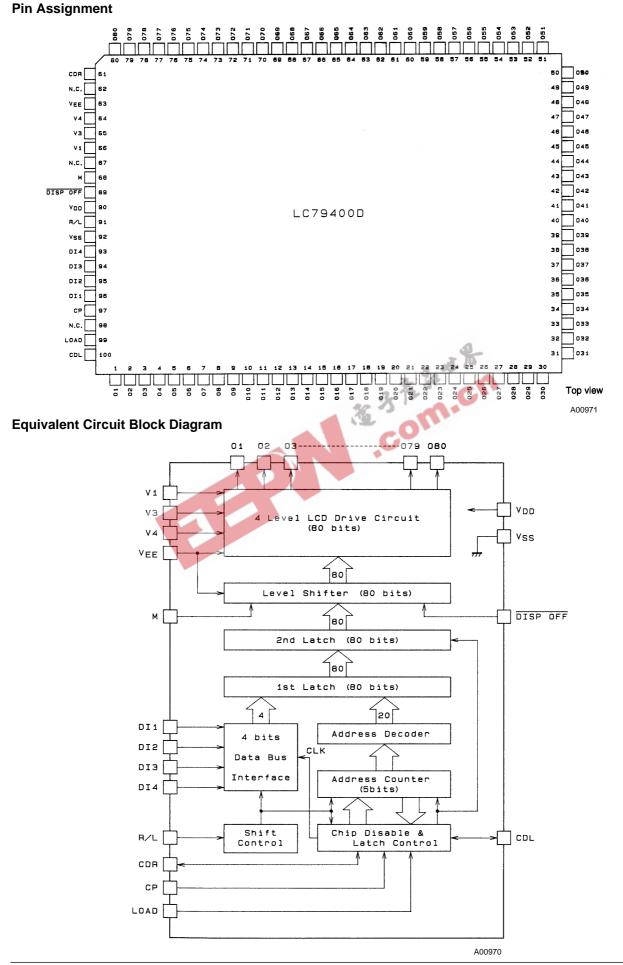

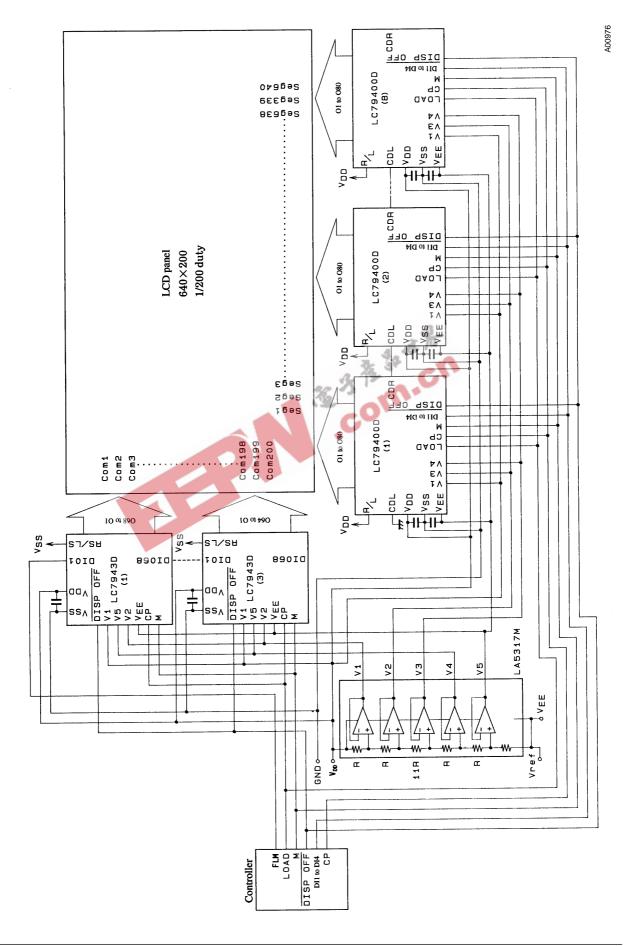

The LC79400D is a large-scale dot matrix LCD segment driver LSI. Display data transferred from the controller (4-bit parallel format) is processed through 80-bit latching and a LCD drive signal is generated. The LC79400D can be used in conjunction with common driver LC7943D (QIP80D) as well as LC79430D (QIP100D) and LC79431D (QIP100D) to drive a widescreen LCD panel.

### **Features**

- On-chip LCD drive circuit (80 bits)

- Display duty selection ranging from 1/64 to 1/256

- Supports use of chip disable pin for lower large panel power supply dissipation

- Supports externally supplied bias voltage

- Operating power supply voltage/operating temperature include

$V_{DD}$  (logic block) : 5 V ±10 % / -20 to +75 °C

$V_{DD}$ - $V_{EE}$  (LCD block) : 12 V to 32 V / -20 to +75°C

- Data transfer clock provides maximum 3.0 MHz and supports bidirectional shift

- 4-bit parallel data input

- CMOS process

- 100-pin flat plastic package

## **Specifications**

### Absolute Maximum Ratings at Ta = $25\pm2^{\circ}C$ , $V_{SS} = 0$ V

| Parameter                      | Symbol                                  | Conditions | Ratings                       | Unit |

|--------------------------------|-----------------------------------------|------------|-------------------------------|------|

| Maximum supply voltage (logic) | V <sub>DD</sub> max                     |            | -0.3 to +7.0                  | V    |

| Maximum supply voltage (LCD)   | V <sub>DD</sub> - V <sub>EE</sub> max*1 |            | 0 to 35                       | V    |

| Maximum input voltage          | V <sub>I</sub> max                      |            | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Storage temperature range      | Tstg                                    |            | -40 to +125                   | °C   |

Note:1. The voltages V<sub>1</sub>, V<sub>3</sub>, V<sub>4</sub>, V<sub>7</sub>, V<sub>DD</sub> and V<sub>EE</sub> must obey the relationships:  $V_{DD} \ge V1 > V3 > V4 > VEE$ ,  $V_{DD} - V3 \le 7V$ ,  $V4 - V_{EE} \le 7V$ .

## SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

### 0.3 0.3 0.3 0.3 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15 0.15

[LC73701M]

Package Dimensions

unit : mm

3180-QFP100D

| Parameter                | Symbol                            | Conditions                                       | min                 | typ | max                 | Unit |

|--------------------------|-----------------------------------|--------------------------------------------------|---------------------|-----|---------------------|------|

| Supply voltage (logic)   | V <sub>DD</sub>                   |                                                  | 4.5                 |     | 5.5                 | V    |

| Supply voltage (LCD)     | V <sub>DD</sub> - V <sub>EE</sub> | *2, *3                                           | 12                  |     | 32                  | V    |

| Input high-level voltage | VIH                               | DI1 to 4, CP, LOAD, CDR, CDL<br>R/L, M, DISP OFF | 0.8 V <sub>DD</sub> |     |                     | V    |

| Input low-level voltage  | VIL                               | DI1 to 4, CP, LOAD, CDR, CDL<br>R/L, M, DISP OFF |                     |     | 0.2 V <sub>DD</sub> | V    |

| CP (shift clock)         | f <sub>CP</sub>                   | СР                                               |                     |     | 3.0                 | MHz  |

| CP (pulse width)         | f <sub>WC</sub>                   | СР                                               | 100                 |     |                     | ns   |

| LOAD pulse width         | t <sub>WL</sub>                   | LOAD                                             | 100                 |     |                     | ns   |

| Setup time               | <sup>t</sup> SETUP                | DI1 to $4 \rightarrow CP$                        | 80                  |     |                     | ns   |

| Hold time                | tHOLD                             | DI1 to $4 \rightarrow CP$                        | 80                  |     |                     | ns   |

| $CP \rightarrow LOAD$    | t <sub>CL</sub> 1                 | $CP \rightarrow LOAD$                            | 0                   |     |                     | ns   |

| $CF \rightarrow LOAD$    | t <sub>CL</sub> 2                 | $CP \rightarrow LOAD$                            | 100                 |     |                     | ns   |

| $LOAD \to CP$            | t <sub>LC</sub>                   | $LOAD \rightarrow CP$                            | 63                  |     |                     | ns   |

|                          | t <sub>R</sub>                    | СР                                               |                     |     | 50                  | ns   |

| Rise/Fall time           | t <sub>F</sub>                    | СР                                               |                     |     | 50                  | ns   |

| RISE/Fall UITE           | t <sub>RL</sub>                   | LOAD                                             |                     |     | 50                  | ns   |

|                          | t <sub>FL</sub>                   | LOAD                                             |                     |     | 50                  | ns   |

### Allowable Operating Ranges at Ta = -20 to $+75^{\circ}C$ , $V_{SS} = 0$ V

Note: 2. The voltages  $V_1$ ,  $V_3$ ,  $V_4$ ,  $V_7$ ,  $V_{DD}$  and  $V_{EE}$  must obey the relationships:  $V_{DD} \ge V1 \ge V3 \ge V4 \ge V_{EE}$ ,  $V_{DD} = V3 \le 7V$ ,  $V4 = V_{EE} \le V_{EE}$ ,  $V_{DD} = V_{DD} \ge V_$ 7V.

When applying power, apply power to the LCD drive block after applying power to the logic block or apply power to both the blocks simultaneously. When turning off power, turn off power to the logic block after turning off power to the LCD drive block or turn off power to both the blocks simultaneously. 36

# Electrical Characteristics at Ta = 25±2°C, $V_{SS} = 0$ V, $V_{DD} = 5$ V±10%

| _                             |                    |                                                                                                    |                       |     |     |      |

|-------------------------------|--------------------|----------------------------------------------------------------------------------------------------|-----------------------|-----|-----|------|

| Parameter                     | Symbol             | Conditions                                                                                         | min                   | typ | max | Unit |

| Input high-level current      | III                | $V_{IN} = V_{DD}$ ; LOAD, CP, CDR (CDL),<br>R/L, DI1 to DI4, M, DISP OFF                           |                       |     | 1   | μA   |

| Input low-level current       | ηL                 | $V_{IN} = V_{SS}$ ; LOAD, CP, CDR (CDL),<br>R/L, D11 to DI4, M, DISP OFF                           | -1                    |     |     | μA   |

| Output high-level voltage     | V <sub>OH</sub>    | 1 <sub>OH</sub> = -400 μA; CDL (CDR)                                                               | V <sub>DD</sub> - 0.4 |     |     | V    |

| Output low-level voltage      | VOL                | I <sub>OL</sub> = 400 μA; CDL (CDR)                                                                |                       |     | 0.4 | V    |

| Driver en sister              | R <sub>ON</sub> 1  | $V_{DD} - V_{EE} = 30 \text{ V},  V_{DE} - V_O  = 0.5 \text{ V}^{*4};$<br>O1 to O80                |                       | 1.5 | 3.0 | kΩ   |

| Driver on resistor            | R <sub>ON</sub> 2  | $V_{DD} - V_{EE} = 20 \text{ V},  V_{DE} - V_{O}  = 0.5 \text{ V}^{*+};$<br>O1 to O80              |                       | 2.0 | 3.5 | kΩ   |

| Standby current dissipation   | I <sub>ST</sub>    | CDR (CDL) = $V_{DD}$ , $V_{DD} - V_{EE} = 30 V$<br>CP = 3.0 MHz, no-load output: $V_{SS}$          |                       |     | 200 | μA   |

|                               | I <sub>SS</sub> *5 | V <sub>DD</sub> – V <sub>EE</sub> = 30 V, CP = 3 MHz,<br>LOAD = 14 kHz, M = 35 Hz; V <sub>SS</sub> |                       |     | 4.0 | mA   |

| Operation current dissipation | I <sub>SS</sub> *6 | $V_{DD} - V_{EE} = 30 V$ , CP = 3 MHz,<br>LOAD = 14 kHz, M = 35 Hz; $V_{EE}$                       |                       |     | 0.1 | mA   |

| Input capacity                | Cl                 | f = 3.0 MHz; CP                                                                                    |                       | 5   |     | pF   |

Note: 4.  $V_{DE} = V1$  or V3 or V4 or  $V_{EE}$ , V1 =  $V_{DD}$ , V3 = 15/17 ( $V_{DD}$ - $V_{EE}$ ), V4 = 2/17 ( $V_{DD}$ - $V_{EE}$ )

5.  $I_{SS}$  current flows from  $V_{DD}$  to  $V_{SS}$ . 6.  $I_{EE}$  current flows from  $V_{DD}$  to  $V_{EE}$ .

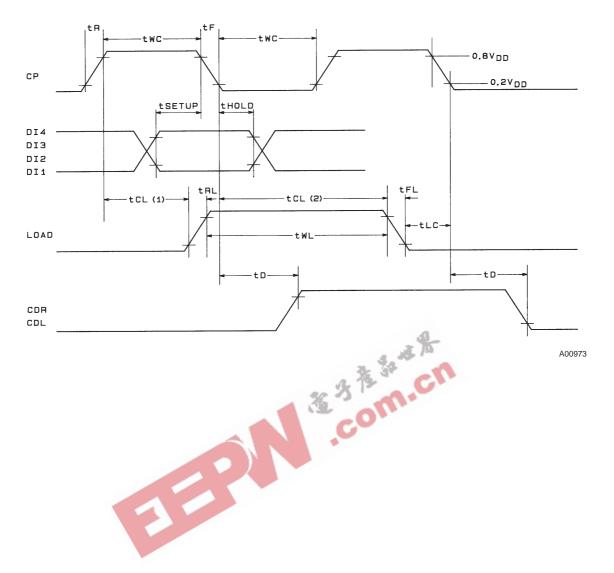

### Switching Characteristics at Ta = $25\pm2^{\circ}$ C, V<sub>SS</sub> = 0 V, V<sub>DD</sub> = 5 V $\pm10\%$

| Parameter         | Symbol         | Conditions              | min | typ | max | Unit |

|-------------------|----------------|-------------------------|-----|-----|-----|------|

| Output delay time | t <sub>D</sub> | Load = 15 pF; CDR (CDL) |     |     | 200 | ns   |

### **Pin Descriptions**

| Pin No | Pin name        | Input/Output | Functions                                                                                                                                                                                 |                                                                      |              |                 |                                                                                              |  |  |

|--------|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------|-----------------|----------------------------------------------------------------------------------------------|--|--|

| 90     | V <sub>DD</sub> |              | $V_{\text{DD}}$ and $V_{\text{SS}}$ : Power supply for logic section                                                                                                                      |                                                                      |              |                 |                                                                                              |  |  |

| 92     | V <sub>SS</sub> | Power supply |                                                                                                                                                                                           |                                                                      |              |                 |                                                                                              |  |  |

| 83     | V <sub>EE</sub> |              | $V_{\text{DD}}$ and $V_{\text{EE}}$ : Power supply for LCD drive circuit                                                                                                                  |                                                                      |              |                 |                                                                                              |  |  |

| 86     | V1              |              | LCD drive level power supply                                                                                                                                                              |                                                                      |              |                 |                                                                                              |  |  |

| 85     | V3              | Power supply | V1 and $V_{EE}$ : Select level                                                                                                                                                            |                                                                      |              |                 |                                                                                              |  |  |

| 84     | V4              |              |                                                                                                                                                                                           | V1 and V <sub>EE</sub> : Select level<br>V3 and V4 : Nonselect level |              |                 |                                                                                              |  |  |

| 97     | CP              | Input        |                                                                                                                                                                                           | ta shift clock                                                       |              | on the trailir  | na edae)                                                                                     |  |  |

| 81     | CDR             | Input/Output |                                                                                                                                                                                           |                                                                      | (inggoinig ( |                 | ig ougo)                                                                                     |  |  |

| 100    | CDL             | Input/Output | Chip disable pin<br>H level : Data not accepted                                                                                                                                           |                                                                      |              |                 |                                                                                              |  |  |

| 100    | CDL             | input/Output |                                                                                                                                                                                           |                                                                      |              |                 |                                                                                              |  |  |

|        |                 |              | L level : Data accepted                                                                                                                                                                   |                                                                      |              |                 |                                                                                              |  |  |

|        |                 |              | Pin Name                                                                                                                                                                                  | Input/Outpu                                                          |              |                 | Pin Description                                                                              |  |  |

|        |                 |              | CDR                                                                                                                                                                                       | Input                                                                | L            |                 | ut pin for the IC's internal disable F/F                                                     |  |  |

|        |                 |              | CDL                                                                                                                                                                                       | Output                                                               |              | Connects        | of the IC's internal disable F/F<br>to the next stage CDR pin whe<br>g a cascade connection. |  |  |

|        |                 |              | CDL                                                                                                                                                                                       | Input                                                                | н            |                 | ut pin for the IC's internal disable F/F                                                     |  |  |

|        |                 |              | CDR                                                                                                                                                                                       | Output                                                               |              |                 | of the IC's internal disable F/I                                                             |  |  |

|        |                 |              |                                                                                                                                                                                           |                                                                      | *            | Connects        | to the next stage CDL pin whe                                                                |  |  |

|        |                 |              |                                                                                                                                                                                           | -10                                                                  | 4 33-        | establishin     | g a cascade connection.                                                                      |  |  |

| 99     | LOAD            | Input        | Display data latch clock (triggering on the trailing edge). On the trail<br>edge, output levels switch in response to the particular combination<br>display data, M and DISP OFF signals. |                                                                      |              |                 |                                                                                              |  |  |

| 93     | DI4             | Input        | R/I                                                                                                                                                                                       |                                                                      | Input dat    | a and latch     | address                                                                                      |  |  |

| 94     | DI3             |              | R/L Input data and latch address                                                                                                                                                          |                                                                      |              |                 |                                                                                              |  |  |

| 95     | DI2             |              |                                                                                                                                                                                           |                                                                      | 03 04 05 0   | 6 07 08         | 077 078 079 0<br>1                                                                           |  |  |

| 96     | DI1             |              |                                                                                                                                                                                           |                                                                      |              |                 |                                                                                              |  |  |

|        |                 |              |                                                                                                                                                                                           |                                                                      | ]            | Ĺ               |                                                                                              |  |  |

|        |                 |              |                                                                                                                                                                                           | DI4                                                                  |              |                 |                                                                                              |  |  |

|        |                 |              | н                                                                                                                                                                                         |                                                                      |              |                 |                                                                                              |  |  |

|        |                 |              |                                                                                                                                                                                           |                                                                      |              |                 |                                                                                              |  |  |

| 88     | М               | Input        |                                                                                                                                                                                           | output alterna                                                       |              |                 |                                                                                              |  |  |

| 91     | R/L             | Input        | Input pin which performs input/output switching for CDR and CDL pins a directional shift for 4-bit parallel input data.                                                                   |                                                                      |              |                 |                                                                                              |  |  |

| 1      | 01              | Output       | LCD drive                                                                                                                                                                                 | output                                                               |              |                 |                                                                                              |  |  |

| 2      | O2              |              |                                                                                                                                                                                           |                                                                      |              |                 |                                                                                              |  |  |

|        |                 |              |                                                                                                                                                                                           |                                                                      |              |                 | DISP OFF signal can be u                                                                     |  |  |

|        |                 |              | to create o                                                                                                                                                                               | utput levels a                                                       | as shown be  | elow.           | _                                                                                            |  |  |

|        |                 |              | М                                                                                                                                                                                         | Q                                                                    | DISP OFF     | Output          | ]                                                                                            |  |  |

| 79     | O79             |              | L                                                                                                                                                                                         | L                                                                    | н            | V3              | 1                                                                                            |  |  |

| 80     | O80             |              | L                                                                                                                                                                                         | н                                                                    | Н            | V1              | 1                                                                                            |  |  |

|        |                 |              | H                                                                                                                                                                                         | L                                                                    | Н            | V4              | 1                                                                                            |  |  |

|        |                 |              | н                                                                                                                                                                                         | н                                                                    | н            | V <sub>EE</sub> | *Don't care                                                                                  |  |  |

|        |                 |              | *                                                                                                                                                                                         | *                                                                    | L            | VEE<br>V1       | (To be set to either "H" or "L                                                               |  |  |

|        |                 |              |                                                                                                                                                                                           |                                                                      | L            | V I             |                                                                                              |  |  |

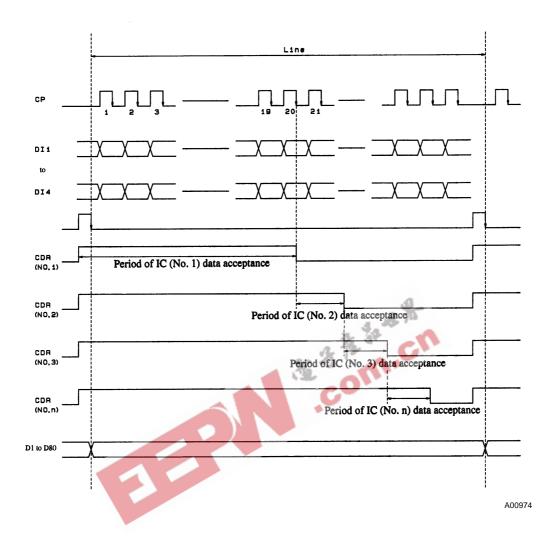

### **Operation Timing (for R/L = H)**

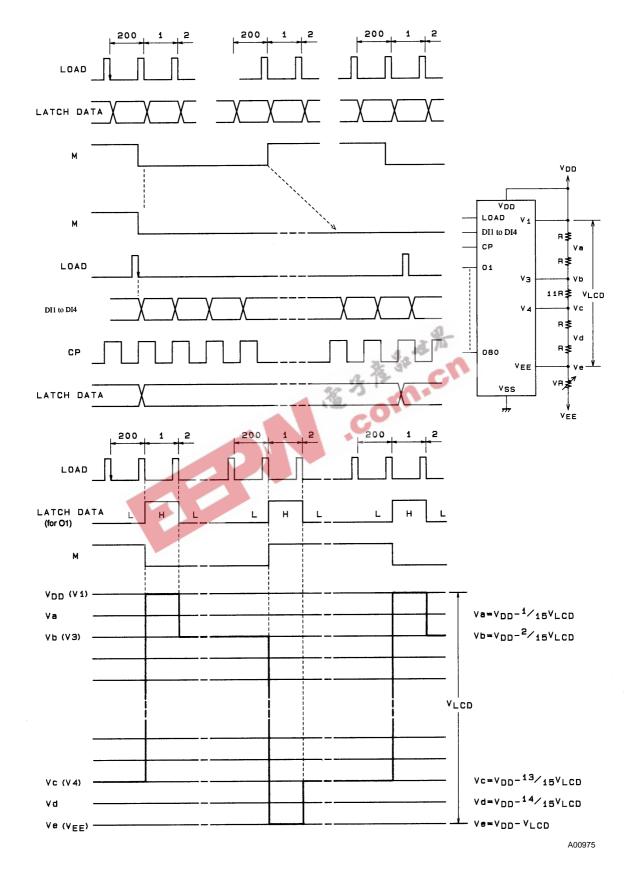

### Time Chart (1/200 Duty 1/15 Bias)Switching Characteristics

### LC79400D

Sample Application

### **Switching Characteristics**

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of November, 1997. Specifications and information herein are subject to change without notice.