## SANYO Semiconductors DATA SHEET

# Silicon Gate CMOS IC LC749450NW — Digital RGB Image Processor IC

### Overview

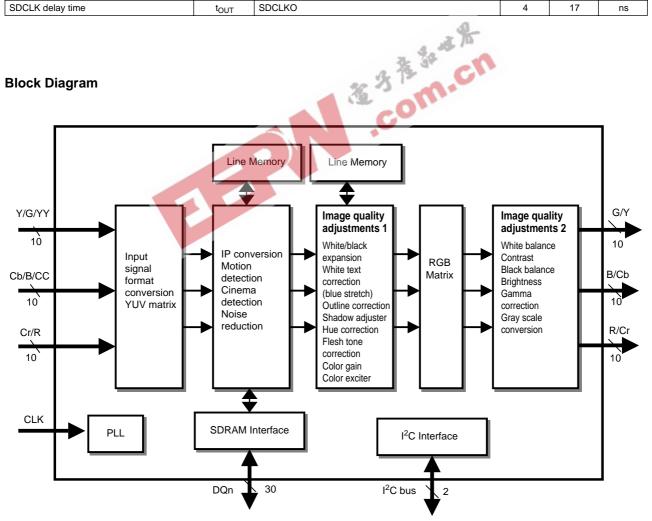

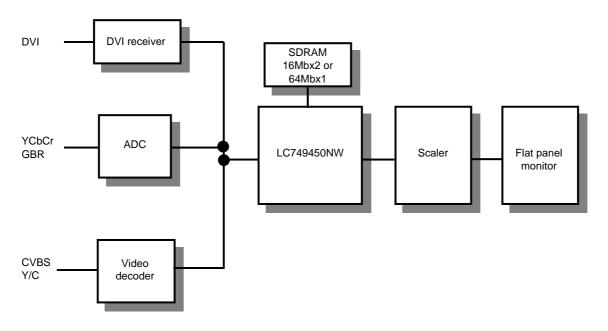

The LC749450NW RGB image processing IC converts interlaced video signals such as NTSC and PAL to progressive scan and adjusts the image quality of that signal. Since the LC749450NW can operate at input clock frequencies up to 27 MHz, it is optimal as a pixel display device IC for high-quality high-resolution images. A high image quality progressive scan signal playback system can be implemented easily by combining the LC749450NW with external memory (two 16M SDRAMs).

#### **Features**

- Accepts 30-bit (4:4:4) YCbCr signals, 20-bit (4:2:2) YCbCr signals, and 10-bit RT.656 signals as inputs.

- Supports digital TV inputs (480i, 480p, 1080i, and 720p): 30-bit YCbCr digital signal input.

- 30-bit digital RGB signal inputs

- Produces 30-bit and 24-bit digital RGB (or YCbCr) signal outputs

- Provides both YCbCr/YPbPr  $\rightarrow$  RGB conversion and RGB  $\rightarrow$  YCbCr conversion

- Motion adaptive jaggy-less interlaced to progressive conversion

- 3:2 pull down

- Multiple noise reduction systems (1D, 2D, and 3D)

- Cross color and cross luminance cancellers

- Horizontal outline correction (LTI and CTL)

- Sharpness (horizontal and vertical)

- Sharpness adjuster (shading relief enhancement)

- White and black level expansion, white text correction (blue stretch)

- Flesh tone correction

- Hue and color gain adjustments

- Color exciter (6-phase RGBYMC independent saturation adjustment)

- Brightness and contrast adjustment

- White balance and black balance adjustment

- Gamma correction (Independent RGB, programmable LUT system)

- Dithering (10-bit and 8-bit)

- Clamp control

- Aspect ratio conversion  $(4:3 \rightarrow 16:9)$

- Clock generator (PLL) circuit

- SDRAM interface

- I<sup>2</sup>C bus and CPU interface circuits

SDPIC<sup>TM</sup>: SANYO Digital Picture Improvement Core

SDPIC<sup>TM</sup> is a registered trademark of SANYO Electric Co., Ltd.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

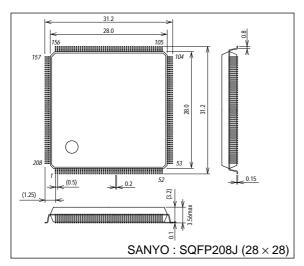

#### **Package Dimensions**

unit: mm 3261

### **IC Specifications**

Supply voltage: Core block: 1.8 V, I/O blocks: 3.3 V

Maximum operating frequency: 27 MHz (IP conversion mode), 135 MHz (IP conversion not used)

Package: 208-pin SQFP

Main Applications

LCD TVs, monitors, and projectors

PDP TVs and progressive scan TVs

### Main Applications

• DVD players and recorders

#### **Functional Overview**

1. Input signal formats

The digital data port supports the following input signal formats.

30-bit RGB

30-bit (4:4:4) YCbCr/YPbPr

20-bit (4:2:2) YCbCr/YPbPr

10-bit signals conforming to the ITU-R BT.656 standard (horizontal and vertical sync inputs required)

NTSC (480i/480p), PAL (576i/576p), and HD (1080i/720p) RGB (up to 135 MHz)

#### 2. IP conversion block

For NTSC (480i) and PAL (576i) inputs the LC749450NW provides motion adaptive IP conversion or cinema IP conversion (3:2 pull down) with both 2D/3D noise reduction and cross color/cross luminance cancellation. External SDRAM (either  $2 \times 16$  Mbits or  $1 \times 64$  Mbits) is required when the functions of this block are enabled. This block is set to bypass mode for 480p, 576p, 1080i, 720p, and PC (RGB) inputs.

#### (1) Motion adaptive IP conversion

The LC749450NW performs motion detection for each pixel that enters the IP conversion block. Based on that result, the block performs interlaced to progressive conversion. Pixels that are found to be static are interpolated between fields and pixels that are found to be moving are interpolated within the field.

Since this circuit takes correlations in the diagonal directions into account when performing inter-field interpolation for moving sections of the image, it can create smooth video with minimal stair-stepping artifacts (jaggies). Furthermore, this function can handle images that range from relaxed smooth video to video with violent motion by setting parameters and changing the motion threshold values for each pixel.

Continued from preceding page.

#### (2) Cinema mode IP conversion (3:2 pull down)

When an NTSC interlaced signal that was generated by a film (cinema) source is input, it automatically recognizes the signal as a cinema source and performs cinema mode IP conversion that is optimal for cinema sources. The threshold value for that recognition can be set with a parameter.

#### (3) Noise reduction (2D, 3D)

The LC749450NW provides three noise reduction functions: 3D noise reduction, which reduces noise between fields, 2D noise reduction, which reduces noise within the field, and 1D noise reduction, which reduces noise in the scan line direction. This block contains the 3D and 2D noise reduction functions and can operate independently for both the luminance signal and the chrominance signal.

#### (4) Cross color and cross luminance canceller

This circuit can reduce the cross color noise (rainbow-like color smearing) and cross luminance (dot) noise that is generated when a decoder (such as a 3-line decoder) other than 3D YC separator decoder is used for NTSC input. This function makes it possible to produce clear and vivid video with no color blotting and no dot interference.

#### 3. Image quality adjustment block

The LC749450NW provides a full complement of image quality adjustment functions and can perform the image quality adjustments required for optimal flat panel TV display.

#### (1) Horizontal outline correction (LTI/CTI)

The LTI/CTI block applies outline correction to the input signal. The apparent sharpness in the video image is enhanced by increasing the slope of the input signal. Since this function does not add overshoot or undershoot to edges in the video signal, it creates natural-looking images. This function operates independently on the luminance and chrominance signals.

#### (2) Sharpness (horizontal and vertical)

The sharpness function can correct the outlines in the input signal. This function differs from the LTI/CTI function described above in that it adds an appropriate peak in the corrected outline area. The amount of this peak and a coring level that prevents fine noise from being aggravated can be set in the control registers for this circuit. This function only operates on the luminance signal.

#### (3) Shadow adjuster

The shadow adjuster function detects the outlines in the input signal and adds an appropriate peak before and after the outline to add an appearance of a shadow. This creates a video signal that is varied and not dull.

#### (4) White and black expansion

The white and black expansion function adaptively expands the white and black levels in the Y component of the YCbCr signal using the white and black peak levels in the immediately preceding field, the luminance signal average picture level (APL), distributional information, and microcontroller settings. The white and black peaks are the maximum and minimum values in the input data within a single field. When the white and black expansion function is used, the values of the settings must be set appropriately.

### (5) White text correction (blue stretch)

The blue stretch function creates visually pleasing white text by adding a small amount of blue to white characters. A gain adjustment is applied to section of the Y signal recognized as white text and added to the Cb signal.

#### (6) Flesh tone correction

The flesh tone correction function extracts just the set skin color without affecting other colors and allows just that color to be adjusted.

### (7) Hues and color gain adjustment

The hue adjustment adjusts the hue of the whole image. The color gain adjustment adjusts the depth of the color by controlling the gain applied to the color difference signals. This function can adjust the Cb and Cr signals independently.

#### (8) Color exciter

The color exciter can independently control the red, green, blue, magenta, yellow, and cyan colors.

#### (9) Brightness and contrast controls

The brightness control adjusts the brightness of the screen as a whole and the contrast control adjusts the gain applied to the brightness.

#### (10) White balance and black balance adjustments

These adjust the appearance of white and black on the LCD panel.

#### (11) Gamma correction

This function allows the creation of arbitrary gamma curves to match the characteristics of the LCD panel used. The RGB channels can be adjusted independently, using internal programmable LUT.

#### (12) Dithering

The LC749450NW performs internal signal processing with a 10-bit precision. When these signals are output as 8-bit values, the lower two bits are rounded by dithering.

#### 4. Outputs and Other Functions

#### (1) Matrix conversion

The LC749450NW provides the following matrix conversion functions.

$YCbCr \rightarrow RGB$

$YPbPr \rightarrow RGB$

$YPbPr \rightarrow YCbCr$

$RGB \rightarrow YCbCr$

### (2) Aspect ratio conversion

xpander . An input Rec.601 signal (example: 720 × 240) can be expanded in the horizontal direction and displayed on a WVGA panel.

#### (3) Output formats

The LC749450NW can output video in the following formats.

Digital RGB (30 or 24 bits)

Digital YCbCr (30 or 24 bits)

#### (4) Clamp control

The LC749450NW can generate the clamp signals required for the front-end A/D converter. It can also generate arbitrary pulses (high, low, or high impedance) by comparing with an IC internal threshold value (that can be set with a register setting).

#### (5) SDRAM interface

The LC749450NW includes an SDRAM interface that can directly connect either:

Two 16 Mbit SDRAMs (512 words  $\times$  16 bits  $\times$  2 banks)

One 64 Mbit SDRAM (512 words  $\times$  32 bits  $\times$  4 banks).

This allows end product systems to be constructed easily.

SDRAMs with a speed grade of 70 or better must be used.

### (6) I<sup>2</sup>C bus interface and CPU interface

The LC749450NW is basically designed to be controlled by setting internal registers over the I<sup>2</sup>C bus.

The slave address can be switched to match the system by controlling pin 85 (SLADR).

The following slave addresses are supported.

SLADR = low: E0h

SLADR = high: E2h

Certain registers can also be controlled over the CPU interface.

### I/O Specifications

### Input Signals

| Signal type      | Number of pins | Symbol | Description                   | Notes                                                                  |

|------------------|----------------|--------|-------------------------------|------------------------------------------------------------------------|

| Video signals    | 10             | YIN    | Y or G                        | NTSC/PAL/DTV (4801, 480P, 1080I)                                       |

|                  | 10             | CBI    | Cb or B or C                  | or progressive scan RGB (up to SXGA)                                   |

|                  | 10             | CRI    | Cr or R or OSD                | or NTSC/PAL decoder input                                              |

| Sync signals     | 1              | DHS    | Horizontal sync signal        | Pixel sync horizontal sync signal input                                |

|                  |                |        |                               | The polarity can be switched by setting the DVPOLIN internal register. |

|                  | 1              | DVS    | Vertical sync signal          | Vertical sync signal input                                             |

|                  |                |        |                               | The polarity can be switched by setting the DVPOLIN internal register. |

| Data enable      | 1              | DEHI   | Data enable                   | Valid video period enable signal (horizontal/composite)                |

| signals          | 1              | DEVI   | Vertical data enable          | Valid video period enable signal (vertical)                            |

|                  | 1              | FIELD  | Field signal input            | Field signal input                                                     |

| Pixel clock      | 1              | CLKI   | Clock                         | System clock input                                                     |

| Fixed oscillator | 1              | DCLKI  | Used for the output dot clock | System clock input                                                     |

|                  | 1              | XTAL   |                               | Fixed clock input or test clock input                                  |

| System reset     | 1              | XRST   | System reset                  | System reset input, active low                                         |

| Total            | 40             | _      | _                             | _                                                                      |

### Output Signals

| Signal type    | Number of pins | Symbol  | Description             | Notes                                                                    |

|----------------|----------------|---------|-------------------------|--------------------------------------------------------------------------|

| Video signals  | 10             | ODG     | G                       | RGB output                                                               |

|                | 10             | ODB     | В                       | The LC749450NW also supports dithered 8-bit output.                      |

|                | 10             | ODR     | R                       |                                                                          |

| Sync signals   | 1              | DHO     | Horizontal sync signal  | This pin outputs the DHS pin input after a delay. (Used for pixel sync.) |

|                |                |         |                         | (This can be set over the I <sup>2</sup> C bus.)                         |

|                | 1              | DVO     | Vertical sync signal    | Outputs a vertical pixel sync signal.                                    |

| Data enable    | 1              | AREA    | Data enable             | Outputs a valid area signal.                                             |

| signals        |                |         |                         | 20 0                                                                     |

| Pixel clocks   | 1              | CLKOUT  | Outputs the input clock | The polarity can be inverted.                                            |

| Clamp pulse    | 1              | CLAMPO  | For A/D conversion      | Outputs a pulse signal used for A/D conversion clamp period verification |

| signals        |                |         |                         |                                                                          |

| Clamp levels   | 1              | CLPG    | Y/G clamp level         | Clamp level discrimination output                                        |

|                | 1              | CLPB    | Cb/B clamp level        | (Too large: low, too small: high, match: high-impedance)                 |

|                | 1              | CLPR    | Cr/R clamp level        |                                                                          |

| Field          | 1              | ODEVPPO | Field discrimination    | Outputs an odd/even field discrimination signal                          |

| discrimination | 1              |         |                         | (Used when IP conversion is not used.)                                   |

| signals        |                |         |                         |                                                                          |

| Total          | 39             |         | _                       | _                                                                        |

### Control Signals

| Signal type                  | Number of pins | Symbol | Description     | Notes                                                                    |

|------------------------------|----------------|--------|-----------------|--------------------------------------------------------------------------|

| I <sup>2</sup> C bus signals | 1              | SDAIO  | Data bus        | Used for setting internal registers and reading out the internal status. |

|                              | 1              | SCLI   | Bus clock       | The slave address is "1110000+(R/W)".                                    |

|                              | 1              | SLADR  | Slave switching | Sets the I <sup>2</sup> C bus slave address.                             |

|                              |                |        |                 | Normally low, High: E2h, Low: E0h.                                       |

| Data output                  | 1              | OE     |                 | Data output enable signal                                                |

| signals                      |                |        |                 |                                                                          |

| XTAL                         | 1              | XTALSW |                 | This signal sets the XTAL clock pin input operation                      |

|                              |                |        |                 | High: The XTAL clock input signal is divided by 2.                       |

| Total                        | 5              | _      | _               | _                                                                        |

### SDRAM Control Signals

| Signal type    | Number of pins | Symbol | Description | Notes                                     |

|----------------|----------------|--------|-------------|-------------------------------------------|

| Clock signals  | 1              | SDCLKI |             | SDRAM clock input                         |

|                | 1              | SDCLKO |             | SDRAM clock output                        |

| Control system | 1              | SDRAS  |             | SDRAM row address strobe signal output    |

| signals        | 1              | SDCAS  |             | SDRAM column address strobe signal output |

|                | 1              | SDWE   |             | SDRAM write enable signal output          |

| Address system | 11             | SAD    |             | SDRAM address signal output               |

| signals        | 1              | SDBS   |             | SDRAM bank select signal output           |

| Data system    | 1              | SDDQM  |             | SDRAM data mask signal output             |

| signals        | 32             | SDQ    |             | SDRAM data input and output               |

| Total          | 50             | _      |             | _                                         |

### Other Signals

| Signal type  | Number of pins                                                                                                                        | Symbol    | Description      | Notes                                                    |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|----------------------------------------------------------|--|--|--|--|--|

| CPU and test | 4                                                                                                                                     | GP_ADR1   | GP address input | General-purpose parallel bus address input/test setting  |  |  |  |  |  |

| signals      | 4                                                                                                                                     | GP_ADR2   | GP address input | General-purpose parallel bus address input/test setting  |  |  |  |  |  |

|              | 8                                                                                                                                     | GP_IO     | GP I/O           | General-purpose parallel bus I/O or test circuit outputs |  |  |  |  |  |

|              | 1                                                                                                                                     | GP_WR     |                  | General-purpose parallel bus write enable                |  |  |  |  |  |

|              | 1                                                                                                                                     | GP_CS     |                  | General-purpose parallel bus chip select                 |  |  |  |  |  |

|              | 1                                                                                                                                     | GP_MOD    |                  | Internal register control method selection               |  |  |  |  |  |

|              |                                                                                                                                       |           |                  | High: Parallel bus mode                                  |  |  |  |  |  |

|              |                                                                                                                                       |           |                  | Low: I <sup>2</sup> C bus mode                           |  |  |  |  |  |

|              | 1                                                                                                                                     | GP_TST_SW |                  | General-purpose parallel bus I/O or test mode switching  |  |  |  |  |  |

|              |                                                                                                                                       |           |                  | High: Parallel bus mode                                  |  |  |  |  |  |

|              |                                                                                                                                       |           |                  | Low: Test mode                                           |  |  |  |  |  |

|              | 6                                                                                                                                     | TSTI      | Test input       | Test inputs. These pins are normally left open.          |  |  |  |  |  |

|              | 5                                                                                                                                     | TSTO      | Test output      | Test outputs. These pins are normally left open.         |  |  |  |  |  |

| Total        | 33                                                                                                                                    | _         | _                | (c) // (c)                                               |  |  |  |  |  |

|              | 6 TSTI Test input Test inputs. These pins are normally left open. 5 TSTO Test output Test outputs. These pins are normally left open. |           |                  |                                                          |  |  |  |  |  |

### **Specifications**

### Absolute Maximum Ragings at $V_{SS} = 0 \ V$

| Parameter                     | Symbol               | Conditions | Ratings                  | Unit |

|-------------------------------|----------------------|------------|--------------------------|------|

| Maximum aupply valtage (I/O)  | DV <sub>DD</sub> 33  |            | -0.3 to +3.96            | V    |

| Maximum supply voltage (I/O)  | AV <sub>DD</sub> 33  |            | -0.3 10 +3.90            | V    |

| Maximum aupply valtage (core) | DV <sub>DD</sub> 18  |            | -0.3 to +2.16            | V    |

| Maximum supply voltage (core) | DPV <sub>DD</sub> 18 |            | -0.3 10 +2.16            | ٧    |

| Input voltage                 | VI                   |            | -0.5 to 6.0              | ٧    |

| Output voltage                | Vo                   |            | $-0.3$ to $V_{DD} + 0.3$ | ٧    |

| Allowable power dissipation   | Pd max               |            | 1                        | W    |

| Storage temperature           | Tstg                 |            | -55 to +125              | °C   |

| Operating temperature         | Topr                 |            | -30 to +70               | °C   |

### Allowable Operating Ranges at $Ta = -30 \text{ to } +70^{\circ}\text{C}$

| Parameter             | Cumbal              | Conditions |      | Unit |      |      |  |

|-----------------------|---------------------|------------|------|------|------|------|--|

| Faranietei            | Symbol              | Conditions | min  | typ  | max  | UIII |  |

| Supply voltage (I/O)  | DV <sub>DD</sub> 33 |            | 3.15 | 3.3  | 3.45 | V    |  |

| Supply voltage (core) | V <sub>DD</sub> 18  |            | 1.71 | 1.8  | 1.89 | V    |  |

| Input voltage range   | V <sub>IN</sub>     |            | 0    |      | 5.5  | V    |  |

### Input and Output Pin Capacitance at $Ta=25^{\circ}C,\,V_{DD}=V_{I}=0~V$

| Parameter   | Symbol Conditions - |            | Ratings      |     |     | Linit |  |

|-------------|---------------------|------------|--------------|-----|-----|-------|--|

| Parameter   | Symbol              | Conditions | <b>a</b> min | typ | max | Unit  |  |

| Input pins  | C <sub>IN</sub>     | f = 1 MHz  | 70           |     | 10  | pF    |  |

| Output pins | C <sub>OUT</sub>    | f = 1 MHz  | -            |     | 10  | pF    |  |

| I/O pins    | C <sub>I/O</sub>    | f = 1 MHz  |              |     | 10  | pF    |  |

# DC Characteristics at $Ta = -30 \text{ to } +70^{\circ}\text{C}$ , $V_{DD}33 = 3.15 \text{ to } 3.45 \text{ V}$ , $V_{DD}18 = 1.71 \text{ to } 1.89 \text{ V}$

| Parameter                              | Symbol          | Conditions                                                        |                | Unit |      |       |  |

|----------------------------------------|-----------------|-------------------------------------------------------------------|----------------|------|------|-------|--|

| Farameter                              | Symbol          | Conditions                                                        | min            | typ  | max  | Offic |  |

| High-level input voltage               | V               | 5 V inputs                                                        | 2.0            |      | 5.5  | V     |  |

| High-level input voltage               | V <sub>IH</sub> | 5 V Schmitt inputs                                                | 1.50           |      | 5.5  | V     |  |

| Low level input voltage                | V               | 5 V inputs                                                        | -0.3           |      | 0.8  | V     |  |

| Low-level input voltage                | V <sub>IL</sub> | 5 V Schmitt inputs                                                | -0.3           |      | 0.90 | V     |  |

| Llieb level input everent              |                 | $V_I = V_{DD}$                                                    | -10            |      | +10  | μΑ    |  |

| High-level input current               | ſΉ              | V <sub>I</sub> = V <sub>DD</sub> , with pull-down resistor used   | +10            |      | +100 | μΑ    |  |

| Low-level input current                | I <sub>IL</sub> | $V_I = V_{SS}$                                                    | -10            |      | +10  | μΑ    |  |

| High level output voltage              | \/-··           | T08 type, I <sub>OH</sub> = -4 mA                                 | $V_{DD} - 0.8$ |      |      | V     |  |

| High-level output voltage              | V <sub>OH</sub> | T12 type, I <sub>OH</sub> = -8 mA                                 | $V_{DD} - 0.8$ |      |      | V     |  |

| Low-level output voltage               | .,              | T08 type, I <sub>OL</sub> = 4 mA                                  |                |      | 0.4  | V     |  |

| Low-level output voltage               | V <sub>OL</sub> | T12 type, I <sub>OL</sub> = 8 mA                                  |                |      | 0.4  | V     |  |

| Output leakage current I <sub>OZ</sub> |                 | In the high-impedance output state                                | -10            |      | +10  | μΑ    |  |

| Pull-down resistor                     | RDN             |                                                                   | 43             | 58   | 118  | kΩ    |  |

| Operating current drain                | IDDOP           | tck = 135 MHz                                                     |                | 500  |      | mA    |  |

| Static current drain *1                | IDDST           | Outputs open, V <sub>I</sub> = V <sub>SS</sub> or V <sub>DD</sub> |                | 300  |      | μΑ    |  |

<sup>\*1:</sup> Some input pins have a built-in pull-down resistor. Note that there are thus certain circuit structures for which the static current drain cannot be guaranteed.

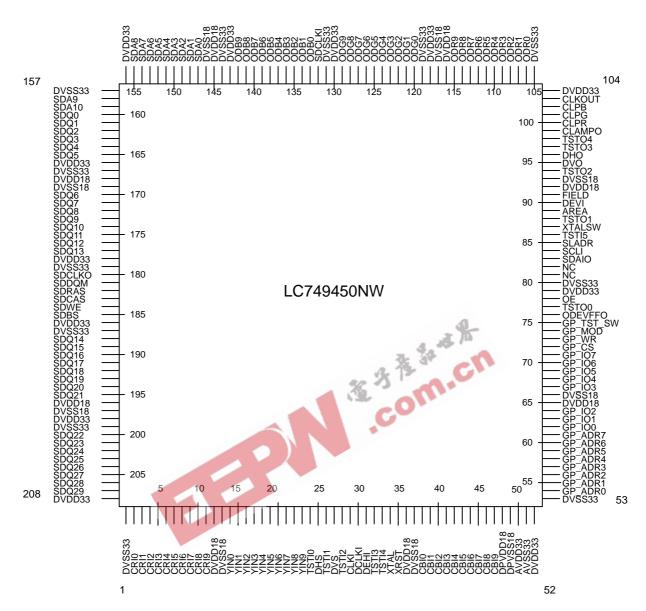

### **Pin Assignment**

Top view

### **Pin Listing**

| Pin No.  | Symbol                                     |        | circuit type | Connected to           | Notes                                                                |

|----------|--------------------------------------------|--------|--------------|------------------------|----------------------------------------------------------------------|

|          | -                                          | I/O    | Circuit type |                        |                                                                      |

| 1        | DV <sub>SS</sub> 33                        | P .    | _            | GND                    | 3.3 V system ground                                                  |

| 2        | CRI0                                       | I .    |              |                        |                                                                      |

| 3        | CRI1                                       | l      |              |                        |                                                                      |

| 4        | CRI2                                       | 1      |              |                        |                                                                      |

| 5        | CRI3                                       | - 1    |              |                        |                                                                      |

| 6        | CRI4                                       | - 1    | PHICD        | Digital interface      | Cr/R signal input                                                    |

| 7        | CRI5                                       | - 1    |              |                        |                                                                      |

| 9        | CRI6<br>CRI7                               | l<br>I |              |                        |                                                                      |

| 10       | CRI7                                       | ı      |              |                        |                                                                      |

| 11       | CRI9                                       | ı      |              |                        |                                                                      |

| 12       | DV <sub>DD</sub> 18                        | P      | _            | Power supply           | 1.8 V system power supply                                            |

| 13       | DV <sub>SS</sub> 18                        | P      | _            | GND                    | 1.8 V system ground                                                  |

| 14       | YIN0                                       | i      |              | OND                    | 1.0 v Gyotom ground                                                  |

| 15       | YIN1                                       | i      |              |                        |                                                                      |

| 16       | YIN2                                       | i      |              |                        |                                                                      |

| 17       | YIN3                                       | ı      |              |                        |                                                                      |

| 18       | YIN4                                       | ı      |              |                        | Y/G signal input                                                     |

| 19       | YIN5                                       | i      | PHICD        | Digital interface      | RT.656 input                                                         |

| 20       | YIN6                                       | i      |              |                        |                                                                      |

| 21       | YIN7                                       | i      |              |                        |                                                                      |

| 22       | YIN8                                       | ı      |              |                        |                                                                      |

| 23       | YIN9                                       | ı      |              |                        | 2_                                                                   |

| 24       | TSTI0                                      | ı      | PHICD        | Open                   | Test input. This pin is normally left open.                          |

| 25       | DHS                                        | 1      | PHICD        | ·                      | Horizontal sync signal (The polarity can be switched.)               |

| 26       | TSTI1                                      | ı      | PHICD        | Open                   | Test input. This pin is normally left open.                          |

| 27       | DVS                                        | I      | PHICD        | 4                      | Vertical sync signal (The polarity can be switched.)                 |

| 28       | TSTI2                                      | I      | PHISD        | Open                   | Test input. This pin is normally left open.                          |

| 29       | CLKI                                       | I      | PHIC         |                        | System clock                                                         |

| 30       | DCLKI                                      | I      | PHIC         |                        | System clock                                                         |

| 31       | DEHI                                       | I      | PHICD        |                        | Valid video period enable signal input                               |

| 32       | TSTI3                                      | I      | PHISD        | Open                   | Test input. This pin is normally left open.                          |

| 33       | TSTI4                                      | I      | PHICD        | Open                   | Test input. This pin is normally left open.                          |

| 34       | XTAL                                       |        | PHIC         |                        | Fixed clock connection                                               |

| 35       | XRST                                       | 1      | PHIS         | Initialization circuit | System reset (Reset on a low-level input)                            |

| 36       | DV <sub>DD</sub> 18                        | Р      |              | Power supply           | 1.8 V system power supply                                            |

| 37       | DV <sub>SS</sub> 18                        | Р      |              | GND                    | 1.8 V system ground                                                  |

| 38       | CBI0                                       | I      |              |                        |                                                                      |

| 39       | CBI1                                       | 1      |              |                        |                                                                      |

| 40       | CBI2                                       | - 1    |              |                        |                                                                      |

| 41       | CBI3                                       | I      |              |                        |                                                                      |

| 42       | CBI4                                       | I      | PHICD        | Digital interface      | Cb/B signal input                                                    |

| 43       | CBI5                                       | I      |              |                        |                                                                      |

| 44<br>45 | CBI6<br>CBI7                               | I      |              |                        |                                                                      |

|          |                                            | ı      |              |                        |                                                                      |

| 46<br>47 | CBI8<br>CBI9                               | ı      |              |                        |                                                                      |

| 48       | DPV <sub>DD</sub> 18                       | P      | _            | Power supply           | PLL 1.8 V digital system power supply                                |

| 49       | DPV <sub>DD</sub> 18                       | P      | _            | GND                    | PLL 1.8 V digital system ground                                      |

| 50       | AV <sub>DD</sub> 33                        | P      | _            | Power supply           | PLL 3.3 V analog system power supply                                 |

| 51       | AV <sub>DD</sub> 33<br>AV <sub>SS</sub> 33 | P      | _            | GND                    | PLL 3.3 V analog system power supply  PLL 3.3 V analog system ground |

| 52       | DV <sub>DD</sub> 33                        | P      |              | Power supply           | 3.3 V system power supply                                            |

| 53       | DV <sub>SS</sub> 33                        | P      | _            | GND                    | 3.3 V system ground                                                  |

| 54       | GP_ADR0                                    | ı      |              | <u> </u>               |                                                                      |

| 55       | GP_ADR1                                    | i      |              |                        |                                                                      |

| 56       | GP_ADR2                                    | i      |              |                        |                                                                      |

| 57       | GP_ADR3                                    | ı      | D            |                        | CPU address input or                                                 |

| 58       | GP_ADR4                                    | ı      | PHICD        |                        | Test mode subsidiary setting inputs                                  |

| 59       | GP_ADR5                                    | ı      |              |                        |                                                                      |

| 60       | GP_ADR6                                    | ı      |              |                        |                                                                      |

| 61       | GP_ADR7                                    | ı      |              |                        |                                                                      |

|          |                                            |        |              |                        |                                                                      |

Continued from preceding page.

| Pin No.           | Symbol                                     |              | Circuit type | Connected to        | Notes                                                                           |

|-------------------|--------------------------------------------|--------------|--------------|---------------------|---------------------------------------------------------------------------------|

|                   | OD 100                                     | 1/0          | Circuit type |                     |                                                                                 |

| 62                | GP_IO0                                     | В            | DUDTOO       |                     | CPU I/O or                                                                      |

| 63                | GP_IO1                                     | B<br>B       | PHBT08       |                     | Test circuit outputs                                                            |

| 64                | GP_IO2                                     | P            |              | Dawar ayanlı        | 4.0 V avietem neural gumbli                                                     |

| 65                | DV <sub>DD</sub> 18                        | P            | _            | Power supply        | 1.8 V system power supply                                                       |

| 66<br>67          | DV <sub>SS</sub> 18                        | В            | _            | GND                 | 1.8 V system ground                                                             |

|                   | GP_IO3                                     |              |              |                     |                                                                                 |

| 68                | GP_IO4                                     | В            | PHBT08       |                     | CPU I/O or                                                                      |

| 69                | GP_IO5                                     | B<br>B       | PUBIO        |                     | Test circuit outputs                                                            |

| 70<br>71          | GP_IO6                                     |              |              |                     |                                                                                 |

| 71                | GP_IO7<br>GP_CS                            | B<br>I       | PHICD        |                     | CDIT hus ship anable input                                                      |

| 73                |                                            | <u>'</u><br> | PHICD        |                     | CPU bus chip enable input  CPU bus write enable input                           |

| 74                | GP_WR                                      | <u>'</u>     | PHICD        |                     | CPU bus mode switch                                                             |

| 75                | GP_MOD<br>CPU_TST_SW                       | <u>'</u>     | PHISD        |                     | CPU/test mode switch                                                            |

| 76                | ODEVFFO                                    | 0            | PHOT08       |                     |                                                                                 |

| 77                | TSTO0                                      | 0            | PHOT12       | Onen                | Field discrimination signal output                                              |

|                   | OE                                         |              |              | Open                | Test output. This pin is normally left open.                                    |

| 78<br>79          |                                            | I<br>P       | PHISD        | Power supply        | Output enable                                                                   |

| 80                | DVD <sub>DD</sub> 33                       | P            | _            | GND                 | 3.3 V system power supply                                                       |

| 81                | DV <sub>SS</sub> 33<br>NC                  | Р            | _            |                     | 3.3 V system ground                                                             |

|                   | NC<br>NC                                   |              | _            | Open                | No connection                                                                   |

| 82<br>83          | SDAIO                                      | <u> </u>     | PHBT12       | Open                | No connection  I'C bus data I/O                                                 |

| 84                | SCLI                                       |              | PHISD        |                     | I <sup>2</sup> C bus clock input                                                |

| 85                |                                            | <u>'</u>     | PHISD        |                     | I²C bus slave address setting                                                   |

| 86                | SLADR<br>TST15                             | <u>'</u>     | PHISD        | Open                | Test input. This pin is normally left open.                                     |

| 87                | XTALSW                                     | <u>'</u><br> | PHISD        | Open                | XTAL clock pin input mode setting input                                         |

| 88                |                                            | 0            | PHOT08       | Open                | Test output. This pin is normally left open.                                    |

| 89                | TSTO1<br>AREAO                             | 0            | PHOT08       | Open                | Valid area signal output                                                        |

| 90                | DEVI                                       |              | PHICD        |                     | Vertical valid video period enable signal input                                 |

| 90 91             | FIELD                                      | <u>'</u>     | PHICD        |                     | Field signal input                                                              |

| 92                | DV <sub>DD</sub> 18                        | P            | — —          | Power supply        | 1.8 V system power supply                                                       |

| 93                | DV <sub>DD</sub> 18<br>DV <sub>SS</sub> 18 | P            |              | GND                 | 1.8 V system ground                                                             |

| 94                | TSTO2                                      | 0            | PHOT08       | Open                | Test output. This pin is normally left open.                                    |

| 95                | DVO                                        | 0            | PHOT08       | Орен                | Vertical sync signal output (The polarity can be switched.)                     |

| 96                | DHO                                        | 0            | PHOT08       |                     | Horizontal sync signal output (The polarity can be switched.)                   |

| 97                | TSTO3                                      | 0            | PHOT08       | Open                | Test output. This pin is normally left open.                                    |

| 98                | TSTO4                                      | 0            | PHOT08       | Open                | Test output. This pin is normally left open.                                    |

| 99                | CLAMPOO                                    | 0            | PHOT08       | Ороп                | A/D conversion clamp period verification pulse output                           |

| 100               | CLPR                                       | 0            | PHOT12       |                     | Clamp control output (R/Cr)                                                     |

| 101               | CLPG                                       | 0            | PHOT12       |                     | Clamp control output (G/Y)                                                      |

| 102               | CLPB                                       | 0            | PHOT12       |                     | Clamp control output (B/Cb)                                                     |

| 103               | CLKOUT                                     | 0            | PHOT12       |                     | Clock output                                                                    |

| 104               | DV <sub>DD</sub> 33                        | P            | _            | Power supply        | 3.3 V system power supply                                                       |

| 105               | DV <sub>SS</sub> 33                        | Р            | _            | GND                 | 3.3 V system ground                                                             |

| 106               | ODR0                                       | 0            |              |                     | , • • • • • • • • • • • • • • • • •                                             |

| 107               | ODR1                                       | 0            |              |                     |                                                                                 |

| 108               | ODR2                                       | 0            |              |                     |                                                                                 |

| 109               | ODR3                                       | 0            |              |                     |                                                                                 |

| 110               | ODR4                                       | 0            |              |                     |                                                                                 |

| 111               | ODR5                                       | 0            | PHOT08       |                     | R signal outputs                                                                |

| 112               | ODR6                                       | 0            |              |                     |                                                                                 |

|                   | ODR7                                       | 0            |              |                     |                                                                                 |

| 113               |                                            | 0            |              |                     |                                                                                 |

| 113<br>114        | UDR8                                       | -            | ı            |                     |                                                                                 |

| 114               | ODR8<br>ODR9                               | 0            |              |                     |                                                                                 |

| 114<br>115        | ODR9                                       | O<br>P       | _            | Power supply        | 1.8 V system power supply                                                       |

| 114<br>115<br>116 | ODR9<br>DV <sub>DD</sub> 18                |              | _<br>        | Power supply<br>GND | 1.8 V system power supply 1.8 V system ground                                   |

| 114<br>115        | ODR9                                       | Р            | _<br>        |                     | 1.8 V system power supply     1.8 V system ground     3.3 V system power supply |

Continued from preceding page.

| Pin No.    | Symbol              | 1/0                                              | Circuit type | Connected to | Notes                     |

|------------|---------------------|--------------------------------------------------|--------------|--------------|---------------------------|

| 120        | ODG0                | 0                                                | Circuit type |              |                           |

| 120        |                     | 0                                                |              |              |                           |

| 121<br>122 | ODG1<br>ODG2        | 0                                                | -            |              |                           |

| 123        |                     | 0                                                | -            |              |                           |

| 123        | ODG3<br>ODG4        | 0                                                | -            |              |                           |

| 125        | ODG4<br>ODG5        | 0                                                | PHOT08       |              | G signal outputs          |

|            |                     |                                                  | -            |              |                           |

| 126        | ODG6                | 0                                                |              |              |                           |

| 127        | ODG7                | 0                                                |              |              |                           |

| 128        | ODG8                | 0                                                | -            |              |                           |

| 129        | ODG9                | 0                                                |              | Dawas aveals | 2.2.1/                    |

| 130        | DV <sub>DD</sub> 33 | P<br>P                                           | _            | Power supply | 3.3 V system power supply |

| 131        | DV <sub>SS</sub> 33 | <del>                                     </del> |              | GND          | 3.3 V system ground       |

| 132        | SDCLKI              | 1                                                | PHIC         |              | SDRAM system clock        |

| 133        | ODB0                | 0                                                |              |              |                           |

| 134        | ODB1                | 0                                                |              |              |                           |

| 135        | ODB2                | 0                                                |              |              |                           |

| 136        | ODB3                | 0                                                |              |              |                           |

| 137        | ODB4                | 0                                                | PHOT08       |              | B signal outputs          |

| 138        | ODB5                | 0                                                |              |              |                           |

| 139        | ODB6                | 0                                                |              |              |                           |

| 140        | ODB7                | 0                                                |              |              |                           |

| 141        | ODB8                | 0                                                |              |              |                           |

| 142        | ODB9                | 0                                                |              |              | 2                         |

| 143        | DV <sub>DD</sub> 33 | Р                                                | _            | Power supply | 3.3 V system power supply |

| 144        | DV <sub>SS</sub> 33 | Р                                                | _            | GND          | 3.3 V system ground       |

| 145        | DV <sub>DD</sub> 18 | Р                                                | _            | Power supply | 1.8 V system power supply |

| 146        | DV <sub>SS</sub> 18 | Р                                                | _            | GND          | 1.8 V system ground       |

| 147        | SAD0                | 0                                                |              |              | 132                       |

| 148        | SAD1                | 0                                                |              |              |                           |

| 149        | SAD2                | 0                                                |              |              |                           |

| 150        | SAD3                | 0                                                |              |              |                           |

| 151        | SAD4                | 0                                                | PHOT12       |              | SDRAM address outputs     |

| 152        | SAD5                | 0                                                |              |              |                           |

| 153        | SAD6                | 0                                                |              |              |                           |

| 154        | SAD7                | 0                                                |              |              |                           |

| 155        | SAD8                | 0                                                |              |              |                           |

| 156        | DV <sub>DD</sub> 33 | Р                                                |              | Power supply | 3.3 V system power supply |

| 157        | DV <sub>SS</sub> 33 | Р                                                | _            | GND          | 3.3 V system ground       |

| 158        | SAD9                | 0                                                | PHOT12       |              | SDRAM address outputs     |

| 159        | SAD10               | 0                                                | 1110112      |              | OBIVITY address surpus    |

| 160        | SDQ0                | В                                                |              |              |                           |

| 161        | SDQ1                | В                                                |              |              |                           |

| 162        | SDQ2                | В                                                | PHBT12       |              | SDRAM data I/O            |

| 163        | SDQ3                | В                                                | FMD172       |              | SUNAIVI Uala I/O          |

| 164        | SDQ4                | В                                                |              |              |                           |

| 165        | SDQ5                | В                                                |              |              |                           |

| 166        | DV <sub>DD</sub> 33 | Р                                                | _            | Power supply | 3.3 V system power supply |

| 167        | DV <sub>SS</sub> 33 | Р                                                | _            | GND          | 3.3 V system ground       |

| 168        | DV <sub>DD</sub> 18 | Р                                                | _            | Power supply | 1.8 V system power supply |

| 169        | DV <sub>SS</sub> 18 | Р                                                | _            | GND          | 1.8 V system ground       |

| 170        | SDQ6                | В                                                |              |              |                           |

| 171        | SDQ7                | В                                                | ]            |              |                           |

| 172        | SDQ8                | В                                                | ]            |              |                           |

| 173        | SDQ9                | В                                                | 1            |              |                           |

| 174        | SDQ10               | В                                                | PHBT12       |              | SDRAM clock output        |

| 175        | SDQ11               | В                                                |              |              |                           |

| 176        | SDQ12               | В                                                |              |              |                           |

| 177        | SDQ13               | В                                                |              |              |                           |

| 178        | DV <sub>DD</sub> 33 | Р                                                | _            | Power supply | 3.3 V system power supply |

| 179        | DV <sub>SS</sub> 33 | P                                                | _            | GND          | 3.3 V system ground       |

| 113        | L 2 4 8 8 9 9       | _ '                                              | _            | CIAD         | 0.0 v Gyotom ground       |

### Continued from preceding page.

| Pin No. Symbol      |                                                                                                                                                                                                                                                      | circuit type | Connected to | Notes                              |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|------------------------------------|--|--|--|

| ,                   | I/O                                                                                                                                                                                                                                                  | Circuit type |              |                                    |  |  |  |

|                     |                                                                                                                                                                                                                                                      |              |              | SDRAM clock output                 |  |  |  |

| SDDQM               | 0                                                                                                                                                                                                                                                    | PHOT12       |              | SDRAM data mask output             |  |  |  |

| SDRAS               | 0                                                                                                                                                                                                                                                    | PHOT12       |              | SDRAM row address strobe output    |  |  |  |

| SDCAS               | 0                                                                                                                                                                                                                                                    | PHOT12       |              | SDRAM column address strobe output |  |  |  |

| SDWE                | 0                                                                                                                                                                                                                                                    | PHOT12       |              | SDRAM write enable output          |  |  |  |

| SDBS                | 0                                                                                                                                                                                                                                                    | PHOT12       |              | SDRAM bank select output           |  |  |  |

| DV <sub>DD</sub> 33 | Р                                                                                                                                                                                                                                                    |              | Power supply | 3.3 V system power supply          |  |  |  |

| DV <sub>SS</sub> 33 | Р                                                                                                                                                                                                                                                    | _            | GND          | 3.3 V system ground                |  |  |  |

| SDQ14               | В                                                                                                                                                                                                                                                    |              |              |                                    |  |  |  |

| SDQ15               | В                                                                                                                                                                                                                                                    |              |              |                                    |  |  |  |

| SDQ16               | В                                                                                                                                                                                                                                                    |              |              |                                    |  |  |  |

| SDQ17               | В                                                                                                                                                                                                                                                    | DUDT12       |              | SDBAM alook output                 |  |  |  |

| SDQ18               | В                                                                                                                                                                                                                                                    | PHBIIZ       |              | SDRAM clock output                 |  |  |  |

| SDQ19               | В                                                                                                                                                                                                                                                    | ]            |              |                                    |  |  |  |

| 194 SDQ20 E         | В                                                                                                                                                                                                                                                    | 1            |              |                                    |  |  |  |

| SDQ21               | В                                                                                                                                                                                                                                                    | 1            |              |                                    |  |  |  |

| DV <sub>DD</sub> 18 | Р                                                                                                                                                                                                                                                    | _            | Power supply | 1.8 V system power supply          |  |  |  |

| DV <sub>SS</sub> 18 | Р                                                                                                                                                                                                                                                    | _            | GND          | 1.8 V system ground                |  |  |  |

| DV <sub>DD</sub> 33 | Р                                                                                                                                                                                                                                                    | _            | Power supply | 3.3 V system power supply          |  |  |  |

| DV <sub>SS</sub> 33 | Р                                                                                                                                                                                                                                                    | _            | GND          | 3.3 V system ground                |  |  |  |

| SDQ22               | В                                                                                                                                                                                                                                                    |              |              |                                    |  |  |  |

| SDQ23               | В                                                                                                                                                                                                                                                    | 1            |              |                                    |  |  |  |

| SDQ24               | В                                                                                                                                                                                                                                                    | 1            |              | 2_                                 |  |  |  |

| SDQ25               | В                                                                                                                                                                                                                                                    | DUDTAG       |              | CDDAM data 1/0                     |  |  |  |

| SDQ26               | В                                                                                                                                                                                                                                                    | PHBI12       |              | SDRAM data I/O                     |  |  |  |

| SDQ27               | В                                                                                                                                                                                                                                                    | 1            |              | 23                                 |  |  |  |

| SDQ28               | В                                                                                                                                                                                                                                                    | 1            |              | SDRAM data I/O                     |  |  |  |

| SDQ29               | В                                                                                                                                                                                                                                                    | 1            |              | Car Carlo                          |  |  |  |

| DV <sub>DD</sub> 33 | Р                                                                                                                                                                                                                                                    | _            | Power supply | 3.3 V system power supply          |  |  |  |

|                     |                                                                                                                                                                                                                                                      | 1            | 311          |                                    |  |  |  |

|                     | SDCLKO SDDQM SDRAS SDCAS SDWE SDBS DV <sub>DD</sub> 33 DV <sub>SS</sub> 33 SDQ14 SDQ15 SDQ16 SDQ17 SDQ18 SDQ20 SDQ21 DV <sub>DD</sub> 18 DV <sub>SS</sub> 18 DV <sub>DD</sub> 33 DV <sub>SS</sub> 33 SDQ22 SDQ25 SDQ25 SDQ27 SDQ26 SDQ27 SDQ28 SDQ29 | SDCLKO       |              |                                    |  |  |  |

### **Pin Circuits**

| I/O type | Function                                | Applicable pins                                                                                                       | Equivalent circuit |

|----------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------|

| PHIC     | 5 V input                               | CLKI, DCLKI, XTALI, SDCLKI                                                                                            |                    |

| PHIS     | 5 V Schmitt input                       | XRST                                                                                                                  |                    |

| PHICD    | 5 V pull-down resistor<br>input         | YIN0 to 9, CBI0 to 9, CRI0 to 9, GP_ADR0 to 7, DEHI, DEVI, DHS, DVS, FIELD, GP_CS, GP_WR, GP_MOD, TSTI0, TSTI1, TSTI4 |                    |

| PHISD    | 5 V pull-down resistor<br>Schmitt input | XTAL_SW, SCLI, SLADR, OE, CPU_TST_SW, TSTI2, TSTI3, TSTI5                                                             |                    |

| PHOT08   | 8 mA 3-state drive output               | ODR0 to 9, ODG0 to 9, ODB0 to 9, DHO, DVO, ODEVFFO, CLAMPOO, AREAO, TSTO1 to 4                                        |                    |

| POT08    | 8 mA 3-state drive output               | CLPB, CLPG, CLPR                                                                                                      |                    |

| PHOT12   | 12 mA 3-state drive output              | CLPB, CLPG, CLPR  CLKOUT, SAD0 to 10, SDCLKO, SDRAS, SDCAS, SDWE, SDDQM, SDBS, TSTO0                                  | m.c.               |

| РНВТ08   | 8 mA 3-state drive I/O                  | GP_IO0 to 7                                                                                                           |                    |

| PHBT12   | 12 mA 3-state drive I/O                 | SDQ0 to 29, SDAIO                                                                                                     |                    |

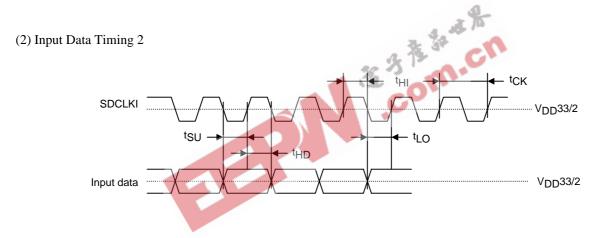

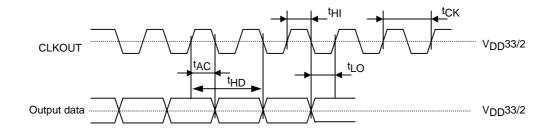

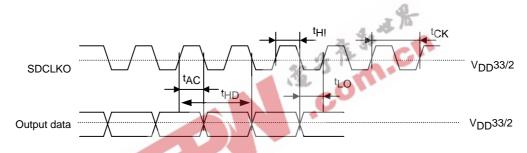

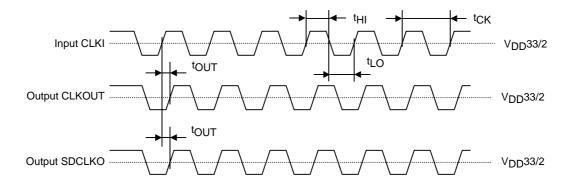

### **Input and Output Data Timing**

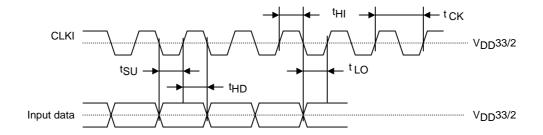

### (1) Input Data Timing 1

| Parameter             | Symbol          | Pins                             | min  | max | Unit |

|-----------------------|-----------------|----------------------------------|------|-----|------|

| Clock low-level time  | t <sub>LO</sub> |                                  | 3.70 |     | ns   |

| Clock high-level time | t <sub>HI</sub> | CLKI                             | 3.70 | _   | ns   |

| Clock period          | t <sub>CK</sub> |                                  | 7.40 | _   | ns   |

| Input data setup time | t <sub>SU</sub> | YIN [9:0], CBI [9:0], CRI [9:0], | 2.5  | _   | ns   |