#### GENERAL DESCRIPTION

The M2080/81/82 and M2085/86/87 are VCSO (Voltage

Controlled SAW Oscillator) based clock PLLs designed for FEC clock ratio translation in 10Gb optical systems such as OC-192 or 10GbE. They support FEC (Forward Error Correction) clock multiplication ratios, both forward (mapping) and

inverse (de-mapping). Multiplication ratios are pin-selected from pre-programming look-up tables.

#### **FEATURES**

- ◆ Integrated SAW delay line; Output of 15 to 700 MHz \*

- ◆ Low phase jitter < 0.5 ps rms typical (12kHz to 20MHz or 50kHz to 80MHz)

- ◆ LVPECL clock output (CML and LVDS options available)

- ◆ Pin-selectable PLL divider ratios support FEC ratios

- M2080/85: OTU1 (255/238) and OTU2 (255/237) Mapping M2081/86: OTU1 (238/255) or OTU2 (237/255) De-mapping M2082/87: OTU1 (238/255) and OTU2 (237/255) De-mapping

- ◆ Reference clock inputs support differential LVDS, LVPECL, as well as single-ended LVCMOS, LVTTL

- ◆ Loss of Lock (LOL) output pin; Narrow Bandwidth control input (NBW pin)

- ◆ AutoSwitch (AUTO pin) automatic (non-revertive) reference clock reselection upon clock failure

- ◆ Acknowledge pin (REF\_ACK pin) indicates the actively selected reference input

- ◆ Options for Hitless Switching (HS) with or without Phase Build-out (PBO) to enable SONET (GR-253) /SDH (G.813) MTIE and TDEV compliance during reselection

- ♦ Single 3.3V power supply

- ◆ Small 9 x 9 mm SMT (surface mount) package

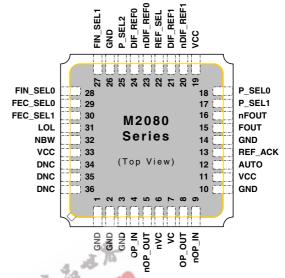

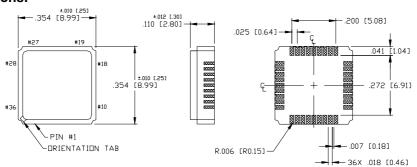

### PIN ASSIGNMENT (9 x 9 mm SMT)

Figure 1: Pin Assignment

#### Example I/O Clock Frequency Combinations Using M2081-11-622.0800 FEC De-Map Ratios

| FEC De-Map<br>PLL Ratio<br>Mfec / Rfec | Base Input Rate <sup>1</sup><br>(MHz) | Output Clock<br>(either output)<br>MHz |

|----------------------------------------|---------------------------------------|----------------------------------------|

| 1/1                                    | 622.0800                              | 622.08                                 |

| 237/255                                | 666.5143                              | or                                     |

| 238/255                                | 669.3266                              | 155.52                                 |

Table 1: Example I/O Clock Frequency Combinations

Note 1: Input reference clock can be the base frequency shown divided by "Mfin" (as shown in Tables 3 and 4 on pg. 3).

#### SIMPLIFIED BLOCK DIAGRAM

Figure 2: Simplified Block Diagram

<sup>\*</sup> Specify VCSO center frequency at time of order.

### VCSO FEC PLL with AutoSwitch for SONET/OTN

Preliminary Information

#### **PIN DESCRIPTIONS**

| 8 OP_6 6 nVC 7 VC 11, 19, 33 VCC             | IN Input OUT Output Input Power             | Internal pull-down resistor <sup>1</sup> | Power supply ground connections.  External loop filter connections.  See Figure 5, External Loop Filter, on pg. 9.  Power supply connection, connect to +3.3V.  Automatic/manual reselection mode for clock input:  Logic 1 automatic reselection upon clock failure  (non-revertive)  Logic 0 manual selection only (using REF_SEL)  Reference Acknowledgement pin for input mux state; outputs |

|----------------------------------------------|---------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9 nOP 5 nOP 8 OP_0 6 nVC 7 VC 11, 19, 33 VCC | OUT Output Input Power  Input  Input  Input | Internal pull-down resistor <sup>1</sup> | See Figure 5, External Loop Filter, on pg. 9.  Power supply connection, connect to +3.3V.  Automatic/manual reselection mode for clock input: Logic 1 automatic reselection upon clock failure (non-revertive) Logic 0 manual selection only (using REF_SEL)  Reference Acknowledgement pin for input mux state; outputs                                                                         |

| 8 OP_6 6 nVC 7 VC 11, 19, 33 VCC             | OUT Output Input Power  Input               | Internal pull-down resistor <sup>1</sup> | See Figure 5, External Loop Filter, on pg. 9.  Power supply connection, connect to +3.3V.  Automatic/manual reselection mode for clock input: Logic 1 automatic reselection upon clock failure (non-revertive) Logic 0 manual selection only (using REF_SEL)  Reference Acknowledgement pin for input mux state; outputs                                                                         |

| 7 VC<br>11, 19, 33 VCC<br>12 AUTC            | Power  O Input                              | Internal pull-down resistor <sup>1</sup> | Automatic/manual reselection mode for clock input:  Logic 1 automatic reselection upon clock failure (non-revertive)  Logic 0 manual selection only (using REF_SEL)  Reference Acknowledgement pin for input mux state; outputs                                                                                                                                                                  |

| 12 AUTO                                      | O Input                                     | Internal pull-down resistor <sup>1</sup> | Automatic/manual reselection mode for clock input: Logic 1 automatic reselection upon clock failure (non-revertive) Logic 0 manual selection only (using REF_SEL) Reference Acknowledgement pin for input mux state; outputs                                                                                                                                                                     |

|                                              | <u> </u>                                    | ·<br>                                    | Logic 1 automatic reselection upon clock failure (non-revertive) Logic 0 manual selection only (using REF_SEL) Reference Acknowledgement pin for input mux state; outputs                                                                                                                                                                                                                        |

|                                              | _ACK Outpu                                  | t .                                      | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                          |

| 13 REF_                                      |                                             | •                                        | the currently selected reference input pair: Logic 1 indicates nDIF_REF1, DIF_REF1 Logic 0 indicates nDIF_REF0, DIF_REF0                                                                                                                                                                                                                                                                         |

| 15 FOUT<br>16 nFOU                           | UT Outpu                                    | t No internal terminator                 | Clock output pair. Differential LVPECL.                                                                                                                                                                                                                                                                                                                                                          |

| 17 P_SE<br>18 P_SE<br>25 P_SE                | ELO Input                                   | Internal pull-down resistor <sup>1</sup> | Post-PLL , P divider selection. LVCMOS/LVTTL. See Table 8, P Divider Look-Up Table (LUT), on pg. 4.                                                                                                                                                                                                                                                                                              |

| 20 nDIF                                      | _REF1                                       | Biased to Vcc/2 2                        | Reference clock input pair 1. Differential LVPECL or LVDS.                                                                                                                                                                                                                                                                                                                                       |

| 21 DIF_                                      | REF1 Input                                  | Internal pull-down resistor <sup>1</sup> | Resistor bias on inverting terminal supports TTL or LVCMOS.                                                                                                                                                                                                                                                                                                                                      |

| 22 REF_                                      | _SEL Input                                  | Internal pull-down resistor <sup>1</sup> | Reference clock input selection. LVCMOS/LVTTL: Logic 1 selects DIF_REF1, nDIF_REF1. Logic 0 selects DIF_REF0, nDIF_REF0.                                                                                                                                                                                                                                                                         |

| 23 nDIF                                      | _REF0                                       | Biased to Vcc/2 <sup>2</sup>             | Reference clock input pair 0. Differential LVPECL or LVDS.                                                                                                                                                                                                                                                                                                                                       |

| 24 DIF_I                                     | REF0 Input                                  | Internal pull-down resistor <sup>1</sup> | = D'                                                                                                                                                                                                                                                                                                                                                                                             |

|                                              | SEL1<br>SEL0 Input                          | Internal pull-down resistor <sup>1</sup> | Input clock frequency selection. LVCMOS/LVTTL. See Tables 3 and 4 Mfin Divider Look-Up Tables (LUT) on pg. 3.                                                                                                                                                                                                                                                                                    |

|                                              | _SEL0<br>_SEL1 Input                        | Internal pull-down resistor <sup>1</sup> | Mfec and Rfec divider value selection. LVCMOS/ LVTTL.<br>See Tables 5, 6, and 7 on pg. 3.                                                                                                                                                                                                                                                                                                        |

| 31 LOL                                       | Outpu                                       | t                                        | Loss of Lock indicator output. Asserted when internal PLL is not tracking the input reference for frequency and phase. <sup>3</sup> Logic 1 indicates loss of lock. Logic 0 indicates locked condition.                                                                                                                                                                                          |

| 32 NBW                                       | <i>l</i> Input                              | Internal pull-UP resistor <sup>1</sup>   | Narrow Bandwidth enable. LVCMOS/LVTTL: Logic 1 - Narrow loop bandwidth, $R_{\text{IN}}$ = 2100k $\Omega$ Logic 0 - Wide bandwidth, $R_{\text{IN}}$ = 100k $\Omega$                                                                                                                                                                                                                               |

| 34, 35, 36 DNC                               |                                             | Do Not Connect.                          |                                                                                                                                                                                                                                                                                                                                                                                                  |

Note 1: For typical values of internal pull-down and pull-UP resistors, see **DC Characteristics** on pg. 11.

Table 2: Pin Descriptions

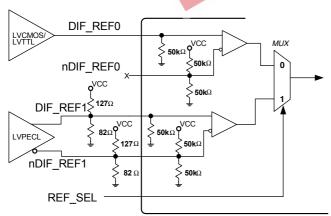

Note 2: Biased to Vcc/2, with  $50k\Omega$  to Vcc and  $50k\Omega$  to ground. See **Differential Inputs Biased to VCC/2** on pg. 11.

Note 3: See **LVCMOS Outputs** in DC Characteristics on pg. 11.

### VCSO FEC PLL with AutoSwitch for SONET/OTN

Preliminary Information

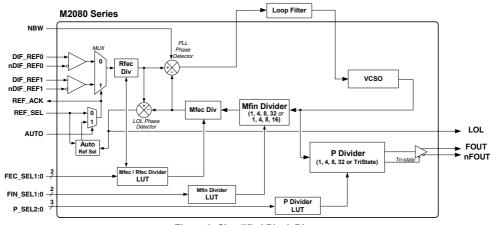

#### **DETAILED BLOCK DIAGRAM**

Figure 3: Detailed Block Diagram

#### **DIVIDER SELECTION TABLES**

#### Mfin Divider Look-Up Tables (LUT)

The FIN\_SEL1:0 pins select the feedback divider value ("Mfin"), which sets the overall PLL ratio range. Since the VCSO frequency is fixed, this allows input reference selection. The look-up tables vary by device variant.

#### M2080/81/82: Mfin Value LUT (Includes Divide by 32)

| FIN_ | SEL1: | Mfin<br>Value | Sample Input Reference Freq. (MHz) Options<br>For M2080 <sup>1</sup> , M2081 & M2082 <sup>2</sup> |

|------|-------|---------------|---------------------------------------------------------------------------------------------------|

| 0    | 0     | 32            | 19.44                                                                                             |

| 0    | 1     | 8             | 77.76                                                                                             |

| 1    | 0     | 4             | 155.52                                                                                            |

| 1    | 1     | 1             | 622.08                                                                                            |

Table 3: M2080/81/82: Mfin Value LUT (Includes Divide by 32)

Note 1: For M2080 with Fvcso = 666.5143 or 669.3266 Note 2: For M2081 and M2082 with Fvcso = 622.0800.

#### M2085/86/87: Mfin Value LUT (Includes Divide by 16)

| FIN. | FIN_SEL1:0 Mfin<br>Value |   | Mfin<br>Value | Sample Input Reference Freq. (MHz) Options<br>For M2085 <sup>1</sup> , M2086 & M2087 <sup>2</sup> |  |  |  |  |  |

|------|--------------------------|---|---------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0    | ) (                      | 0 | 16            | 38.88                                                                                             |  |  |  |  |  |

| 0    | ) .                      | 1 | 8             | 77.76                                                                                             |  |  |  |  |  |

| 1    | (                        | ) | 4             | 155.52                                                                                            |  |  |  |  |  |

| 1    |                          | 1 | 1             | 622.08                                                                                            |  |  |  |  |  |

Table 4: M2085/86/87: Mfin Value LUT (Includes Divide by 16)

Note 1: For M2085 with Fvcso = 666.5143 or 669.3266 Note 2: For M2086 and M2087 with Fvcso = 622.0800.

#### Mfec and Rfec Divider Look-Up Tables (LUTs)

The FEC\_SEL pins select the Mfec/Rfec divider ratio. The look-up tables vary by device variant. The Mfec and Rfec values also establish phase detector frequency. A lower phase detector frequency improves jitter tolerance and lowers loop bandwidth.

#### M2080/85: FEC Map LUT, OTU1 (255/238) and OTU2 (255/237)

| FEC_SEL1:0<br>1 0 Mfec F |       | Rfec | Description | Base Input<br>Rate (MHz)           | Fvcso =<br>Base Output<br>Rate (MHz) |          |

|--------------------------|-------|------|-------------|------------------------------------|--------------------------------------|----------|

| Foi                      | M2080 | or M | 12085       | with Fvcso = 666.5143 (OTU         | 11 FEC rate):                        |          |

| 0                        | 0     | 15   | 14          | 255/238 OC-48 to OTU1 encode       | 622.08                               | 666.5143 |

| 0                        | 1     | 15   | 15          | OTU1 repeater or jitter attenuator | 666.5143                             | 666.5143 |

| Foi                      | M2080 | or M | 12085       | with Fvcso = 669.3266 (OTU         | 2 FEC rate):                         |          |

| 1                        | 0     | 85   | 79          | 255/237 OC-192 to OTU2 encode      | 622.08                               | 669.3266 |

| 1                        | 1     | 85   | 85          | OTU2 repeater or jitter attenuator | 669.3266                             | 669.3266 |

Table 5: M2080/85: FEC Map LUT, OTU1 (255/238) and OTU2 (255/237)

# M2081/86: FEC De-map LUT, OTU1 (238/255) or OTU2 (237/255) Use this option for *either* OTU1 *or* OTU2 de-mapping applications, but not both.

| FEC_<br>1 | FEC_SEL1:0<br>1 0 |        | Rfec  | Description                          | Base Input<br>Rate (MHz) | Fvcso =<br>Base Output<br>Rate (MHz) |

|-----------|-------------------|--------|-------|--------------------------------------|--------------------------|--------------------------------------|

| For       | M208              | 1 or N | 12086 | with Fvcso = 622.08 (OTU1            | or OTU2 FEC              | rate):                               |

| 0         | 0                 | 79     | 85    | 237/255 OTU2 to OC-192 decode        | 669.3266                 | 622.08                               |

| 0         | 1                 | 79     | 79    | OC-192 repeater or jitter attenuator | 622.08                   | 622.08                               |

| 1         | 0                 | 14     | 15    | 238/255 OTU1 to OC-48 decode         | 666.5143                 | 622.08                               |

| 1         | 1                 | 14     | 14    | OC-48 repeater or jitter attenuator  | 622.08                   | 622.08                               |

Table 6: M2081/86: FEC De-map LUT, OTU1 (238/255) or OTU2 (237/255)

VCSO FEC PLL with AutoSwitch for SONET/OTN

Preliminary Information

#### M2082/87: FEC De-map LUT, Both OTU1 and OTU2

Use this option for *both* OTU1 or OTU2 de-mapping applications. The Mfec divider value is kept nearly constant to maintain similar loop bandwidth using one set of external filter component values.

| FEC_<br>1 | SEL1:0<br>0 | Mfec Rfec |       | Description                          | Base Input<br>Rate (MHz) | Fvcso =<br>Base Output<br>Rate (MHz) |

|-----------|-------------|-----------|-------|--------------------------------------|--------------------------|--------------------------------------|

| For       | M208        | 2 or N    | 12087 | with Fvcso = 622.08 (OTU1            | or OTU2 FEC              | c rate):                             |

| 0         | 0           | 79        | 85    | 237/255 OTU2 to OC-192 decode        | 669.3266                 | 622.08                               |

| 0         | 1           | 79        | 79    | OC-192 repeater or jitter attenuator | 622.08                   | 622.08                               |

| 1         | 0           | 84        | 90    | 238/255 OTU1 to OC-48 decode         | 666.5143                 | 622.08                               |

| 1         | 1           | 84        | 84    | OC-48 repeater or jitter attenuator  | 622.08                   | 622.08                               |

Table 7: M2082/87: FEC De-map LUT, Both OTU1 and OTU2

#### P Divider Look-Up Table (LUT)

The P\_SEL2:0 pins select the P divider values, which set the output clock frequency. A P divider of value of 1 will provide a 622.08MHz output when using a 622.08MHz VCSO, for example. P divider values of 4, 8, or 32 are also available, plus a TriState mode. The output can be placed into the valid states as listed in Table 8.

| P_ | SEL | 2:0 | P Value  | M2080-622.0800 or M2085-622.0800<br>Output Frequency (MHz) |

|----|-----|-----|----------|------------------------------------------------------------|

| 0  | 0   | 0   | 32       | 19.44                                                      |

| 0  | 0   | 1   | 32       | 19.44                                                      |

| 0  | 1   | 0   | 1        | 622.08                                                     |

| 0  | 1   | 1   | 4        | 155.52                                                     |

| 1  | 0   | 0   | 8        | 77.76                                                      |

| 1  | 0   | 1   | 4        | 155.52                                                     |

| 1  | 1   | 0   | 8        | 77.76                                                      |

| 1  | 1   | 1   | TriState | N/A                                                        |

Table 8: P Divider Look-Up Table (LUT)

#### **General Guidelines for Phase Detector Frequency**

The phase detector frequency (Fpd) is equal to the input reference frequency (Fref) divided by the Rfec divider value, or:

Fpd = Fref / Rfec

- A lower phase detector frequency should be used for loop timing applications to assure PLL tracking, especially during GR-253 jitter tolerance testing. The recommended maximum phase detector frequency for loop timing mode is 19.44MHz.

- When LOL is to be used for system health monitoring, the phase detector frequency should be 5MHz or greater. Low phase detector frequencies make LOL overly sensitive, and higher phase detector frequencies make LOL less sensitive. The LOL pin should not be used during loop timing mode.

- The preceding guideline also applies when using the AutoSwitch Mode, since AutoSwitch uses the LOL output for clock fault detection.

#### **FUNCTIONAL DESCRIPTION**

The M208x Series is a PLL (Phase Locked Loop) based clock generator that generates output clocks synchronized to one of two selectable input reference clocks.

An internal high "Q" SAW delay line provides low jitter signal performance and establishes the output frequency of the VCSO (Voltage Controlled SAW Oscillator). In a given M208x Series device, the VCSO center frequency is fixed. A common center frequency is 622.08MHz, for SONET or SDH optical network applications. The VCSO center frequency is specified at time of order (see "Ordering Information" on pg. 14). The VCSO has a guaranteed tuning range of  $\pm 120~\rm ppm$  (commercial temperature grade).

Pin selectable dividers are used within the PLL and for the output clock. This enables tailoring of device functionality and performance. The FEC feedback and reference dividers (the "Mfec Divider" and "Rfec Divider") provide the multiplication ratios necessary to accomodate clock translation for both forward and inverse Forward Error Correction. The Mfec and Rfec dividers also control the phase detector frequency. The feedback divider (labeled "Mfin Divider") provides the broader division options needed to accomodate various reference clock frequencies.

For example, the M2082-11-622.0800 (see "Ordering Information" on pg. 14) has a 622.08MHz VCSO frequency:

- The FEC de-mapper PLL ratios (in Tables 6 and 7) enable the M2082-11-622.0800 to accept "base" input reference frequencies of: 666.5143 (OTU1), 669.3266 (OTU2), and 622.08MHz (OC-192).

- The Mfin feedback divider enables the actual input reference clock to be the base input frequency divided by 1, 4, 8, or 32 or 16. Therefore, for the base input frequency of 622.08MHz, the actual input reference clock frequencies can be: 622.08, 155.52, 77.76, and 19.44 or 38.88MHz. (See Tables 3 and 4 on pg. 3.)

**Key to Device Variants and Look-up Table Options**

| ,                 |                                                                    |                             |  |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------|-----------------------------|--|--|--|--|--|--|

| Device<br>Variant | Look-up Table Option  Mfin Lookup Table is: Mfec Look-up Table is: |                             |  |  |  |  |  |  |

| M2080             | Table 3                                                            | Table 5 (FEC mapper LUT)    |  |  |  |  |  |  |

| M2081             | (includes divider value 32)                                        | Table 6 (FEC de-mapper LUT) |  |  |  |  |  |  |

| M2082             |                                                                    | Table 7 (FEC de-mapper LUT) |  |  |  |  |  |  |

| M2085             | Table 4                                                            | Table 5 (FEC mapper LUT)    |  |  |  |  |  |  |

| M2086             | (includes divider value 16)                                        | Table 6 (FEC de-mapper LUT) |  |  |  |  |  |  |

| M2087             |                                                                    | Table 7 (FEC de-mapper LUT) |  |  |  |  |  |  |

Table 9: Key to Device Variants and Look-up Table Options

The P divider scales the VCSO output enabling lower output frequency selections (Table 8).

### VCSO FEC PLL with AutoSwitch for SONET/OTN

Preliminary Information

The M208x Series includes a Loss of Lock (LOL) indicator, which provides status information to system management software. A Narrow Bandwidth (NBW) control pin is provided as an additional mechanism for adjusting PLL loop bandwidth without affecting the phase detector frequency.

Options are available for Hitless Switching (HS) with or without Phase Build-out (PBO). They provide SONET/SDH MTIE and TDEV compliance during a reference clock reselection.

#### **Input Reference Clocks**

Two clock reference inputs and a selection mux are provided. Either reference clock input can accept a differential clock signal (such as LVPECL or LVDS) or a single-ended clock input (LVCMOS or LVTTL on the non-inverting input).

A single-ended reference clock on the unselected reference input can cause an increase in output clock jitter. For this reason, differential reference inputs are preferred; interference from a differential input on the non-selected input is minimal.

Configuration of a single-ended input has been facilitated by biasing nDIF\_REF0 and nDEF\_REF1 to Vcc/2, with  $50k\Omega$  to Vcc and  $50k\Omega$  to ground. The input clock structure, and how it is used with either LVCMOS/LVTTL inputs or a DC- coupled LVPECL clock, is shown in Figure 4.

Figure 4: Input Reference Clocks

#### **Differential Inputs**

Differential LVPECL inputs are connected to both reference input pins in the usual manner. The external load termination resistors shown in Figure 4 (the 127 $\Omega$  and 82 $\Omega$  resistors) is ideally suited for both AC and DC coupled LVPECL reference clock lines. These provide the 50 $\Omega$  load termination and the VTT bias voltage.

#### Single-ended Inputs

Single-ended inputs (LVCMOS or LVTTL) are connected to the non-inverting reference input pin (DIF\_REF0 or DIF\_REF1). The inverting reference input pin (nDIF\_REF0 or nDIF\_REF1) must be left unconnected.

In single-ended operation, when the unused inverting input pin (nDIF\_REF0 or nDEF\_REF1) is left floating (not connected), the input will self-bias at VCC/2.

#### **PLL Operation**

The M2080/81/82 and M2085/86/87 are complete clock PLLs. They use a phase detector and configurable dividers to synchronize the output of the VCSO with the selected reference clock.

The M208x Series components are similar to the M2060 Series components except that the M208x Series includes the selectable AutoSwitch feature. The M208x Series also has only one clock output, as the AutoSwitch control pins replace of the second output.

The PLL will work correctly, meaning it will phase-lock the VCSO output to the input reference clock, when the internal phase detector inputs are able to run at the same frequency. This means the PLL dividers must be set appropriately and a suitable reference frequency must be chosen for the intended output frequency. When the PLL is not set up appropriately, the VCSO is forced to its upper or lower operating limit which is typically about 200 ppm above or below the VCSO center frequency. See "APR, VCSO Absolute Pull-Range" row, in the AC Characteristics table on pg. 12.

In normal phase-locked condition, the instantaneous phase error is measured by the phase detector and is converted to charge pump current pulses. These current pulses are then integrated by the external loop filter to create a VCSO control voltage. The loop filter acts as a low pass filter to remove unwanted reference clock jitter above a determined frequency or PLL bandwidth. For reference phase jitter frequencies within the loop bandwidth, phase jitter amplitude is passed on to the output clock according to the PLL loop frequency response curve.

### VCSO FEC PLL with AutoSwitch for SONET/OTN

Preliminary Information

The relationship between the nominal VCSO center frequency (Fvcso), the Mfin divider, the Mfec divider, the Rfec divider, and the input reference frequency (Fin) is:

$$Fvcso = Fin \times Mfin \times \frac{Mfec}{Rfec}$$

The Mfec, Rfec, and Mfin dividers can be set by pin configuration using the input pins FEC\_SEL1, FEC\_SEL0, FIN SEL1, and FIN SEL0.

#### **Post-PLL Divider**

The M2080/81/82 and M2085/86/87 also feature a post-PLL (P) divider.

Through use of the P divider, the device's output frequency (Fout) can be that of the VCSO (such as 622.08MHz) or the VCSO frequency divided by 4, 8 or 32 (common optical reference clocks in SONET and SDH systems).

The P\_SEL2:0 pins select the value for the P divider. (See Table 8 on pg. 4.)

Accounting for the P divider, the complete relationship between the input clock reference frequency (Fin) and output clock frequency (Fout) is defined as:

Fout =

$$\frac{\text{Fvcso}}{P}$$

=  $\text{Fin} \times \frac{\text{Mfin} \times \text{Mfec}}{\text{Rfec} \times P}$

Due to the narrow tuning range of the VCSO (±120ppm guaranteed), appropriate selection of all of the following are required for the PLL be able to lock: VCSO center frequency, input frequency, and divider selections.

#### **TriState**

The TriState feature puts the LVPECL output driver into a high impedance state, effectively disconnecting the driver from the FOUT and nFOUT pins of the device. In TriState, the M208x Series is not driving the output clock net with a defined logic level. The impedance of the clock net is then set to  $50\Omega$  by the external circuit resistors. The  $50\Omega$  impedance level of the LVPECL TriState allows manufacturing In-circuit Test to drive the clock net with an external LVPECL source to validate the integrity of clock net and the clock load.

Any unused output (single-ended or differential) should be left unconnected (floating) in system application. This minimizes output switching current and therefore minimizes noise modulation of the VCSO.

#### Loss of Lock Indicator (LOL) Output Pin

Under normal device operation, when the PLL is locked, the LOL Phase Detector drives LOL to logic 0. Under circumstances when the VCSO cannot fully phase lock to the input (as measured by a greater than 4 ns discrepancy between the feedback and reference clock rising edges at the LOL Phase Detector) the LOL output goes to logic 1. The LOL pin will return back to logic 0 when the phase detector error is less than 2 ns. The loss of lock indicator is a low current LVCMOS output.

#### **Guidelines for Using LOL**

In a given application, the magnitude of peak-to-peak jitter at the phase detector will usually increase as the Rfec divider is increased. If the LOL pin will be used to detect an unusual clock condition, or a clock fault, the FEC\_SEL1:0 pins should be set to provide a phase detector frequency of 5MHz or greater (the phase detector frequency is equal to Fin divided by the Rfec divider). Otherwise, false LOL indications may result. A phase detector frequency of 10MHz or greater is desirable when reference jitter is over 500ps, or when the device is used within a noisy system environment. LOL should not be used when the device is used in a loop timing application.

### VCSO FEC PLL with AutoSwitch for SONET/OTN

Preliminary Information

#### AutoSwitch (AUTO) Reference Clock Reselection

This device offers an automatic reference clock reselection feature for switching input reference clocks upon a reference clock failure. With the AUTO input pin set to high and the LOL output low, the device is placed into automatic reselection (AutoSwitch) mode. Once in AutoSwitch mode, when LOL then goes high (due to a reference clock fault), the input clock reference is automatically reselected internally, as indicated by the state change of the REF\_ACK output. Automatic clock reselection is made only once (it is non-revertive). Re-arming of automatic mode requires placing the device into manual selection (Manual Select) mode (AUTO pin low) before returning to AutoSwitch mode (AUTO pin high).

#### **Using the AutoSwitch Feature**

See also Table 10, Example AutoSwitch Sequence.

In application, the system is powered up with the device in Manual Select mode (AUTO pin is set low), allowing sufficient time for the reference clock and device PLL to settle. The REF\_SEL input selects the reference clock to be used in Manual Select mode and the initial reference clock used in AutoSwitch mode. The REF\_SEL input state must be maintained when switching to AutoSwitch mode (AUTO pin high) and must still be maintained until a reference fault occurs.

Once a reference fault occurs, the LOL output goes high and the input reference is automatically reselected. The

REF\_ACK output always indicates the reference selection status and the LOL output always indicates the PLL lock status.

A successful automatic reselection is indicated by a change of state of the REF\_ACK output and a momentary level high of the LOL output (minimum high time is 10 ns).

If an automatic reselection is made to a non-valid reference clock (one to which the PLL cannot lock), the REF\_ACK output will change state but the LOL output will remain high.

No further automatic reselection is made; only one reselection is made each time the AutoSwitch mode is armed. AutoSwitch mode is re-armed by placing the device into Manual Select mode (AUTO pin low) and then into AutoSwitch mode again (AUTO pin high).

Following an automatic reselection and prior to selecting Manual Select mode (AUTO pin low), the REF\_SEL pin has no control of reference selection. To prevent an unintential reference reselection, AutoSwitch mode must not be re-enabled until the desired state of the REF\_SEL pin is set and the LOL output is low. It is recommended to delay the re-arming of AutoSwitch mode, following an automatic reselection, to ensure the PLL is fully locked on the new reference. In most system configurations, where loop bandwidth is in the range of 100-1000 Hz and damping factor below 10, a delay of 500 ms should be sufficient. Until the PLL is fully locked intermittent LOL pulses may occur.

#### **Example AutoSwitch Sequence**

0 = Low: 1 = High. Example with REF SEL initially set to 0 (i.e., DIF REF0 selected)

| 0 = Lo           | 0 = Low; 1 = High. Example with REF_SEL initially set to 0 ( <i>i.e.,</i> DIF_REF0 selected) |                   |               |               |                                                                                                                                                                                              |  |  |

|------------------|----------------------------------------------------------------------------------------------|-------------------|---------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| REF_SEL<br>Input | Selected Clock Input                                                                         | REF_ACK<br>Output | AUTO<br>Input | LOL<br>Output | Conditions                                                                                                                                                                                   |  |  |

|                  |                                                                                              |                   |               |               | Initialization                                                                                                                                                                               |  |  |

| 0                | DIF_REF0                                                                                     | 0                 | 0             | 1             | Device power-up. Manual Select mode. DIF_REF0 input selected reference, not yet locked to.                                                                                                   |  |  |

| 0                | DIF_REF0                                                                                     | 0                 | 0             | -0-           | LOL to 0: Device locked to reference (may get intermittent LOL pulses until fully locked).                                                                                                   |  |  |

| 0                | DIF_REF0                                                                                     | 0                 | -1-           | 0             | AUTO set to 1: Device placed in AutoSwitch mode (with DIF_REF0 as initial reference clock).                                                                                                  |  |  |

|                  |                                                                                              |                   |               |               | Operation & Activation                                                                                                                                                                       |  |  |

| 0                | DIF_REF0                                                                                     | 0                 | 1             | 0             | Normal operation with AutoSwitch mode armed, with DIF_REF0 as initial reference clock.                                                                                                       |  |  |

| 0                | DIF_REF0                                                                                     | 0                 | 1             | -1-           | LOL to 1: Clock fault on DIF_REF0, loss of lock indicated by LOL pin,                                                                                                                        |  |  |

| 0                | -DIF_REF1-                                                                                   | -1-               | 1             | 1             | and immediate automatic reselection to DIF_REF1 (indicated by REF_ACK pin).                                                                                                                  |  |  |

| 0                | DIF_REF1                                                                                     | 1                 | 1             | -0-           | LOL to 0: Device locks to DIF_REF1 (assuming valid clock on DIF_REF1).                                                                                                                       |  |  |

|                  |                                                                                              |                   |               |               | Re-initialization                                                                                                                                                                            |  |  |

| -1-              | DIF_REF1                                                                                     | 1                 | 1             | 0             | REF_SEL set to 1: Prepares for Manual Selection of DIF_REF1 before then re-arming AutoSwitch.                                                                                                |  |  |

| 1                | DIF_REF1                                                                                     | 1                 | -0-           | 0             | AUTO set to 0: Manual Select mode entered briefly, manually selecting DIF_REF1 as reference.                                                                                                 |  |  |

| 1                | DIF_REF1                                                                                     | 1                 | -1-           | 0             | AUTO set to 1: Device is placed in AutoSwitch mode (delay recommended to ensure device fully locked), re-initializing AutoSwitch with DIF_REF1 now specified as the initial reference clock. |  |  |

Table 10: Example AutoSwitch Sequence

VCSO FEC PLL with AutoSwitch for SONET/OTN

Preliminary Information

#### **Optional Hitless Switching and Phase Build-out**

The M208x Series is available with a Hitless Switching feature that is enabled during device manufacturing. In addition, a Phase Build-out feature is also offered. These features are offered as device options and are specified by device order code. Refer to "Ordering Information" on pg. 14.

The Hitless Switching feature (with or without Phase Build-out) is designed for applications where switching occurs between two stable system reference clocks. It should not be used in loop timing applications, or when reference clock jitter is greater than 1 ns pk-pk. The Hitless Switching sequence is triggered by the LOL circuit, which is activated by a 4 ns phase transient. This magnitude of phase transient can generated by the CDR (Clock & Data Recovery unit) in loop timing mode, especially during a system jitter tolerance test. It can also be generated by some types of Stratum clock DPLLs (digital PLL), especially those that do not include a post de-jitter APLL (analog PLL).

When the M208x Series is operating in wide bandwidth mode (NBW=0), the optional Hitless Switching function puts the device into narrow bandwidth mode when during the Hitless Switching sequence. This allows the PLL to lock the new input clock phase gradually. With proper configuration of the external loop filter, the output clock phase change complies with MTIE and TDEV specifications for GR-253 (SONET) and ITU G.813 (SDH) during input reference clock changes.

The optional proprietary Phase Build-out (PBO) function enables the PLL to absorb most of the phase change of the input clock during reference switching. The PBO function selects a new VCSO clock edge for the PLL Phase Detector feedback clock, selecting the edge closest in phase to the new input clock phase. This reduces re-lock time, the generation of wander, and extra output clock cycles.

The Hitless Switching and Phase Build-out functions are triggered by the LOL circuit. For proper operation, a low phase detector frequency must be avoided. See "Guidelines for Using LOL" on pg. 6 for information regarding the phase detector frequency.

#### **HS/PBO Sequence Trigger Mechanism**

The HS function (or the combined HS/PBO function) is armed after the device locks to the input clock reference. Once armed, HS is triggered by the occurance of a Loss of Lock condition. This would typically occur as a consequence of a clock reference failure, a clock failure upstream to the M208x Series, or a M208x Series clock reference mux reselection.

#### **HS/PBO Operation**

Once triggered, the following HS/PBO sequence occurs:

- 1. The HS function disables the PLL Phase Detector and puts the device into NBW (narrow bandwidth) mode. The internal resistor Rin is changed to 2100k $\Omega$ . See the Narrow Bandwidth (NBW) Control Pin on pg. 8.

- If included, the PBO function adds to (builds out) the phase in the clock feedback path (in VCSO clock cycle increments) to align the feedback clock with the (new) reference clock input phase.

- 3. The PLL Phase Detector is enabled, allowing the PLL to re-lock.

- 4. Once the PLL Phase Detector feedback and input clocks are locked to within 2 nsec for 8 consecutive cycles, a timer (WBW timer) for resuming wide bandwidth (in 175 nsec) is started.

- 5. When the WBW timer times out, the device reverts to wide loop bandwidth mode (i.e., Rin is returned to  $100k\Omega$ ) and the HS/PBO function is re-armed.

The LOL pin will indicate lock status on a cycle-to-cycle basis and may be intermittent until PLL phase lock has fully stabilized.

#### Narrow Bandwidth (NBW) Control Pin

A Narrow Loop Bandwidth control pin (NBW pin) is included to enable adjustment of the PLL loop bandwidth. In wide bandwidth mode (NBW=0), the internal resistor Rin is  $100k\Omega$ . With the NBW pin asserted (NBW=1), the internal resistor Rin is changed to  $2100k\Omega$ . This lowers the loop bandwidth by a factor of about 21 (2100 / 100) and lowers the damping factor by about 4.6 (the square root of 21), assuming the same external loop filter component values.

VCSO FEC PLL with AutoSwitch for SONET/OTN

Preliminary Information

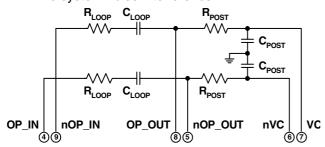

#### **External Loop Filter**

To provide stable PLL operation, the M2080/81/82 requires the use of an external loop filter. This is provided via the provided filter pins (see Figure 5). The loop filter is implemented as a differential circuit to minimize system noise interference.

Figure 5: External Loop Filter

PLL bandwidth is affected by loop filter component values, "Mfec" and "Mfin" values, and the "PLL Loop Constants" listed in AC Characteristics on pg. 12.

The FEC\_SEL setting can be used to actively change PLL loop bandwidth in a given application. See "Mfec and Rfec Divider Look-Up Tables (LUTs)" on pg. 3.

See Table 11, Example Values for Loop Filter External Components, below.

#### **PLL Simulator Tool Available**

A free PC software utility is available on the ICS website (www.icst.com). The M2000 Timing Modules PLL Simulator is a downloadable application that simulates PLL jitter and wander transfer characteristics. This enables the user to set appropriate external loop component values in a given application.

## Example Values for Loop Filter External Components <sup>1</sup> for Particular M208x Series Devices

VCSO Parameters:  $K_{VCO} = 800 \text{kHz} / V$ ,  $R_{IN} = 100 \text{k}\Omega$  (pin NBW = 0), VCSO Bandwidth = 700 kHz.

| Device       |                           | Device Configuration       |                |              |            | Example External Component Values |               |        |                       | Nominal Performance With These Values |                          |  |

|--------------|---------------------------|----------------------------|----------------|--------------|------------|-----------------------------------|---------------|--------|-----------------------|---------------------------------------|--------------------------|--|

|              | F <sub>Ref</sub><br>(MHz) | F <sub>vcso</sub><br>(MHz) | FIN_SEL<br>1:0 | MRSEL<br>1:0 | R loop     | C loop                            | R post        | C post | PLL Loop<br>Bandwidth |                                       | Passband<br>Peaking (dB) |  |

| M2080, M2080 | 622.08                    | 622.08                     | 1 1            | 0 1          | 5.6kΩ      | 10μF                              | 68k $\Omega$  | 470pF  | 530Hz                 | 6.5                                   | 0.05                     |  |

| M2080, M2085 | 155.52                    | 669.3266                   | 1 0            | 1 0          | 243.0k $Ω$ | 0.1μF                             | 34k $\Omega$  | 470pF  | 1kHz                  | 5.9                                   | 0.06                     |  |

| M2081, M2086 | 77.76                     | 622.08                     | 0 1            | 0 1          | 8.2kΩ      | 10μF                              | 100k $\Omega$ | 470pF  | 360Hz                 | 6.5                                   | 0.05                     |  |

| M2081        | 19.44                     | 622.08                     | 0 0            | 1 1          | 8.2kΩ      | 10μF                              | 100kΩ         | 470pF  | 360Hz                 | 6.5                                   | 0.05                     |  |

Table 11: Example Values for Loop Filter External Components

Note 1: K<sub>VCO</sub>, VCSO Bandwidth, M Divider Value, and External Loop Filter Component Values determine Loop Bandwidth, Damping Factor, and Passband Peaking. For PLL Simulator software, go to www.icst.com.

Refer to the M208x Series product web page at www.icst.com/products/summary/m2080-2087.htm for additional product information.

VCSO FEC PLL with AutoSwitch for SONET/OTN

Preliminary Information

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Symbol          | Parameter            | Rating                       | Unit |

|-----------------|----------------------|------------------------------|------|

| V <sub>I</sub>  | Inputs               | -0.5 to $V_{\rm CC}$ +0.5    | ٧    |

| V <sub>o</sub>  | Outputs              | -0.5 to V <sub>CC</sub> +0.5 | V    |

| V <sub>CC</sub> | Power Supply Voltage | 4.6                          | V    |

| T <sub>s</sub>  | Storage Temperature  | -45 to +100                  | °C   |

Table 12: Absolute Maximum Ratings

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in Recommended Conditions of Operation, DC Characteristics, or AC Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### **RECOMMENDED CONDITIONS OF OPERATION**

| Symbol          | Parameter                     |                 | Min 🚜          | yp Max | Unit |

|-----------------|-------------------------------|-----------------|----------------|--------|------|

| V <sub>CC</sub> | Positive Supply Voltage       | 36 3            | 3.1 <b>3</b> 5 | 3.465  | V    |

| TΔ              | Ambient Operating Temperature | 130             | 0,,            |        |      |

|                 | Cor                           | nmercial        | 0              | +70    | °C   |

|                 | Ind                           | <b>us</b> trial | -40            | +85    | °C   |

Table 13: Recommended Conditions of Operation

VCSO FEC PLL with AutoSwitch for SONET/OTN

Preliminary Information

#### **ELECTRICAL SPECIFICATIONS**

#### **DC Characteristics**

Unless stated otherwise,  $V_{CC} = 3.3V \pm 5\%$ ,  $T_A = 0$  °C to +70 °C (commercial),  $T_A = -40$  °C to +85 °C (industrial),  $F_{VCSO} = F_{OUT} = 622-675$ MHz, LVPECL outputs terminated with  $50\Omega$  to  $V_{CC} - 2V$

|                        | Symbol                | Parameter                      |                                                  | Min                   | Тур     | Max                   | Unit      | Conditions                                          |  |

|------------------------|-----------------------|--------------------------------|--------------------------------------------------|-----------------------|---------|-----------------------|-----------|-----------------------------------------------------|--|

| Power Supp             | ly V <sub>CC</sub>    | Positive Supply Voltage        |                                                  | 3.135                 | 3.3     | 3.465                 | V         |                                                     |  |

|                        | I <sub>cc</sub>       | Power Supply Current           |                                                  |                       | 175     | 225                   | mA        | _                                                   |  |

| All<br>Differential    | V <sub>P-P</sub>      | Peak to Peak Input Voltage     | DIF_REF0, nDIF_REF0, DIF_REF1, nDIF_REF1         | 0.15                  |         |                       | V         |                                                     |  |

|                        | V <sub>CMR</sub>      | Common Mode Input              |                                                  | 0.5                   |         | V <sub>cc</sub> 85    | V         |                                                     |  |

| Inputs                 | C <sub>IN</sub>       | Input Capacitance              | _ , _                                            |                       |         | 4                     | pF        |                                                     |  |

| Differential           | I <sub>IH</sub>       | Input High Current (Pull-down) |                                                  |                       |         | 150                   | μΑ        | $V_{CC} = V_{IN} =$                                 |  |

| Inputs with Pull-down  | I <sub>IL</sub>       | Input Low Current (Pull-down)  | DIF_REF0, DIF_REF1                               | -5                    |         |                       | μΑ        | - 3.456V                                            |  |

| Full-uowii             | $R_{pulldown}$        | Internal Pull-down Resistance  |                                                  |                       | 50      |                       | $k\Omega$ |                                                     |  |

| Differential           | I <sub>IH</sub>       | Input High Current (Biased) 1  |                                                  | 4                     |         | 150                   | μΑ        | V <sub>IN</sub> =                                   |  |

| Inputs<br>Biased to    | $I_IL$                | Input Low Current (Biased) 1   | nDIF_REF0, nDIF_REF1                             | -150                  |         |                       | μΑ        | 0 to 3.456V                                         |  |

| VCC/2 <sup>1</sup>     | R <sub>bias</sub>     | Biased to Vcc/2 <sup>1</sup>   | 4. 落                                             | C                     | Note 1) |                       | kΩ        | _                                                   |  |

| All LVCMOS             | V <sub>IH</sub>       | Input High Voltage             | AUTO, REF_SEL, FIN_SEL1,                         | 2                     |         | V <sub>cc</sub> + 0.3 | V         |                                                     |  |

| / LVTTL                | V <sub>IL</sub>       | Input Low Voltage              | FIN_SEL0, FEC_SEL1,<br>FEC_SEL0, P_SEL2, P_SEL1, | -0.3                  |         | 0.8                   | V         |                                                     |  |

| Inputs                 | $C_{IN}$              | Input Capacitance              | P_SEL0, NBW                                      |                       |         | 4                     | pF        |                                                     |  |

| LVCMOS /               | I <sub>IH</sub>       | Input High Current (Pull-down) | AUTO, REF_SEL, FIN_SEL1,                         |                       |         | 150                   | μΑ        | $V_{CC} = V_{IN} = $ - 3.456V                       |  |

| LVTTL<br>Inputs with   | I <sub>IL</sub>       | Input Low Current (Pull-down)  | FIN_SEL0, FEC_SEL1,<br>FEC_SEL0, P_SEL2, P_SEL1, | -5                    |         |                       | μΑ        | - 0.430V                                            |  |

| Pull-down              | R <sub>pulldown</sub> | Internal Pull-down Resistance  | P_SEL0                                           |                       | 50      |                       | kΩ        |                                                     |  |

| LVCMOS /               | I <sub>IH</sub>       | Input High Current (Pull-UP)   |                                                  |                       |         | 5                     | μΑ        | V <sub>CC</sub> = 3.456V<br>- V <sub>IN</sub> = 0 V |  |

| LVTTL<br>Inputs with   | I <sub>IL</sub>       | Input Low Current (Pull-UP)    | NBW                                              | -150                  |         |                       | μΑ        | - V <sub>IN</sub> - O V                             |  |

| Pull-UP                | R <sub>pullup</sub>   | Internal Pull-UP Resistance    |                                                  |                       | 50      |                       | $k\Omega$ |                                                     |  |

| Differential<br>Output | $V_{OH}$              | Output High Voltage            | FOUT, nFOUT                                      | V <sub>cc</sub> - 1.4 |         | V <sub>cc</sub> - 1.0 | V         |                                                     |  |

|                        | $V_{OL}$              | Output Low Voltage             |                                                  | V <sub>cc</sub> - 2.0 |         | V <sub>cc</sub> - 1.7 | V         |                                                     |  |

|                        | V <sub>P-P</sub>      | Peak to Peak Output Voltage 2  |                                                  | 0.4                   |         | 0.85                  | V         |                                                     |  |

| LVCMOS                 | $V_{OH}$              | Output High Voltage            | LOL, REF_ACK                                     | 2.4                   |         | $V_{CC}$              | V         | I <sub>OH</sub> = 1mA                               |  |

| Outputs                | V <sub>OL</sub>       | Output Low Voltage             | LOL, NEF_AON                                     | GND                   |         | 0.4                   | V         | I <sub>OL</sub> = 1mA                               |  |

Note 1: Biased to Vcc/2, with  $50k\Omega$  to Vcc and  $50k\Omega$  to ground. See Figure 4, Input Reference Clocks, on pg. 5 Table 14: DC Characteristics Note 2: Single-ended measurement. See Figure 6, Output Rise and Fall Time, on pg. 12.

VCSO FEC PLL with AutoSwitch for SONET/OTN

Preliminary Information

### **ELECTRICAL SPECIFICATIONS (CONTINUED)**

**AC Characteristics** Unless stated otherwise,  $V_{CC} = 3.3V \pm 5\%$ ,  $T_A = 0$  °C to +70 °C (commercial),  $T_A = -40$  °C to +85 °C (industrial),  $F_{VCSO} = F_{OUT} = 622-675$ MHz, LVPECL outputs terminated with  $50\Omega$  to  $V_{CC} - 2V$

|                                    | Symbol                          | Parameter                                  |                                             | Min     | Тур  | Max | Unit   | Conditions                  |

|------------------------------------|---------------------------------|--------------------------------------------|---------------------------------------------|---------|------|-----|--------|-----------------------------|

|                                    | F <sub>IN</sub>                 | Input Frequency                            | DIF_REF0, nDIF_REF0,<br>DIF_REF1, nDIF_REF1 | 10      |      | 700 | MHz    |                             |

|                                    | F <sub>OUT</sub>                | Output Frequency                           | FOUT, nFOUT                                 | 15      |      | 700 | MHz    |                             |

|                                    | APR VCSO Absolute<br>Pull-Range |                                            | Commercial                                  | ±120    | ±200 |     | ppm    |                             |

|                                    |                                 |                                            | Industrial                                  | ±50     | ±150 |     | ppm    |                             |

|                                    | $K_{VCO}$                       | VCO Gain                                   |                                             |         | 800  |     | kHz/V  |                             |

| PLL Loop<br>Constants <sup>1</sup> | R <sub>IN</sub>                 | Internal Loop Resistor                     | Wide Bandwidth                              |         | 100  |     | kΩ     |                             |

|                                    |                                 |                                            | Narrow Bandwidth                            |         | 2100 |     | kΩ     |                             |

|                                    | BW <sub>VCSO</sub>              | VCSO Bandwidth                             |                                             |         | 700  |     | kHz    |                             |

| Phase Noise and Jitter             | Фп                              | Single Side Band                           | 1kHz Offset                                 | - 40 15 | -73  |     | dBc/Hz | Fin=19.44 or                |

|                                    |                                 | Phase Noise<br>@622.08MHz                  | 10kHz Offset                                | 13      | -103 |     | dBc/Hz | 38.88 MHz<br>Mfin=32 or 16, |

|                                    |                                 |                                            | 100kHz Offset                               | die.    | -126 |     | dBc/Hz | Mfec=Rfec                   |

|                                    | J(t)                            | J(t) Jitter (rms)                          | 12kHz to 20MHz                              |         | 0.25 | 0.5 | ps     |                             |

|                                    |                                 | @622.08MHz                                 | 50kHz to 80MHz                              |         | 0.25 | 0.5 | ps     |                             |

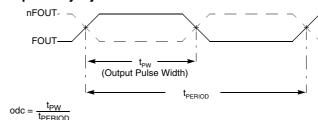

|                                    |                                 | Output Duty Cycle <sup>2</sup> FOUT, nFOUT | P = 4, 8, or 32                             | 45      | 50   | 55  | %      |                             |

|                                    |                                 |                                            | P = 1                                       | 40      | 50   | 60  | %      |                             |

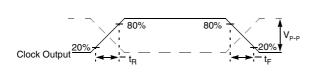

|                                    | t <sub>R</sub>                  | Output Rise Time 2                         | FOUT, nFOUT                                 | 200     | 450  | 500 | ps     | 20% to 80%                  |

|                                    | t <sub>F</sub>                  | Output Fall Time 2                         | - 1 001, 111 001                            | 200     | 450  | 500 | ps     | 20% to 80%                  |

Table 15: AC Characteristics

Note 1: Parameters needed for PLL Simulator software; see Table 11, Example Values for Loop Filter External Components, on pg. 9. Note 2: See Parameter Measurement Information on pg. 12.

#### PARAMETER MEASUREMENT INFORMATION

#### **Output Rise and Fall Time**

Figure 6: Output Rise and Fall Time

#### **Output Duty Cycle**

Figure 7: Output Duty Cycle

VCSO FEC PLL with AutoSwitch for SONET/OTN

Preliminary Information

#### DEVICE PACKAGE - 9 x 9mm CERAMIC LEADLESS CHIP CARRIER

#### **Mechanical Dimensions:**

Refer to the M208x Series product web page at www.icst.com/products/summary/m2080-2087.htm for recommended PCB footprint, solder mask, furnace profile, and related information.

Figure 8: Device Package - 9 x 9mm Ceramic Leadless Chip Carrier

### Preliminary Information M2080/81/82, M2085/86/87 VCSO FEC PLL with AutoSwitch for SONET/OTN

#### **ORDERING INFORMATION**

#### Standard VCSO Output Frequencies (MHz)\*

#### **Part Numbering Scheme**

| Part Number: M208 Divider Look-up Table Option                                                                           | 3x-yz- <u>xxx.xxxx</u> |

|--------------------------------------------------------------------------------------------------------------------------|------------------------|

| See Table 9, page 4.                                                                                                     |                        |

| Output type ————————————————————————————————————                                                                         |                        |

| (For CML or LVDS clock output, consult factory)                                                                          |                        |

| Hitless Switching / Phase Build-out Options —  1 = none 2 = Hitless Switching 3 = Hitless Switching with Phase Build-out |                        |

| Temperature —                                                                                                            |                        |

| "=" = 0 to +70 °C (commercial)                                                                                           |                        |

| $I = -40 \text{ to } +85 ^{\circ}\text{C} \text{ (industrial)}$                                                          |                        |

| VCSO Frequency (MHz)  See Table 16, right. Consult ICS for other frequence                                               | ncies.                 |

| 622.0800 | 669.3120 |

|----------|----------|

| 625.0000 | 669.3266 |

| 627.3296 | 669.6429 |

| 644.5313 | 670.8386 |

| 666.5143 | 672.1600 |

| 669.1281 | 690.5692 |

Table 16: Standard VCSO Output Frequencies

Figure 9: Part Numbering Scheme

Note \*: Fout can equal Fvcso divided by: 1, 4, 8, or 32.

Consult ICS for the availability of other VCSO frequencies.

#### **Example Part Numbers**

| Example Fart Numbers             |            |                                        |  |  |  |

|----------------------------------|------------|----------------------------------------|--|--|--|

| VCSO Frequency (MHz) Temperature |            | Order Part Number (Examples)           |  |  |  |

| 622.0800                         | commercial | M2081-11-622.0800 or M2082-11-622.0800 |  |  |  |

| 022.0000                         | industrial | M2081-11I622.0800 or M2082-11I622.0800 |  |  |  |

| 669.3266                         | commercial | M2080-11-669.3266 or M2085-11-669.3266 |  |  |  |

| 003.0200                         | industrial | M2080-11I669.3266 or M2085-11I669.3266 |  |  |  |

|                                  |            | Table 17: Example Part Numbers         |  |  |  |

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems (ICS) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by ICS. ICS reserves the right to change any circuitry or specifications without notice. ICS does not authorize or warrant any ICS product for use in life support devices or critical medical instruments.