## 512 Kbit (64K x8) UV EPROM and OTP EPROM

#### **Features**

- 5V ± 10% supply voltage in read operation

- Access time: 45 ns

- Low power "CMOS" consumption:

- Active current 30 mA

- Standby current 100 μA

- Programming voltage: 12.75 V ± 0.25 V

- Programming time around 6 s.

- Electronic Signature

- Manufacturer code: 20h

- Device code: 3Dh

- Packages

- ECOPACK® versions

Table 1. Device summary

| Package | 45 ns         | 70 ns         | 90 ns                        | 100 ns           | 120 ns                               | 150 ns                       |

|---------|---------------|---------------|------------------------------|------------------|--------------------------------------|------------------------------|

| PDIP28  |               |               | M27C512-90B6                 |                  |                                      |                              |

| PLCC32  |               | M27C512-70C6  | M27C512-90C1                 | M27C512-<br>10C6 | M27C512-<br>12C3                     |                              |

| FDIP28W | M27C512-45XF1 | M27C512-70XF1 | M27C512-90F1<br>M27C512-90F6 | M27C512-<br>10F1 | M27C512-<br>12F1<br>M27C512-<br>12F3 | M27C512-15F1<br>M27C512-15F6 |

Contents M27C512

## **Contents**

| 1 | Desc | cription                         | 3 |

|---|------|----------------------------------|---|

| 2 | Devi | ce operation                     | 5 |

|   | 2.1  | Read mode                        | 5 |

|   | 2.2  | Standby mode                     | 5 |

|   | 2.3  | Two line output control          | 6 |

|   | 2.4  | System considerations            | 6 |

|   | 2.5  | Programming                      | 7 |

|   | 2.6  | PRESTO IIB programming algorithm | 7 |

|   | 2.7  | Program Inhibit                  | 8 |

|   | 2.8  | Program Verify                   |   |

|   | 2.9  | Electronic Signature             | 8 |

| 3 | Eras | Electronic Signature             | 9 |

| 4 | Maxi | mum rating                       | 0 |

| 5 | DC a | and AC parameters                | 1 |

| 6 | Pack | rage mechanical                  | 7 |

| 7 | Part | numbering                        | 0 |

| 8 | Revi | sion history2º                   | 1 |

M27C512 Description

## 1 Description

The M27C512 is a 512 Kbit EPROM offered in the two ranges UV (ultra violet erase) and OTP (one time programmable). It is ideally suited for applications where fast turn-around and pattern experimentation are important requirements and is organized as 65536 by 8 bits.

The FDIP28W (window ceramic frit-seal package) has transparent lid which allows the user to expose the chip to ultraviolet light to erase the bit pattern. A new pattern can then be written to the device by following the programming procedure.

For applications where the content is programmed only one time and erasure is not required, the M27C512 is offered in FDIP28W, PDIP28, and PLCC32 packages. In order to meet environmental requirements, ST offers the M27C512 in ECOPACK® packages. ECOPACK packages are Lead-free. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

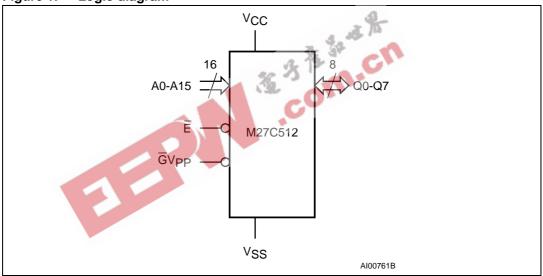

Figure 1. Logic diagram

Table 2. Signal names

| Name             | Description                    | Direction |

|------------------|--------------------------------|-----------|

| A0-A15           | Address Inputs                 | Inputs    |

| Q0-Q7            | Data outputs                   | Outputs   |

| Ē                | Chip Enable                    | Input     |

| GV <sub>PP</sub> | Output Enable / Program Supply | Input     |

| V <sub>CC</sub>  | Supply Voltage                 | Supply    |

| V <sub>SS</sub>  | Ground                         | Supply    |

| NC               | Not Connected Internally       | -         |

| DU               | Don't Use                      | -         |

Description M27C512

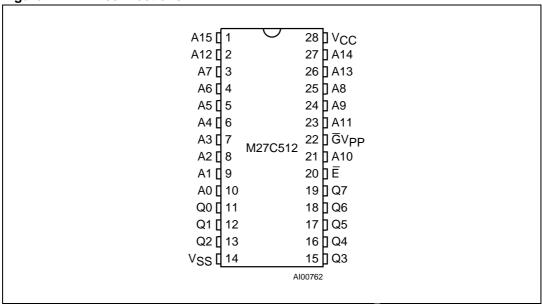

Figure 2. DIP connections

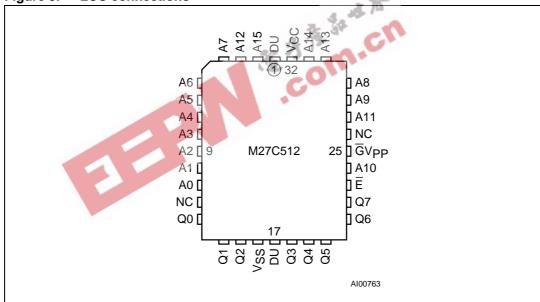

Figure 3. LCC connections

M27C512 Device operation

## 2 Device operation

The modes of operations of the M27C512 are listed in the Operating Modes table. A single power supply is required in the read mode. All inputs are TTL levels except for  $\overline{GV}_{PP}$  and 12V on A9 for Electronic Signature.

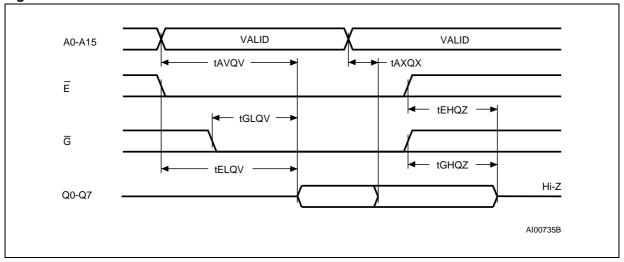

#### 2.1 Read mode

The M27C512 has two control functions, both of which must be logically active in order to obtain data at the outputs. Chip Enable  $(\overline{E})$  is the power control and should be used for device selection. Output Enable  $(\overline{G})$  is the output control and should be used to gate data to the output pins, independent of device selection. Assuming that the addresses are stable, the address access time  $(t_{AVQV})$  is equal to the delay from  $\overline{E}$  to output  $(t_{ELQV})$ . Data is available at the output after a delay of  $t_{GLQV}$  from the falling edge of  $\overline{G}$ , assuming that  $\overline{E}$  has been low and the addresses have been stable for at least  $t_{AVQV}$ ,  $t_{GLQV}$ .

### 2.2 Standby mode

The M27C512 has a standby mode which reduces the active current from 30mA to  $100\mu A$  The M27C512 is placed in the standby mode by applying a CMOS high signal to the  $\overline{E}$  input. When in the standby mode, the outputs are in a high impedance state, independent of the  $\overline{G}V_{PP}$  input.

Table 3. Operating modes<sup>(1)</sup>

| Mode                 | Ē                     | GV <sub>PP</sub> | А9       | Q7-Q0    |

|----------------------|-----------------------|------------------|----------|----------|

| Read                 | V <sub>IL</sub>       | V <sub>IL</sub>  | Х        | Data Out |

| Output Disable       | V <sub>IL</sub>       | V <sub>IH</sub>  | Х        | Hi-Z     |

| Program              | V <sub>IL</sub> Pulse | V <sub>PP</sub>  | Х        | Data In  |

| Program Inhibit      | V <sub>IH</sub>       | V <sub>PP</sub>  | Х        | Hi-Z     |

| Standby              | V <sub>IH</sub>       | Х                | Х        | Hi-Z     |

| Electronic Signature | V <sub>IL</sub>       | V <sub>IL</sub>  | $V_{ID}$ | Codes    |

<sup>1.</sup>  $X = V_{IH}$  or  $V_{IL}$ ,  $V_{ID} = 12V \pm 0.5V$ .

Table 4. Electronic Signature

| Identifier             | Α0              | Q7 | Q6 | Q5 | Q4 | Q3 | Q2 | Q1 | Q0 | Hex Data |

|------------------------|-----------------|----|----|----|----|----|----|----|----|----------|

| Manufacturer's<br>Code | V <sub>IL</sub> | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 20h      |

| Device Code            | V <sub>IH</sub> | 0  | 0  | 1  | 1  | 1  | 1  | 0  | 1  | 3Dh      |

Device operation M27C512

#### 2.3 Two line output control

Because EPROMs are usually used in larger memory arrays, the product features a 2 line control function which accommodates the use of multiple memory connection. The two line control function allows:

- The lowest possible memory power dissipation,

- Complete assurance that output bus contention will not occur.

For the most efficient use of these two control lines,  $\overline{E}$  should be decoded and used as the primary device selecting function, while  $\overline{G}$  should be made a common connection to all devices in the array and connected to the  $\overline{READ}$  line from the system control bus. This ensures that all deselected memory devices are in their low power standby mode and that the output pins are only active when data is required from a particular memory device.

### 2.4 System considerations

The power switching characteristics of Advanced CMOS EPROMs require careful decoupling of the devices. The supply current,  $I_{CC}$ , has three segments that are of interest to the system designer: the standby current level, the active current level, and transient current peaks that are produced by the falling and rising edges of  $\overline{E}$ . The magnitude of the transient current peaks is dependent on the capacitive and inductive loading of the device at the output. The associated transient voltage peaks can be suppressed by complying with the two line output control and by properly selected decoupling capacitors. It is recommended that a  $0.1\mu F$  ceramic capacitor be used on every device between  $V_{CC}$  and  $V_{SS}$ . This should be a high frequency capacitor of low inherent inductance and should be placed as close to the device as possible. In addition, a  $4.7\mu F$  bulk electrolytic capacitor should be used between  $V_{CC}$  and  $V_{SS}$  for every eight devices. The bulk capacitor should be located near the power supply connection point. The purpose of the bulk capacitor is to overcome the voltage drop caused by the inductive effects of PCB traces.

M27C512 Device operation

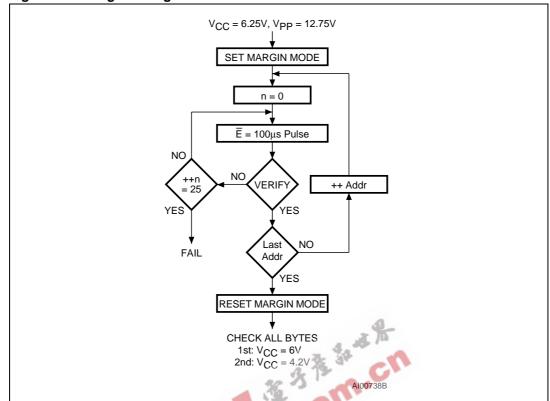

Figure 4. Programming flowchart

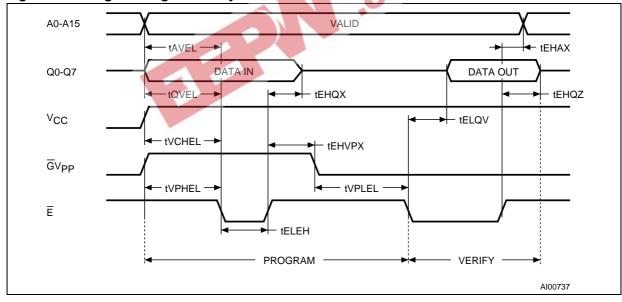

## 2.5 Programming

When delivered (and after each erasure for UV EPROM), all bits of the M27C512 are in the '1' state. Data is introduced by selectively programming '0's into the desired bit locations. Although only '0's will be programmed, both '1's and '0's can be present in the data word. The only way to change a '0' to a '1' is by die exposure to ultraviolet light (UV EPROM). The M27C512 is in the programming mode when  $V_{PP}$  input is at 12.75V and  $\overline{E}$  is pulsed to  $V_{IL}$ . The data to be programmed is applied to 8 bits in parallel to the data output pins. The levels required for the address and data inputs are TTL.  $V_{CC}$  is specified to be 6.25V  $\pm$  0.25V. The M27C512 can use PRESTO IIB Programming Algorithm that drastically reduces the programming time (typically less than 6 seconds). Nevertheless to achieve compatibility with all programming equipments, PRESTO Programming Algorithm can be used as well.

## 2.6 PRESTO IIB programming algorithm

PRESTO IIB Programming Algorithm allows the whole array to be programmed with a guaranteed margin, in a typical time of 6.5 seconds. This can be achieved with STMicroelectronics M27C512 due to several design innovations described in the M27C512 datasheet to improve programming efficiency and to provide adequate margin for reliability. Before starting the programming the internal MARGIN MODE circuit is set in order to guarantee that each cell is programmed with enough margin. Then a sequence of 100µs program pulses are applied to each byte until a correct verify occurs. No overprogram pulses are applied since the verify in MARGIN MODE provides the necessary margin.

Device operation M27C512

#### 2.7 Program Inhibit

Programming of multiple M27C512s in parallel with different data is also easily accomplished. Except for  $\overline{E}$ , all like inputs including  $\overline{G}V_{PP}$  of the parallel M27C512 may be common. A TTL low level pulse applied to a M27C512's  $\overline{E}$  input, with  $V_{PP}$  at 12.75V, will program that M27C512. A high level  $\overline{E}$  input inhibits the other M27C512s from being programmed.

### 2.8 Program Verify

A verify (read) should be performed on the programmed bits to determine that they were correctly programmed. The verify is accomplished with  $\overline{G}$  at  $V_{IL}$ . Data should be verified with  $t_{FLOV}$  after the falling edge of  $\overline{E}$ .

### 2.9 Electronic Signature

The Electronic Signature (ES) mode allows the reading out of a binary code from an EPROM that will identify its manufacturer and type. This mode is intended for use by programming equipment to automatically match the device to be programmed with its corresponding programming algorithm. The ES mode is functional in the 25°C  $\pm$  5°C ambient temperature range that is required when programming the M27C512. To activate the ES mode, the programming equipment must force 11.5V to 12.5V on address line A9 of the M27C512. Two identifier bytes may then be sequenced from the device outputs by toggling address line A0 from  $V_{IL}$  to  $V_{IH}$ . All other address lines must be held at  $V_{IL}$  during Electronic Signature mode. Byte 0 (A0 =  $V_{IL}$ ) represents the manufacturer code and byte 1 (A0 =  $V_{IH}$ ) the device identifier code. For the STMicroelectronics M27C512, these two identifier bytes are given in <Blue>Table 4. and can be read-out on outputs Q7 to Q0.

## 3 Erasure operation (applies for UV EPROM)

The erasure characteristics of the M27C512 is such that erasure begins when the cells are exposed to light with wavelengths shorter than approximately 4000 Å. It should be noted that sunlight and some type of fluorescent lamps have wavelengths in the 3000-4000 Å range.

Research shows that constant exposure to room level fluorescent lighting could erase a typical M27C512 in about 3 years, while it would take approximately 1 week to cause erasure when exposed to direct sunlight. If the M27C512 is to be exposed to these types of lighting conditions for extended periods of time, it is suggested that opaque labels be put over the M27C512 window to prevent unintentional erasure. The recommended erasure procedure for the M27C512 is exposure to short wave ultraviolet light which has wavelength 2537 Å. The integrated dose (i.e. UV intensity x exposure time) for erasure should be a minimum of 15 W-sec/cm². The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with 12000  $\mu\text{W/cm}^2$  power rating. The M27C512 should be placed within 2.5 cm (1 inch) of the lamp tubes during the erasure. Some lamps have a filter on their tubes which should be removed before erasure.

Maximum rating M27C512

## 4 Maximum rating

Stressing the device outside the ratings listed in <Blue>Table 5. may cause permanent damage to the device. These are stress ratings only, and operation of the device at these, or any other conditions outside those indicated in the Operating sections of this specification, is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

Table 5. Absolute maximum ratings

| Symbol                         | Parameter                                    | Value      | Unit |

|--------------------------------|----------------------------------------------|------------|------|

| T <sub>A</sub>                 | Ambient Operating Temperature <sup>(1)</sup> | -40 to 125 | °C   |

| T <sub>BIAS</sub>              | Temperature Under Bias                       | -50 to 125 | °C   |

| T <sub>STG</sub>               | Storage Temperature                          | -65 to 150 | °C   |

| T <sub>LEAD</sub>              | Lead Temperature during Soldering            | (note 1)   | °C   |

| V <sub>IO</sub> (2)            | Input or Output Voltage (except A9)          | –2 to 7    | V    |

| V <sub>CC</sub>                | Supply Voltage                               | –2 to 7    | V    |

| V <sub>A9</sub> <sup>(2)</sup> | A9 Voltage                                   | –2 to 13.5 | V    |

| V <sub>PP</sub>                | Program Supply Voltage                       | –2 to 14   | V    |

<sup>1.</sup> Depends on range.

Minimum DC voltage on Input or Output is -0.5V with possible undershoot to -2.0V for a period less than 20ns. Maximum DC voltage on Output is V<sub>CC</sub> +0.5V with possible overshoot to V<sub>CC</sub> +2V for a period less than 20ns.

## 5 DC and AC parameters

This section summarizes the operating and measurement conditions, and the DC and AC characteristics of the device. The parameters in the DC and AC Characteristic tables that follow are derived from tests performed under the Measurement Conditions summarized in the relevant tables. Designers should check that the operating conditions in their circuit match the measurement conditions when relying on the quoted parameters.

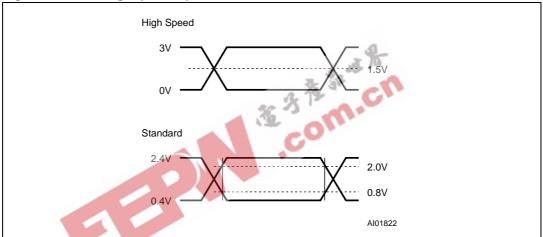

Table 6. AC measurement conditions

|                                       | High Speed | Standard     |

|---------------------------------------|------------|--------------|

| Input Rise and Fall Times             | ≤ 10ns     | ≤ 20ns       |

| Input Pulse Voltages                  | 0 to 3V    | 0.4V to 2.4V |

| Input and Output Timing Ref. Voltages | 1.5V       | 0.8V and 2V  |

Figure 5. Testing input/output waveform

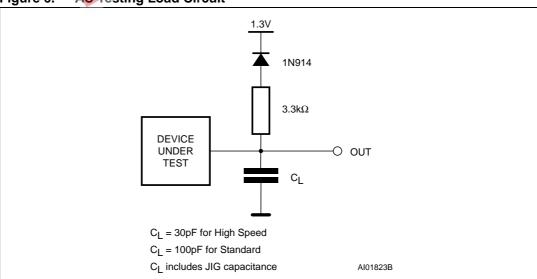

Figure 6. AC Testing Load Circuit

Table 7. Capacitance

| Symbol           | Parameter          | Test Condition <sup>(1)(2)</sup> | Min | Max | Unit |

|------------------|--------------------|----------------------------------|-----|-----|------|

| C <sub>IN</sub>  | Input Capacitance  | $V_{IN} = 0V$                    |     | 6   | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 0V            |     | 12  | pF   |

<sup>1.</sup>  $T_A = 25^{\circ}C$ , f = 1MHz

Table 8. Read mode DC characteristics

| Symbol                         | Parameter                     | Test Condition <sup>(1)</sup>                                             | Min                    | Max                 | Unit |

|--------------------------------|-------------------------------|---------------------------------------------------------------------------|------------------------|---------------------|------|

| I <sub>LI</sub>                | Input Leakage Current         | $0V \leq V_{IN} \leq V_{CC}$                                              |                        | ±10                 | μA   |

| I <sub>LO</sub>                | Output Leakage Current        | $0V \le V_{OUT} \le V_{CC}$                                               |                        | ±10                 | μA   |

| I <sub>CC</sub>                | Supply Current                | $\overline{E} = V_{IL}, \overline{G} = V_{IL},$ $I_{OUT} = 0mA, f = 5MHz$ |                        | 30                  | mA   |

| I <sub>CC1</sub>               | Supply Current (Standby) TTL  | E = V <sub>IH</sub>                                                       |                        | 1                   | mA   |

| I <sub>CC2</sub>               | Supply Current (Standby) CMOS | $\overline{E} > V_{CC} - 0.2V$                                            |                        | 100                 | μA   |

| I <sub>PP</sub>                | Program Current               | $V_{PP} = V_{CC}$                                                         | .0                     | 10                  | μΑ   |

| V <sub>IL</sub>                | Input Low Voltage             | 3                                                                         | -0.3                   | 0.8                 | V    |

| V <sub>IH</sub> <sup>(2)</sup> | Input High Voltage            | 表等                                                                        | 2                      | V <sub>CC</sub> + 1 | V    |

| V <sub>OL</sub>                | Output Low Voltage            | I <sub>OL</sub> = 2.1mA                                                   |                        | 0.4                 | V    |

| V.                             | Output High Voltage TTL       | $I_{OH} = -1 \text{mA}$                                                   | 3.6                    |                     | V    |

| V <sub>OH</sub>                | Output High Voltage CMOS      | I <sub>OH</sub> = -100μA                                                  | V <sub>CC</sub> – 0.7V |                     | V    |

<sup>1.</sup>  $V_{CC}$  must be applied simultaneously with or before  $V_{PP}$  and removed simultaneously or after  $V_{PP}$ .

<sup>2.</sup> Sampled only, not 100% tested.

<sup>2.</sup> Maximum DC voltage on Output is  $V_{\rm CC}$  +0.5V.

**Read mode AC characteristics** Table 9.

|                       |                  |                                            |                                                |                    |     | Unit |     |    |

|-----------------------|------------------|--------------------------------------------|------------------------------------------------|--------------------|-----|------|-----|----|

| Symbol                | Alt              | It Parameter                               | Test Condition <sup>(1)</sup>                  | -45 <sup>(2)</sup> |     |      | -70 |    |

|                       |                  |                                            |                                                | Min                | Max | Min  | Max |    |

| t <sub>AVQV</sub>     | t <sub>ACC</sub> | Address Valid to Output Valid              | $\overline{E} = V_{IL}, \overline{G} = V_{IL}$ |                    | 45  |      | 70  | ns |

| t <sub>ELQV</sub>     | t <sub>CE</sub>  | Chip Enable Low to<br>Output Valid         | $\overline{G} = V_{IL}$                        |                    | 45  |      | 70  | ns |

| t <sub>GLQV</sub>     | t <sub>OE</sub>  | Output Enable Low to<br>Output Valid       | E = V <sub>IL</sub>                            |                    | 25  |      | 35  | ns |

| t <sub>EHQZ</sub> (3) | t <sub>DF</sub>  | Chip Enable High to<br>Output Hi-Z         | $\overline{G} = V_{IL}$                        | 0                  | 25  | 0    | 30  | ns |

| t <sub>GHQZ</sub> (3) | t <sub>DF</sub>  | Output Enable High to Output Hi-Z          | E = V <sub>IL</sub>                            | 0                  | 25  | 0    | 30  | ns |

| t <sub>AXQX</sub>     | t <sub>OH</sub>  | Address Transition to<br>Output Transition | $\overline{E} = V_{IL}, \overline{G} = V_{IL}$ | 0                  |     | 0    |     | ns |

V<sub>CC</sub> must be applied simultaneously with or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

Speed obtained with High Speed AC measurement conditions.

Sampled only, not 100% tested.

Table 10. Read mode AC characteristics

|                                  |                  |                                               |                                                | G   | 0   | M27 | C512 |     |     |     |     |      |

|----------------------------------|------------------|-----------------------------------------------|------------------------------------------------|-----|-----|-----|------|-----|-----|-----|-----|------|

| Symbol                           | Alt              | Parameter                                     | Test Condition <sup>(1)</sup>                  | 99  | 90  | -1  | 10   | -1  | 12  | -1  | 15  | Unit |

|                                  |                  |                                               |                                                | Min | Max | Min | Max  | Min | Max | Min | Max |      |

| t <sub>AVQV</sub>                | t <sub>ACC</sub> | Address Valid to<br>Output Valid              | $\overline{E} = V_{ L}, \overline{G} = V_{ L}$ |     | 90  |     | 100  |     | 120 |     | 150 | ns   |

| t <sub>ELQV</sub>                | t <sub>CE</sub>  | Chip Enable Low to Output Valid               | G = V <sub>IL</sub>                            |     | 90  |     | 100  |     | 120 |     | 150 | ns   |

| t <sub>GLQV</sub>                | t <sub>OE</sub>  | Output Enable Low to Output Valid             | $\overline{E} = V_{IL}$                        |     | 40  |     | 40   |     | 50  |     | 60  | ns   |

| t <sub>EHQZ</sub> (2)            | t <sub>DF</sub>  | Chip Enable High to Output Hi-Z               | G = V <sub>IL</sub>                            | 0   | 30  | 0   | 30   | 0   | 40  | 0   | 50  | ns   |

| t <sub>GHQZ</sub> <sup>(2)</sup> | t <sub>DF</sub>  | Output Enable<br>High to Output Hi-<br>Z      | E = V <sub>IL</sub>                            | 0   | 30  | 0   | 30   | 0   | 40  | 0   | 50  | ns   |

| t <sub>AXQX</sub>                | t <sub>ОН</sub>  | Address Transition<br>to Output<br>Transition | $\overline{E} = V_{IL}, \overline{G} = V_{IL}$ | 0   |     | 0   |      | 0   |     | 0   |     | ns   |

<sup>1.</sup>  $V_{CC}$  must be applied simultaneously with or before  $V_{PP}$  and removed simultaneously or after  $V_{PP}$ .

<sup>2.</sup> Sampled only, not 100% tested.

Figure 7. Read mode AC waveforms

Table 11. Programming mode DC characteristics

| Symbol          | Parameter               | Test Condition <sup>(1)(2)</sup> | Min      | Max                   | Unit |

|-----------------|-------------------------|----------------------------------|----------|-----------------------|------|

| I <sub>LI</sub> | Input Leakage Current   | $V_{IL} \leq V_{IN} \leq V_{IH}$ | - 8-     | ±10                   | μΑ   |

| I <sub>CC</sub> | Supply Current          | 35.                              | 42 14 14 | 50                    | mA   |

| I <sub>PP</sub> | Program Current         | $\overline{E} = V_{IL}$          | C        | 50                    | mA   |

| V <sub>IL</sub> | Input Low Voltage       |                                  | -0.3     | 0.8                   | V    |

| V <sub>IH</sub> | Input High Voltage      | C                                | 2        | V <sub>CC</sub> + 0.5 | V    |

| V <sub>OL</sub> | Output Low Voltage      | I <sub>OL</sub> = 2.1mA          |          | 0.4                   | V    |

| V <sub>OH</sub> | Output High Voltage TTL | $I_{OH} = -1mA$                  | 3.6      |                       | V    |

| V <sub>ID</sub> | A9 Voltage              |                                  | 11.5     | 12.5                  | V    |

<sup>1.</sup>  $T_A = 25$  °C;  $V_{CC} = 6.25V \pm 0.25V$ ;  $V_{PP} = 12.75V \pm 0.25V$

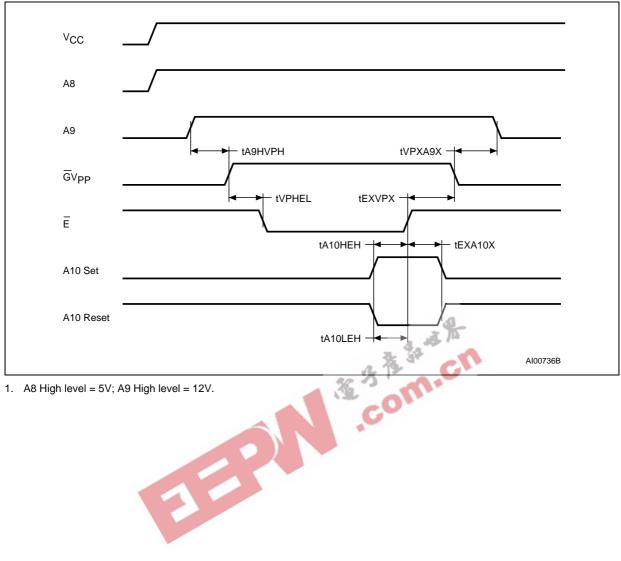

Table 12. Margin Mode AC Characteristics

| 145.0 12.           | a. g              | modo / to onaraotoriotico                                |                                     |     |     |      |

|---------------------|-------------------|----------------------------------------------------------|-------------------------------------|-----|-----|------|

| Symbol              | Alt               | Parameter                                                | Test<br>Condition <sup>(1)(2)</sup> | Min | Max | Unit |

| t <sub>A9HVPH</sub> | t <sub>AS9</sub>  | V <sub>A9</sub> High to V <sub>PP</sub> High             |                                     | 2   |     | μs   |

| t <sub>VPHEL</sub>  | t <sub>VPS</sub>  | V <sub>PP</sub> High to Chip Enable Low                  |                                     | 2   |     | μs   |

| t <sub>A10HEH</sub> | t <sub>AS10</sub> | V <sub>A10</sub> High to Chip Enable High (Set)          |                                     | 1   |     | μs   |

| t <sub>A10LEH</sub> | t <sub>AS10</sub> | V <sub>A10</sub> Low to Chip Enable High (Reset)         |                                     | 1   |     | μs   |

| t <sub>EXA10X</sub> | t <sub>AH10</sub> | Chip Enable Transition to V <sub>A10</sub> Transition    |                                     | 1   |     | μs   |

| t <sub>EXVPX</sub>  | t <sub>VPH</sub>  | Chip Enable Transition to V <sub>PP</sub> Transition     |                                     | 2   |     | μs   |

| t <sub>VPXA9X</sub> | t <sub>AH9</sub>  | V <sub>PP</sub> Transition to V <sub>A9</sub> Transition |                                     | 2   |     | μs   |

<sup>1.</sup>  $T_A = 25$  °C;  $V_{CC} = 6.25V \pm 0.25V$ ;  $V_{PP} = 12.75V \pm 0.25V$

<sup>2.</sup>  $V_{CC}$  must be applied simultaneously with or before  $V_{PP}$  and removed simultaneously or after  $V_{PP}$ .

<sup>2.</sup>  $V_{CC}$  must be applied simultaneously with or before  $V_{PP}$  and removed simultaneously or after  $V_{PP}$ .

Figure 8. Margin mode AC waveforms

1. A8 High level = 5V; A9 High level = 12V.

**Programming mode AC characteristics** Table 13.

| Symbol                | Alt              | Parameter                                      | Test<br>Condition <sup>(1)(2)</sup> | Min | Max | Unit |

|-----------------------|------------------|------------------------------------------------|-------------------------------------|-----|-----|------|

| t <sub>AVEL</sub>     | t <sub>AS</sub>  | Address Valid to Chip Enable Low               |                                     | 2   |     | μs   |

| t <sub>QVEL</sub>     | t <sub>DS</sub>  | Input Valid to Chip Enable Low                 |                                     | 2   |     | μs   |

| t <sub>VCHEL</sub>    | t <sub>VCS</sub> | V <sub>CC</sub> High to Chip Enable Low        |                                     | 2   |     | μs   |

| t <sub>VPHEL</sub>    | t <sub>OES</sub> | V <sub>PP</sub> High to Chip Enable Low        |                                     | 2   |     | μs   |

| t <sub>VPLVPH</sub>   | t <sub>PRT</sub> | V <sub>PP</sub> Rise Time                      |                                     | 50  |     | ns   |

| t <sub>ELEH</sub>     | t <sub>PW</sub>  | Chip Enable Program Pulse Width (Initial)      |                                     | 95  | 105 | μs   |

| t <sub>EHQX</sub>     | t <sub>DH</sub>  | Chip Enable High to Input Transition           |                                     | 2   |     | μs   |

| t <sub>EHVPX</sub>    | t <sub>OEH</sub> | Chip Enable High to V <sub>PP</sub> Transition |                                     | 2   |     | μs   |

| t <sub>VPLEL</sub>    | t <sub>VR</sub>  | V <sub>PP</sub> Low to Chip Enable Low         |                                     | 2   |     | μs   |

| t <sub>ELQV</sub>     | t <sub>DV</sub>  | Chip Enable Low to Output Valid                |                                     |     | 1   | μs   |

| t <sub>EHQZ</sub> (3) | t <sub>DFP</sub> | Chip Enable High to Output Hi-Z                |                                     | 0   | 130 | ns   |

| t <sub>EHAX</sub>     | t <sub>AH</sub>  | Chip Enable High to Address Transition         | - 9-                                | 0   |     | ns   |

- 2. V<sub>CC</sub> must be applied simultaneously with or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>

3. Sampled only, not 100% tested.

Figure 9. Programming and Verifix median.

Programming and Verify modes AC waveforms Figure 9.

M27C512 Package mechanical

# 6 Package mechanical

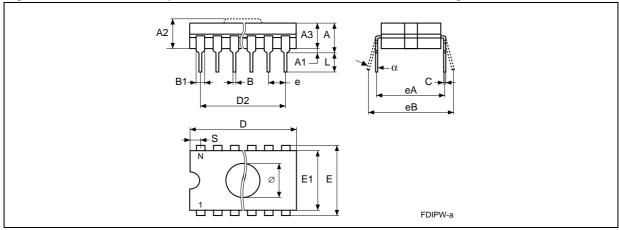

Figure 10. FDIP28W - 28 pin Ceramic Frit-seal DIP, with window, Package Outline

<sup>1.</sup> Drawing is not to scale.

Table 14. FDIP28W - 28 pin Ceramic Frit-seal DIP, with window, Package Mechanical Data

| Symbol |       | millimeters |       | inches |       |       |

|--------|-------|-------------|-------|--------|-------|-------|

|        | Тур   | Min         | Max   | Тур    | Min   | Max   |

| А      |       |             | 5.72  | -011   |       | 0.225 |

| A1     |       | 0.51        | 1.40  | .0     | 0.020 | 0.055 |

| A2     |       | 3.91        | 4.57  |        | 0.154 | 0.180 |

| А3     |       | 3.89        | 4.50  |        | 0.153 | 0.177 |

| В      |       | 0.41        | 0.56  |        | 0.016 | 0.022 |

| B1     | 1.45  |             | _     | 0.057  | -     | _     |

| С      |       | 0.23        | 0.30  |        | 0.009 | 0.012 |

| D      |       | 36.50       | 37.34 |        | 1.437 | 1.470 |

| D2     | 33.02 | -           | -     | 1.300  | -     | -     |

| E      | 15.24 | -           | -     | 0.600  | _     | -     |

| E1     |       | 13.06       | 13.36 |        | 0.514 | 0.526 |

| е      | 2.54  | -           | -     | 0.100  | -     | -     |

| eA     | 14.99 | -           | -     | 0.590  | _     | -     |

| eB     |       | 16.18       | 18.03 |        | 0.637 | 0.710 |

| L      |       | 3.18        | 4.10  |        | 0.125 | 0.161 |

| S      |       | 1.52        | 2.49  |        | 0.060 | 0.098 |

| Ø      | 7.11  | -           | -     | 0.280  | -     | -     |

| α      |       | 4°          | 11°   |        | 4°    | 11°   |

| N      |       | 28          |       |        | 28    |       |

Package mechanical M27C512

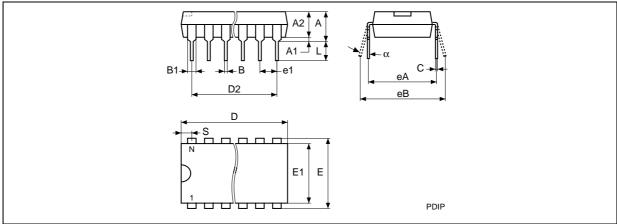

Figure 11. PDIP28 - 28 pin Plastic DIP, 600 mils width, Package Outline

1. Drawing is not to scale.

Table 15. PDIP28 - 28 pin Plastic DIP, 600 mils width, Package Mechanical Data

| Symbol |        | millimeters |        | inches |            |        |

|--------|--------|-------------|--------|--------|------------|--------|

|        | Тур    | Min         | Max    | Тур    | <u>Min</u> | Max    |

| Α      | 4.445  |             |        | 0.1750 | 113        |        |

| A1     | 0.630  |             |        | 0.0248 | CL         |        |

| A2     | 3.810  | 3.050       | 4.570  | 0.1500 | 0.1201     | 0.1799 |

| В      | 0.450  |             |        | 0.0177 |            |        |

| B1     | 1.270  |             | 1 /    | 0.0500 |            |        |

| С      |        | 0.230       | 0.310  |        | 0.0091     | 0.0122 |

| D      | 36.830 | 36.580      | 37.080 | 1.4500 | 1.4402     | 1.4598 |

| D2     | 33.020 | -           | _      | 1.3000 | _          | _      |

| E      | 15.240 |             |        | 0.6000 |            |        |

| E1     | 13.720 | 12.700      | 14.480 | 0.5402 | 0.5000     | 0.5701 |

| e1     | 2.540  | _           | -      | 0.1000 | _          | _      |

| eA     | 15.000 | 14.800      | 15.200 | 0.5906 | 0.5827     | 0.5984 |

| eB     |        | 15.200      | 16.680 |        | 0.5984     | 0.6567 |

| L      | 3.300  |             |        | 0.1299 |            |        |

| S      |        | 1.78        | 2.08   |        | 0.070      | 0.082  |

| α      |        | 0°          | 10°    |        | 0°         | 10°    |

| N      |        | 28          |        |        | 28         | •      |

M27C512 Package mechanical

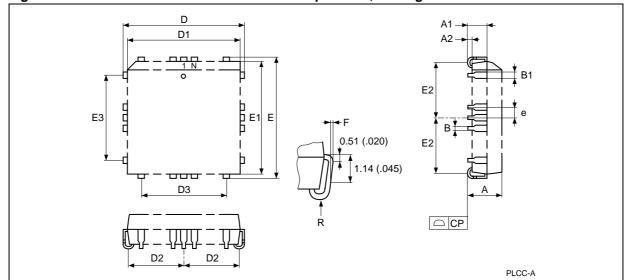

Figure 12. PLCC32 - 32 lead Plastic Leaded Chip Carrier, Package Outline

1. Drawing is not to scale.

Table 16. PLCC32 - 32 lead Plastic Leaded Chip Carrier, Package Mechanical Data

| Symbol | millimeters |       |       | inches |       |       |

|--------|-------------|-------|-------|--------|-------|-------|

|        | Тур         | Min   | Max   | Тур    | Min   | Max   |

| А      |             | 3.18  | 3.56  | CO.    | 0.125 | 0.140 |

| A1     |             | 1.53  | 2.41  |        | 0.060 | 0.095 |

| A2     |             | 0.38  | )' -  |        | 0.015 | _     |

| В      |             | 0.33  | 0.53  |        | 0.013 | 0.021 |

| B1     |             | 0.66  | 0.81  |        | 0.026 | 0.032 |

| СР     |             |       | 0.10  |        |       | 0.004 |

| D      |             | 12.32 | 12.57 |        | 0.485 | 0.495 |

| D1     |             | 11.35 | 11.51 |        | 0.447 | 0.453 |

| D2     |             | 4.78  | 5.66  |        | 0.188 | 0.223 |

| D3     | 7.62        | _     | _     | 0.300  | _     | _     |

| E      |             | 14.86 | 15.11 |        | 0.585 | 0.595 |

| E1     |             | 13.89 | 14.05 |        | 0.547 | 0.553 |

| E2     |             | 6.05  | 6.93  |        | 0.238 | 0.273 |

| E3     | 10.16       | _     | _     | 0.400  | _     | _     |

| е      | 1.27        | -     | _     | 0.050  | _     | _     |

| F      |             | 0.00  | 0.13  |        | 0.000 | 0.005 |

| R      | 0.89        | _     | _     | 0.035  | _     | _     |

| N      |             | 32    | •     |        | 32    | •     |

Part numbering M27C512

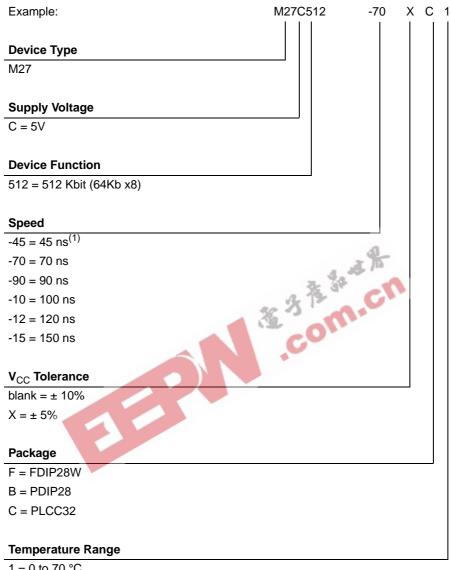

#### Part numbering 7

Table 17. **Ordering Information Scheme**

1 = 0 to 70 °C

3 = -40 to 125 °C

$6 = -40 \text{ to } 85 \,^{\circ}\text{C}$

1. High Speed, see AC Characteristics section for further information.

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST Sales Office.

M27C512 Revision history

# 8 Revision history

Table 18. Document revision history

| Date             | Revision                                                           | Changes                                                                                                                                                                                                                                                                                              |  |  |  |

|------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| November<br>1998 | 1.0                                                                | First Issue                                                                                                                                                                                                                                                                                          |  |  |  |

| 25-Sep-2000      | 1.1                                                                | AN620 Reference removed                                                                                                                                                                                                                                                                              |  |  |  |

| 02-Apr-2001      | 1.2 FDIP28W mechanical dimensions changed ( <blue>Table 14.</blue> |                                                                                                                                                                                                                                                                                                      |  |  |  |

| 29-Aug-2002      | 1.3                                                                | Package mechanical data clarified for PDIP28 ( <i>Table 15</i> ), PLCC32 ( <i>Table 16</i> , <i>Figure 12</i> ) and TSOP28 (Table 16., Figure 7.)                                                                                                                                                    |  |  |  |

| 08-Nov-2004      | 2.0                                                                | Details of ECOPACK lead-free package options added. Additional Burn-in option removed                                                                                                                                                                                                                |  |  |  |

| 18-May-2007      | 3                                                                  | ECOPACK lead-free text updated in Section 1: Description. TLEAD and Note 1 removed from Table 5: Absolute maximum ratings. TSOP28 package removed. 60, 80, 200 and 250 access times removed from the whole document. Blank, TR, E, and F Options removed from Table 17: Ordering Information Scheme. |  |  |  |

|                  |                                                                    | 3 Com. Com. Com. Com. Com. Com. Com. Com.                                                                                                                                                                                                                                                            |  |  |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com