# **Low Noise Dual Operational Amplifier**

The MC33077 is a precision high quality, high frequency, low noise monolithic dual operational amplifier employing innovative bipolar design techniques. Precision matching coupled with a unique analog resistor trim technique is used to obtain low input offset voltages. Dual-doublet frequency compensation techniques are used to enhance the gain bandwidth product of the amplifier. In addition, the MC33077 offers low input noise voltage, low temperature coefficient of input offset voltage, high slew rate, high AC and DC open loop voltage gain and low supply current drain. The all NPN transistor output stage exhibits no deadband cross-over distortion, large output voltage swing, excellent phase and gain margins, low open loop output impedance and symmetrical source and sink AC frequency performance.

The MC33077 is available in plastic DIP and SOIC-8 packages (P and D suffixes).

#### **Features**

- Low Voltage Noise: 4.4 nV/\(\sqrt{Hz}\) @ 1.0 kHz

- Low Input Offset Voltage: 0.2 mV

- Low TC of Input Offset Voltage: 2.0 μV/°C

- High Gain Bandwidth Product: 37 MHz @ 100 kHz

- High AC Voltage Gain: 370 @ 100 kHz 1850 @ 20 kHz

- Unity Gain Stable: with Capacitance Loads to 500 pF

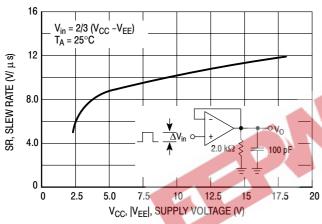

- High Slew Rate: 11 V/µs

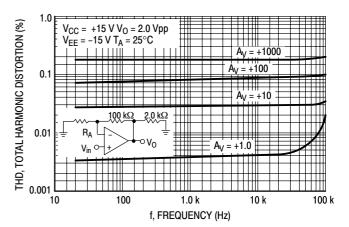

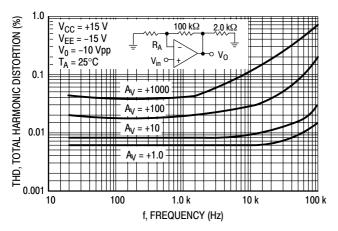

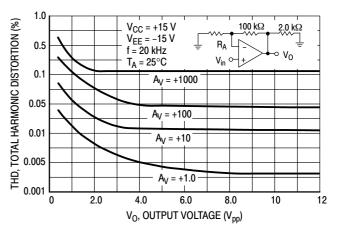

- Low Total Harmonic Distortion: 0.007%

- Large Output Voltage Swing: +14 V to −14.7 V

- High DC Open Loop Voltage Gain: 400 k (112 dB)

- High Common Mode Rejection: 107 dB

- Low Power Supply Drain Current: 3.5 mA

- Dual Supply Operation: ±2.5 V to ±18 V

- Pb-Free Package is Available

ON Semiconductor®

http://onsemi.com

### **MARKING DIAGRAMS**

SOIC-8 **D SUFFIX CASE 751**

PDIP-8 P SUFFIX **CASE 626**

= Assembly Location

= Wafer Lot WL, L YY, Y = Year

WW, W = Work Week

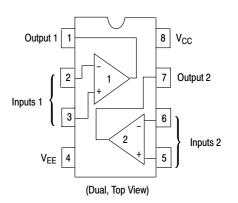

#### **PIN CONNECTIONS**

#### ORDERING INFORMATION

| Device      | Package             | Shipping <sup>†</sup> |

|-------------|---------------------|-----------------------|

| MC33077D    | SOIC-8              | 98 Units/Rail         |

| MC33077DR2  | SOIC-8              | 2500 Tape & Reel      |

| MC33077DR2G | SOIC-8<br>(Pb-Free) | 2500 Tape & Reel      |

| MC33077P    | PDIP-8              | 50 Units/Rail         |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### **MAXIMUM RATINGS**

| Rating                                                         | Symbol           | Value       | Unit |

|----------------------------------------------------------------|------------------|-------------|------|

| Supply Voltage (V <sub>CC</sub> to V <sub>EE</sub> )           | V <sub>S</sub>   | +36         | V    |

| Input Differential Voltage Range                               | $V_{IDR}$        | (Note 1)    | V    |

| Input Voltage Range                                            | V <sub>IR</sub>  | (Note 1)    | V    |

| Output Short Circuit Duration (Note 2)                         | t <sub>SC</sub>  | Indefinite  | sec  |

| Maximum Junction Temperature                                   | TJ               | +150        | °C   |

| Storage Temperature                                            | T <sub>stg</sub> | -60 to +150 | °C   |

| ESD Protection at any Pin  - Human Body Model  - Machine Model | V <sub>esd</sub> | 550<br>150  | V    |

| Maximum Power Dissipation                                      | P <sub>D</sub>   | (Note 2)    | mW   |

| Operating Temperature Range                                    | T <sub>A</sub>   | -40 to + 85 | °C   |

Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If stress limits are exceeded device functional operation is not implied, damage may occur and reliability may be affected. Functional operation should be restricted to the Recommended Operating Conditions.

- Either or both input voltages should not exceed V<sub>CC</sub> or V<sub>EE</sub> (See Applications Information).

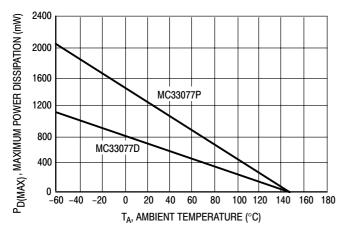

Power dissipation must be considered to ensure maximum junction temperature (T<sub>J</sub>) is not exceeded (See power dissipation performance characteristic, Figure 2).

# **DC ELECTRICAL CHARACTERISTICS** ( $V_{CC}$ = +15 V, $V_{EE}$ = -15 V, $T_A$ = 25°C, unless otherwise noted.)

| Characteristics                                                                                                                                          | Symbol                                                                   | Min                 | Тур                              | Max                      | Unit  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------|----------------------------------|--------------------------|-------|

| Input Offset Voltage (R <sub>S</sub> = 10 $\Omega$ , V <sub>CM</sub> = 0 V, V <sub>O</sub> = 0 V)<br>$T_A$ = +25°C<br>$T_A$ = -40° to +85°C              | V <sub>IO</sub>                                                          | -<br>-              | 0.13<br>-                        | 1.0<br>1.5               | mV    |

| Average Temperature Coefficient of Input Offset Voltage $R_S = 10~\Omega,~V_{CM} = 0~V,~V_O = 0~V,~T_A = -40^\circ$ to +85°C                             | $\Delta V_{IO}/\Delta T$                                                 | -                   | 2.0                              | _                        | μV/°C |

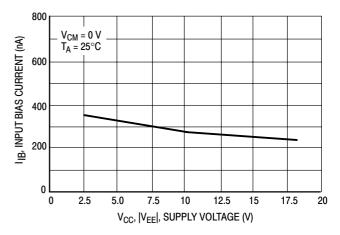

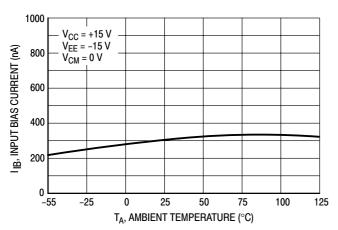

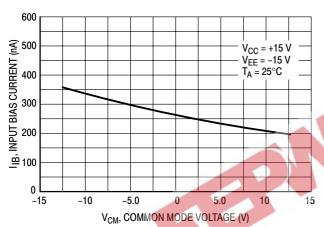

| Input Bias Current ( $V_{CM} = 0 \text{ V}, V_O = 0 \text{ V}$ ) $T_A = +25^{\circ}\text{C}$ $T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}$         | I <sub>IB</sub>                                                          | -                   | 280<br>-                         | 1000<br>1200             | nA    |

| Input Offset Current ( $V_{CM} = 0 \text{ V}, V_{O} = 0 \text{ V}$ ) $T_{A} = +25^{\circ}\text{C}$ $T_{A} = -40^{\circ} \text{ to } +85^{\circ}\text{C}$ | I <sub>IO</sub>                                                          | -                   | 15<br>-                          | 180<br>240               | nA    |

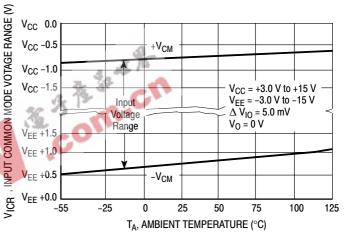

| Common Mode Input Voltage Range ( $\Delta V_{IO}$ ,= 5.0 mV, $V_{O}$ = 0 V)                                                                              | V <sub>ICR</sub>                                                         | ±13.5               | ±14                              | -                        | V     |

| Large Signal Voltage Gain (V $_{O}$ = $\pm 1.0$ V, R $_{L}$ = 2.0 kΩ) $T_{A}$ = +25°C $T_{A}$ = -40° to +85°C                                            | A <sub>VOL</sub>                                                         | 150<br>125          | 400<br>-                         | _<br>_                   | kV/V  |

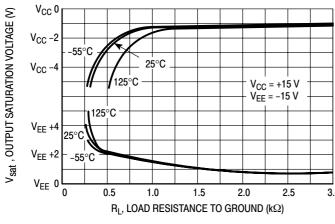

| Output Voltage Swing ( $V_{ID}$ = $\pm 1.0$ V)<br>$R_L$ = 2.0 k $\Omega$<br>$R_L$ = 2.0 k $\Omega$<br>$R_L$ = 10 k $\Omega$<br>$R_L$ = 10 k $\Omega$     | V <sub>O+</sub><br>V <sub>O-</sub><br>V <sub>O+</sub><br>V <sub>O-</sub> | +13.0<br>-<br>+13.4 | +13.6<br>-14.1<br>+14.0<br>-14.7 | -<br>-13.5<br>-<br>-14.3 | V     |

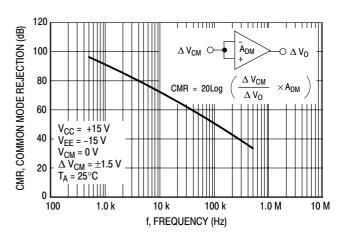

| Common Mode Rejection (V <sub>in</sub> = ±13 V)                                                                                                          | CMR                                                                      | 85                  | 107                              | _                        | dB    |

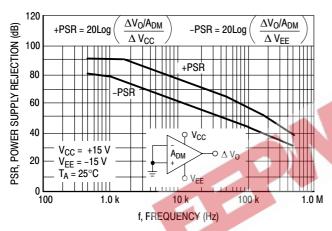

| Power Supply Rejection (Note 3) $V_{CC}/V_{EE} = +15 \text{ V/} -15 \text{ V to } +5.0 \text{ V/} -5.0 \text{ V}$                                        | PSR                                                                      | 80                  | 90                               | _                        | dB    |

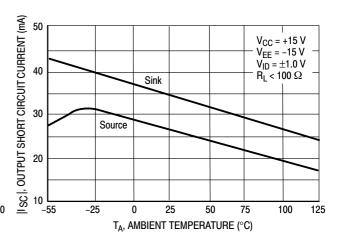

| Output Short Circuit Current ( $V_{ID}$ = $\pm 1.0$ V, Output to Ground)<br>Source<br>Sink                                                               | I <sub>SC</sub>                                                          | +10<br>-20          | +26<br>-33                       | +60<br>+60               | mA    |

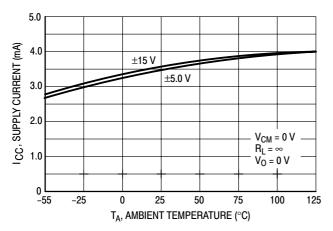

| Power Supply Current ( $V_O = 0 \text{ V}$ , All Amplifiers)<br>$T_A = +25^{\circ}\text{C}$<br>$T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}$       | I <sub>D</sub>                                                           | -<br>-              | 3.5<br>-                         | 4.5<br>4.8               | mA    |

<sup>3.</sup> Measured with  $V_{\mbox{\footnotesize{CC}}}$  and  $V_{\mbox{\footnotesize{EE}}}$  simultaneously varied.

## AC ELECTRICAL CHARACTERISTICS (V $_{CC}$ = +15 V, V $_{EE}$ = -15 V, T $_{A}$ = 25°C, unless otherwise noted.)

| Characteristics                                                                                                                                                                                                                                                                                                                                                            | Symbol          | Min         | Тур                                        | Max              | Unit   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|--------------------------------------------|------------------|--------|

| Slew Rate ( $V_{in} = -10 \text{ V to } +10 \text{ V}, R_L = 2.0 \text{ k}\Omega, C_L = 100 \text{ pF}, A_V = +1.0$ )                                                                                                                                                                                                                                                      | SR              | 8.0         | 11                                         | -                | V/μs   |

| Gain Bandwidth Product (f = 100 kHz)                                                                                                                                                                                                                                                                                                                                       | GBW             | 25          | 37                                         | -                | MHz    |

| AC Voltage Gain (R <sub>L</sub> = $2.0 \text{ k}\Omega$ , V <sub>O</sub> = $0 \text{ V}$ )<br>f = $100 \text{ kHz}$<br>f = $20 \text{ kHz}$                                                                                                                                                                                                                                | A <sub>VO</sub> | -           | 370<br>1850                                | -                | V/V    |

| Unity Gain Bandwidth (Open Loop)                                                                                                                                                                                                                                                                                                                                           | BW              | -           | 7.5                                        | -                | MHz    |

| Gain Margin (R <sub>L</sub> = 2.0 k $\Omega$ , C <sub>L</sub> = 10 pF)                                                                                                                                                                                                                                                                                                     | A <sub>m</sub>  | -           | 10                                         | -                | dB     |

| Phase Margin (R <sub>L</sub> = 2.0 k $\Omega$ , C <sub>L</sub> = 10 pF)                                                                                                                                                                                                                                                                                                    | Ø <sub>m</sub>  | -           | 55                                         | -                | Deg    |

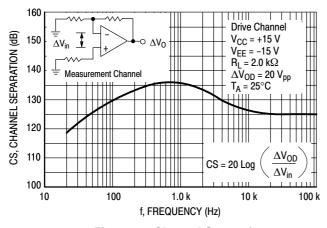

| Channel Separation (f = 20 Hz to 20 kHz, $R_L$ = 2.0 k $\Omega$ , $V_O$ = 10 $V_{pp}$ )                                                                                                                                                                                                                                                                                    | CS              | -           | -120                                       | -                | dB     |

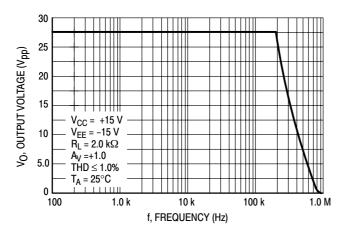

| Power Bandwidth ( $V_O = 27_{p-p}$ , $R_L = 2.0 \text{ k}\Omega$ , THD $\leq 1\%$ )                                                                                                                                                                                                                                                                                        | BW <sub>p</sub> | -           | 200                                        | -                | kHz    |

| $\begin{aligned} & \text{Distortion } (R_L = 2.0 \text{ k}\Omega) \\ & A_V = +1.0, \ f = 20 \text{ Hz to } 20 \text{ kHz} \\ & V_O = 3.0 \text{ V}_{RMS} \\ & A_V = 2000, \ f = 20 \text{ kHz} \\ & V_O = 2.0 \text{ V}_{pp} \\ & V_O = 10 \text{ V}_{pp} \\ & A_V = 4000, \ f = 100 \text{ kHz} \\ & V_O = 2.0 \text{ V}_{pp} \\ & V_O = 10 \text{ V}_{pp} \end{aligned}$ | THD             | -           | 0.007<br>0.215<br>0.242<br>0.3.19<br>0.316 | -<br>-<br>-<br>- | %      |

| Open Loop Output Impedance (V <sub>O</sub> = 0 V, f = f <sub>U</sub> )                                                                                                                                                                                                                                                                                                     | Z <sub>O</sub>  | _           | 36                                         | -                | Ω      |

| Differential Input Resistance (V <sub>CM</sub> = 0 V)                                                                                                                                                                                                                                                                                                                      | R <sub>in</sub> | _           | 270                                        | -                | kΩ     |

| Differential Input Capacitance (V <sub>CM</sub> = 0 V)                                                                                                                                                                                                                                                                                                                     | C <sub>in</sub> | _           | 15                                         | _                | pF     |

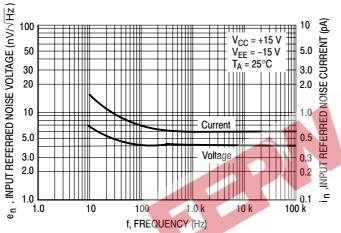

| Equivalent Input Noise Voltage ( $R_S$ = 100 $\Omega$ )<br>f = 10 Hz<br>f = 1.0 kHz                                                                                                                                                                                                                                                                                        | e <sub>n</sub>  | 1 1         | 6.7<br>4.4                                 | _<br>            | nV/√Hz |

| Equivalent Input Noise Current (f = 1.0 kHz) f = 10 Hz f = 1.0 kHz                                                                                                                                                                                                                                                                                                         | i <sub>n</sub>  | _<br>_<br>_ | 1.3<br>0.6                                 | _<br>_<br>_      | pA/√Hz |

Figure 2. Maximum Power Dissipation versus Temperature

Figure 3. Input Bias Current versus Supply Voltage

Figure 4. Input Bias Current versus Temperature

Figure 5. Input Offset Voltage versus Temperature

Figure 6. Input Bias Current versus

Common Mode Voltage

Figure 7. Input Common Mode Voltage Range versus Temperature

Figure 8. Output Saturation Voltage versus Load Resistance to Ground

Figure 9. Output Short Circuit Current versus Temperature

Figure 10. Supply Current versus Temperature

Figure 11. Common Mode Rejection versus Frequency

Figure 12. Power Supply Rejection versus Frequency

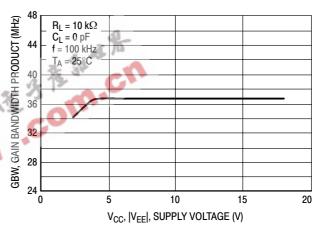

Figure 13. Gain Bandwidth Product versus Supply Voltage

Figure 14. Gain Bandwidth Product versus Temperature

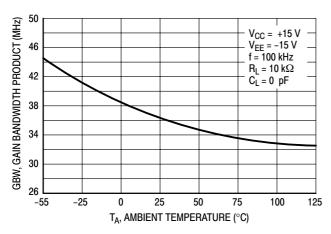

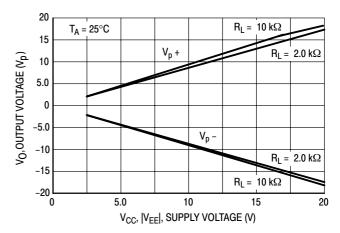

Figure 15. Maximum Output Voltage versus Supply Voltage

Figure 16. Output Voltage versus Frequency

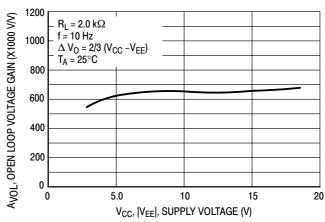

Figure 17. Open Loop Voltage Gain versus Supply Voltage

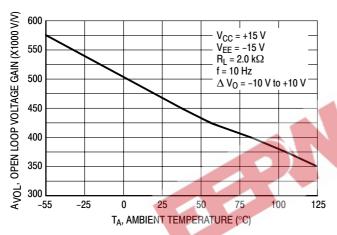

Figure 18. Open Loop Voltage Gain versus Temperature

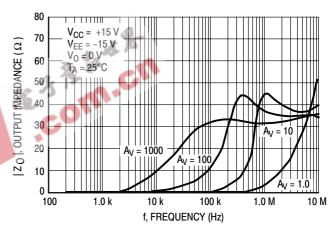

Figure 19. Output Impedance versus Frequency

Figure 20. Channel Separation versus Frequency

Figure 21. Total Harmonic Distortion versus Frequency

Figure 22. Total Harmonic Distortion versus Frequency

Figure 23. Total Harmonic Distortion versus Output Voltage

Figure 24. Slew Rate versus Supply Voltage

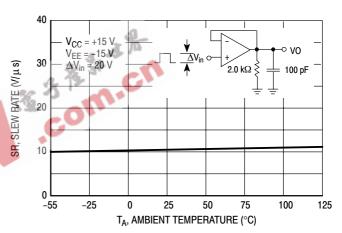

Figure 25. Slew Rate versus Temperature

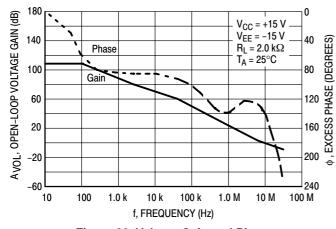

Figure 26. Voltage Gain and Phase versus Frequency

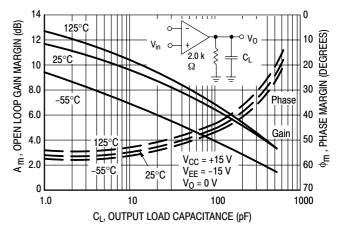

Figure 27. Open Loop Gain Margin and Phase Margin versus Output Load Capacitance

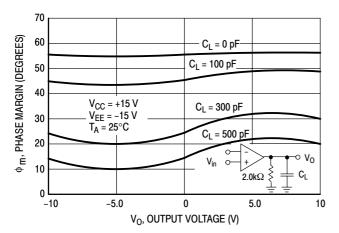

Figure 28. Phase Margin versus

Output Voltage

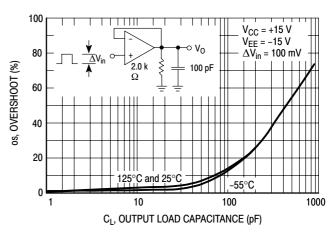

Figure 29. Overshoot versus Output Load Capacitance

Figure 30. Input Referred Noise Voltage and Current versus Frequency

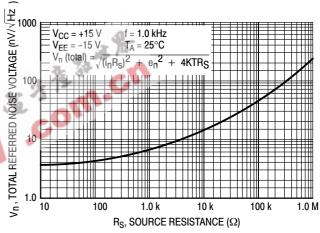

Figure 31. Total Input Referred Noise Voltage versus Source Resistant

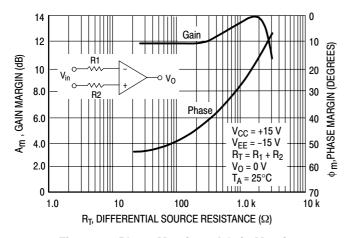

Figure 32. Phase Margin and Gain Margin versus Differential Source Resistance

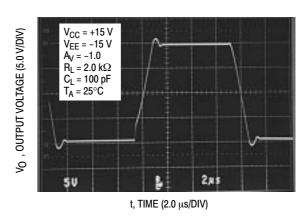

Figure 33. Inverting Amplifier Slew Rate

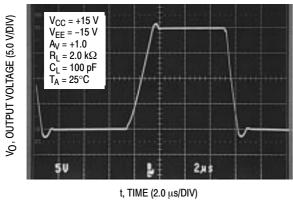

Figure 34. Non-inverting Amplifier Slew Rate

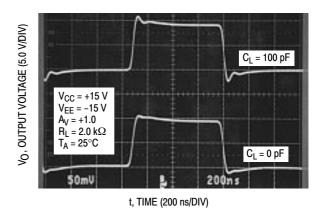

Figure 35. Non-inverting Amplifier Overshoot

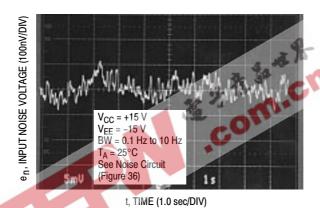

Figure 36. Low Frequency Noise Voltage versus Time

#### **APPLICATIONS INFORMATION**

The MC33077 is designed primarily for its low noise, low offset voltage, high gain bandwidth product and large output swing characteristics. Its outstanding high frequency gain/phase performance make it a very attractive amplifier for high quality preamps, instrumentation amps, active filters and other applications requiring precision quality characteristics.

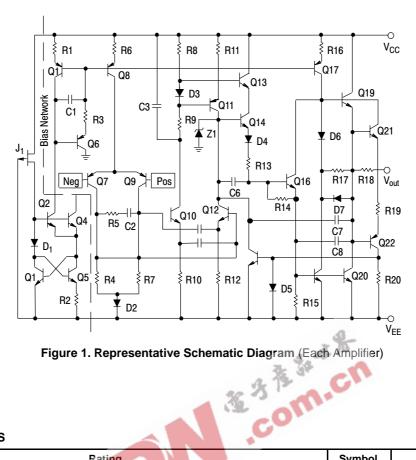

The MC33077 utilizes high frequency lateral PNP input transistors in a low noise bipolar differential stage driving a compensated Miller integration amplifier. Dual–doublet frequency compensation techniques are used to enhance the gain bandwidth product. The output stage uses an all NPN transistor design which provides greater output voltage swing and improved frequency performance over more conventional stages by using both PNP and NPN transistors (Class AB). This combination produces an amplifier with superior characteristics.

Through precision component matching and innovative current mirror design, a lower than normal temperature coefficient of input offset voltage (2.0  $\mu$ V/°C as opposed to 10  $\mu$ V/°C), as well as low input offset voltage, is accomplished.

The minimum common mode input range is from 1.5 V below the positive rail ( $V_{CC}$ ) to 1.5 V above the negative rail ( $V_{EE}$ ). The inputs will typically common mode to within 1.0 V of both negative and positive rails though degradation in offset voltage and gain will be experienced as the common mode voltage nears either supply rail. In practice, though not recommended, the input voltage may exceed  $V_{CC}$  by approximately 3.0 V and decrease below the  $V_{EE}$  by approximately 0.6 V without causing permanent damage to the device. If the input voltage on either or both inputs is less than approximately 0.6 V, excessive current may flow, if not limited, causing permanent damage to the device.

The amplifier will not latch with input source currents up to 20 mA, though in practice, source currents should be limited to 5.0 mA to avoid any parametric damage to the device. If both inputs exceed  $V_{CC}$ , the output will be in the high state and phase reversal may occur. No phase reversal will occur if the voltage on one input is within the common mode range and the voltage on the other input exceeds  $V_{CC}$ . Phase reversal may occur if the input voltage on either or both inputs is less than 1.0 V above the negative rail. Phase reversal will be experienced if the voltage on either or both inputs is less than  $V_{EE}$ .

Through the use of dual—doublet frequency compensation techniques, the gain bandwidth product has been greatly enhanced over other amplifiers using the conventional single pole compensation. The phase and gain error of the amplifier remains low to higher frequencies for fixed amplifier gain configurations.

With the all NPN output stage, there is minimal swing loss to the supply rails, producing superior output swing, no crossover distortion and improved output phase symmetry with output voltage excursions (output phase symmetry being the amplifiers ability to maintain a constant phase relation independent of its output voltage swing). Output phase symmetry degradation in the more conventional PNP and NPN transistor output stage was primarily due to the inherent cut—off frequency mismatch of the PNP and NPN transistors used (typically 10 MHz and 300 MHz, respectively), causing considerable phase change to occur as the output voltage changes. By eliminating the PNP in the output, such phase change has been avoided and a very significant improvement in output phase symmetry as well as output swing has been accomplished.

The output swing improvement is most noticeable when operation is with lower supply voltages (typically 30% with  $\pm$  5.0 V supplies). With a 10 k load, the output of the amplifier can typically swing to within 1.0 V of the positive rail (V<sub>CC</sub>), and to within 0.3 V of the negative rail (V<sub>EE</sub>), producing a 28.7 V<sub>pp</sub> signal from ±15 V supplies. Output voltage swing can be further improved by using an output pull-up resistor referenced to the V<sub>CC</sub>. Where output signals are referenced to the positive supply rail, the pull-up resistor will pull the output to  $V_{\mbox{\footnotesize{CC}}}$  during the positive swing, and during the negative swing, the NPN output transistor collector will pull the output very near V<sub>EE</sub>. This configuration will produce the maximum attainable output signal from given supply voltages. The value of load resistance used should be much less than any feedback resistance to avoid excess loading and allow easy pull-up of

Output impedance of the amplifier is typically less than 50  $\Omega$  at frequencies less than the unity gain crossover frequency (see Figure 19). The amplifier is unity gain stable with output capacitance loads up to 500 pF at full output swing over the  $-55^\circ$  to  $+125^\circ C$  temperature range. Output phase symmetry is excellent with typically 4°C total phase change over a 20 V output excursion at 25°C with a 2.0 k $\Omega$  and 100 pF load. With a 2.0 k $\Omega$  resistive load and no capacitance loading, the total phase change is approximately one degree for the same 20 V output excursion. With a 2.0 k $\Omega$  and 500 pF load at 125°C, the total phase change is typically only 10°C for a 20 V output excursion (see Figure 28).

As with all amplifiers, care should be exercised to insure that one does not create a pole at the input of the amplifier which is near the closed loop corner frequency. This becomes a greater concern when using high frequency amplifiers since it is very easy to create such a pole with relatively small values of resistance on the inputs. If this does occur, the amplifier's phase will degrade severely causing the amplifier to become unstable. Effective source resistances, acting in conjunction with the input capacitance of the amplifier, should be kept to a minimum to avoid creating such a pole at the input (see Figure 32). There is minimal effect on stability where the created input pole is much greater than the closed loop corner frequency. Where amplifier stability is affected as a result of a negative feedback resistor in conjunction with the

amplifier's input capacitance, creating a pole near the closed loop corner frequency, lead capacitor compensation techniques (lead capacitor in parallel with the feedback resistor) can be employed to improve stability. The feedback resistor and lead capacitor RC time constant should be larger than that of the uncompensated input pole frequency. Having a high resistance connected to the noninverting input of the amplifier can create a like instability problem. Compensation for this condition can be accomplished by adding a lead capacitor in parallel with the noninverting input resistor of such a value as to make the RC time constant larger than the RC time constant of the uncompensated input resistor acting in conjunction with the amplifiers input capacitance.

For optimum frequency performance and stability, careful component placement and printed circuit board layout should be exercised. For example, long unshielded input or output leads may result in unwanted input output coupling. In order to reduce the input capacitance, the body of resistors connected to the input pins should be physically close to the input pins. This not only minimizes the input pole creation for optimum frequency response, but also minimizes extraneous signal "pickup" at this node. Power supplies should be decoupled with adequate capacitance as close as possible to the device supply pin.

In addition to amplifier stability considerations, input source resistance values should be low to take full advantage of the low noise characteristics of the amplifier. Thermal noise (Johnson Noise) of a resistor is generated by thermally-charged carriers randomly moving within the resistor creating a voltage. The RMS thermal noise voltage in a resistor can be calculated from:

$$E_{nr} = / \overline{4k \, TR \times BW}$$

where:

$k = Boltzmann's Constant (1.38 \times 10^{-23} joules/k)$

T = Kelvin temperature

R = Resistance in ohms

BW = Upper and lower frequency limit in Hertz.

By way of reference, a 1.0 k $\Omega$  resistor at 25°C will produce a 4.0 nV/ $\sqrt{\text{Hz}}$  of RMS noise voltage. If this resistor is connected to the input of the amplifier, the noise voltage will be gained—up in accordance to the amplifier's gain configuration. For this reason, the selection of input source resistance for low noise circuit applications warrants serious consideration. The total noise of the amplifier, as referred to its inputs, is typically only 4.4 nV/ $\sqrt{\text{Hz}}$  at 1.0 kHz.

The output of any one amplifier is current limited and thus protected from a direct short to ground, However, under such conditions, it is important not to allow the amplifier to exceed the maximum junction temperature rating. Typically for  $\pm 15~\rm V$  supplies, any one output can be shorted continuously to ground without exceeding the temperature rating.

Note: All capacitors are non-polarized.

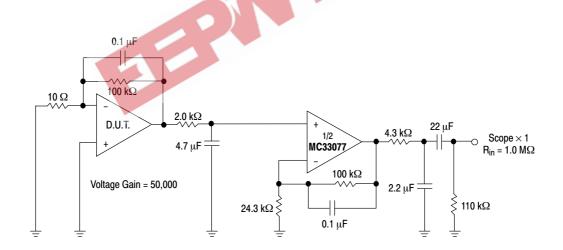

Figure 37. Voltage Noise Test Circuit (0.1 Hz to 10  ${\rm Hz}_{\rm p-p}$ )

#### **PACKAGE DIMENSIONS**

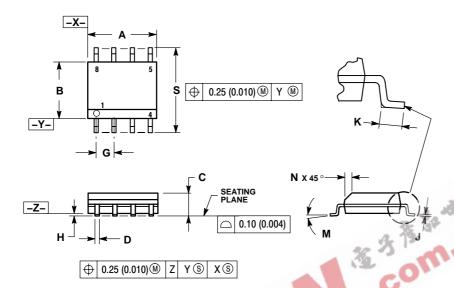

## SOIC-8 **D SUFFIX** CASE 751-07 **ISSUE AB**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

- 2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

- STANDARD IS 751-07.

|     | MILLIMETERS |      | MILLIMETERS INCHE |       | HES |

|-----|-------------|------|-------------------|-------|-----|

| DIM | MIN         | MAX  | MIN               | MAX   |     |

| Α   | 4.80        | 5.00 | 0.189             | 0.197 |     |

| ∞ B | 3.80        | 4.00 | 0.150             | 0.157 |     |

| C   | 1.35        | 1.75 | 0.053             | 0.069 |     |

| D   | 0.33        | 0.51 | 0.013             | 0.020 |     |

| G   | 1.27 BSC    |      | 0.050 BSC         |       |     |

| H   | 0.10        | 0.25 | 0.004             | 0.010 |     |

| J   | 0.19        | 0.25 | 0.007             | 0.010 |     |

| K   | 0.40        | 1.27 | 0.016             | 0.050 |     |

| М   | 0 °         | 8 °  | 0 ° 8             |       |     |

| N   | 0.25        | 0.50 | 0.010             | 0.020 |     |

| S   | 5.80        | 6.20 | 0.228             | 0.244 |     |

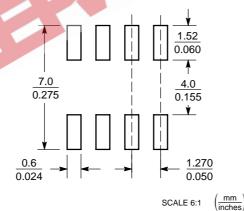

## **SOLDERING FOOTPRINT\***

#### SOIC-8

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

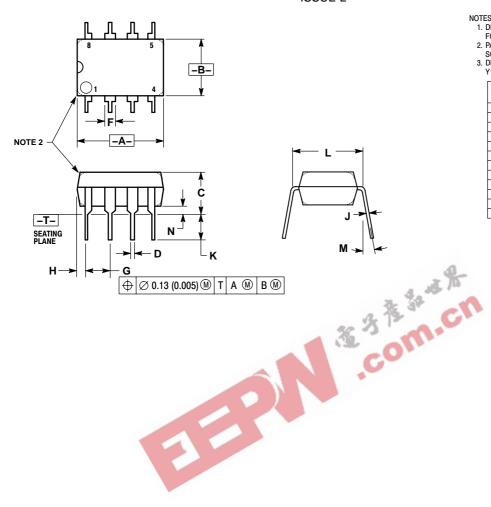

PDIP-8 **P SUFFIX** CASE 626-05 ISSUE L

#### NOTES:

- DIMENSION L TO CENTER OF LEAD WHEN FORMED PARALLEL.

- 2. PACKAGE CONTOUR OPTIONAL (ROUND OR SQUARE CORNERS).

- 3. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

|     | MILLIMETERS |       | INC       | HES   |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| Α   | 9.40        | 10.16 | 0.370     | 0.400 |

| В   | 6.10        | 6.60  | 0.240     | 0.260 |

| С   | 3.94        | 4.45  | 0.155     | 0.175 |

| D   | 0.38        | 0.51  | 0.015     | 0.020 |

| F   | 1.02        | 1.78  | 0.040     | 0.070 |

| G   | 2.54 BSC    |       | 0.100 BSC |       |

| Н   | 0.76        | 1.27  | 0.030     | 0.050 |

| J   | 0.20        | 0.30  | 0.008     | 0.012 |

| K   | 2.92        | 3.43  | 0.115     | 0.135 |

| L   | 7.62 BSC    |       | 0.300 BSC |       |

| M   |             | 10°   |           | 10°   |

| N   | 0.76        | 1.01  | 0.030     | 0.040 |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized legal and several sources. associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2-9-1 Kamimeguro, Meguro-ku, Tokyo, Japan 153-0051 Phone: 81-3-5773-3850

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative