# MC68HC05L25

**Data Sheet**

MC68HC05L25 Rev. 3.1 9/2005

freescale.com

# MC68HC05L25

#### **Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://www.freescale.com/

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

# **Revision History**

| Date               | Revision<br>Level | Description                                                                      | Page<br>Number(s) |

|--------------------|-------------------|----------------------------------------------------------------------------------|-------------------|

| May,<br>2002       | 3.0               | Reformatted to add additional page references and correct World Wide Web address | N/A               |

| September,<br>2005 | 3.1               | Updated to meet Freescale identity guidelines.                                   | Throughout        |

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2005. All rights reserved.

**Revision History**

# **List of Chapters**

| Chapter 1 General Description                                                                                    |     |

|------------------------------------------------------------------------------------------------------------------|-----|

| Chapter 2 Memory Map                                                                                             | 23  |

| Chapter 3 Operating Modes                                                                                        | 31  |

| Chapter 4 Central Processor Unit (CPU) Core                                                                      | 35  |

| Chapter 5 Resets                                                                                                 | 39  |

| Chapter 6 Interrupts                                                                                             | 41  |

| Chapter 7 Input/Output Ports (I/O)                                                                               | 49  |

| Chapter 6 Interrupts  Chapter 7 Input/Output Ports (I/O).  Chapter 8 Oscillators and Clock  Chapter 9 Time Base. | 75  |

| Chapter 9 Time Base                                                                                              |     |

| Chapter 10 Serial Peripheral Interface                                                                           |     |

| Chapter 11 LCD Driver                                                                                            |     |

| Chapter 12 Analog Subsystem                                                                                      |     |

| Chapter 13 Event Counter                                                                                         |     |

| Chapter 14 Instruction Set                                                                                       | 123 |

| Chapter 15 Electrical Specifications                                                                             | 137 |

| Chapter 16 Mechanical Specifications                                                                             | 145 |

| Chapter 17 Ordering Information                                                                                  | 147 |

**List of Chapters**

# **Table of Contents**

# Chapter 1 General Description

| 1.1                                                                              | Introduction                                                                                                                                                                                                                             | . 13                                                 |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1.2                                                                              | Features                                                                                                                                                                                                                                 | . 13                                                 |

| 1.3                                                                              | Mask Options                                                                                                                                                                                                                             | . 14                                                 |

| 1.4                                                                              | MCU Structure                                                                                                                                                                                                                            | . 14                                                 |

| 1.5                                                                              | Functional Pin Description                                                                                                                                                                                                               | . 16                                                 |

| 1.5.1                                                                            | V <sub>DD</sub> and V <sub>SS</sub>                                                                                                                                                                                                      |                                                      |

| 1.5.2                                                                            | V <sub>LCD</sub>                                                                                                                                                                                                                         | . 20                                                 |

| 1.5.3                                                                            | RESET                                                                                                                                                                                                                                    | . 20                                                 |

| 1.5.4                                                                            | OSC1 and OSC2 Crystal or Ceramic Resonator External Clock XOSC1 and XOSC2. Crystal                                                                                                                                                       | . 20                                                 |

| 1.5.4.1                                                                          | Crystal or Ceramic Resonator                                                                                                                                                                                                             | . 21                                                 |

| 1.5.4.2                                                                          | External Clock                                                                                                                                                                                                                           | . 21                                                 |

| 1.5.5                                                                            | XOSC1 and XOSC2                                                                                                                                                                                                                          | . 21                                                 |

| 1.5.5.1                                                                          | Crystal                                                                                                                                                                                                                                  | . 21                                                 |

| 1.5.5.2                                                                          | External Clock                                                                                                                                                                                                                           | . 22                                                 |

| 1.5.5.3                                                                          |                                                                                                                                                                                                                                          | . 22                                                 |

| 1.5.6                                                                            | PA0-PA2/KWI0-KWI2, PA3/KWI3/BZ, PA4/AD0/EVI, PA5/ADI, PA6/RMO, and PA7                                                                                                                                                                   |                                                      |

| 1.5.7                                                                            | PB0–PB7/FP24–FP17                                                                                                                                                                                                                        | . 22                                                 |

| 1.5.8                                                                            | PC0/SCK, PC1/SDO, PC2/SDI, and PC3/IRQ                                                                                                                                                                                                   | . 22                                                 |

| 1.5.9                                                                            | BP3/FP0, FP1–FP18, and PB0–PB7/FP24–FP17                                                                                                                                                                                                 |                                                      |

| 1 5 10                                                                           | BP0-BP2 and BP3/FP0                                                                                                                                                                                                                      | 22                                                   |

| 1.5.10                                                                           | DI 0-DI 2 and DI 3/110                                                                                                                                                                                                                   | . 22                                                 |

| 1.5.10                                                                           |                                                                                                                                                                                                                                          | . 22                                                 |

| 1.5.10                                                                           | Chapter 2 Memory Map                                                                                                                                                                                                                     | . 22                                                 |

| 2.1                                                                              | Chapter 2                                                                                                                                                                                                                                |                                                      |

|                                                                                  | Chapter 2<br>Memory Map                                                                                                                                                                                                                  | . 23                                                 |

| 2.1                                                                              | Chapter 2 Memory Map Introduction                                                                                                                                                                                                        | . 23<br>. 24                                         |

| 2.1                                                                              | Chapter 2 Memory Map Introduction Input/Output and Control Registers                                                                                                                                                                     | . 23<br>. 24<br>. 24                                 |

| 2.1<br>2.2<br>2.2.1                                                              | Chapter 2 Memory Map Introduction Input/Output and Control Registers Read/Write Bits                                                                                                                                                     | . 23<br>. 24<br>. 24                                 |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4                                   | Chapter 2 Memory Map Introduction Input/Output and Control Registers Read/Write Bits Read-Only Bits                                                                                                                                      | . 23<br>. 24<br>. 24<br>. 24                         |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5                          | Chapter 2 Memory Map  Introduction  Input/Output and Control Registers Read/Write Bits Read-Only Bits Write-Only Bits Reserved Bits Reset Value                                                                                          | . 23<br>. 24<br>. 24<br>. 24<br>. 24                 |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6                 | Chapter 2 Memory Map  Introduction Input/Output and Control Registers Read/Write Bits Read-Only Bits Write-Only Bits Reserved Bits. Reset Value Option Map.                                                                              | . 23<br>. 24<br>. 24<br>. 24<br>. 24<br>. 25         |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5                          | Chapter 2 Memory Map  Introduction  Input/Output and Control Registers Read/Write Bits Read-Only Bits Write-Only Bits Reserved Bits Reset Value                                                                                          | . 23<br>. 24<br>. 24<br>. 24<br>. 24<br>. 25         |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6                 | Chapter 2 Memory Map  Introduction Input/Output and Control Registers Read/Write Bits Read-Only Bits Write-Only Bits Reserved Bits. Reset Value Option Map.                                                                              | . 23<br>. 24<br>. 24<br>. 24<br>. 25<br>. 25         |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7        | Chapter 2 Memory Map  Introduction Input/Output and Control Registers Read/Write Bits Read-Only Bits Write-Only Bits Reserved Bits. Reset Value Option Map. Random-Access Memory (RAM)                                                   | . 23<br>. 24<br>. 24<br>. 24<br>. 25<br>. 25         |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7        | Chapter 2 Memory Map  Introduction Input/Output and Control Registers Read/Write Bits Read-Only Bits Write-Only Bits Reserved Bits Reset Value Option Map. Random-Access Memory (RAM)  Read-Only Memory (ROM)                            | . 23<br>. 24<br>. 24<br>. 24<br>. 25<br>. 25         |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.3 | Chapter 2 Memory Map  Introduction Input/Output and Control Registers Read/Write Bits Read-Only Bits Write-Only Bits Reserved Bits Reset Value Option Map. Random-Access Memory (RAM)  Read-Only Memory (ROM)  Chapter 3 Operating Modes | . 23<br>. 24<br>. 24<br>. 25<br>. 25<br>. 25         |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7        | Chapter 2 Memory Map  Introduction Input/Output and Control Registers Read/Write Bits Read-Only Bits Write-Only Bits Reserved Bits Reset Value Option Map. Random-Access Memory (RAM)  Read-Only Memory (ROM)  Chapter 3                 | . 23<br>. 24<br>. 24<br>. 24<br>. 25<br>. 25<br>. 25 |

| Table of       | f Contents                                                                                                                                                                                                  |          |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

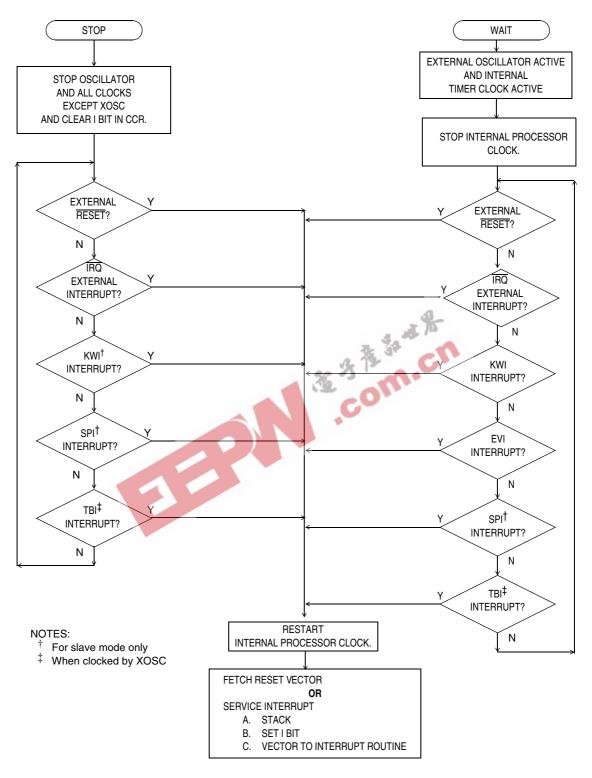

| 3.3            | Low-Power Modes                                                                                                                                                                                             |          |

| 3.3.1          | STOP Instruction                                                                                                                                                                                            |          |

| 3.3.2          | WAIT Instruction                                                                                                                                                                                            |          |

| 3.4            | COP Watchdog Timer Considerations 3                                                                                                                                                                         | iJ       |

|                | Chapter 4                                                                                                                                                                                                   |          |

|                | Central Processor Unit (CPU) Core                                                                                                                                                                           |          |

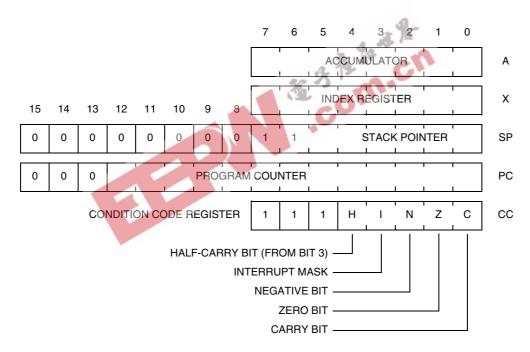

| 4.1            | Introduction                                                                                                                                                                                                |          |

| 4.2            | Registers                                                                                                                                                                                                   |          |

| 4.2.1<br>4.2.2 | Accumulator                                                                                                                                                                                                 |          |

| 4.2.2          | Stack Pointer                                                                                                                                                                                               |          |

| 4.2.4          | Program Counter                                                                                                                                                                                             |          |

| 4.2.5          | Condition Code Register                                                                                                                                                                                     |          |

|                | Chapter 5                                                                                                                                                                                                   |          |

|                | Resets                                                                                                                                                                                                      |          |

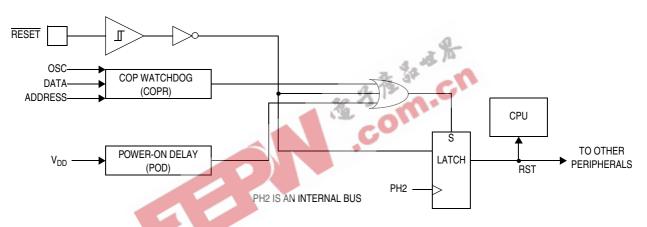

| 5.1            |                                                                                                                                                                                                             | ŧΟ       |

| 5.2            | External Reset (RESET)                                                                                                                                                                                      | ,o<br>{9 |

| 5.3            | Internal Resets                                                                                                                                                                                             | 19       |

| 5.3.1          | Power-On Delay (POD)                                                                                                                                                                                        | 10       |

| 5.3.2          | Introduction         3           External Reset (RESET)         3           Internal Resets         3           Power-On Delay (POD)         4           Computer Operating Properly Reset (COPR)         4 | 0        |

|                | Chapter 6                                                                                                                                                                                                   |          |

|                | Interrupts                                                                                                                                                                                                  |          |

| 6.1            | Introduction                                                                                                                                                                                                | 11       |

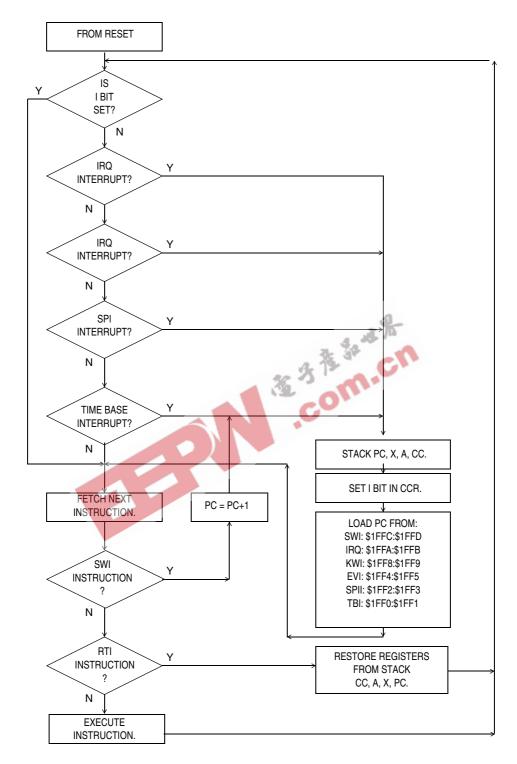

| 6.2            | CPU Interrupt Processing                                                                                                                                                                                    |          |

| 6.3            | Reset Interrupt Sequence                                                                                                                                                                                    |          |

| 6.4            | Software Interrupt (SWI)                                                                                                                                                                                    |          |

| 6.5            | Hardware Interrupts                                                                                                                                                                                         |          |

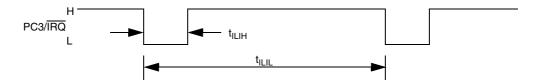

| 6.6            | External Interrupt (IRQ)                                                                                                                                                                                    |          |

| 6.6.1          | External Interrupt Trigger Condition4                                                                                                                                                                       |          |

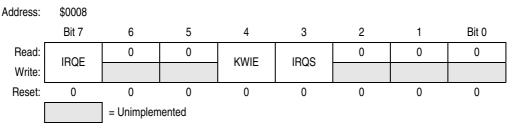

| 6.6.2          | Interrupt Control Register                                                                                                                                                                                  |          |

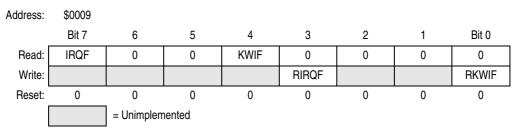

| 6.6.3          | Interrupt Status Register                                                                                                                                                                                   |          |

| 6.7            | Serial Peripheral Interface Interrupt (SPII)                                                                                                                                                                |          |

| 6.8            | Event Counter Interrupt (EVI)                                                                                                                                                                               |          |

| 6.9            | Time Base Interrupt (TBI)                                                                                                                                                                                   |          |

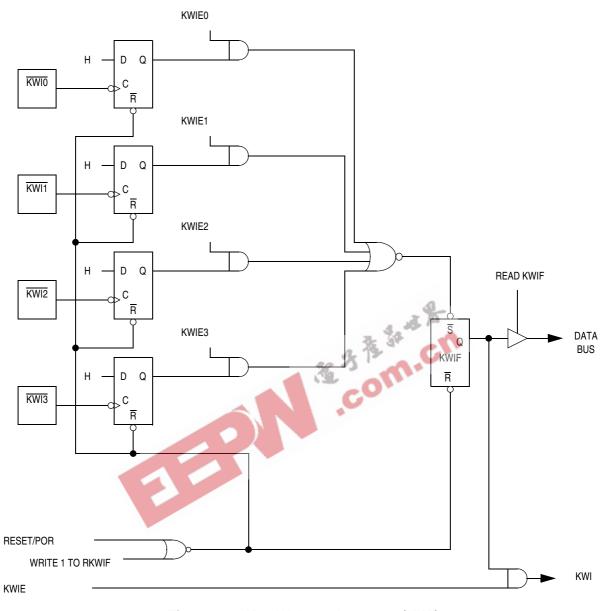

| 6.10           | Key Wakeup Interrupt (KWI)                                                                                                                                                                                  |          |

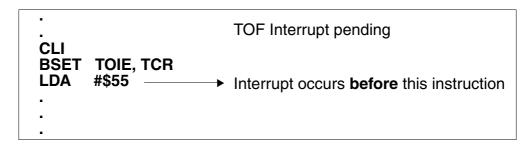

| 6.11           | IRQ/KWI Software Consideration                                                                                                                                                                              | ю        |

|                | Chapter 7 Input/Output Ports (I/O)                                                                                                                                                                          |          |

| 7.1            | Introduction                                                                                                                                                                                                | 0        |

| 7.1            | Port A 4                                                                                                                                                                                                    |          |

| 7.2<br>7.2.1   | Port A Data Register                                                                                                                                                                                        |          |

| 7.2.2          | Port A Data Direction Register                                                                                                                                                                              |          |

|                |                                                                                                                                                                                                             | _        |

MC68HC05L25 Data Sheet, Rev. 3.1

8

|                |                                                                                      | Table of Contents |

|----------------|--------------------------------------------------------------------------------------|-------------------|

| 7.2.3          | Port A Pullup Register                                                               | 54                |

| 7.2.4          | Port A Wired-OR Mode Register                                                        |                   |

| 7.2.5          | Key Wakeup Interrupt (KWI)                                                           |                   |

| 7.2.6          | I/O Pin Truth Tables                                                                 |                   |

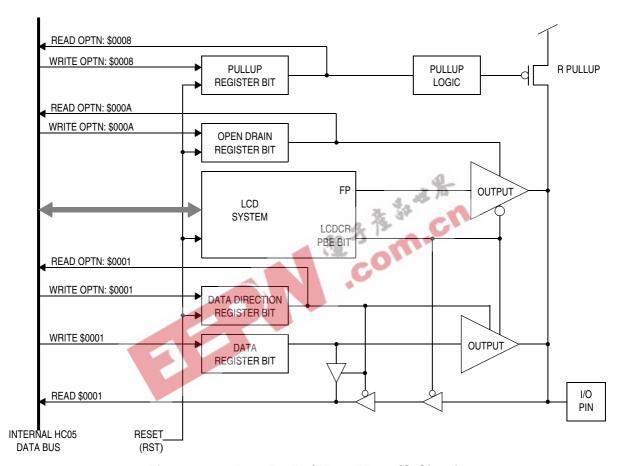

| 7.3            | Port B                                                                               |                   |

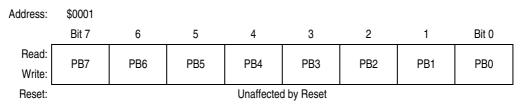

| 7.3.1          | Port B Data Register                                                                 |                   |

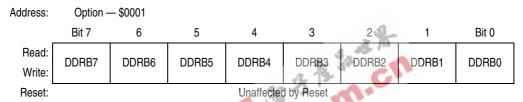

| 7.3.2          | Port B Data Direction Register                                                       |                   |

| 7.3.3          | Port B Pullup Register                                                               |                   |

| 7.3.4          | Port B Wire-ORed Mode Register                                                       | 62                |

| 7.3.5          | I/O Pin Truth Tables                                                                 | 63                |

| 7.4            | Port C                                                                               | 64                |

| 7.4.1          | Port C Data Register                                                                 |                   |

| 7.4.2          | Port C Data Direction Register                                                       |                   |

| 7.4.3          | Port C Pullup Register                                                               |                   |

| 7.4.4          | Port C Wired-OR Mode Register                                                        |                   |

| 7.4.5          | I/O Pin Truth Tables                                                                 |                   |

| 7.5            | I/O Port Programming                                                                 | 71                |

| 7.5.1          | Pin Data Direction                                                                   | 71                |

| 7.5.2          | Output Pin                                                                           | 71                |

| 7.5.3          | Pin Data Direction Output Pin Input Pin I/O Pin Transitions I/O Pins with Subsystems | 71                |

| 7.5.4          | I/O Pin Transitions                                                                  |                   |

| 7.5.5          | I/O Pins with Subsystems                                                             |                   |

| 7.5.6          | Resistor Control Register 1                                                          | 70                |

| 7.5.7<br>7.5.8 | Resistor Control Register 2                                                          | 74                |

| 7.5.0          | Open Drain Output Control Negister                                                   |                   |

|                | Chapter 8                                                                            |                   |

|                | Oscillators and Clock                                                                |                   |

| 3.1            | Introduction                                                                         | 75                |

| 3.2            | OSC Clock Divider and POR Counter                                                    | 75                |

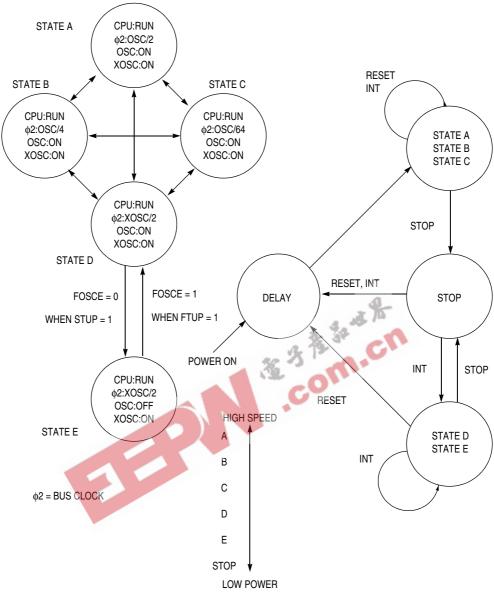

| 3.3            | System Clock Control                                                                 | 75                |

| 3.4            | OSC and XOSC                                                                         |                   |

| 3.5            | OSC On Line                                                                          |                   |

| 3.6            | XOSC On Line                                                                         |                   |

| 3.6.1          | XOSC with FOSCE = 1                                                                  |                   |

| 3.6.2          | XOSC with FOSCE = 0                                                                  |                   |

| 3.6.3          | XOSC with FOSCE = 0 and STOP                                                         |                   |

| 3.6.4          | Unused XOSC                                                                          |                   |

| 3.7            | Stop and Wait Modes                                                                  |                   |

| 3.8            | XOSC Clock Divider and POD Counter                                                   |                   |

| 3.0<br>3.9     | System Clock Control                                                                 |                   |

|                | •                                                                                    |                   |

| 3.10           | XOSC                                                                                 |                   |

| 3.11           | Stop and Wait Modes                                                                  |                   |

| 3.12           | Miscellaneous Register                                                               | 80                |

#### **Table of Contents**

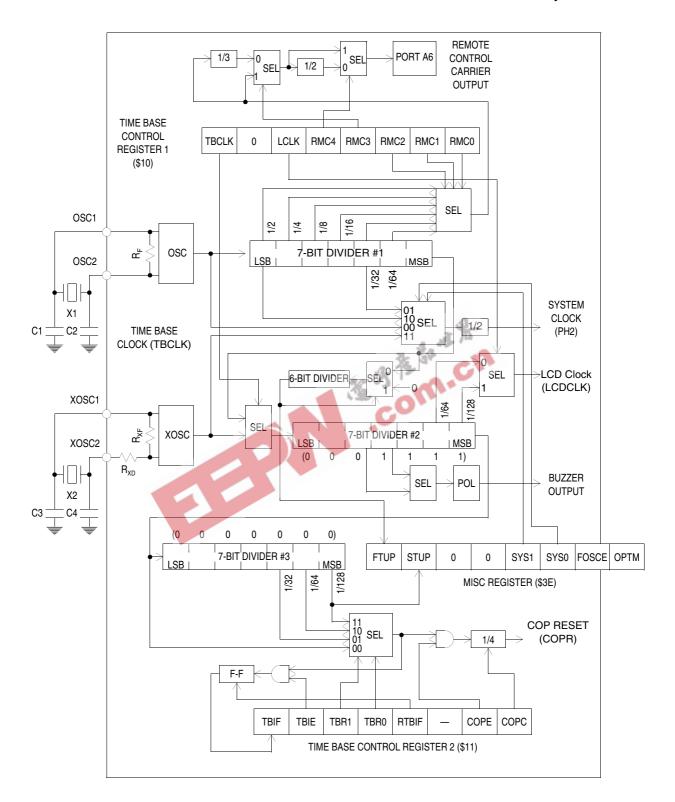

# Chapter 9 Time Base

| 9.1    | Introduction                           | 83 |

|--------|----------------------------------------|----|

| 9.2    | Time Base Submodules                   |    |

| 9.2.1  | LCDCLK                                 |    |

| 9.2.2  | STUP                                   |    |

| 9.2.3  | TBI                                    | 83 |

| 9.2.4  | COP                                    |    |

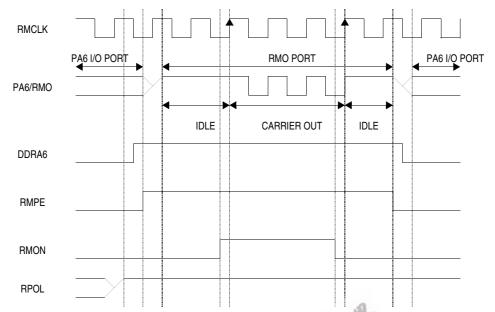

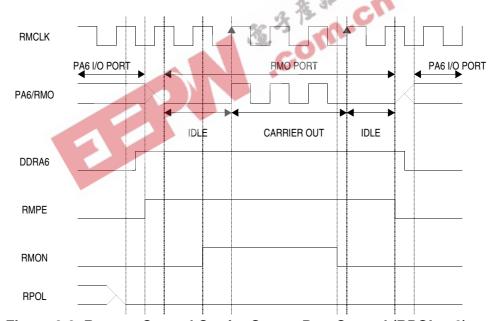

| 9.2.5  | Remote Control Carrier Generator       |    |

| 9.2.6  | Buzzer Tone Generator                  |    |

| 9.3    | Time Base Control Register 1           |    |

| 9.4    | Time Base Control Register 2           |    |

| 9.5    | Time Base Control Register 3           |    |

|        |                                        |    |

|        | Chapter 10 Serial Peripheral Interface |    |

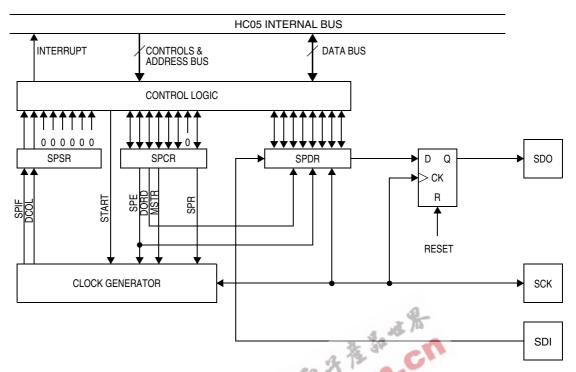

| 10.1   | Introduction                           | 91 |

| 10.2   | Features.  Block Diagram               | 91 |

| 10.3   | Block Diagram                          | 91 |

| 10.3.1 | Control                                | 91 |

| 10.3.2 | SPDR                                   | 91 |

| 10.3.3 | SPCR                                   | 91 |

| 10.3.4 | Clock Generator                        |    |

| 10.3.5 | Others                                 |    |

| 10.3.6 | Signal Description                     |    |

| 10.3.7 | Serial Data Out (SDO)                  |    |

| 10.3.8 | Serial Data In (SDI)                   |    |

| 10.3.9 | Serial Clock (SCK)                     |    |

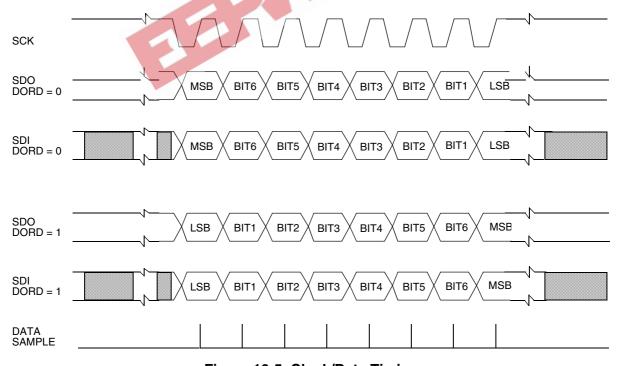

| 10.4   | Functional Description                 | 93 |

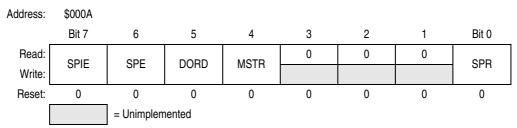

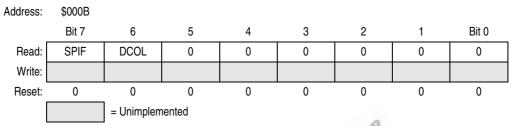

| 10.5   | Register Description                   | 94 |

| 10.5.1 | Serial Peripheral Control Register     |    |

| 10.5.2 | Serial Peripheral Status Register      |    |

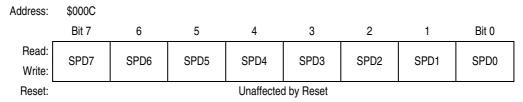

| 10.5.3 | SPI Data Register                      | 96 |

| 10.5.4 | Timing Diagram                         | 96 |

| 10.5.5 | Stop/Wait Condition                    |    |

| 10.5.6 | Stop Mode                              | 97 |

| 10.5.7 | Wait Mode                              | 97 |

|        | Chapter 11                             |    |

|        | LCD Driver                             |    |

| 11.1   | Introduction                           | 99 |

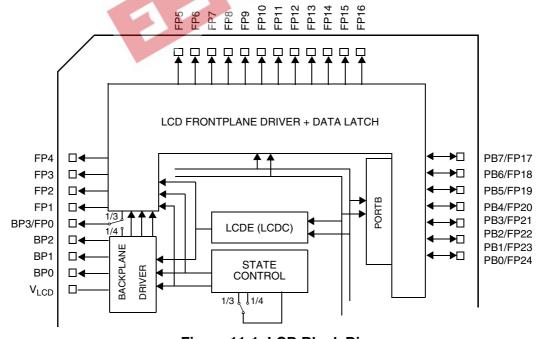

| 11.2   | Block Diagram                          |    |

| 11.3   | Functional Description                 | 00 |

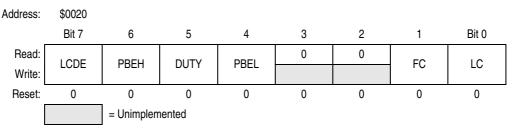

| 11.3.1 | LCD Control Register                   |    |

| 11.3.2 | Fast Change Option                     | 01 |

| 11.3.3 | LCD Data Registers                     | 01 |

MC68HC05L25 Data Sheet, Rev. 3.1

|        | Table of Conte                                        | ents |

|--------|-------------------------------------------------------|------|

| 11.4   | Terminal Description                                  | 102  |

| 11.4.1 | V <sub>I CD</sub> Bias Inputs                         |      |

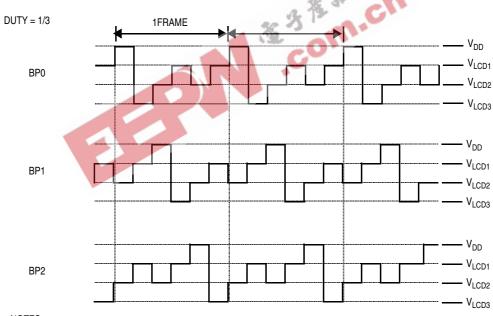

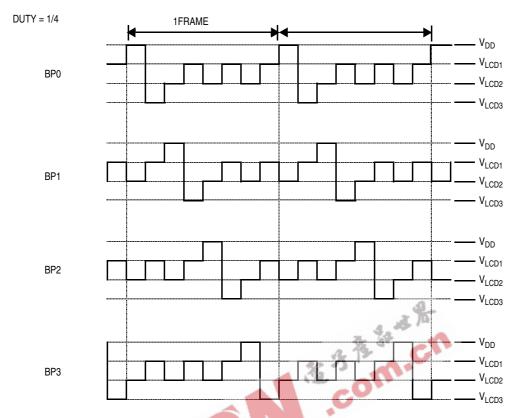

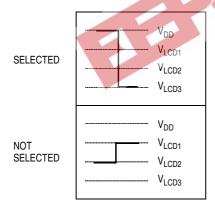

| 11.4.2 | Backplane Drivers (BP0–BP3)                           |      |

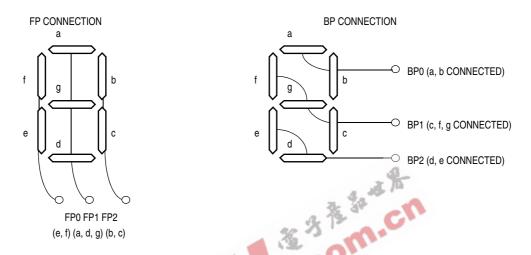

| 11.4.3 | Frontplane Drivers                                    | 103  |

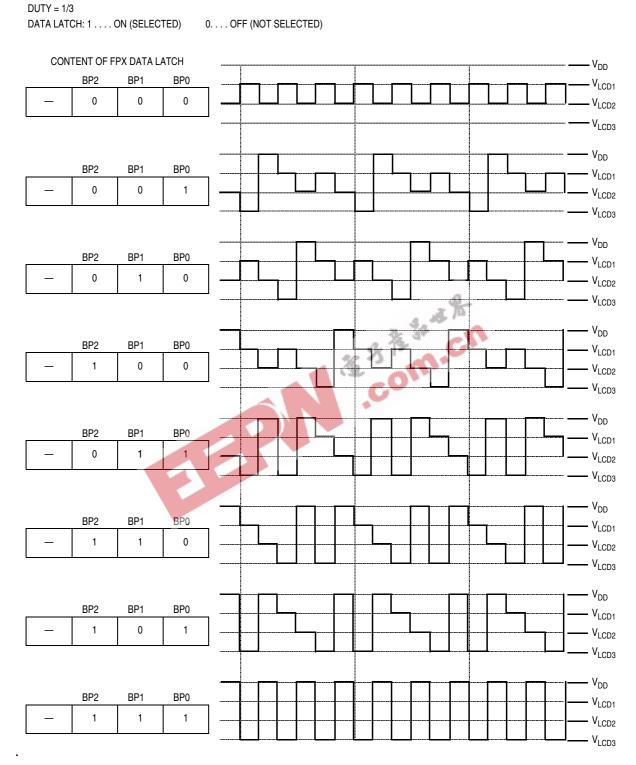

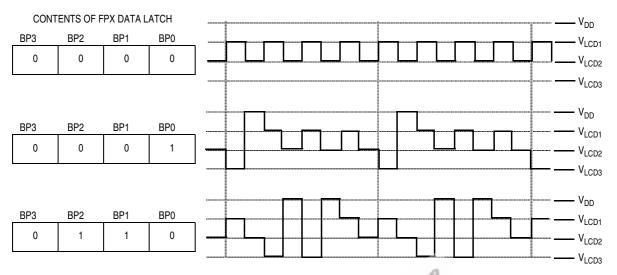

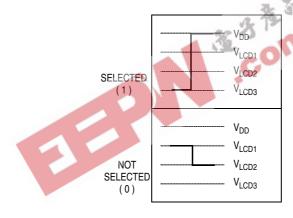

| 11.5   | LCD Connection and LCD Driver Operation               | 107  |

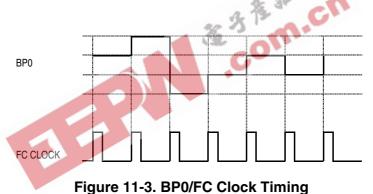

| 11.6   | LCD Waveform Base Clock and LCD Cycle Frame           | 110  |

| 11.6.1 | Time Base Control Register 1                          |      |

| 11.6.2 | LCD Cycle Frame                                       |      |

| 11.7   | Simplified LCD Schematic                              | 111  |

|        | Chapter 12                                            |      |

|        | Analog Subsystem                                      |      |

| 12.1   | Introduction                                          | 113  |

| 12.2   | Analog Section                                        | 113  |

| 12.3   | Ratiometric Conversion                                | 113  |

| 12.3.1 | V <sub>REFH</sub>                                     | 113  |

| 12.3.2 | Accuracy and Precision                                | 113  |

| 12.4   | Conversion Process  Digital Section  Conversion Times | 113  |

| 12.5   | Digital Section                                       | 113  |

| 12.5.1 | Conversion Times                                      | 114  |

| 12.5.2 | IIIIGIIIAI VOIGUG EXIGIIIAI OGUIIIAIUI                |      |

| 12.5.3 | Multi-Channel Operation                               | 114  |

| 12.6   | A/D Subsystem Operation during Wait Modes             |      |

| 12.7   | A/D Subsystem Operation during Stop Modes             |      |

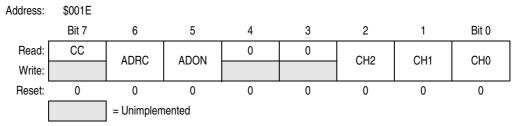

| 12.8   | A/D Status and Control Register                       |      |

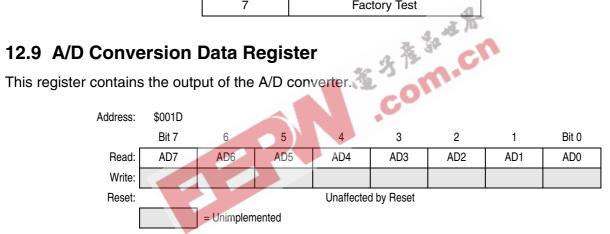

| 12.9   | A/D Conversion Data Register                          | 116  |

|        | Chapter 13                                            |      |

|        | Event Counter                                         |      |

| 13.1   | Features                                              |      |

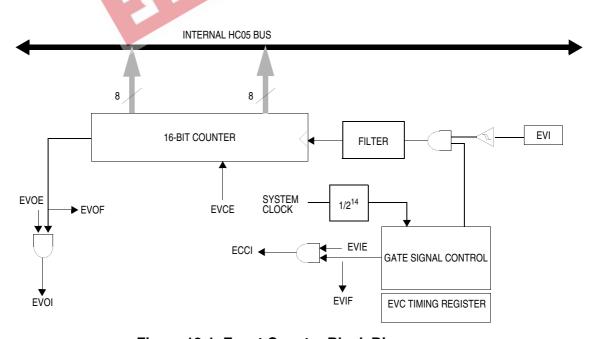

| 13.2   | Introduction                                          | 117  |

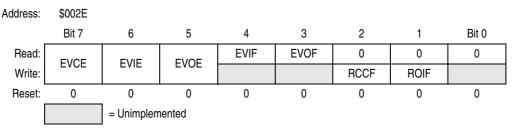

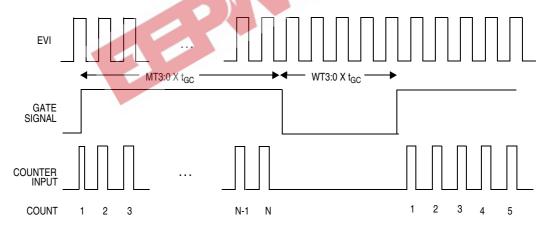

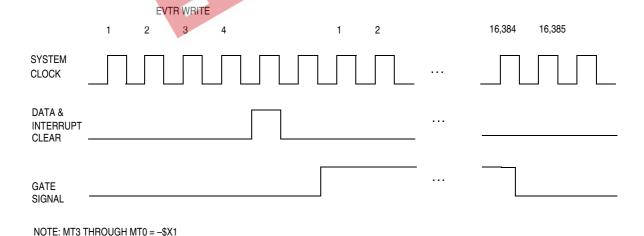

| 13.3   | Event Counter Status/Control Register                 | 118  |

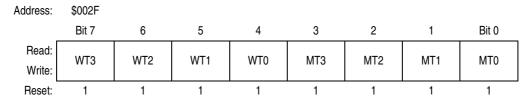

| 13.4   | Event Counter Timing Register                         | 119  |

| 13.5   | Event Counter Interrupts                              | 121  |

| 13.6   | Event Counter During Wait Mode                        | 121  |

| 13.7   | Event Counter During Stop Mode                        | 121  |

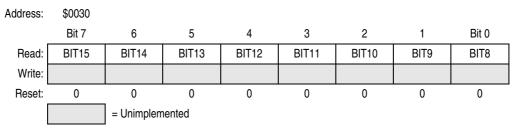

| 13.8   | Event Counter Data Registers                          | 122  |

|        | Chapter 14                                            |      |

|        | Instruction Set                                       |      |

| 14.1   | Introduction                                          |      |

| 14.2   | Addressing Modes                                      |      |

| 14.2.1 | Inherent                                              |      |

| 14.2.2 | Immediate                                             |      |

| 14.2.3 | Direct                                                | 123  |

| Table of                                                                                        | f Contents                           |                            |

|-------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------|

| 14.2.4<br>14.2.5<br>14.2.6                                                                      | Extended                             | 24                         |

| 14.2.7<br>14.2.8<br>14.3                                                                        |                                      | 24                         |

| 14.3.1<br>14.3.2<br>14.3.3                                                                      | Register/Memory Instructions         | 25<br>26                   |

| 14.3.4<br>14.3.5<br>14.4                                                                        | ·                                    | 28<br>28                   |

| 14.5                                                                                            | Opcode Map                           |                            |

|                                                                                                 | Chapter 15 Electrical Specifications |                            |

| 15.1<br>15.2<br>15.3<br>15.4<br>15.5<br>15.6<br>15.7<br>15.8<br>15.9<br>15.10<br>15.11<br>15.12 | Introduction                         | 40<br>41<br>41<br>42<br>43 |

|                                                                                                 | Mechanical Specifications            |                            |

|                                                                                                 | Chapter 17 Ordering Information      |                            |

| 17.1<br>17.2<br>17.3<br>17.4<br>17.5<br>17.6                                                    | Introduction                         | 47<br>47<br>48<br>48       |

# **Chapter 1 General Description**

#### 1.1 Introduction

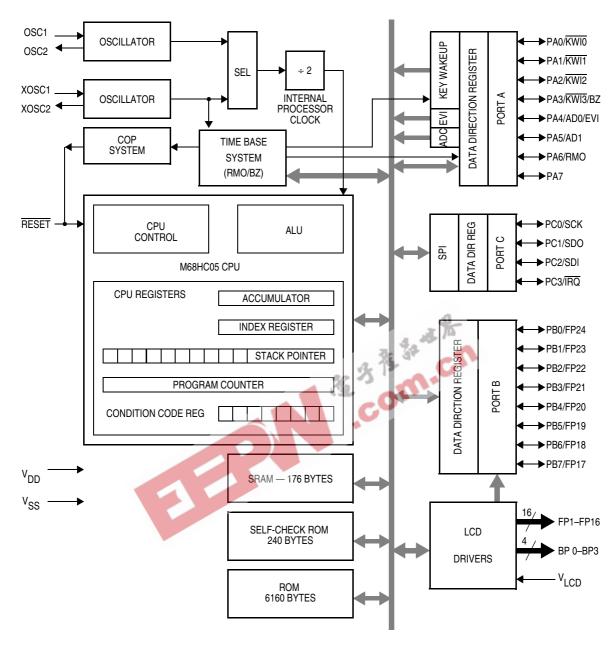

The MC68HC05L25 is a member of M68HC05 Family of low-cost microcontroller units (MCUs). A functional block diagram of the MC68HC05L25 is shown in Figure 1-1.

#### 1.2 Features

- Low-Cost. HC05 Core

- 48-Pin Quad Flat Pack (VQFP) and 52-Pin Quad Flat Pack (TQFP)

- 6160 Bytes of User ROM, Including 16 Bytes of User Vectors

- 176 Bytes of User RAM

- 24 x 4 or 25 x 3 Multiplexed Liquid Crystal Display (LCD) Drive

- Serial Peripheral Interface (SPI)

- Two-Channel Analog-to-Digital (A/D) Converter

- 16-Bit Event Counter

- **Time Base Timer**

- Computer Operating Properly (COP) Watchdog Timer

- Infrared (IR) Remote Carrier Output (Software Selectable 33-to-67 Percent or 50-to-50 Percent Duty)

- Buzzer Output (Software-Selectable Frequencies)

- 20 Bidirectional Input/Output (I/O) Lines, Including:

- Four Key Wakeup Input Lines

- Software-Programmable Pullups

- Software-Programmable Open-Drain Lines

- High-Current (20 mA) Lines

- Software-Selectable Sensitivity on IRQ Interrupt (Edge- and Level-Sensitive or Edge-Sensitive Only)

- STOP Instruction Disable Option

- On-Chip Dual 4-MHz/32-kHz (Typical) Oscillator Circuits

- Single-Chip, Self-Check, and Test Modes

- Power-Saving Stop and Wait Modes

#### **General Description**

# 1.3 Mask Options

Table 1-1 shows the mask programmable options available on the MC68HC05L25.

**Table 1-1. Mask Option Selection**

| Name                                                                                                                    | Selection | Description                                                       |  |

|-------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------|--|

|                                                                                                                         |           | RESET pin pullup resistor                                         |  |

| RSTR RE RESET pullup resistor enable (connected)                                                                        |           | RESET pullup resistor enable (connected)                          |  |

|                                                                                                                         | RD        | RESET pullup resistor disable (not connected)                     |  |

| OSC feedback resistor OSCR OE OSC feedback resistor enable (connected) OD OSC feedback resistor disable (not connected) |           | OSC feedback resistor                                             |  |

|                                                                                                                         |           | OSC feedback resistor enable (connected)                          |  |

|                                                                                                                         |           | OSC feedback resistor disable (not connected)                     |  |

| XOSC feedback/ damping resistor                                                                                         |           | XOSC feedback/ damping resistor                                   |  |

| XOSCR                                                                                                                   | XE        | XOSC feedback and damping resistor enable (both connected)        |  |

|                                                                                                                         | XD        | XOSC feedback and damping resistor disable (both not connected)   |  |

|                                                                                                                         |           | STOP instruction                                                  |  |

| STOPE                                                                                                                   | SE        | STOP instruction enable (STOP instruction operates normally)      |  |

|                                                                                                                         | SD        | STOP instruction disable (executing STOP will not halt OSC clock) |  |

## 1.4 MCU Structure

The overall block diagram of the MC68HC05L25 is shown in Figure 1-1.

Figure 1-1. MC68HC05L25 Block Diagram

**General Description**

# 1.5 Functional Pin Description

#### NOTE

A line over a signal name <u>indicates</u> an active low signal. For example, RESET is active high and RESET is active low. Any reference to voltage, current, resistance, capacitance, time, or frequency specified in the following paragraphs will refer to the nominal values. The exact values and their tolerance or limits are specified in <u>Chapter 15 Electrical Specifications</u>.

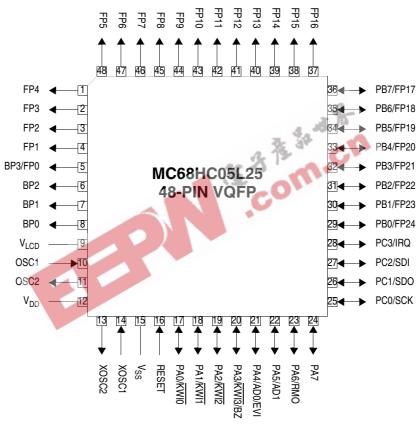

The MC68HC05L25 is available in the 48-pin VQFP and 52-pin TQFP. The pin assignments for the 48-pin VQFP are shown in Figure 1-2 and Table 1-2.

Figure 1-2. 48-Pin VQFP Single-Chip Mode Pinout

16 Freescale Semiconductor

MC68HC05L25 Data Sheet, Rev. 3.1

Table 1-2 summarizes the 48-pin VQFP pin configurations.

Table 1-2. 48-Pin VQFP Pin Configurations

| Pin No. | Pin Name        | I/O |

|---------|-----------------|-----|

| 10      | OSC1            | I   |

| 11      | OSC2            | 0   |

| 12      | V <sub>DD</sub> | DC  |

| 13      | XOSC2           | 0   |

| 14      | XOSC1           | I   |

| 15      | $V_{SS}$        | DC  |

| 16      | RESET           | I   |

| 17      | PA0/KWI0        | I/O |

| 18      | PA1/KWI1        | I/O |

| 19      | PA2/KWI2        | I/O |

| 20      | PA3/KWI3/BZ     | I/O |

| 21      | PA4/AD0/EVI     | I/O |

| 22      | PA5/AD1         | I/O |

| 23      | PA6/RMO         | 1/0 |

| 24      | PA7             | 1/0 |

| 25      | PC0/SCK         | I/O |

| 26      | PC1/SDO         | 1/0 |

| 27      | PC2/SDI         | I/O |

| 28      | PC3/IRQ         | 1/0 |

| Pin No. | Pin Name         | I/O |

|---------|------------------|-----|

| 29      | PB0/FP24         | I/O |

| 30      | PB1/FP23         | I/O |

| 31      | PB2/FP22         | I/O |

| 32      | PB3/FP21         | I/O |

| 33      | PB4/FP20         | I/O |

| 34      | PB5/FP19         | I/O |

| 35      | PB6/FP18         | I/O |

| 36      | PB7/FP17         | I/O |

| 37      | FP16             | 0   |

| 38      | FP15             | 0   |

| 39      | FP14             | 0   |

| 40      | FP13             | 0   |

| 41      | FP12             | 0   |

| 42      | FP11             | 0   |

| 43      | FP10             | 0   |

| 44      | FP9              | 0   |

| 45      | FP8              | 0   |

| 46      | FP7              | 0   |

| 47      | FP6              | 0   |

| 48      | FP5              | 0   |

| 1       | FP4              | 0   |

| 2       | FP3              | 0   |

| 3       | FP2              | 0   |

| 4       | FP1              | 0   |

| 5       | BP3/FP0          | 0   |

| 6       | BP2              | 0   |

| 7       | BP1              | 0   |

| 8       | BP0              | 0   |

| 9       | V <sub>LCD</sub> | DC  |

#### **General Description**

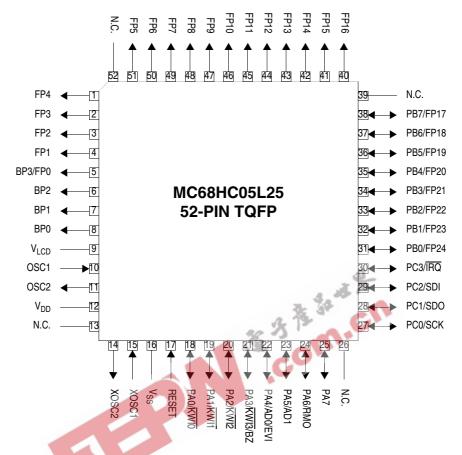

The pin assignments for the 52-pin TQFP are shown in Figure 1-3 and Table 1-3.

Figure 1-3. 52-Pin TQFP Single-Chip Mode Pinout

Table 1-3 summarizes the 52-pin VQFP pin configurations.

**Table 1-3. 52-Pin TQFT Pin Configurations**

| Pin No. | Pin Name        | I/O |

|---------|-----------------|-----|

| 10      | OSC1            | - 1 |

| 11      | OSC2            | 0   |

| 12      | $V_{DD}$        | DC  |

| 14      | XOSC2           | 0   |

| 15      | XOSC1           | I   |

| 16      | V <sub>SS</sub> | DC  |

| 17      | RESET           | I   |

| 18      | PA0/KWI0        | I/O |

| 19      | PA1/KWI1        | I/O |

| 20      | PA2/KWI2        | I/O |

| 21      | PA3/KWI3/BZ     | I/O |

| 22      | PA4/AD0/EVI     | I/O |

| 23      | PA5/AD1         | I/O |

| 24      | PA6/RMO         | I/O |

| 25      | PA7             | 1/0 |

| 27      | PC0/SCK         | I/O |

| 28      | PC1/SDO         | I/O |

| 29      | PC2/SDI         | I/O |

| 30      | PC3/IRQ         | I/O |

| Pin No. | Pin Name         | I/O |  |  |  |  |

|---------|------------------|-----|--|--|--|--|

| 31      | PB0/FP24         | I/O |  |  |  |  |

| 32      | PB1/FP23         | I/O |  |  |  |  |

| 33      | PB2/FP22         | I/O |  |  |  |  |

| 34      | PB3/FP21         | I/O |  |  |  |  |

| 35      | PB4/FP20         | I/O |  |  |  |  |

| 36      | PB5/FP19         | I/O |  |  |  |  |

| 37      | PB6/FP18         | I/O |  |  |  |  |

| 38      | PB7/FP17         | I/O |  |  |  |  |

| 40      | FP16             | 0   |  |  |  |  |

| 41      | FP15             | 0   |  |  |  |  |

| 42      | FP14             | 0   |  |  |  |  |

| 43      | FP13             | 0   |  |  |  |  |

| 44      | FP12             | 0   |  |  |  |  |

| 45      | FP11             | 0   |  |  |  |  |

| 46      | FP10             | 0   |  |  |  |  |

| 47      | FP9              | 0   |  |  |  |  |

| 48      | FP8              | 0   |  |  |  |  |

| 49      | FP7              | 0   |  |  |  |  |

| 50      | FP6              | 0   |  |  |  |  |

| 51      | FP5              | 0   |  |  |  |  |

| 1       | FP4              | 0   |  |  |  |  |

| 2       | FP3              | 0   |  |  |  |  |

| 3       | FP2              | 0   |  |  |  |  |

| 4       | FP1              | 0   |  |  |  |  |

| 5       | BP3/FP0          | 0   |  |  |  |  |

| 6       | BP2              | 0   |  |  |  |  |

| 7       | BP1              | 0   |  |  |  |  |

| 8       | BP0              | 0   |  |  |  |  |

| 9       | V <sub>LCD</sub> | DC  |  |  |  |  |

|         |                  |     |  |  |  |  |

| 13 | N.C. |

|----|------|

| 26 | N.C. |

| 39 | N.C. |

| 52 | N.C. |

The following paragraphs describe the general function of each pin.

#### **General Description**

### 1.5.1 $V_{DD}$ and $V_{SS}$

Power is supplied to the MCU through  $V_{DD}$  and  $V_{SS}$ .  $V_{DD}$  is the positive supply, and  $V_{SS}$  is ground. The MCU operates from a single power supply.

Very fast signal transitions occur on the MCU pins. The short rise and fall times place very high short-duration current demands on the power supply. To prevent noise problems, special care should be taken to provide good power supply bypassing at the MCU by using bypass capacitors with good high-frequency characteristics that are positioned as close to the MCU as possible. Bypassing requirements vary, depending on how heavily the MCU pins are loaded.

#### 1.5.2 V<sub>I CD</sub>

This pin provides an offset to the LCD driver bias for adjusting the contrast of LCD. See Chapter 11 LCD Driver for additional information.

#### 1.5.3 **RESET**

This pin can be used as an input to reset the MCU to a known startup state by pulling it to the low state. The RESET pin contains a steering diode to discharge any voltage on the pin to V<sub>DD</sub> when the power is removed. The RESET pin contains an internal Schmitt trigger to improve its noise immunity as an input. Refer to Chapter 5 Resets.

#### 1.5.4 OSC1 and OSC2

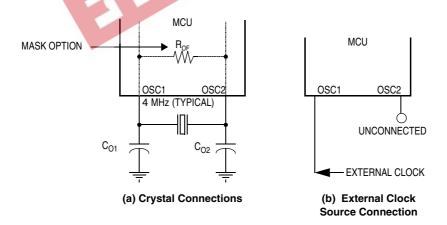

The OSC1 and OSC2 pins are the connections for the 2-pin on-chip oscillator. The OSC1 and OSC2 pins can accept these sets of components:

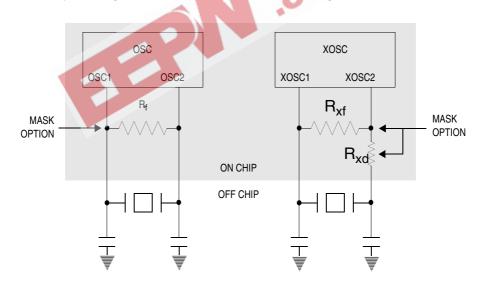

- 1. A crystal or ceramic resonator as shown in Figure 1-4(a)

- 2. An external clock signal as shown in Figure 1-4(b)

Figure 1-4. Oscillator Connections

The frequency,  $f_{OSC}$ , of the oscillator or external clock source is divided by two to produce the internal operating frequency,  $f_{OP}$ , by default.

21

#### 1.5.4.1 Crystal or Ceramic Resonator

The circuit in Figure 1-4(a) shows a typical 2-pin oscillator circuit for an AT-cut, parallel, resonant crystal. The crystal manufacturer's recommendations should be followed, since the crystal parameters determine the external component values required to provide maximum stability and reliable startup. The load capacitance values used in the oscillator circuit design should include all stray capacitances. The crystal and components should be mounted as close as possible to the pins for startup stabilization and to minimize output distortion. An internal startup feedback resistor of  $R_{\text{OF}}$  between OSC1 and OSC2 can be selected as a mask option.

#### 1.5.4.2 External Clock

An external clock from another CMOS-compatible device can be connected to the OSC1 input, with the OSC2 output not connected, as shown in Figure 1-4(b). This configuration is possible regardless of the oscillator setup.

#### 1.5.5 XOSC1 and XOSC2

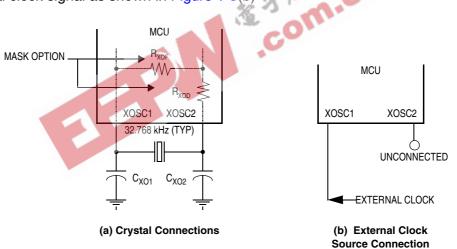

The XOSC1 and XOSC2 pins are the connections for the 2-pin on-chip oscillator. The XOSC1 and XOSC2 pins can accept these sets of components:

- 1. A crystal as shown in Figure 1-5(a)

- 2. An external clock signal as shown in Figure 1-5(b)

Figure 1-5. Oscillator Connections

The frequency,  $f_{XOSC}$ , of the oscillator or external clock source is divided by two to produce the internal operating frequency,  $f_{OP}$ , if selected by SYS1:SYS0 bits.

#### 1.5.5.1 Crystal

The circuit in Figure 1-5(a) shows a typical 2-pin oscillator circuit for a 32.768-kHz "watch" crystal. The crystal manufacturer's recommendations should be followed, since the crystal parameters determine the external component values required to provide maximum stability and reliable startup. The load capacitance values used in the oscillator circuit design should include all stray capacitances. The crystal and components should be mounted as close as possible to the pins for start-up stabilization and to

#### **General Description**

minimize output distortion. An internal startup feedback resistor of  $R_{xof}$  between XOSC1 and XOSC2 and a damping resistor of  $R_{xod}$  in series to XOSC2 can be selected as a mask option.

#### 1.5.5.2 External Clock

As shown in Figure 1-5(b), an external clock from another CMOS-compatible device can be connected to the XOSC1 input (with the XOSC2 output not connected). This configuration is possible regardless of the oscillator setup.

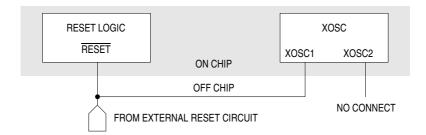

#### 1.5.5.3 XOSC Not Used

When XOSC is not used, the XOSC1 pin must be connected to the RESET pin to assure proper initialization of the clock circuitry. XOSC2 pin should remain unconnected.

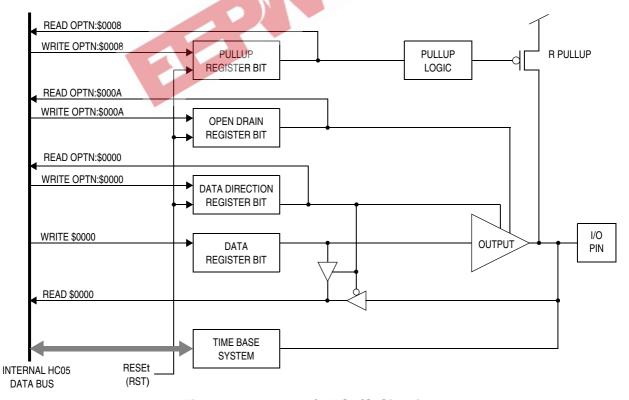

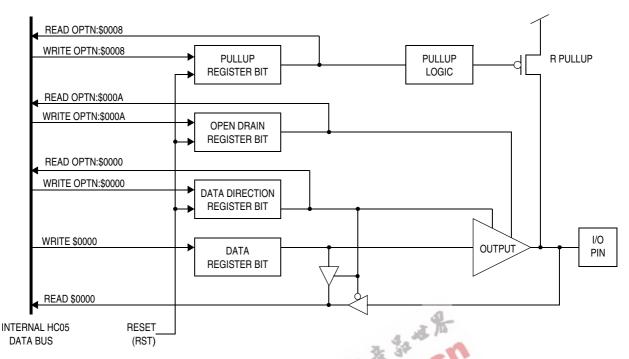

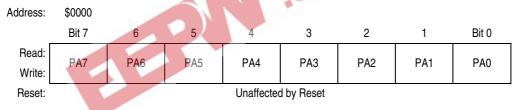

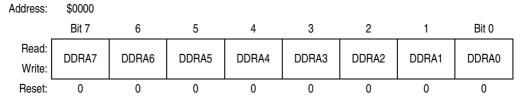

#### 1.5.6 PA0-PA2/KWI0-KWI2, PA3/KWI3/BZ, PA4/AD0/EVI, PA5/ADI, PA6/RMO, and PA7

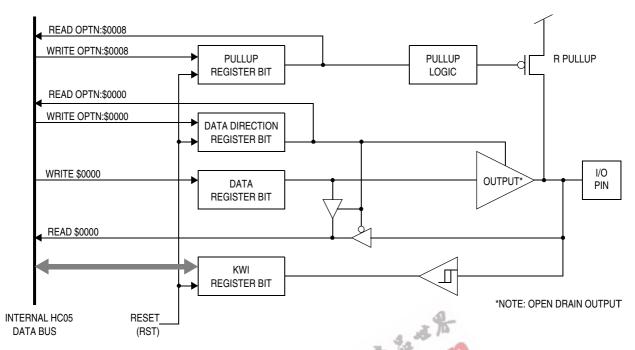

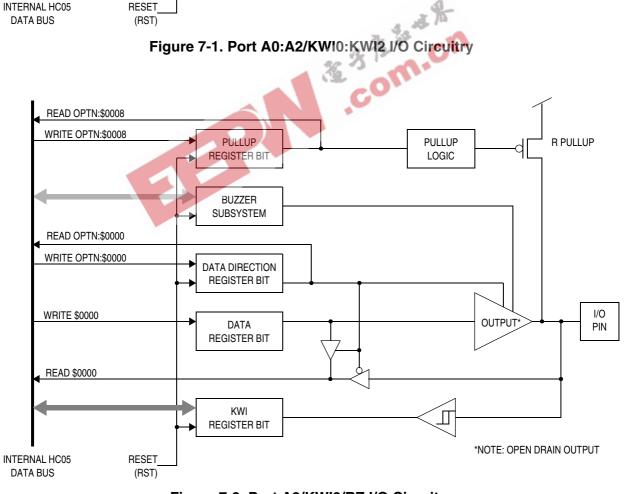

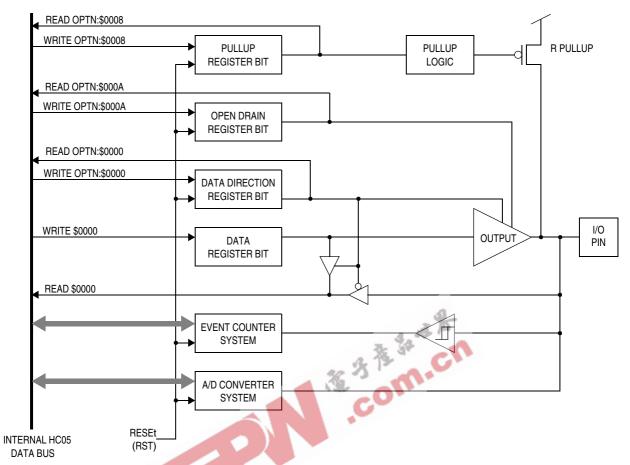

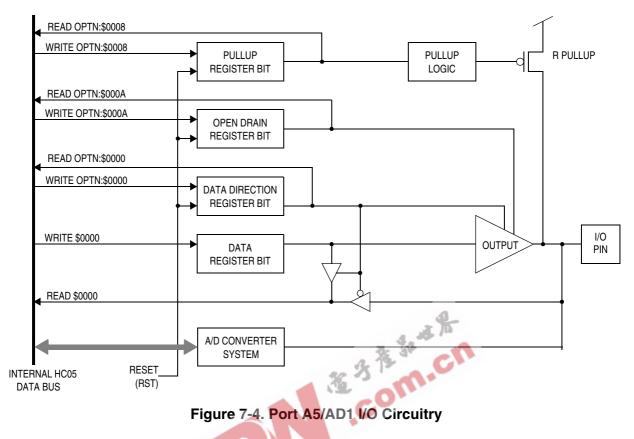

Port A is an 8-bit I/O port. The state of any pin is software programmable and all port A lines are configured as inputs during power-on or reset. Bits 0 through 3 are shared with the key wakeup subsystem, and bit 3 also is shared with the buzzer subsystem. Bit 4 is shared with the A/D converter and event counter. Bit 5 is shared with the A/D converter. Bit 6 is shared with the infrared (IR) remote output. See Chapter 7 Input/Output Ports (I/O) for more details on the I/O ports.

#### 1.5.7 PB0-PB7/FP24-FP17

These eight I/O lines comprise port B. The state of any pin is software programmable, and all bits are configured as LCD output during power-on or reset. These bits are shared with LCD frontplane drivers. See Chapter 7 Input/Output Ports (I/O) for more details on the I/O ports.

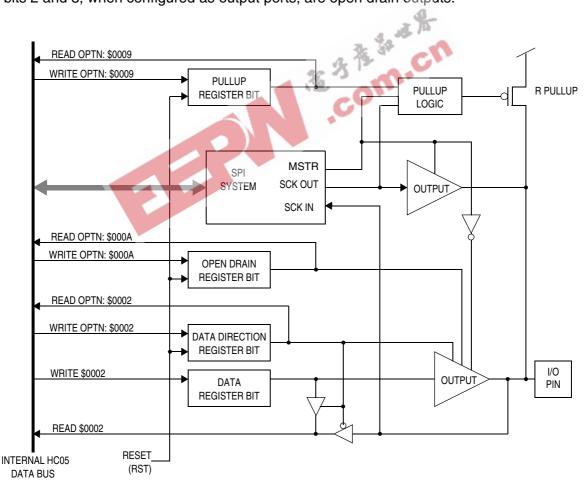

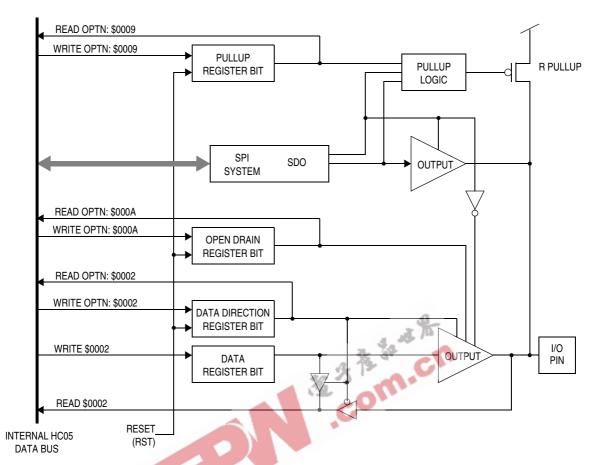

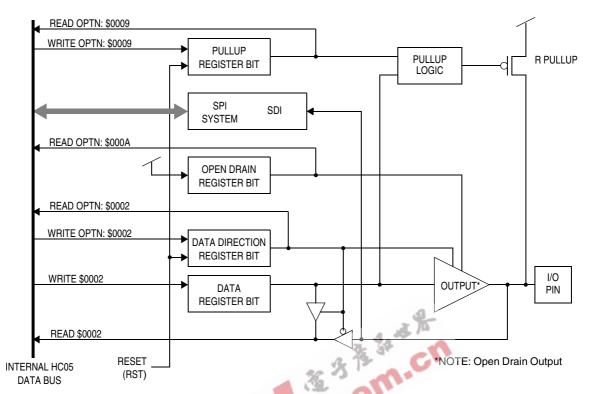

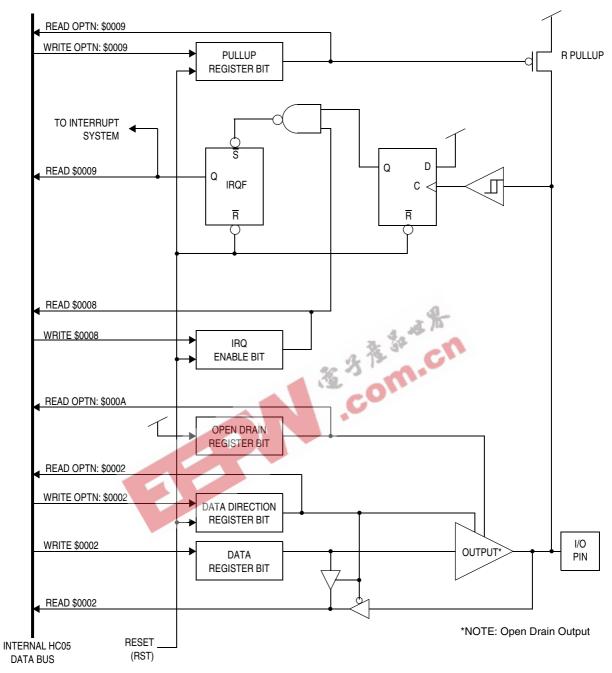

#### 1.5.8 PC0/SCK, PC1/SDO, PC2/SDI, and PC3/IRQ

These four I/O lines comprise port C. Bits 0 through 2 are shared with the SPI subsystem. Bit 3 is shared with the  $\overline{IRQ}$  input. The state of any pin is software programmable, and all port C lines are configured as port inputs during power-on or reset. Each port C pin can be configured with a pullup resistor by a software option. SPI output pins SCK and SDO can be configured as open-drain outputs by a software option. See Chapter 7 Input/Output Ports (I/O) for more details on the I/O ports. The PC3/ $\overline{IRQ}$  pin is used for special mode entry. Do not apply voltages above  $V_{DD}$  for normal single-chip mode operation. See Chapter 15 Electrical Specifications for more details.

#### 1.5.9 BP3/FP0, FP1-FP18, and PB0-PB7/FP24-FP17

The LCD display has 25 frontplane drivers. Frontplanes 17 through 24 are shared with port B bits 7 through 0, respectively. Frontplane 0 is shared with backplane 3. See Chapter 11 LCD Driver for additional information.

#### 1.5.10 BP0-BP2 and BP3/FP0

The LCD display has four backplane drivers. Backplane 3 is multiplexed with frontplane 0. See Chapter 11 LCD Driver for additional information.

# **Chapter 2 Memory Map**

#### 2.1 Introduction

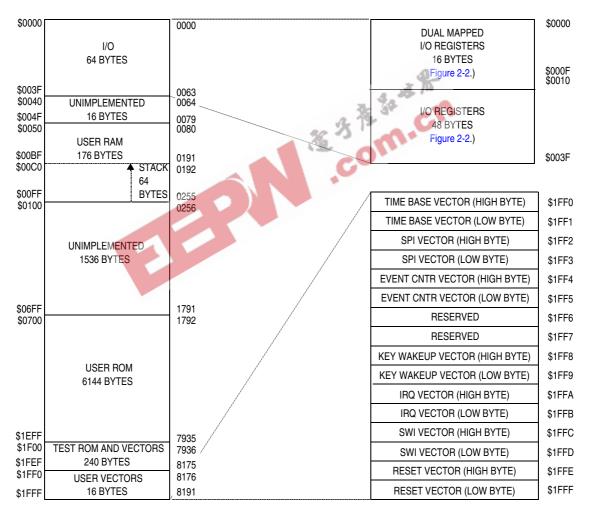

When the MC68HC05L25 is in the single-chip mode, 80 bytes of input/output (I/O) registers, 176 bytes of user RAM (including a 64-byte stack), 6144 bytes of user ROM, and 16 bytes of user vectors are available in the 8-K memory map as shown in Figure 2-1.

Figure 2-1. MC68HC05L25 Single-Chip Mode Memory Map

**Memory Map**

## 2.2 Input/Output and Control Registers

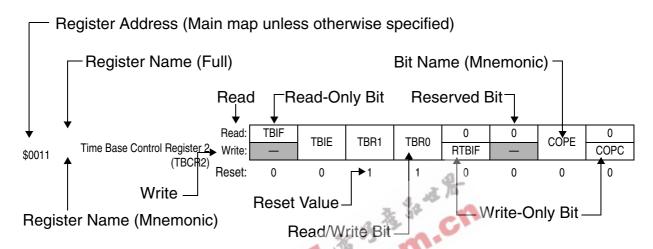

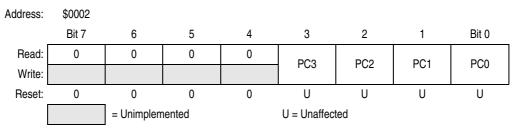

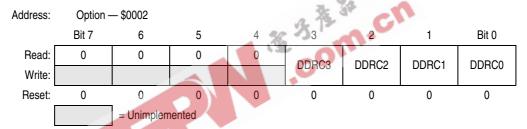

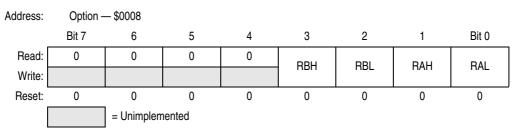

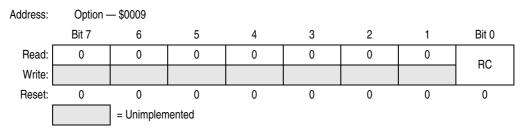

The I/O and control registers reside in locations \$0000 through \$003F. A summary of these registers is shown in Figure 2-3. The bit assignments for each register are shown in Figure 2-4. Reading from unimplemented bits (denoted with —) will return unknown states (unless explicitly defined to read 0), and writing to unimplemented bits will have no effect. See also Figure 2-2.

Figure 2-2. Register Description Key

#### 2.2.1 Read/Write Bits

Read/write bits are typically control bits. They are, in general, not modified by a module. Reset: indicates the initial value of the latch.

#### 2.2.2 Read-Only Bits

Read-only bits are status flag bits. They are indicators of module status. Reset: indicates the value that will be read immediately after system reset or before the module is enabled.

#### 2.2.3 Write-Only Bits

Write-only bits are control bits. They typically return a state of 0 to prevent an inadvertent write to this bit by a READ-MODIFY-WRITE instruction. Reset: indicates the value that will be read immediately after system reset, which is the forced read value (typically 0).

#### 2.2.4 Reserved Bits

Reserved bits are read-only bits that typically read 0. Writes to these bits are ignored, and the user should not write 1 for future compatibility. Reset: indicates the value that will be read immediately after system reset which is the forced read value of 0, typically.

25

#### 2.2.5 Reset Value

Values specified on the row marked Reset: are initial values of register bits after system reset. Those bits unaffected by reset are marked with the letter U. Those bits that are unaffected by reset but initialized by power-on reset are marked with an asterisk (\*).

#### 2.2.6 Option Map

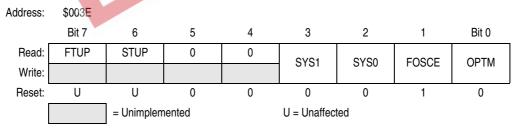

Address locations \$0000 through \$000F are dual mapped. When the OPTM bit in the MISC register is cleared, the main address map is accessed. When the OPTM bit in the MISC register is set, the option address map is accessed.

#### NOTE

Although not necessary for this device, the OPTM bit should be cleared when accessing memory locations \$0010 and above for future compatibility.

#### 2.2.7 Random-Access Memory (RAM)

The user RAM consists of 176 bytes (including the stack) at locations \$0050 through \$00FF. The stack can access 64 locations beginning at address \$00FF and proceeding down to \$00CO.

#### NOTE

Using the stack area for data storage or temporary work locations requires care to prevent it from being overwritten due to stacking from an interrupt or subroutine call.

# 2.3 Read-Only Memory (ROM)

This chip has a total of 6160 bytes of ROM. These are implemented as 6144 bytes of user ROM at locations \$0700 through \$1EFF and 16 bytes of user vectors at locations \$1FF0 through \$1FFF. A total of 240 bytes of test ROM and vectors is located from \$1F00 through \$1FEF.

#### **Memory Map**

| Address | Name (Main Map Registers)          |

|---------|------------------------------------|

| \$0000  | Port A Data Register               |

| \$0001  | Port B Data Register               |

| \$0002  | Port C Data Register               |

| \$0003  | Unimplemented                      |

| \$0004  | Unimplemented                      |

| \$0005  | Unimplemented                      |

| \$0006  | Unimplemented                      |

| \$0007  | Unimplemented                      |

| \$0008  | Interrupt Control Register         |

| \$0009  | Interrupt Status Register          |

| \$000A  | Serial Peripheral Control Register |

| \$000B  | Serial Peripheral Status Register  |

| \$000C  | Serial Peripheral Data Register    |

| \$000D  | Unimplemented                      |

| \$000E  | Unimplemented                      |

| \$000F  | Unimplemented                      |

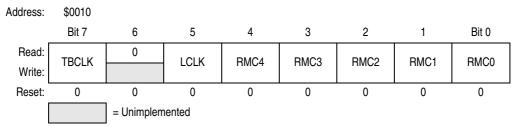

| \$0010  | Time Base Control Register 1       |

| \$0011  | Time Base Control Register 2       |

| \$0012  | Unimplemented                      |

| \$0013  | Unimplemented                      |

| \$0014  | Unimplemented                      |

| \$0015  | Unimplemented                      |

| \$0016  | Unimplemented                      |

| \$0017  | Unimplemented                      |

| \$0018  | Unimplemented                      |

| \$0019  | Unimplemented                      |

| \$001A  | Unimplemented                      |

| \$001B  | Unimplemented                      |

| \$001C  | Unimplemented                      |

| \$001D  | A/D Data Register                  |

| \$001E  | A/D Control/Status Register        |

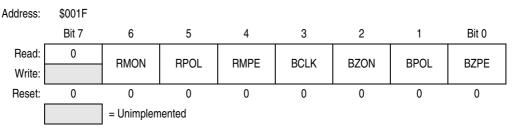

| \$001F  | Time Base Control Register 3       |

| \$0020  | LCD Control Register               |

| \$0021  | LCD Data Register 1                |

| \$0022  | LCD Data Register 2                |

| \$0023  | LCD Data Register 3                |

| \$0024  | LCD Data Register 4                |

| \$0025  | LCD Data Register 5                |

| \$0026  | LCD Data Register 6                |

| \$0027  | LCD Data Register 7                |

| Address | Name                                  |

|---------|---------------------------------------|

| \$0028  | LCD Data Register 8                   |

| \$0029  | LCD Data Register 9                   |

| \$002A  | LCD Data Register 10                  |

| \$002B  | LCD Data Register 11                  |

| \$002C  | LCD Data Register 12                  |

| \$002D  | LCD Data Register 13                  |

| \$002E  | Event Counter Control/Status Register |

| \$002F  | Event Counter Timing Register         |

| \$0030  | Event Counter Data High Register      |

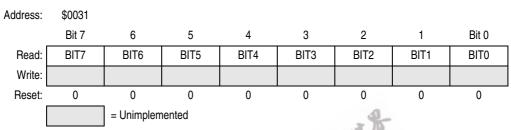

| \$0031  | Event Counter Data Low Register       |

| \$0032  | Unimplemented                         |

| \$0033  | Unimplemented                         |

| \$0034  | Unimplemented                         |

| \$0035  | Unimplemented                         |

| \$0036  | Unimplemented                         |

| \$0037  | Unimplemented                         |

| \$0038  | Unimplemented                         |

| \$0039  | Unimple <b>men</b> ted                |

| \$003A  | Unimplemented                         |

| \$003B  | Unimplemented                         |

| \$003C  | Unimplemented                         |

| \$003D  | Unimplemented                         |

| \$003E  | Miscellaneous Register                |

| \$003F  | Unimplemented                         |

| OPTN    | Name                             |

|---------|----------------------------------|

| Address | (Option Map Registers)           |

| \$0000  | Port A Data Direction Register   |

| \$0001  | Port B Data Direction Register   |

| \$0002  | Port C Data Direction Register   |

| \$0003  | Unimplemented                    |

| \$0004  | Unimplemented                    |

| \$0005  | Unimplemented                    |

| \$0006  | Unimplemented                    |

| \$0007  | Unimplemented                    |

| \$0008  | Resistor Control Register        |

| \$0009  | Resistor Control Register        |

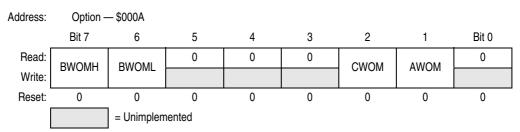

| \$000A  | Wired-OR Mode Register           |

| \$000B  | Unimplemented                    |

| \$000C  | Unimplemented                    |

| \$000D  | Unimplemented                    |

| \$000E  | Key Wakeup Input Enable Register |

| \$000F  | Mask Option Status Register      |

Figure 2-3. I/O Register Memory Map Summary

#### Read-Only Memory (ROM)

Figure 2-4. I/O Registers (Sheet 1 of 3)

#### **Memory Map**

| Addr.  | Register Name                 |                 | Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6                   | 5      | 4         | 3          | 2        | 1         | Bit 0 |  |

|--------|-------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------|-----------|------------|----------|-----------|-------|--|

| \$0021 | LCD Data Register<br>(LDAT1)  | Read:<br>Write: | F1B3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | F1B2                | F1B1   | F1B0      | F0B3       | F0B2     | F0B1      | F0B0  |  |

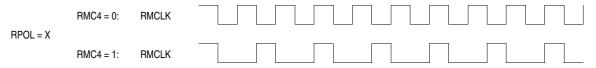

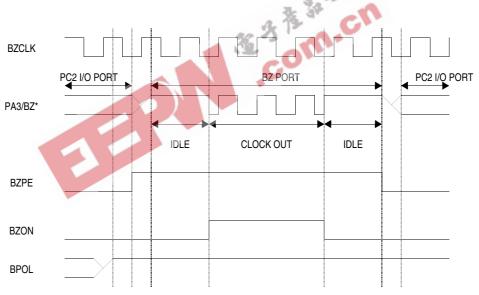

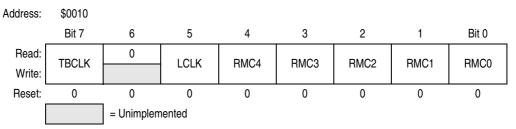

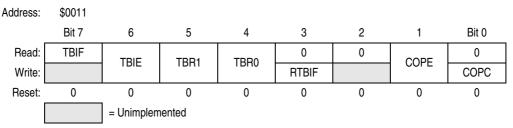

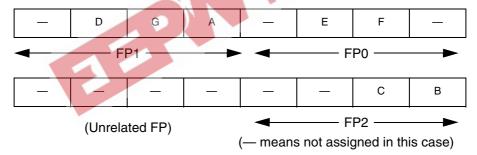

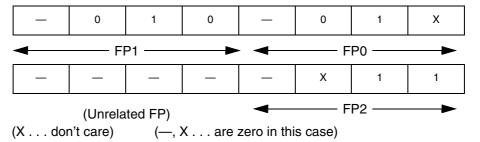

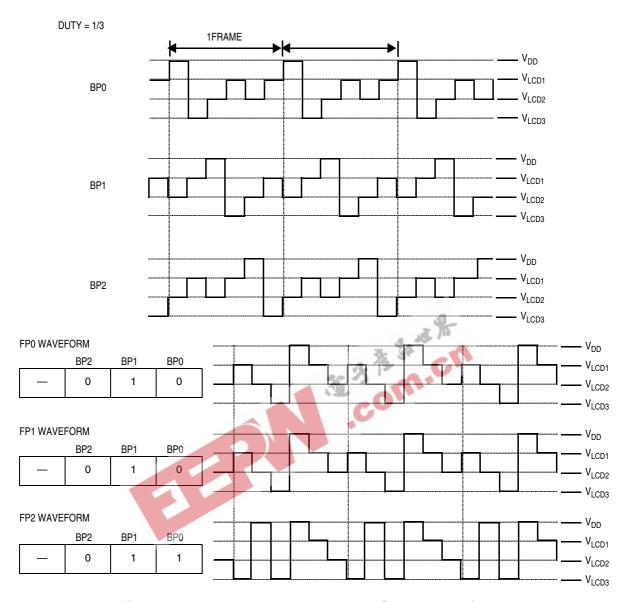

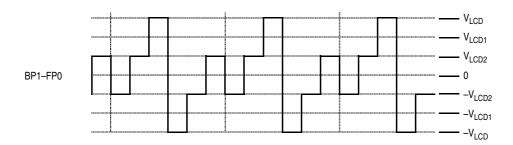

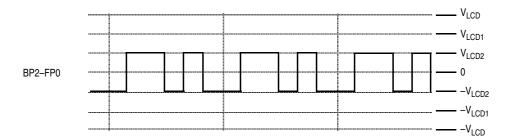

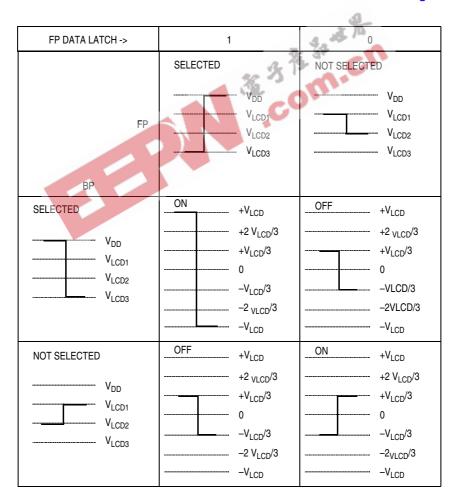

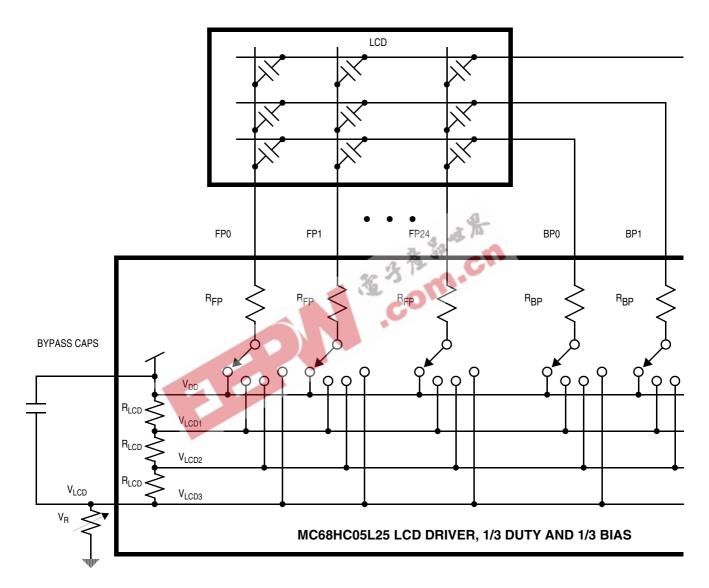

|        | See page 102.                 | Reset:          | Unaffected by reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     |        |           |            |          |           |       |  |