Addendum

HC908JB8AD/D Rev. 0, 4/2002

Addendum to MC68HC908JB8 Technical Data

This addendum provides additional information to the *MC68HC908JB8 Technical Data*, Rev. 2 (Motorola document number MC68HC908JB8/D),

#### MC68HC08JB8A

The MC68HC08JB8A is the ROM part equivalent to the MC68HC908JB8. The entire MC68HC908JB8 data book apply to this ROM device, with exceptions outlined in this addendum.

Table 1. Summary of MC68HC08JB8A and MC68HC908JB8 Differences

|                                               | MC68HC08JB8A                                                                  | MC68HC908JB8                                                |

|-----------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------|

| Memory (\$DC00-\$FBFF)                        | 8,192 bytes ROM                                                               | 8,192 bytes FLASH                                           |

| User vectors (\$FFF0-\$FFFF)                  | 16 bytes ROM                                                                  | 16 bytes FLASH                                              |

| Registers at \$FE08 and \$FF09                | Not used; locations are reserved.                                             | FLASH related registers.<br>\$FE08 — FLCR<br>\$FF09 — FLBPR |

| Monitor ROM (\$FC00-\$FDFF and \$FE10-\$FFDF) | \$FC00–\$FDFF: Not used.<br>\$FE10–\$FFDF: Used for<br>testing purposes only. | Used for testing and FLASH programming/erasing.             |

| OSC1 and OSC2 pins                            | V <sub>DD</sub> level (5V logic)                                              | V <sub>REG</sub> level (3.3V logic)                         |

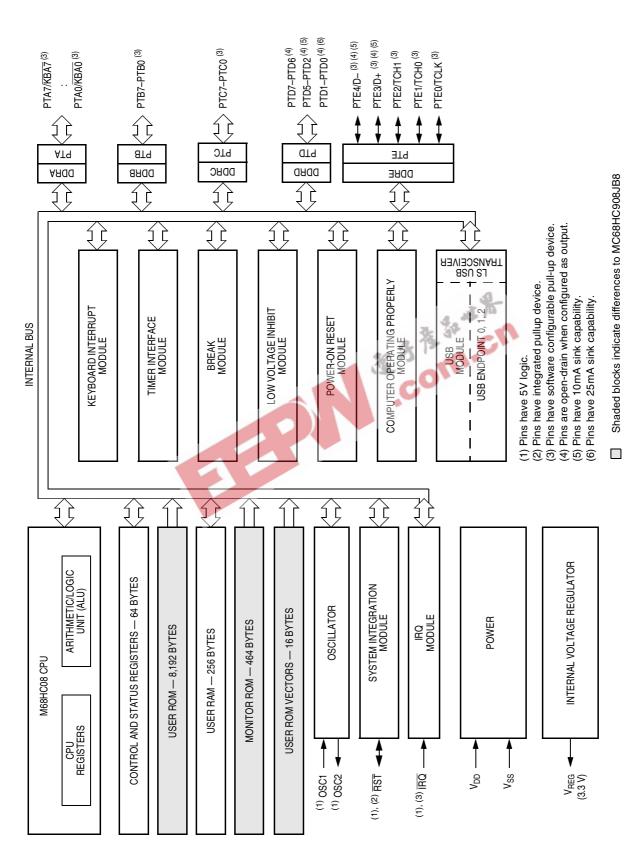

MCU Block Diagram Figure 1 shows the block diagram of the MC68HC08JB8A.

Memory Map The MC68HC08JB8A has 8,192 bytes of user ROM from \$DC00 to \$FBFF, and

16 bytes of user ROM vectors from \$FFF0 to \$FFFF. On the MC68HC908JB8,

these memory locations are FLASH memory.

Figure 2 shows the memory map of the MC68HC08JB8A.

Figure 1. MC68HC08JB8A Block Diagram

HC908JB8AD/D MC68HC08JB8A

| \$0000<br>I | I/O Registers                              |

|-------------|--------------------------------------------|

| \$003F      | 64 Bytes                                   |

| \$0040      | RAM                                        |

| ↓<br>\$013F | 256 Bytes                                  |

| \$0140      | Unimplemented                              |

| ↓<br>\$DBFF | 56,000 Bytes                               |

| \$DC00      | 2011                                       |

| <b>1</b>    | ROM<br>8,192 Bytes                         |

| \$FBFF      | 5,102 5,100                                |

| \$FC00<br>↓ | Unimplemented                              |

| \$FDFF      | 512 Bytes                                  |

| \$FE00      | Break Status Register (BSR)                |

| \$FE01      | Reset Status Register (RSR)                |

| \$FE02      | Reserved                                   |

| \$FE03      | Break Flag Control Register (BFCR)         |

| \$FE04      | Interrupt Status Register 1 (INT1)         |

| \$FE05      | Reserved                                   |

| \$FE06      | Reserved                                   |

| \$FE07      | Reserved                                   |

| \$FE08      | Reserved                                   |

| \$FE09      | Reserved                                   |

| \$FE0A      | Reserved                                   |

| \$FE0B      | Reserved                                   |

| \$FE0C      | Break Address High Register (BRKH)         |

| \$FE0D      | Break Address Low Register (BRKL)          |

| \$FE0E      | Break Status and Control Register (BRKSCR) |

| \$FE0F      | Reserved                                   |

| \$FE10      | Monitor ROM                                |

| ↓<br>\$FFDF | 464 Bytes                                  |

| \$FFE0      | Deserred                                   |

| ↓           | Reserved<br>16 Bytes                       |

| \$FFEF      |                                            |

| \$FFF0<br>↓ | ROM Vectors                                |

| \$FFFF      | 16 Bytes                                   |

|             |                                            |

Figure 2. MC68HC08JB8A Memory Map

#### HC908JB8AD/D

**Reserved Registers** The two registers at \$FE08 and \$FE09 are reserved locations on the

MC68HC08JB8A.

On the MC68HC908JB8, these two locations are the FLASH control register

and the FLASH block protect register respectively.

**Monitor ROM** The monitor program (monitor ROM: \$FE10-\$FFDF) on the MC68HC08JB8A

is for device testing only. \$FC00-\$FDFF are unused.

**Electrical** Electrical specifications for the MC68HC908JB8 apply to the MC68HC08JB8A, **Specifications**

except for the parameters indicated below.

DC Electrical Characteristics

**Table 2. DC Electrical Characteristics**

| Characteristic <sup>(1)</sup>                                                                                                                                                                                                                               | Symbol           | Min                                         | Typ <sup>(2)</sup>                               | Max                                         | Unit           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------|--------------------------------------------------|---------------------------------------------|----------------|

| Regulator output voltage                                                                                                                                                                                                                                    | V <sub>REG</sub> | 3.0                                         | 3.3                                              | 3.6                                         | V              |

| Output high voltage (I <sub>Load</sub> = -2.0 mA) PTA0-PTA7, PTB0-PTB7, PTC0-PTC7, PTE0-PTE2                                                                                                                                                                | V <sub>OH</sub>  | V <sub>REG</sub> -0.8                       | _                                                | _                                           | V              |

| Output low voltage  (I <sub>Load</sub> = 1.6 mA) All I/O pins  (I <sub>Load</sub> = 25 mA) PTD0-PTD1 in ILDD mode  (I <sub>Load</sub> = 10 mA) PTE3-PTE4 with USB disabled                                                                                  | V <sub>OL</sub>  | 111                                         | _<br>_<br>_                                      | 0.4<br>0.5<br>0.4                           | >              |

| Input high voltage All ports, OSC1 IRQ, RST                                                                                                                                                                                                                 | V <sub>IH</sub>  | $0.7 \times V_{REG}$<br>$0.7 \times V_{DD}$ |                                                  | V <sub>REG</sub><br>V <sub>DD</sub>         | V              |

| Input low voltage All ports, OSC1 IRQ, RST                                                                                                                                                                                                                  | V <sub>IL</sub>  | V <sub>SS</sub><br>V <sub>SS</sub>          | _                                                | $0.3 \times V_{REG}$<br>$0.3 \times V_{DD}$ | >              |

| Output low current (V <sub>OL</sub> = 2.0 V)<br>PTD2–PTD5 in LDD mode                                                                                                                                                                                       | I <sub>OL</sub>  | 12 (17)                                     | 17 (22)                                          | 22 (27)                                     | mA             |

| $V_{DD}$ supply current, $V_{DD}$ = 5.25V, $f_{OP}$ = 3MHz<br>Run, with low speed USB <sup>(3)</sup><br>Run, with USB suspended <sup>(3)</sup><br>Wait, with low speed USB <sup>(4)</sup><br>Wait, with USB suspended <sup>(4)</sup><br>Stop <sup>(5)</sup> | I <sub>DD</sub>  |                                             | 6.0 (5.0)<br>5.5 (4.5)<br>4.0 (3.0)<br>3.0 (2.5) | 7.5<br>6.5<br>5.0<br>4.0                    | mA<br>mA<br>mA |

| 0 °C to 70°C                                                                                                                                                                                                                                                |                  | _                                           | 30                                               | 100                                         | μA             |

HC908JB8AD/D MC68HC08JB8A

**Table 2. DC Electrical Characteristics**

| Characteristic <sup>(1)</sup>                                                                                                  | Symbol                              | Min                 | Typ <sup>(2)</sup> | Max                      | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------|--------------------|--------------------------|------|

| I/O ports Hi-Z leakage current                                                                                                 | I <sub>IL</sub>                     | _                   | _                  | ± 10                     | μΑ   |

| Input current                                                                                                                  | I <sub>IN</sub>                     | _                   | _                  | ± 1                      | μΑ   |

| Capacitance Ports (as input or output)                                                                                         | C <sub>Out</sub><br>C <sub>In</sub> | _                   | _                  | 12<br>8                  | pF   |

| POR re-arm voltage <sup>(6)</sup>                                                                                              | V <sub>POR</sub>                    | 0                   | _                  | 100                      | mV   |

| POR rise-time ramp rate <sup>(7)</sup>                                                                                         | R <sub>POR</sub>                    | 0.035               | _                  | _                        | V/ms |

| Monitor mode entry voltage                                                                                                     | $V_{DD}+V_{HI}$                     | $1.4 \times V_{DD}$ |                    | $2 \times V_{DD}$        | V    |

| Pullup resistors Port A, port B, port C, PTE0–PTE2, RST, IRQ PTE3–PTE4 (with USB module disabled) D– (with USB module enabled) | R <sub>PU</sub>                     | 25<br>4<br>1.2      | 40<br>5<br>1.5     | 55<br>6<br>2.0           | kΩ   |

| LVI reset                                                                                                                      | V <sub>LVR</sub>                    | 2.8 (2.4)           | 3.3 (2.7)          | 3.8 (3.0) <sup>(8)</sup> | V    |

- 1.  $V_{DD}$  = 4.0 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted.

- 2. Typical values reflect average measurements at midpoint of voltage range, 25 °C only.

- 3. Run (operating)  $I_{DD}$  measured using external square wave clock source ( $f_{XCLK} = 6$  MHz). All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs.  $C_L = 20$  pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run  $I_{DD}$ . Measured with all modules enabled.

- 4. Wait  $I_{DD}$  measured using external square wave clock source ( $f_{XCLK}$  = 6 MHz); all inputs 0.2 V from rail; no dc loads; less than 100 pF on all outputs.  $C_L$  = 20 pF on OSC2; 15 k $\Omega$  ± 5% termination resistors on D+ and D- pins; all ports configured as inputs; OSC2 capacitance linearly affects wait  $I_{DD}$

- 5. STOP I<sub>DD</sub> measured with USB in suspend mode; OSC1 grounded; transceiver pullup resistor of 1.5 k $\Omega$  ± 5% between V<sub>REG</sub> and D– pins and 15 k $\Omega$  ± 5% termination resistor on D+ pin; no port pins sourcing current.

- 6. Maximum is highest voltage that POR is guaranteed.

- If minimum V<sub>REG</sub> is not reached before the internal POR reset is released, RST must be driven low externally until minimum V<sub>REG</sub> is reached.

- 8. The numbers in parenthesis are MC68HC08JB8 (non-A part) values.

#### Memory Characteristics

**Table 3. Memory Characteristics**

| Characteristic             | Symbol    | Min | Max | Unit |

|----------------------------|-----------|-----|-----|------|

| RAM data retention voltage | $V_{RDR}$ | 1.3 | _   | V    |

Notes:

Since MC68HC08JB8A is a ROM device, FLASH memory electrical characteristics do not apply.

### HC908JB8AD/D

MC68HC08JB8A Order Numbers These part numbers are generic numbers only. To place an order, ROM code must be submitted to the ROM Processing Center (RPC).

Table 4. MC68HC08JB8A Order Numbers

| MC order number | Package     | Operating temperature range |

|-----------------|-------------|-----------------------------|

| MC68HC08JB8AJP  | 20-pin PDIP | 0 °C to +70 °C              |

| MC68HC08JB8AJDW | 20-pin SOIC | 0 °C to +70 °C              |

| MC68HC08JB8AADW | 28-pin SOIC | 0 °C to +70 °C              |

| MC68HC08JB8AFB  | 44-pin QFP  | 0 °C to +70 °C              |

#### MC68HC08JB8A and MC68HC08JB8 Differences

The MC68HC08JB8A and MC68HC08JB8 are identical devices, except for the following:

Table 5. MC68HC08JB8A and MC68HC08JB8 Differences

|                                             | MC68HC08JB8A                                                                                                   | MC68HC08JB8                         |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------|--|

| OSC1 and OSC2 pins                          | V <sub>DD</sub> level (5V logic)                                                                               | V <sub>REG</sub> level (3.3V logic) |  |

| Output low current on PTD2-PTD5 in LDD mode | See <b>Table 2</b> . <b>DC Electrical Characteristics</b> . The numbers in parenthesis are MC68HC08JB8 values. |                                     |  |

| Operating I <sub>DD</sub> currents          |                                                                                                                |                                     |  |

| LVI trip points                             |                                                                                                                |                                     |  |

**NOTES**