# **OPA129**

# Ultra-Low Bias Current Difet® **OPERATIONAL AMPLIFIER**

### FEATURES

- ULTRA-LOW BIAS CURRENT: 100fA max

- LOW OFFSET: 2mV max

- LOW DRIFT: 10µV/°C max

- HIGH OPEN-LOOP GAIN: 94dB min

- LOW NOISE: 15nV/√Hz at 10kHz

- PLASTIC DIP and SOIC PACKAGE

### DESCRIPTION

The OPA129 is an ultra-low bias current monolithic operational amplifier offered in an 8-pin PDIP and SO-8 package. Using advanced geometry dielectrically-isolated FET (Difet®) inputs, this monolithic amplifier achieves a high performance level.

Difet fabrication eliminates isolation-junction leakage current-the main contributor to input bias current with conventional monolithic FETs. This reduces input bias current by a factor of 10 to 100. Very low input bias current can be achieved without resorting to small-geometry FETs or CMOS designs which can suffer from much larger offset voltage, voltage noise, drift, and poor power supply rejection.

The OPA129's special pinout eliminates leakage current that occurs with other op amps. Pins 1 and 4 have no internal connection, allowing circuit board guard traces-even with the surface-mount package version.

OPA129 is available in 8-pin DIP and SO-8 packages, specified for operation from -40°C to +85°C.

## APPLICATIONS

- PHOTODETECTOR PREAMP

- CHROMATOGRAPHY

- ELECTROMETER AMPLIFIERS

- MASS SPECTROMETER

- pH PROBE AMPLIFIER

- **GAGE MEASUREMENT**

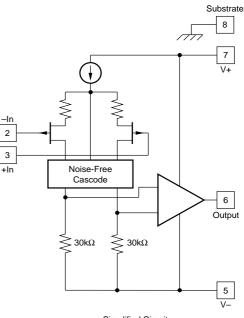

Simplified Circuit

Difet® Burr-Brown Corp.

Tel: (520) 746-1111 • Twx: 910-952-1111 • Cable: BBRCORP

International Airport Industrial Park • Mailing Address: PO Box 11400 • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706 Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

©1994 Burr-Brown Corporation

## SPECIFICATIONS

### ELECTRICAL

At V\_S =  $\pm 15V$  and T\_A = +25°C unless otherwise noted. Pin 8 connected to ground.

|                                                                                                              |                                                                                                                                                                                                                        | OPA129PB, UB      |                                                |                     | OPA129P, U  |               |         |                                                         |

|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------|---------------------|-------------|---------------|---------|---------------------------------------------------------|

| PARAMETER                                                                                                    | CONDITION                                                                                                                                                                                                              | MIN               | TYP                                            | MAX                 | MIN         | TYP           | MAX     | UNITS                                                   |

| INPUT BIAS CURRENT <sup>(1)</sup><br>vs Temperature                                                          | V <sub>CM</sub> = 0V                                                                                                                                                                                                   | Dou               | ±30<br>ubles every 1                           | ±100<br>0°C         |             | *             | ±250    | fA                                                      |

| INPUT OFFSET CURRENT                                                                                         | V <sub>CM</sub> = 0V                                                                                                                                                                                                   |                   | ±30                                            |                     |             | *             |         | fA                                                      |

| OFFSET VOLTAGE<br>Input Offset Voltage<br>vs Temperature<br>Supply Rejection                                 | $V_{CM} = 0V$<br>$V_{S} = \pm 5V \text{ to } \pm 18V$                                                                                                                                                                  |                   | ±0.5<br>±3<br>±3                               | ±2<br>±10<br>±100   |             | ±1<br>±5<br>* | ±5<br>* | mV<br>μV/°C<br>μV/V                                     |

| NOISE<br>Voltage<br>Current                                                                                  | $\begin{array}{c} f=10Hz\\ f=100Hz\\ f=1kHz\\ f=0kHz\\ f_{B}=0.1Hz \ to \ 10Hz\\ f=10kHz \end{array}$                                                                                                                  |                   | 85<br>28<br>17<br>15<br>4<br>0.1               |                     |             | * * * * *     |         | nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>μVp-p<br>fA/√Hz |

| INPUT IMPEDANCE<br>Differential<br>Common-Mode                                                               |                                                                                                                                                                                                                        |                   | 10 <sup>13</sup>    1<br>10 <sup>15</sup>    2 |                     |             | *             |         | Ω    pF<br>Ω    pF                                      |

| VOLTAGE RANGE<br>Common-Mode Input Range<br>Common-Mode Rejection                                            | V <sub>IN</sub> = ±10V                                                                                                                                                                                                 | ±10<br>80         | ±12<br>118                                     | 4.4                 | 3 % -       | *             |         | V<br>dB                                                 |

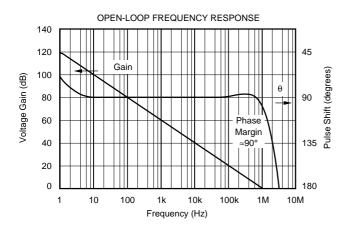

| OPEN-LOOP GAIN, DC<br>Open-Loop Voltage Gain                                                                 | $R_L \ge 2k\Omega$                                                                                                                                                                                                     | 94                | 120                                            | ない                  | (*)         | *             |         | dB                                                      |

| FREQUENCY RESPONSE<br>Unity Gain, Small Signal<br>Full Power Response<br>Slew Rate<br>Settling Time:<br>0.1% | $\begin{array}{l} 20 \text{Vp-p, } R_{\text{L}} = 2 k \Omega \\ \text{V}_{\text{O}} = \pm 10 \text{V}, R_{\text{L}} = 2 k \Omega \\ \text{G} = -1, R_{\text{L}} = 2 k \Omega, \ 10 \text{V} \ \text{Step} \end{array}$ | 4                 | 1<br>47<br>2.5<br>5                            | om                  | *           | * * *         |         | MHz<br>kHz<br>V/μs<br>μs                                |

| 0.1%<br>0.01%<br>Overload Recovery, 50% Overdrive <sup>(2)</sup>                                             | G = -1                                                                                                                                                                                                                 |                   | 10<br>5                                        |                     |             | *             |         | μs<br>μs<br>μs                                          |

| RATED OUTPUT<br>Voltage Output<br>Current Output<br>Load Capacitance Stability<br>Short-Circuit Current      | $\begin{array}{l} R_L = 2k\Omega \\ V_O = \pm 12V \\ Gain = +1 \end{array}$                                                                                                                                            | ±12<br>±6         | ±13<br>±10<br>1000<br>±35                      | ±55                 | *           | * * *         | *       | V<br>mA<br>pF<br>mA                                     |

| POWER SUPPLY<br>Rated Voltage<br>Voltage Range, Derated Performance<br>Current, Quiescent                    | I <sub>O</sub> = 0mA                                                                                                                                                                                                   | ±5                | ±15<br>1.2                                     | ±18<br>1.8          | *           | *             | *       | V<br>V<br>mA                                            |

| TEMPERATURE<br>Specification<br>Operating<br>Storage<br>Thermal Resistance                                   | Ambient Temperature<br>Ambient Temperature                                                                                                                                                                             | -40<br>-40<br>-40 |                                                | +85<br>+125<br>+125 | *<br>*<br>* |               | *<br>*  | 0°<br>0°<br>0°                                          |

| PDIP—"P"<br>SOIC—"U"                                                                                         | $\theta_{\rm JA}$ , Junction-to-Ambient                                                                                                                                                                                |                   | 90<br>100                                      |                     |             | *             |         | °C/W<br>°C/W                                            |

NOTES: (1) High-speed automated test. (2) Overload recovery is defined as the time required for the output to return from saturation to linear operation following the removal of a 50% input overdrive.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

#### **ABSOLUTE MAXIMUM RATINGS**

| Power Supply Voltage±18V                          |

|---------------------------------------------------|

| Differential Input VoltageV- to V+                |

| Input Voltage Range                               |

| Storage Temperature Range40°C to +125°C           |

| Operating Temperature Range40°C to +125°C         |

| Lead Temperature (soldering, 10s; SOIC 3s) +300°C |

| Output Short Circuit Duration <sup>(1)</sup>      |

| Junction Temperature (T <sub>J</sub> )+150°C      |

|                                                   |

NOTE: (1) Short circuit may be to power supply common at +25°C ambient.

## ELECTROSTATIC DISCHARGE SENSITIVITY

Any integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet published specifications.

#### **PACKAGE INFORMATION**

| MODEL    | PACKAGE           | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|----------|-------------------|------------------------------------------|

| OPA129P  | 8-pin Plastic DIP | 006                                      |

| OPA129PB | 8-pin Plastic DIP | 006                                      |

| OPA129U  | 8-pin SOIC        | 182                                      |

| OPA129UB | 8-pin SOIC        | 182                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

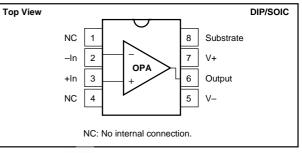

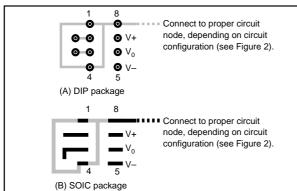

#### **CONNECTION DIAGRAM**

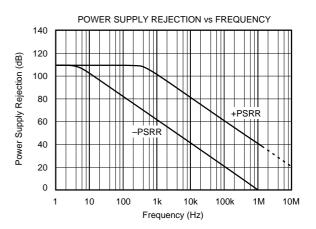

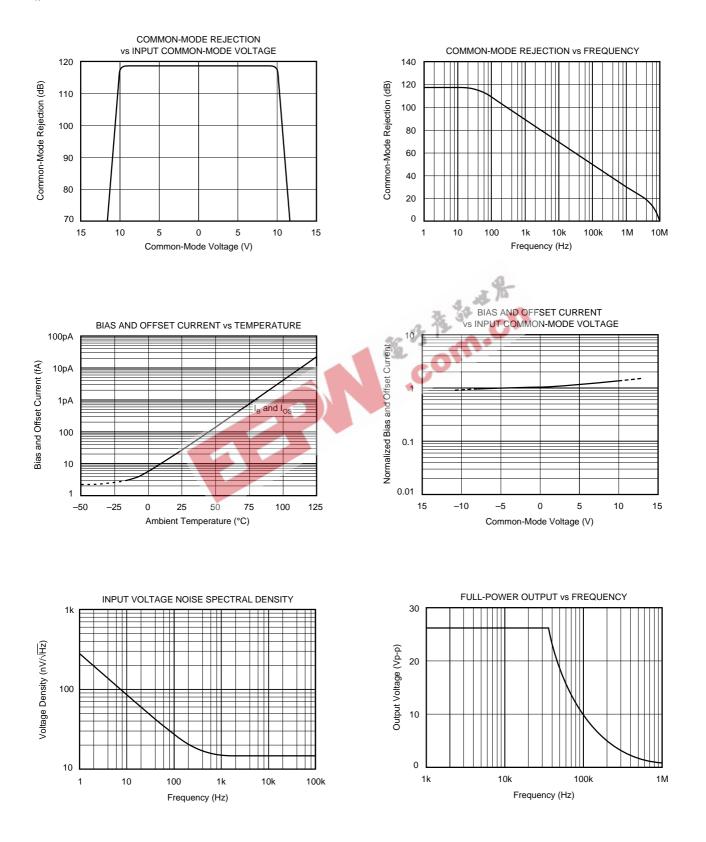

### **TYPICAL PERFORMANCE CURVES**

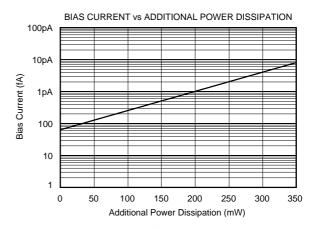

$T_{A} = +25^{\circ}C$ , +15VDC, unless otherwise noted.

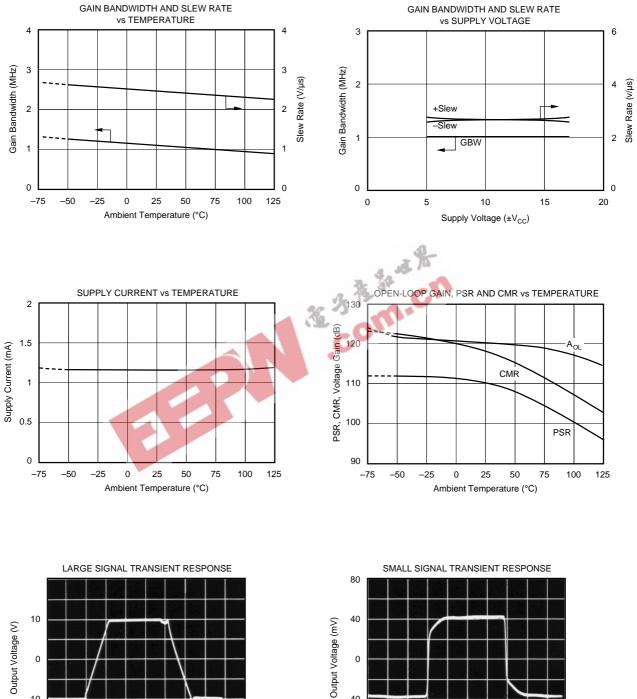

## **TYPICAL PERFORMANCE CURVES (CONT)**

$T_A = +25^{\circ}C$ , +15VDC, unless otherwise noted.

4

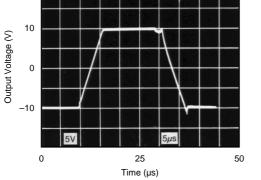

## **TYPICAL PERFORMANCE CURVES (CONT)**

$T_A = +25^{\circ}C$ , +15VDC, unless otherwise noted.

0

-40

-80

0

20m

2

111

8

10

6

4

Time (µs)

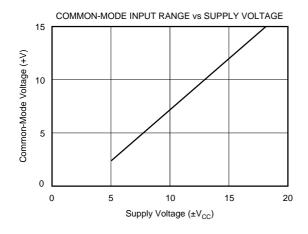

### **TYPICAL PERFORMANCE CURVES (CONT)**

$T_A = +25^{\circ}C$ , +15VDC, unless otherwise noted.

## APPLICATIONS INFORMATION

### NON-STANDARD PINOUT

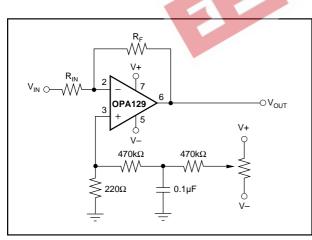

The OPA129 uses a non-standard pinout to achieve lowest possible input bias current. The negative power supply is connected to pin 5—see Figure 1. This is done to reduce the leakage current from the V- supply (pin 4 on conventional op amps) to the op amp input terminals. With this new pinout, sensitive inputs are separated from both power supply pins.

FIGURE 1. Offset Adjust Circuit.

#### OFFSET VOLTAGE TRIM

The OPA129 has no conventional offset trim connections. Pin 1, next to the critical inverting input, has no internal connection. This eliminates a source of leakage current and allows guarding of the input terminals. Pin 1 and pin 4, next to the two input pins, have no internal connection. This allows an optimized circuit board layout with guarding—see "circuit board layout."

Due to its laser-trimmed input stage, most applications do not require external offset voltage trimming. If trimming is required, the circuit shown in Figure 1 can be used. Power supply voltages are divided down, filtered and applied to the non-inverting input. The circuit shown is sensitive to variation in the supply voltages. Regulation can be added, if needed.

#### **GUARDING AND SHIELDING**

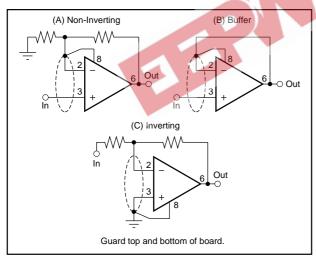

Ultra-low input bias current op amps require precautions to achieve best performance. Leakage current on the surface of circuit board can exceed the input bias current of the amplifier. For example, a circuit board resistance of  $10^{12}\Omega$  from a power supply pin to an input pin produces a current of 15pA—more than one-hundred times the input bias current of the op amp.

To minimize surface leakage, a guard trace should completely surround the input terminals and other circuitry connecting to the inputs of the op amp. The DIP package should have a guard trace on both sides of the circuit board. The guard ring should be driven by a circuit node equal in potential to the op amp inputs—see Figure 2. The substrate, pin 8, should also be connected to the circuit board guard to assure that the amplifier is fully surrounded by the guard potential. This minimizes leakage current and noise pick-up.

Careful shielding is required to reduce noise pickup. Shielding near feedback components may also help reduce noise pick-up.

Triboelectric effects (friction-generated charge) can be a troublesome source of errors. Vibration of the circuit board, input connectors and input cables can cause noise and drift. Make the assembly as rigid as possible. Attach cables to avoid motion and vibration. Special low noise or low leakage cables may help reduce noise and leakage current. Keep all input connections as short possible. Surface-mount components may reduce circuit board size and allow a more rigid assembly.

### **CIRCUIT BOARD LAYOUT**

The OPA129 uses a new pinout for ultra low input bias current. Pin 1 and pin 4 have no internal connection. This allows ample circuit board space for a guard ring surrounding the op amp input pins—even with the tiny SO-8 surfacemount package. Figure 3 shows suggested circuit board layouts. The guard ring should be connected to pin 8 (substrate) as shown. It should be driven by a circuit node equal in potential to the input terminals of the op amp—see Figure 2 for common circuit configurations.

### TESTING

Accurately testing the OPA129 is extremely difficult due to its high performance. Ordinary test equipment may not be able to resolve the amplifier's extremely low bias current.

Inaccurate bias current measurements can be due to:

- 1. Test socket leakage,

- 2. Unclean package,

- 3. Humidity or dew point condensations,

- 4. Circuit contamination from fingerprints or anti-static treatment chemicals,

- 5. Test ambient temperature,

- 6. Load power dissipation,

- 7. Mechanical stress,

- 8. Electrostatic and electromagnetic interference.

FIGURE 3. Suggested Board Layout for Input Guard.

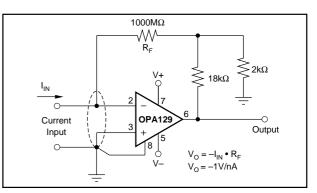

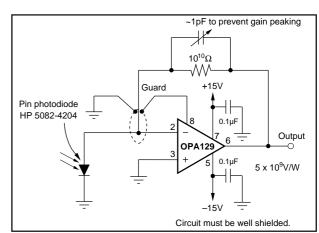

FIGURE 4. Current-to-Voltage Converter.

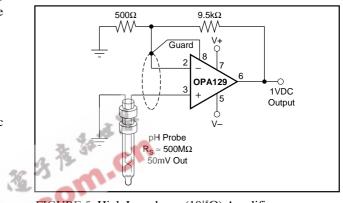

FIGURE 5. High Impedance ( $10^{15}\Omega$ ) Amplifier.

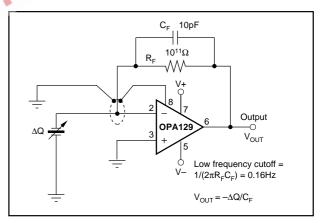

FIGURE 6. Piezoelectric Transducer Charge Amplifier.

**OPA129**