# W83601R/602R Winbond SMBus GPI/O

# **PRELIMINARY**

# W83601R/602R Data Sheet Revision History

|    | Pages        | Dates | Version | Version | Main Contents                                                                                                  |

|----|--------------|-------|---------|---------|----------------------------------------------------------------------------------------------------------------|

|    |              |       |         | on Web  |                                                                                                                |

| 1  | n.a.         |       |         | n.a.    | All the version before 0.30 are for internal use.                                                              |

| 2  | n.a.         | 99/8  | 0.3     | n.a.    | First publication.                                                                                             |

| 3  | P.4,5<br>P.6 | 99/8  | 0.31    | n.a.    | Change Pin Description of W83601R pin 3,4,5. Change Pin Description of W83602R pin 3,4. Update Register Table. |

|    | P.10<br>P.13 |       |         |         | CR16 is a reserved register. Please ignore it. Change INT output description.                                  |

| 4  | P.10         | 99/9  | 0.32    | n.a.    | CR15 bit 3 description.                                                                                        |

| 5  |              |       |         |         | Com                                                                                                            |

| 6  |              |       |         |         |                                                                                                                |

| 7  |              |       |         |         |                                                                                                                |

| 8  |              |       | 1       |         |                                                                                                                |

| 9  |              |       |         |         |                                                                                                                |

| 10 |              |       |         |         |                                                                                                                |

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this data sheet belong to their respective owners.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.

#### 1. GENERAL DESCRIPTION

The W83601R/602R are general purpose input/output ICs with SMBus<sup>™</sup>. W83601R provides 15 GPI/O pins. W83602R provides 9 GPI/O pins and ACPI power control function for STR. W83601R/602R both provides SMBus<sup>™</sup> address setting pins to set the address during power- on reset or from external reset.

| W83601R SMBus <sup>™</sup> Address is : | 0 | 0 | 1 | 1 | A2 | A1 | Α0  | R/W |

|-----------------------------------------|---|---|---|---|----|----|-----|-----|

|                                         |   |   | I |   |    |    | i 1 |     |

W83601R/602R also provides a interrupt to inform system that a transition occurs on General Purpose(GP) input pins.

#### 2. FEATURES

- SMBus compliance with 3.3V voltage levels

- Two ports GPI/O which provides more flexibility

- Issue interrupt to notify system that a event occurs

- GP output can be level or pulse mode

- Interrupt output can be level or pulse mode

- Internal power-on reset or external RST# pin reset

- Programmable POWER LED output

- ACPI power management for Suspend To Ram (STR) (only for W83602R)

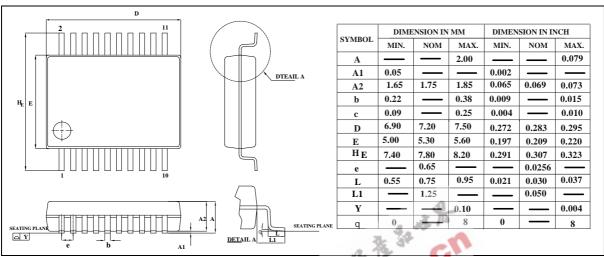

#### 3. PACKAGE

• 20-pin SSOP

# **Preliminary**

#### 4. KEY SPECIFICATIONS

Supply Voltage 5V

Operating Supply Current 1 mA typ.

Operating Temperature 0 - 70 °C

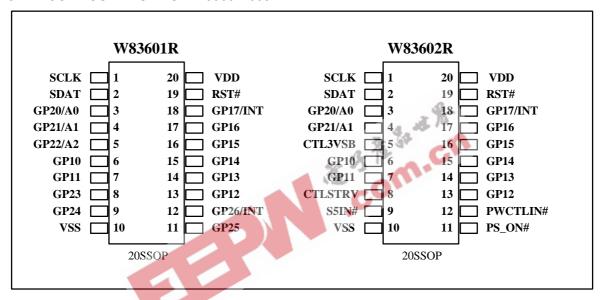

#### 5. PIN CONFIGURATION FOR W83601R/602R

# **Preliminary**

## 6. PIN DESCRIPTION

Note: Please refer to Section 13.2 DC CHARACTERISTICS for details.

I/OD<sub>24t</sub> - TTL level bi-directional pin open drain output with 12 mA sink capability

I/O<sub>24t</sub> - TTL level bi-directional pin with 24 mA source-sink capability

INt - TTL level input pin

INtd - TTL level input pin with internal pull down resistor

INts - TTL level Schmitt-trigger input pin

## W83601R UNIVERSAL GENERAL PURPOSE I/O PORT FOR I2C BUS

| PIN | SYMBOL | I/O                | FUNCTION                                                                                                                |

|-----|--------|--------------------|-------------------------------------------------------------------------------------------------------------------------|

| 1   | SCL    | IN <sub>ts</sub>   | SMBus Clock. (I <sup>2</sup> C clock)                                                                                   |

| 2   | SDA    | I/OD <sub>12</sub> | SMBus bi-directional Data.(I2C data)                                                                                    |

| 3   | GP20   | I/O <sub>24</sub>  | General Purpose I/O . This pin is a setting pin for SMBus(I <sup>2</sup> C)                                             |

|     | A0     | IN <sub>td</sub>   | address bit 0 during power-on reset or RST# pin reset.                                                                  |

| 4   | GP21   | I/O <sub>24</sub>  | General Purpose I/O . This pin is a setting pin for SMBus(I <sup>2</sup> C)                                             |

|     | A1     | IN <sub>td</sub>   | address bit 1 during power-on reset or RST# pin reset.                                                                  |

| 5   | GP22   | I/O <sub>24</sub>  | General Purpose I/O . This pin is a setting pin for SMBus(I <sup>2</sup> C)                                             |

|     | A2     | IN <sub>td</sub>   | address bit 2 during power-on reset or RST# pin reset.                                                                  |

| 6   | GP10   | I/OD <sub>24</sub> | General Purpose I/O default input.                                                                                      |

| 7   | GP11   | I/OD <sub>24</sub> | General Purpose I/O default input.                                                                                      |

| 8   | GP23   | I/OD <sub>24</sub> | General Purpose I/O default input.                                                                                      |

| 9   | GP24   | I/OD <sub>24</sub> | General Purpose I/O default input.                                                                                      |

| 10  | VSS    | PWR                | Ground Pin.                                                                                                             |

| 11  | GP25   | I/OD <sub>24</sub> | General Purpose I/O default input.                                                                                      |

| 12  | GP26   | I/OD <sub>24</sub> | General Purpose I/O default input.                                                                                      |

|     | INT    | OD <sub>24</sub>   | Auto-generate Interrupt signal when detetecting a transition on GPI inputs. This interrupt is either on pin12 or pin18. |

| 13  | GP12   | I/OD <sub>24</sub> | General Purpose I/O default input.                                                                                      |

| 14  | GP13   | I/OD <sub>24</sub> | General Purpose I/O default input.                                                                                      |

| 15  | GP14   | I/OD <sub>24</sub> | General Purpose I/O default input.                                                                                      |

| 16  | GP15   | I/OD <sub>24</sub> | General Purpose I/O default input.                                                                                      |

| 17  | GP16   | I/OD <sub>24</sub> | General Purpose I/O default input.                                                                                      |

| 18  | GP17   | I/OD <sub>24</sub> | General Purpose I/O default input.                                                                                      |

|     | INT    | OD <sub>24</sub>   | Auto-generate Interrupt signal when detetecting a transition on GPI inputs. This interrupt is either on pin12 or pin18  |

| 19  | RST#   | IN <sub>ts</sub>   | Reset signal input.                                                                                                     |

# **Preliminary**

| 20 | VDD | PWR | Power Pin. |

|----|-----|-----|------------|

|----|-----|-----|------------|

# W83602R UNIVERSAL GENERAL PURPOSE I/O PORT FOR I2C BUS & ACPI POWER CONTROL

| PIN                                                                          | SYMBOL                      | I/O                                                                              | FUNCTION                                                                         |

|------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 1                                                                            | SCL                         | IN <sub>ts</sub>                                                                 | SMBus Clock. (I <sup>2</sup> C clock)                                            |

| 2 SDA I/OD <sub>1</sub>                                                      |                             | I/OD <sub>12</sub>                                                               | SMBus bi-directional Data.(I2C data)                                             |

| 3                                                                            | 3 GP20/A0 I/O <sub>24</sub> |                                                                                  | General Purpose I/O. Power on setting for SMBus(I <sup>2</sup> C) address bit 0. |

| 4 GP21/A1 I/O <sub>24</sub> General Purpose I/O. Power on setting for bit 1. |                             | General Purpose I/O. Power on setting for SMBus(I <sup>2</sup> C) address bit 1. |                                                                                  |

| 5                                                                            | CTL3VSB                     | OD <sub>24</sub>                                                                 | Control 3VSB and 3VCC power source for ACPI features.                            |

| 6                                                                            | GP10                        | I/OD <sub>24</sub>                                                               | General Purpose I/O default input.                                               |

| 7                                                                            | GP11                        | I/OD <sub>24</sub>                                                               | General Purpose I/O default input.                                               |

| 8                                                                            | CTLSTR                      | OD <sub>24</sub>                                                                 | Suspend to RAM power control output.                                             |

| 9                                                                            | S5IN#                       | IN <sub>t</sub>                                                                  | S5# signal input.                                                                |

| 10                                                                           | VSS                         | PWR                                                                              | Ground Pin.                                                                      |

| 11                                                                           | PS_ON#                      | OD <sub>24</sub>                                                                 | ATX power power on_off control.                                                  |

|                                                                              |                             | INt                                                                              | Connected to W83627F/HF power control output.                                    |

|                                                                              |                             | I/OD <sub>24</sub>                                                               | General Purpose I/O default input.                                               |

| 14                                                                           | GP13                        | I/OD <sub>24</sub>                                                               | General Purpose I/O default input.                                               |

| 15                                                                           | GP14                        | I/OD <sub>24</sub>                                                               | General Purpose I/O default input.                                               |

| 16                                                                           | GP15                        | I/OD <sub>24</sub>                                                               | General Purpose I/O default input.                                               |

| 17                                                                           | GP16                        | I/OD <sub>24</sub>                                                               | General Purpose I/O default input.                                               |

| 18                                                                           | GP17                        | I/OD <sub>24</sub>                                                               | General Purpose I/O default input.                                               |

|                                                                              | INT                         | OD <sub>24</sub>                                                                 | Auto-generate Interrupt signal when detetecting a transition on GPI inputs.      |

| 19                                                                           | RST#                        | IN <sub>ts</sub>                                                                 | Reset signal input.                                                              |

| 20                                                                           | VDD                         | PWR                                                                              | Power Pin.                                                                       |

# **Preliminary**

## 7. REGISTERS

## 7.1 BRIEF OF REGISTER CONTENTS

| INDEX  | R/W | DEFAULT | REGISTERS DESCRIPTION                          |

|--------|-----|---------|------------------------------------------------|

| 00h    | R   | 1       | GP Port 1: Input Port Data Register            |

| 01h    | R/W | 00      | GP Port 1: Output Port Data Register           |

| 02h    | R/W | f0      | GP Port 1: Polarity Inversion Register         |

| 03h    | R/W | ff      | GP Port 1: Input/Output Configuration Register |

| 04h    | R/W | 00      | GP Port 1: Output style control Register.      |

| 05h    | R   | -       | GP Port 1: Input Latched Data Register.        |

| 06-07h | -   | -       | Reserved Register                              |

| 08h    | R   | -       | GP Port 2: Input Port Register                 |

| 09h    | R/W | 00      | GP Port 2: Output Port Register                |

| 0Ah    | R/W | 70      | GP Port 2: Polarity Inversion Register         |

| 0Bh    | R/W | 7f      | GP Port 2: Input/Output Configuration Register |

| 0Ch    | R/W | 00      | GP Port 2: Output style control Register.      |

| 0Dh    | R   | -       | GP Port 2: Input Latched Data Register.        |

| 0E-0Fh | -   | -       | Reserved Register                              |

| 10h    | R   | 00      | GP Port 1: Interrupt Status Register.          |

| 11h    | R   | 00      | GP Port 2: Interrupt Status Register           |

| 12h    | R/W | 00      | GP Port 1: Interrupt Enable Register           |

| 13h    | R/W | 00      | GP Port 2: Interrupt Enable Register           |

| 14h    | R/W | 00      | Mode Configuration Register                    |

| 15h    | R/W | 00      | Power LED Configuration Register               |

| 16-1Fh | -   | -       | Reserved Register                              |

| 20h    | R   | 60      | Chip ID High Byte Register                     |

| 21h    | R   | 12      | Chip ID Low Byte Register (W83601R)            |

|        |     | 22      | Chip ID Low Byte Register (W83602R)            |

#### 7.2 W83601R/602R REGISTERS DESCRIPTIONS

#### CR00 (GP Port 1: Input port Data Register, Default 0x--, Read Only)

This register is a data port for input only. It reflects the incoming logic levels of the pins whether the pins is defined as an input mode by CR03. It will be inverted data by CR02.

Bit 7 ~ 0: GP17 ~ GP10 Input Data Port.

#### CR01 (GP Port 1: Output port Data Register, Default 0x00, Read/Write)

This register is a data port for output only. It reflects the outgoing logic levels of the pins whether the pins is defined as an output mode by CR03. This register will reflect the value of output Flip-flop while read access. The output data will be inverted or changed output style by CR02 or CR04.

Bit 7 ~ 0: GP17 ~ GP10 Output Data Port.

#### CR02 (GP Port 1: Polarity Inversion Register, Default 0xf0, Read/Write)

This register enables polarity inversion of pins defined as input or output by CR03.

When set to a "1", the incoming/outgoing port value is inverted.

When set to a "0", the incoming/outgoing port value is the same as in data register.

Bit 7 ~ 0: GP17 ~ GP10 Polarity Iversion Register.

#### CR03 (GP Port 1: Input/Output Configuration Register, Default 0xff, Read/Write)

This register selects Input or Output mode of pins.

When set to a "1", respective GPIO port is programmed as an input port.

When set to a "0", respective GPIO port is programmed as an output port.

Bit 7 ~ 0: GP17 ~ GP10 Input/Output Configuration Register.

#### CR04 (GP Port 1: Output Style Control Register, Default 0x00, Read/Write)

This register selects Output style of pins as level or pulse.

When set to a "1", respective GPIO port is programmed as an pulse signal.

When set to a "0", respective GPIO port is programmed as an level signal.

Bit 7 ~ 0: GP17 ~ GP10 Output Style Control Register.

#### CR05 (GP Port 1: Input latched data Register, Default 0x--, Read Only)

This register will latch Port 1 data while power on or RST# pin low, which is controlled by CR14h bit 0.

Bit 7 ~ 0: GP17 ~ GP10 Input latched data.

#### CR06-07 Reserved Register

#### CR08 (GP Port 2: Input port Data Register, Default 0x--, Read Only )

This register is a data port for input only. It reflects the incoming logic levels of the pins whether the pins is defined as an input mode by CR0B. It will be inverted data by CR0A.

Bit 7: Reserved.

Bit 6 ~ 0: GP26 ~ GP20 Input Data Port.

#### CR09 (GP Port 2: Output port Data Register, Default 0x00, Read/Write)

This register is a data port for output only. It reflects the outgoing logic levels of the pins whether the pins is defined as an output mode by CR0B. This register will reflect the value of output Flip-flop while read access. The output data will be inverted or changed output style by CR0A or CR0C.

Bit 7: Reserved.

Bit 7 ~ 0: GP26 ~ GP20 Output Data Port.

#### CR0A (GP Port 2: Polarity Inversion Register, Default 0x70, Read/Write)

This register enables polarity inversion of pins defined as input or output by CR0B.

When set to a "1", the incoming/outgoing port value is inverted.

When set to a "0", the incoming/outgoing port value is the same as in data register.

Bit 7: Reserved.

Bit 6 ~ 0: GP26 ~ GP20 Polarity Inversion Register.

## CR0B (GP Port 2: Input/Output Configuration Register, Default 0x7f, Read/Write)

This register selects Input or Output mode of pins.

When set to a "1", respective GPIO port is programmed as an input port.

When set to a "0", respective GPIO port is programmed as an output port.

Bit 7: Reserved.

Bit 6 ~ 0: GP26 ~ GP20 Input/Output Configuration Register.

#### CR0C (GP Port 2: Output Style Control Register, Default 0x00, Read/Write)

This register selects Output style of pins as level or pulse.

When set to a "1", respective GPIO port is programmed as an pulse signal.

When set to a "0", respective GPIO port is programmed as an level signal.

Bit 7: Reserved.

Bit 6 ~ 0: GP26 ~ GP20 Output Style Control Register.

#### CR0D (GP Port 2: Input latched data Register, Default 0x--, Read Only)

This register will latch Port 2 data while power on or RST# pin low, which is controlled by CR14h bit 1.

Bit 7: Reserved.

Bit 6 ~ 0: GP26 ~ GP20 Input latched data, which bit 2-0 are SMBus address bit A2-A0.

#### **CR0E-0F Reserved Register**

#### CR10 (GP Port1: Interrupt Status Register, Default 0x00, Read Only)

Bit 7-0 : = 1, a transition occurs at pin GP17-GP10.

If GP17/INT is selected as interrupt function, bit 7 of this register will always be 0.

A read to this register will clear this register.

#### CR11 (GP Port2: Interrupt Status Register , Default 0x00, Read Only)

Bit 7: = Reserved.

Bit 6-0 : = 1, a transition occurs at pin GP26-GP20.

If GP26/INT is selected as interrupt function, bit 6 of this register will always be 0.

A read to this register will clear this register.

#### CR12 (GP Port 1: Interrupt Enable Register , Default 0x00 , Read/Write)

Bit 7-0 : = 0, disable GP17-GP10 interrupt output when interrupt function is selected.

# CR13 (GP Port 2: Interrupt Enable Register, Default 0x00, Read/Write)

Bit 7-6: = Reserved.

Bit 5-0 : = 0, disable GP26-GP20 interrupt output when interrupt function is selected.

## CR14 Mode Configuration Register (Default 0x00, Read/Write)

Bit 7 : = 1, Set GP/INT pin as INT function. 0, set GP/INT pin as GP function.

Bit 6 := 1, Set INT function at GP26(pin 12). 0 , Set INT function at GP17(pin 18). W83602R INT function is only at GP17.

Bit 5 : = 1, Set INT output pin as pulse mode. 0, set INT output pin as level mode.

Bit 4 := 1, Set INT output pin polarity is 1 (normal high) . 0, set INT output pin polarity is 0 (normal low). This bit is only for W83601R.

Bit 3 : = 1, Port 2 (CR09h-CR0Ch,CR11h,CR13h) registers can be reset to default data by RST# pin. 0 ,Port 2 (CR09h-CR0Ch) can not be reset by RST# pin.

Bit 2 : = 1, Port 1 (CR01h-CR04h,CR10h,CR12h) registers can be reset to default data by RST# pin. 0 ,Port 1 (CR01h-CR04h) can not be reset by RST# pin.

Bit 1 : = 1, Port 2 CR0Dh can be latched not only by RST# pin but also power-on period. 0, Port 2 CR0Dh can only be latched by power-on period.

Bit 0 : = 1, Port 1 CR05h can be latched not only by RST# pin but also power-on period. 0, Port 1 CR05h can only be latched by power-on period.

# CR15 Power LED Configuration Register (Default 0x00, Read/Write) Priority of LED function is highest.

Bit 7 : = 1, Enable LED function . 0, Disable LED funciton.

When LED function is enable, GP function is ignored despite of input or output.

Bit 6-4: LED frequency selection.

= 111, LED pin is tri-state(OD pin) or drived high(O pin).

= 110, LED pin is a 1 Hz toggle pulse with 50 duty cycle.

= 101, LED pin is a 1/2 Hz toggle pulse with 50 duty cycle.

= 100, LED pin is a 1/4 Hz toggle pulse with 50 duty cycle.

= 000, LED pin is drived low.

Bit 3: = GP port selection.

0, Select GP port 1 as LED function if bit 7 is set to 1.

1, Select GP port 2 as LED function if bit 7 Is set to 1.

As W83602R, setting this bit 1 is meaningless.

Bit 2-0: GP pin selection.

Down =110-000, GP16-GP10 can be selected as LED output when bit 3 is 0.

=101-011, GP25-GP23 can be selected as LED output when bit 3 is 1.

As W83602R, only GP16-GP10 can be selected as LED output.

#### **CR16-1F Reserved Register**

#### CR20 (Chip ID High Byte, Read Only)

Bit 7-0 := 0x60.

CR21 (Chip ID Low Byte, Read Only)

Bit 7-0 : = 0x12 (for W83601R).

= 0x22 (for W83602R).

NOTE: W83602R has no GP22-GP26. All the corresponding register has no effect on W83602R.

# **Preliminary**

#### 8. FUNCTION DESCRIPTIONS

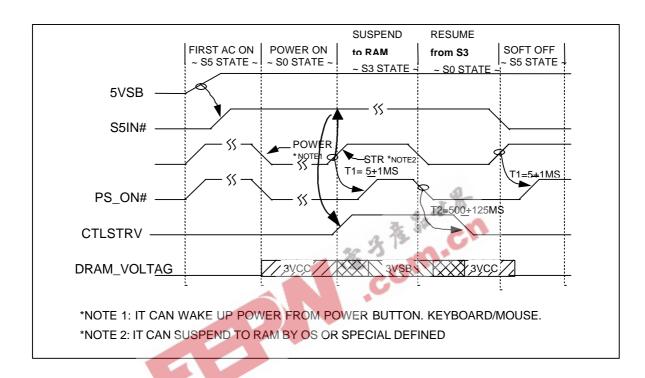

## 8.1 CTLSTRV TIMING WAVEFORMS (ONLY FOR W83602R)

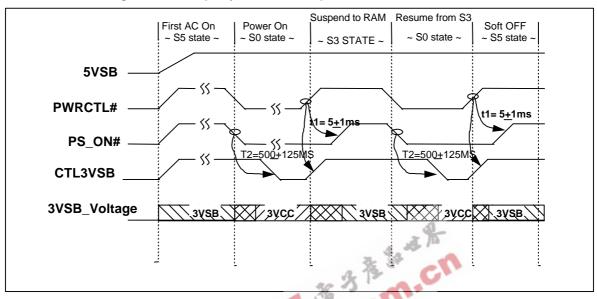

# 8.2 CTL3VSB Timing Waveforms(Only for W83602R)

## 8.3 GPI/O Output Mode:

## 8.3.1 GPO output

Tow output modes for GPO. One is LEVEL and the other is PULSE.

| GPO Output Style | Polarity | Output Port<br>Register | Output Value at Pin | Wave |

|------------------|----------|-------------------------|---------------------|------|

|                  | 0        | 0                       | 0                   |      |

|                  |          | 1                       | 1                   |      |

| Level            | 1        | 0                       | 1                   |      |

|                  |          | 1                       | 0                   |      |

| Pulse            | 0        | write 1                 | Active              | 7    |

|                  | 1        | write 1                 | Active              | 7    |

# **Preliminary**

#### 8.3.2 INT output

Two output modes for INT pin. One is LEVEL mode and the other is PULSE.

| INT Output Mode | Polarity       | Output     | Wave |

|-----------------|----------------|------------|------|

| Level           | 0(normal low)  | 1          |      |

|                 | 1(normal high) | 0          |      |

| Pulse           | 0(normal low)  | High Pulse |      |

|                 | 1(normal high) | Low Pulse  |      |

In Level mode, if INT is activated, it will be de-activated when interrupt status registers are read. In Pulse mode, interrupt will be activated again unless all enabled interrupt status registers are read.

# 8.3.3 GPI interrupt status

Once a transition occurs at GPI input pins, interrupt status registers(CR10, CR11) will be set. At the mean time, if interrupt function is enable, INT pin will generate a interrupt. Reading these interrupt registers will clear themselves and reset interrupt. If an interrupt occurs but no read to interrupt status registers, interrupt will not be generated again.

#### 9. PACKAGE DRAWING AND DIMENSIONS

20 SSOP-209 mil

Headquarters

No. 4, Creation Rd. III Science-Based Industrial Park Hsinchu, Taiwan TEL: 886-35-770066 FAX: 886-35-789467 www: http://www.winbond.com.tw/

Tainei Office

11F, No. 115, Sec. 3, Min-Sheng East Rd.

Taipei, Taiwan TEL: 886-2-7190505 FAX: 886-2-7197502 TLX: 16485 WINTPE

Winbond Electronics (H.K.) Ltd. Rm. 803, World Trade Square, Tower II 123 Hoi Bun Rd., Kwun Tong Kowloon, Hong Kong TEL: 852-27516023-7

FAX: 852-27552064

**Winbond Electronics** (North America) Corp.

2730 Orchard Parkway San Jose, CA 95134 U.S.A. TEL: 1-408-9436666 FAX: 1-408-9436668

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this data sheet belong to their respective owners.

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sale.

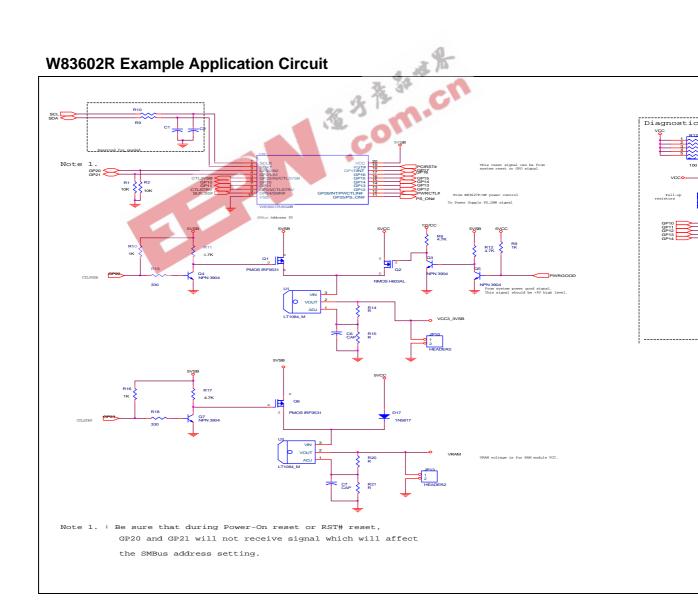

|     | 3 15                              |

|-----|-----------------------------------|

| REV | Decription                        |

| 0.1 | First Publication                 |

| 0.2 | Change CTL3VSB, CTLSTRV Schematic |

Winbond Electronic Corp.

Title W83601R/602R Example Applic

Size Document Number

Custs 602ap.sch