# PLL PhaseLink

(Preliminary) PL580-35/37/38/39

### 38MHz-320MHz Low Phase Noise VCXO

### FEATURES

- Less than 0.4ps RMS (12KHz-20MHz) phase jitter for all frequencies.

- Less than 25ps (typ.) peak to peak jitter for all frequencies.

- Low phase noise output (@ 1MHz frequency offset

- \* -144dBc/Hz for 155.52MHz

- \* -140dBC/Hz for 311.04MHz

- 19MHz-40MHz crystal input.

- 38MHz-320MHz output.

- Available in PECL, LVDS, or CMOS outputs.

- No external varicap required.

- Output Enable selector.

- Wide pull range (+/-200ppm).

- 3.3V operation.

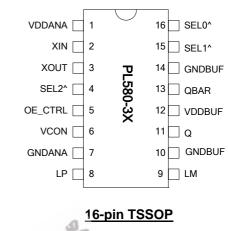

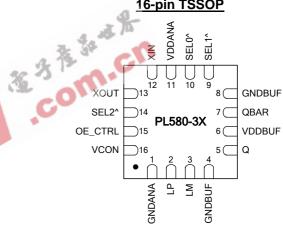

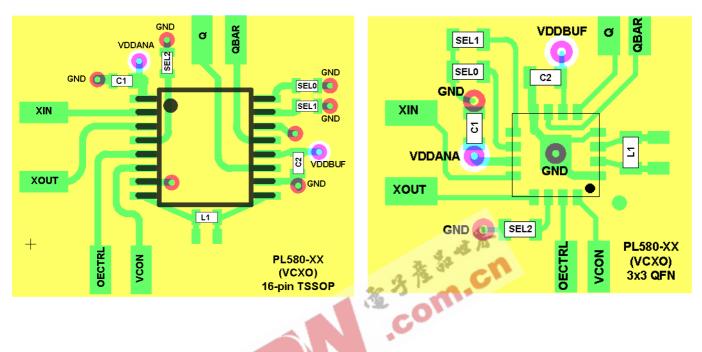

- Available in 3x3 QFN or 16-pin TSSOP packages.

### DESCRIPTION

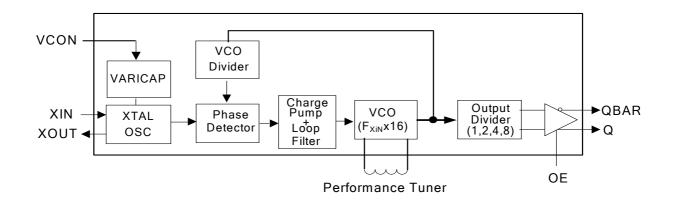

The PL580-3X is a monolithic low jitter and low phase noise VCXO, capable of 0.4ps RMS phase jitter and CMOS, LVDS, or PECL outputs, covering a wide frequency output range up to 320MHz. It allows the control of the output frequency with an input voltage (VCON), using a low cost crystal. The frequency selector pads of PL580-3X enable output frequencies of (2, 4, 8, or 16) \*  $F_{XIN}$ . The PL580-3X is designed to address the demanding requirements of high performance applications such as SONET, GPS, Video, etc.

### BLOCK DIAGRAM

#### <u>3x3 QFN</u>

Note1: QBAR is used for single ended CMOS output. Note2: ^ Denotes internal pull up resistor.

# $({\sf Preliminary}) PL580-35/37/38/39$

# 38MHz-320MHz Low Phase Noise VCXO

### **OUTPUT ENABLE LOGICAL LEVELS**

| Part #                             | OE          | State          |

|------------------------------------|-------------|----------------|

| PL580-38 (PECL)                    | 0 (Default) | Output enabled |

| FE300-38 (FEGE)                    | 1           | Tri-state      |

| PL580-35 (PECL)                    | 0           | Tri-state      |

| PL580-37 (CMOS)<br>PL580-39 (LVDS) | 1 (Default) | Output enabled |

### **PIN DESCRIPTIONS**

| Name    | TSSOP<br>Pin number | 3x3mm QFN<br>Pin number | Туре | Description                                                                                                                                          |

|---------|---------------------|-------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDANA  | 1                   | 11                      | Р    | VDD for analog Circuitry.                                                                                                                            |

| XIN     | 2                   | 12                      | I    | Crystal input pin. (See Crystal Specifications on page 4).                                                                                           |

| XOUT    | 3                   | 13                      | 0    | Crystal output pin. (See Crystal Specifications on page 4).                                                                                          |

| SEL2    | 4                   | 14                      | Ι    | Output frequency Selector pin.                                                                                                                       |

| OE_CTRL | 5                   | 15                      |      | Output enable control pin. (See OE_CTRL Logic Levels).                                                                                               |

| VCON    | 6                   | 16                      |      | Voltage control input.                                                                                                                               |

| GNDANA  | 7                   | 1                       | Р    | Ground for analog circuitry.                                                                                                                         |

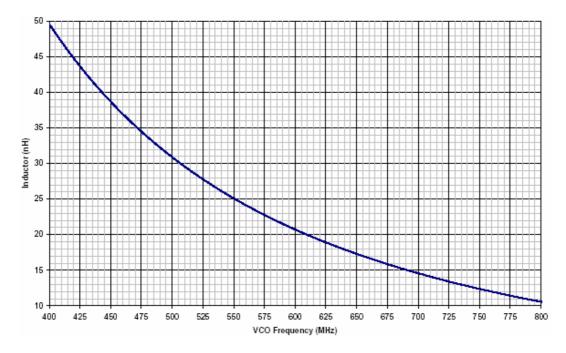

| LP      | 8                   | 2                       | -    | Tuning inductor connection. The inductor is recommended to be<br>a high Q small size 0402 or 0603 SMD component, and must be                         |

| LM      | 9                   | 3                       | -    | placed between LP and adjacent LM pin. Place inductor as close<br>to the IC as possible to minimize parasitic effects and to<br>maintain inductor Q. |

| GNDBUF  | 10                  | 4                       | Р    | GND connection for output buffer circuitry.                                                                                                          |

| Q       | 11                  | 5                       | 0    | PECL or LVDS output.                                                                                                                                 |

| VDDBUF  | 12                  | 6                       | Ρ    | VDD connection for output buffer circuitry. VDDBUF should be separately decoupled from other VDDs whenever possible.                                 |

| QBAR    | 13                  | 7                       | 0    | Complementary PECL, LVDS, Or single ended CMOS output.                                                                                               |

| GNDBUF  | 14                  | 8                       | Р    | GND connection for output buffer circuitry.                                                                                                          |

| SEL1    | 15                  | 9                       |      | Output frequency Selector pin.                                                                                                                       |

| SEL0    | 16                  | 10                      |      | Output frequency Selector pin.                                                                                                                       |

# $({\sf Preliminary}) PL580-35/37/38/39$

38MHz-320MHz Low Phase Noise VCXO

### FREQUENCY SELECTION TABLE

| SEL2 | SEL1 | SEL0 | Selected Multiplier/Output Frequency |

|------|------|------|--------------------------------------|

| 0    | 0    | 0    | VCO Max*                             |

| 0    | 0    | 1    | VCO Min*                             |

| 0    | 1    | 0    | Reserved                             |

| 0    | 1    | 1    | Reserved                             |

| 1    | 0    | 0    | Fin x 2                              |

| 1    | 0    | 1    | Fin x 8                              |

| 1    | 1    | 0    | Fin x 16                             |

| 1    | 1    | 1    | Fin x 4                              |

All SEL pads have internal pull-ups (default value is '1'). Bond to GND to set to 0.

\* Special Test Modes to help selecting the inductor value for the target output frequency.

### PERFORMANCE TUNING & INDUCTOR VALUE SELECTION

Please refer to PhaseLink's 'PhasorV Tuning Assistance' software to automatically calculate the optimum inductor values for your application. In addition, the chart below could be used as a reference for quick inductor value selection. Please note that the inductor values mentioned in the table below, or when using 'PhasorV Tuning Assistance' are derived based on the parasitic values of PhaseLink's evaluation board. For performance enhancement of your custom board design, please follow the following instruction:

Use the special test modes "VCO Max" and "VCO Min" to determine the optimum inductor value. "VCO Max" represents the high end of the VCO range and "VCO Min" represents the low end of the VCO range. The output frequency in the "VCO Max" and "VCO Min" test modes is VCO/16. This means that the output frequencies are around the crystal frequency that will be used. The optimum inductor value is where the target crystal frequency is closest to the middle between the "VCO Max" and "VCO Min" output frequencies. In this case the VCO will lock in the middle of its tuning range with maximum margin on either side.

# (Preliminary) PL580-35/37/38/39

### 38MHz-320MHz Low Phase Noise VCXO

### **ELECTRICAL SPECIFICATIONS** 1. Absolute Maximum Ratings

| PARAMETERS                        | SYMBOL          | MIN. | MAX.                 | UNITS |

|-----------------------------------|-----------------|------|----------------------|-------|

| Supply Voltage                    | V <sub>DD</sub> |      | 4.6                  | V     |

| Input Voltage, dc                 | Vi              | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Output Voltage, dc                | Vo              | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Storage Temperature               | Ts              | -65  | 150                  | °C    |

| Ambient Operating Temperature*    | TA              | -40  | 85                   | °C    |

| Junction Temperature              | TJ              |      | 125                  | °C    |

| Lead Temperature (soldering, 10s) |                 |      | 260                  | °C    |

| ESD Protection, Human Body Model  |                 |      | 2                    | kV    |

Exposure of the device under conditions beyond the limits specified by Maximum Ratings for extended periods may cause permanent damage to the device and affect product reliability. These conditions represent a stress rating only, and functional operations of the device at these or any other conditions above the operational limits noted in this specification is not implied.

\* Note: Operating Temperature is guaranteed by design for all parts (COMMERCIAL and INDUSTRIAL), but tested for COMMERCIAL grade only. 海方巷

#### 2. Crystal Specifications

| PARAMETERS                  | SYMBOL                                | CONDITIONS                | MIN. | TYP. | MAX. | UNITS |

|-----------------------------|---------------------------------------|---------------------------|------|------|------|-------|

| Crystal Resonator Frequency | Fxin                                  | Parallel Fundamental Mode | 19   |      | 40   | MHz   |

|                             |                                       | at VCON = 0V              |      | 17.7 |      |       |

| Crystal Loading Rating      | C <sub>L</sub> (xtal)                 | at VCON = 1.65V           |      | 9.5  |      | pF    |

|                             |                                       | at VCON = 3.3V            |      | 5.4  |      |       |

| Crystal Pullability         | C <sub>0</sub> /C <sub>1 (xtal)</sub> | AT cut                    |      |      | 250  | -     |

| Recommended ESR             | RE                                    | AT cut                    |      |      | 30   | Ω     |

Note: Crystal Loading rating: The listed numbers are for the IC only. Specify the crystal for the value at VCON = 1.65V and add the PCB & package parasitic. A round number (i.e. 12pF) can be achieved by adding external capacitors. Try to add the same value to XIN and XOUT, and please note, that frequency pulling and oscillator gain may decrease.

#### 3. Voltage Control Crystal Oscillator

| PARAMETERS                 | SYMBOL   | CONDITIONS                                                                                                                                             | MIN. | TYP. | MAX. | UNITS |

|----------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| VCXO Stabilization Time *  | Тусховтв | From power valid                                                                                                                                       |      |      | 10   | ms    |

| VCXO Tuning Range          |          | $\begin{array}{l} {\sf F}_{XIN} = 19 - 40 {\sf MHz}; \\ {\sf XTAL} \ {\sf C}_0/{\sf C}_1 < 250 \\ {\sf 0V} \le {\sf VCON} \le 3.3 {\sf V} \end{array}$ |      | 500  |      | ppm   |

| CLK output pullability     |          | VCON=1.65V, ±1.65V                                                                                                                                     | ±200 |      |      | ppm   |

| VCXO Tuning Characteristic |          |                                                                                                                                                        |      | 150  |      | ppm/V |

| Pull range linearity       |          |                                                                                                                                                        |      |      | 10   | %     |

| VCON pin input impedance   |          |                                                                                                                                                        | 60   | 80   |      | kΩ    |

| VCON modulation BW         |          | $0V \le VCON \le 3.3V, -3dB$                                                                                                                           | 25   |      |      | kHz   |

Note: Parameters denoted with an asterisk (\*) represent nominal characterization data and are not production tested to any specific limits.

# 38MHz-320MHz Low Phase Noise VCXO

£....

#### 4. General Electrical Specifications

| PARAMETERS                       | SYMBOL          | CON                                                                                                            | MIN.                                                                                     | TYP.           | MAX.           | UNITS          |    |

|----------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------|----------------|----------------|----|

| Supply Current,<br>Dynamic (with | IDD             | PECL/LVDS/CMOS                                                                                                 | 38MHz <fout<100mhz< td=""><td></td><td></td><td>65/45/30</td><td>mA</td></fout<100mhz<>  |                |                | 65/45/30       | mA |

| Loaded Outputs)                  | עטו             |                                                                                                                | 100MHz <fout<320mhz< td=""><td></td><td></td><td>80/60/40</td><td>ША</td></fout<320mhz<> |                |                | 80/60/40       | ША |

| Operating Voltage                | $V_{\text{DD}}$ |                                                                                                                |                                                                                          | 2.97           |                | 3.63           | V  |

| Output Clock<br>Duty Cycle       |                 | <ul> <li>@ 50% V<sub>DD</sub> (CMOS)</li> <li>@ 1.25V (LVDS)</li> <li>@ V<sub>DD</sub> - 1.3V (PECL</li> </ul> | )                                                                                        | 45<br>45<br>45 | 50<br>50<br>50 | 55<br>55<br>55 | %  |

| Short Circuit<br>Current         |                 |                                                                                                                |                                                                                          |                | ±50            |                | mA |

Note: CMOS operation is not advised above 200MHz with 15pF load; and 320MHz with 10pF load.

#### 5. Jitter Specifications

|                                |                               |           | L P  |      |      |       |

|--------------------------------|-------------------------------|-----------|------|------|------|-------|

| PARAMETERS                     | CONDITIONS                    | FREQUENCY | MIN. | TYP. | MAX. | UNITS |

| Integrated jitter RMS          | Integrated 12 kHz to 20 MHz 🚄 | 155.52MHz |      | 0.4  | 0.5  | 20    |

| Integrated jitter Kino         |                               | 311.04MHz |      | 0.4  | 0.5  | ps    |

|                                | With capacitive decoupling    | 77.76MHz  |      | 2.5  | 4    |       |

| Period jitter RMS              | between VDD and GND.          | 155.52MHz |      | 3    | 5    | ps    |

|                                | Over 10,000 cycles.           | 311.04MHz |      | 4    | 7    |       |

|                                | With capacitive decoupling    | 77.76MHz  |      | 18   | 30   |       |

| Period jitter Peak-to-<br>Peak | between VDD and GND.          | 155.52MHz |      | 20   | 30   | ps    |

|                                | Over 10,000 cycles.           | 311.04MHz |      | 25   | 35   |       |

### 6. Phase Noise Specifications

| PARAMETERS        | FREQ.     | @10Hz | @100Hz | @1kHz | @10kHz | @100kHz | @1M  | @10M | UNITS  |

|-------------------|-----------|-------|--------|-------|--------|---------|------|------|--------|

| Phase Noise       | 77.76MHz  | -66   | -96    | -124  | -134   | -132    | -145 | -149 |        |

| relative to       | 155.52MHz | -62   | -92    | -120  | -132   | -128    | -144 | -150 | dBc/Hz |

| carrier (typical) | 311.04MHz | -59   | -86    | -116  | -129   | -124    | -140 | -148 |        |

Note: Phase Noise measured at VCON = 0V.

### 7. CMOS Electrical Characteristics

| PARAMETERS                  | SYMBOL | CONDITIONS                              | MIN. | TYP. | MAX. | UNITS |

|-----------------------------|--------|-----------------------------------------|------|------|------|-------|

| Output drive current        | Іон    | $V_{OH} = V_{DD} - 0.4V, V_{DD} = 3.3V$ | 30   |      |      | mA    |

|                             | Iol    | $V_{OL} = 0.4V, V_{DD} = 3.3V$          | 30   |      |      | mA    |

| Output Clock Rise/Fall Time |        | 0.3V ~ 3.0V with 15 pF load             |      | 0.7  |      | ns    |

| Output Clock Rise/Fall Time |        | 20%-80% with 50 $\Omega$ Load           |      | 0.3  |      | ns    |

# (Preliminary) PL580-35/37/38/39

### 38MHz-320MHz Low Phase Noise VCXO

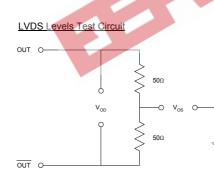

### 8. LVDS Electrical Characteristics

| PARAMETERS                       | SYMBOL                | CONDITIONS                                          | MIN.  | TYP. | MAX.  | UNITS |

|----------------------------------|-----------------------|-----------------------------------------------------|-------|------|-------|-------|

| Output Differential Voltage      | Vod                   |                                                     | 247   | 355  | 454   | mV    |

| V <sub>DD</sub> Magnitude Change | $\Delta V_{	ext{OD}}$ | -                                                   | -50   |      | 50    | mV    |

| Output High Voltage              | Vон                   | R <sub>L</sub> = 100 Ω                              |       | 1.4  | 1.6   | V     |

| Output Low Voltage               | Vol                   | (see figure)                                        | 0.9   | 1.1  |       | V     |

| Offset Voltage                   | Vos                   |                                                     | 1.125 | 1.2  | 1.375 | V     |

| Offset Magnitude Change          | $\Delta V$ os         |                                                     | 0     | 3    | 25    | mV    |

| Power-off Leakage                | Іохо                  | $V_{out} = V_{DD} \text{ or } GND$<br>$V_{DD} = 0V$ |       | ±1   | ±10   | uA    |

| Output Short Circuit Current     | Iosd                  | × 3 12 3                                            | -     | -5.7 | -8    | mA    |

| 9. LVDS Switching Characte       |                       |                                                     |       |      |       |       |

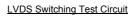

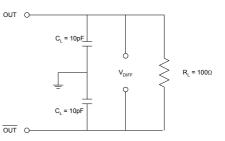

### 9. LVDS Switching Characteristics

| PARAMETERS                   | SYMBOL | CONDITIONS                             | MIN. | TYP. | MAX. | UNITS |

|------------------------------|--------|----------------------------------------|------|------|------|-------|

| Differential Clock Rise Time | tr     | $R_{L} = 100 \Omega$                   | 0.2  | 0.7  | 1.0  | ns    |

| Differential Clock Fall Time | tf     | C <sub>L</sub> = 10 pF<br>(see figure) | 0.2  | 0.7  | 1.0  | ns    |

#### LVDS Transistion Time Waveform

### 38MHz-320MHz Low Phase Noise VCXO

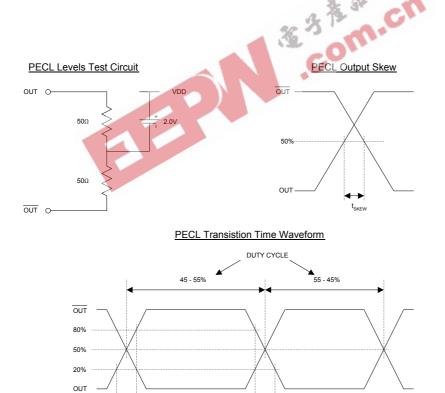

### **10. PECL Electrical Characteristics**

| PARAMETERS          | SYMBOL | CONDITIONS                           | MIN.                    | MAX.                    | UNITS |

|---------------------|--------|--------------------------------------|-------------------------|-------------------------|-------|

| Output High Voltage | Vон    | $R_L = 50 \Omega$ to $(V_{DD} - 2V)$ | V <sub>DD</sub> - 1.025 |                         | V     |

| Output Low Voltage  | Vol    | (see figure)                         |                         | V <sub>DD</sub> - 1.620 | V     |

### **11. PECL Switching Characteristics**

| PARAMETERS              | SYMBOL  | FREQ.              | CONDITIONS     | MIN. | TYP. | MAX. | UNITS |

|-------------------------|---------|--------------------|----------------|------|------|------|-------|

| Clock Rise & Fall Times | + - +-  | <150MHz            | @20/80% - PECL | 0.2  | 0.5  | 0.7  | 20    |

| Clock Rise & Fall Times | tr & tf | >150MHz<br><320MHz | @80/20% - PECL | 0.2  | 0.4  | 0.55 | ns    |

**€**

### 38MHz-320MHz Low Phase Noise VCXO

### LAYOUT RECOMMENDATIONS

### PCB LAYOUT CONSIDERATIONS FOR PERFORMANCE OPTIMIZATION

The following guidelines are to assist you with a performance optimized PCB design:

- Keep all the PCB traces to PL580 as short as possible, as well as keeping all other traces as far away from it as possible.

- Place the crystal as close as possible to both crystal pins of the device. This will reduce the cross-talk between the crystal and the other signals.

- Separate crystal pin traces from the other signals on the PCB, but allow ample distance between the two crystal pin traces.

- Place a 0.01µF~0.1µF decoupling capacitor between VDD and GND, on the component side of the PCB, close to the VDD pin. It is not recommended to place this component on the backside of the PCB. Going through vias will reduce the signal integrity, causing additional jitter and phase noise.

- It is highly recommended to keep the VDD and GND traces as short as possible.

- When connecting long traces (> 1 inch) to a CMOS output, it is important to design the traces as a transmission line or 'stripline', to avoid reflections or ringing. In this case, the CMOS output needs to be matched to the trace impedance. Usually 'striplines' are designed for  $50\Omega$  impedance and CMOS outputs usually have lower than  $50\Omega$  impedance so matching can be achieved by adding a resistor in series with the CMOS output pin to the 'stripline' trace.

- Please contact PhaseLink for the application note on how to design outputs driving long traces or the Gerber files for the PL580 layout.

### 38MHz-320MHz Low Phase Noise VCXO

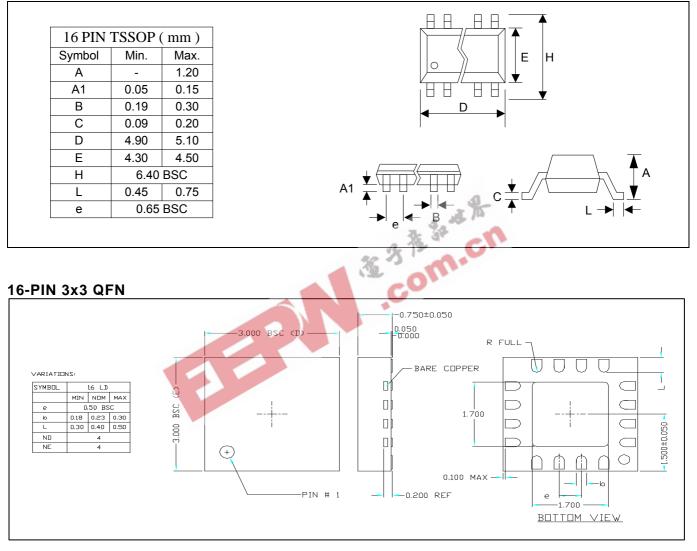

#### **PACKAGE INFORMATION**

#### **16-PIN SSOP**

# 38MHz-320MHz Low Phase Noise VCXO

### **ORDERING INFORMATION**

|                                  | t <i>ordering, please con</i><br>47745 Fremont Blvd., Fre<br>Tel: (510) 492-0990 F |                                                                                      |

|----------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|                                  |                                                                                    | <i>IMBER</i><br>s a combination of the following:<br>d Operating temperature range   |

| PART NU                          | <u>PL580-3X</u><br>MBER                                                            | X C L R<br>R= TAPE & REEL<br>NONE= TUBE<br>L= GREEN PACKAGE<br>NONE= REGULAR PACKAGE |

| PACKAGE<br>O=TSSOP-<br>Q= QFN-16 | 16L                                                                                | TEMPERATURE<br>C=COMMERCIAL<br>I=INDUSTRAL                                           |

| Order Number                     | Marking 📹                                                                          | Package Option                                                                       |

| PL580-35OCL                      | P580-350CL                                                                         | TSSOP - Tube (GREEN Package)                                                         |

| PL580-350CL-R                    | P580-35OCL                                                                         | TSSOP - Tape & Reel (GREEN Package)                                                  |

| PL580-35QCL                      | P580-35QCL                                                                         | QFN - Tube (GREEN Package)                                                           |

| PL580-35QCL-R                    | P580-35QCL                                                                         | QFN - Tape & Reel (GREEN Package)                                                    |

| PL580-370CL                      | P580-370CL                                                                         | TSSOP - Tube (GREEN Package)                                                         |

| PL580-37OCL-R                    | P580-370CL                                                                         | TSSOP - Tape & Reel (GREEN Package)                                                  |

| PL580-37QCL                      | P580-37QCL                                                                         | QFN - Tube (GREEN Package)                                                           |

| PL580-37QCL-R                    | P580-37QCL                                                                         | QFN - Tape & Reel (GREEN Package)                                                    |

| PL580-380CL                      | P580-380CL                                                                         | TSSOP - Tube (GREEN Package)                                                         |

| PL580-380CL-R                    | P580-38OCL                                                                         | TSSOP - Tape & Reel (GREEN Package)                                                  |

| PL580-38QCL                      | P580-38QCL                                                                         | QFN - Tube (GREEN Package)                                                           |

| PL580-38QCL-R                    | P580-38QCL                                                                         | QFN - Tape & Reel (GREEN Package)                                                    |

| PL580-39OCL                      | P580-39OCL                                                                         | TSSOP - Tube (GREEN Package)                                                         |

| PL580-39OCL-R                    | P580-39OCL                                                                         | TSSOP - Tape & Reel (GREEN Package)                                                  |

| PL580-39QCL                      | P580-39QCL                                                                         | QFN - Tube (GREEN Package)                                                           |

| PL580-39QCL-R                    | P580-39QCL                                                                         | QFN - Tape & Reel (GREEN Package)                                                    |

PhaseLink Corporation, reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by Phaselink is believed to be accurate and reliable. However, PhaseLink makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product. LIFE SUPPORT POLICY: PhaseLink's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of PhaseLink Corporation.