## **VOLTAGE DETECTOR**

#### **FEATURES**

- Precise Detection Thresholds .... Standard ± 2.0% Custom ± 1.0%

- Small Packages ......SOT-23A-3, SOT-89, TO-92

- Low Current Drain ......Typ. 1µA

- Wide Detection Range .......2.1V to 6.0V

- Wide Operating Voltage Range ......1.5V to 10V

## **APPLICATIONS**

- Battery Voltage Monitoring

- Microprocessor Reset

- System Brownout Protection

- Switching Circuit in Battery Backup

- Level Discriminator

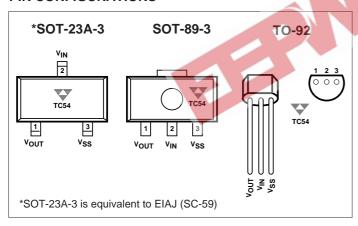

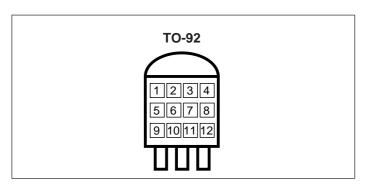

#### **PIN CONFIGURATIONS**

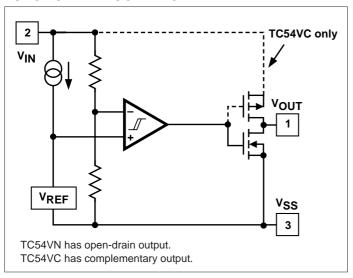

### **FUNCTIONAL BLOCK DIAGRAM**

## **GENERAL DESCRIPTION**

The TC54 Series are CMOS voltage detectors, suited especially for battery-powered applications because of their extremely low  $1\mu A$  operating current and small surface-mount packaging. Each part is laser trimmed to the desired threshold voltage which can be specified from 2.1V to 6.0V, in 0.1V steps.

The device includes a comparator, low-current high-precision reference, laser-trimmed divider, hysteresis circuit and output driver. The TC54 is available with either an opendrain or complementary output stage.

In operation, the TC54's output ( $V_{OUT}$ ) remains in the logic HIGH state as long as  $V_{IN}$  is greater than the specified threshold voltage ( $V_{DET}$ ). When  $V_{IN}$  falls below  $V_{DET}$ , the output is driven to a logic LOW.  $V_{OUT}$  remains LOW until  $V_{IN}$  rises above  $V_{DET}$  by an amount  $V_{HYST}$ , whereupon it resets to a logic HIGH.

#### ORDERING INFORMATION

# PART CODE TC54 V X XX X X X XXXXXXX Output form: N = Nch Open Drain C = CMOS Output Detected Voltage: Ex: 21 = 2.1V; 60 = 6.0V

Extra Feature Code: Fixed: 0

Tolerance:  $1 = \pm 1.0\%$  (custom)  $2 = \pm 2.0\%$  (standard)

**Temperature:** E: – 40°C to + 85°C

Package Type and Pin Count:

CB: SOT-23A-3\*, MB: SOT-89-3, ZB: TO-92-3

### **Taping Direction:**

Standard Taping Reverse Taping No suffix: TO-92 Bulk

\*SOT-23A-3 is equivalent to EIAJ (SC-59).

# **VOLTAGE DETECTOR**

# **TC54**

## **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage (V <sub>IN)</sub> 1                        | 2V  |

|-----------------------------------------------------------|-----|

| Output Voltage: CMOS $(V_{SS} - 0.3)$ to $(V_{IN} + 0.3)$ |     |

| Open Drain (V <sub>SS</sub> – 0.3) to 1                   | 2V  |

| Output Current50                                          | mΑ  |

| Power Dissipation: $(T_A \le 70^{\circ}C)$                |     |

| SOT-23A-3240n                                             | nW  |

| SOT-89-3400n                                              | nW  |

| TO-92440n                                                 | nW  |

| Operating Temperature – 40°C to + 85                      | 5°C |

| Storage Temperature – 65°C to + 150                       | )°C |

| Soldering Temperature 300°C, 10 secon                     | nds |

\* Static-sensitive device. Unused devices must be stored in conductive material. Protect devices from static discharge and static fields. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to Absolute Maximum Rating Conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS:** $T_A = 25$ °C, unless otherwise specified.

| Symbol                             | Parameter                     | <b>Test Conditions</b>                   | 76 30           | Min                 | Тур                 | Max                 | Unit   |

|------------------------------------|-------------------------------|------------------------------------------|-----------------|---------------------|---------------------|---------------------|--------|

| V <sub>IN</sub>                    | Operating Voltage             | $V_{DET} = 2.1 \text{ to } 6.0 \text{V}$ | 537             | 1.5                 |                     | 10.0                | V      |

| I <sub>SS</sub>                    | Quiescent Current             |                                          | J. 011          |                     | 1.0                 | 3.0                 |        |

|                                    |                               | 3.0V                                     | C               |                     | 1.3                 | 3.4                 | μΑ     |

|                                    |                               | 4. <b>0</b> V                            |                 |                     | 1.6                 | 3.8                 |        |

| ·-                                 |                               | 5.0V                                     |                 |                     | 2.0                 | 4.2                 |        |

| $V_{DET}$                          | Threshold Voltage             |                                          |                 | (V <sub>DET</sub> ) |                     | (V <sub>DET</sub> ) | V      |

|                                    |                               |                                          |                 | x 0.98              |                     | x 1.02              |        |

| $V_{HYST}$                         | Hysteresis Range              |                                          |                 | (V <sub>DET</sub> ) | (V <sub>DET</sub> ) | (V <sub>DET</sub> ) | V      |

|                                    |                               |                                          |                 | x 0.02              | x 0.05              | x 0.08              |        |

| I <sub>OUT</sub>                   | Output Current                | Nch V <sub>DS</sub> = 0.5                | $V_{IN} = 2.1V$ |                     | 7.7                 |                     | mA     |

|                                    |                               |                                          | 3.0V            |                     | 10.1                |                     |        |

|                                    |                               |                                          | 4.0V            |                     | 11.5                |                     |        |

|                                    |                               |                                          | 5.0V            |                     | 13.0                |                     |        |

|                                    |                               | Pch $V_{DS} = 2.1V$                      | $V_{IN} = 8.0V$ |                     | - 10.0              |                     |        |

| T <sub>C</sub> (V <sub>DET</sub> ) | Tempco of (V <sub>DET</sub> ) | $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ |                 |                     | ± 100               |                     | ppm/°C |

## **PIN DESCRIPTION**

| Pin No. | Symbol           | Description                                                                                                                                                                            |

|---------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>IN</sub>  | Analog input. This pin is both the power supply input and the voltage to be monitored.                                                                                                 |

| 2       | V <sub>OUT</sub> | Digital output. This output goes low when $V_{IN}$ drops below $V_{\overline{D}ET}$ and returns high when $V_{IN}$ rises above $V_{\overline{D}ET}$ + $V_{HYST}$ . (See timing chart). |

| 3       | V <sub>SS</sub>  | Ground terminal.                                                                                                                                                                       |

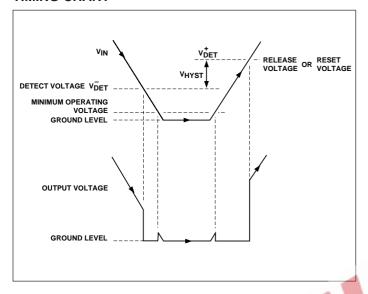

#### **TIMING CHART**

## **DESCRIPTION OF OPERATION**

Refer to the Timing Chart below. In normal steady-state operation, when  $V_{\text{IN}} > V_{\text{DET}}^-$ , the output will be at a logic high. In the case of the TC54V, this is an open-drain condition. If and when the input falls below  $V_{\text{DET}}^-$ , the output will pull down (Logic 0) to  $V_{\text{SS}}$ . Generally,  $V_{\text{OUT}}$  can pull down to within 0.5V of  $V_{\text{SS}}$  at rated output current and input voltage. (See the Electrical Characteristics section).

The output, V<sub>OUT</sub>, will stay valid until the input voltage falls below the Minimum Operating Voltage, V<sub>IN</sub>(MIN), of 1.5V. Below this minimum operating voltage, the output is undefined. During power-up or anytime V<sub>IN</sub> has fallen below V<sub>IN</sub> (MIN), V<sub>OUT</sub> will remain undefined until V<sub>IN</sub> rises above V<sub>IN</sub>(MIN), at which time the output will become valid. V<sub>OUT</sub> will be in its active low state while V<sub>IN</sub>(MIN) < V<sub>IN</sub> < V<sup>+</sup><sub>DET</sub>. (V<sup>+</sup><sub>DET</sub> = V<sup>-</sup><sub>DET</sub> + V<sub>HYST</sub>). If and when the input rises above V<sup>+</sup><sub>DET</sub>, the output will assume its inactive state. (High for TC54VC, open-drain for TC54VN).

## **APPLICATIONS**

Refer to TelCom Semiconductor Application Note #2, Using the TC54 Voltage Detector.

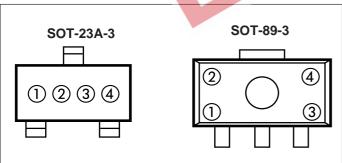

### **MARKING**

① = output (Nch or CMOS) plus first voltage digit

2 3 4 5 6 M N P R S

Nch M N P R S CMOS C D E F H

ex: CMOS 3.x = (D)()()

2 = first voltage decimal (0-9)

ex: CMOS 3.4 = (D)(4)()()

3 & 4 = assembly lot number

- ①, ② & ③ = 54\_ (fixed)

- (4) = output (C = CMOS, N = Nch)

- (5) = first voltage digit (2-6)

- 6 = first voltage decimal (0-9)

- (7) = extra feature code : fixed : 0

- (8) = detecting accuracy

$1 = \pm 1.0\%$  (custom),  $2 = \pm 2.0\%$  (standard)

(9), (10), (11) & (12) = assembly lot number