SLVS086B - APRIL 1995 - REVISED NOVEMBER 1997

- Two Complete PWM Control Circuits

- Outputs Drive MOSFETs Directly

- Oscillator Frequency . . . 50 kHz to 2 MHz

- 3.6-V to 20-V Supply-Voltage Range

- Low Supply Current . . . 3.5 mA Typ

- Adjustable Dead-Time Control, 0% to 100%

- 1.25-V Reference

# description

The TL1454 is a dual-channel pulse-width-modulation (PWM) control circuit, primarily intended for low-power, dc/dc converters. Applications include LCD displays, backlight inverters, notebook com-

puters, and other products requiring small, high-frequency, dc/dc converters. Each PWM channel has its own error amplifier, PWM comparator, dead-time control comparator, and MOSFET driver. The voltage reference, oscillator, undervoltage lockout, and short-circuit protection are common to both channels.

Channel 1 is configured to drive n-channel MOSFETs in step-up or flyback converters, and channel 2 is configured to drive p-channel MOSFETs in step-down or inverting converters. The operating frequency is set with an external resistor and an external capacitor, and dead time is continuously adjustable from 0 to 100% duty cycle with a resistive divider network. Soft start can be implemented by adding a capacitor to the dead-time control (DTC) network. The error-amplifier common-mode input range includes ground, which allows the TL1454 to be used in ground-sensing battery chargers as well as voltage converters.

# AVAILABLE OPTIONS

|               | P                 | ACKAGED DEVICEST   |               | CHIP FORM |

|---------------|-------------------|--------------------|---------------|-----------|

| TA            | SMALL OUTLINE (D) | PLASTIC DIP<br>(N) | TSSOP<br>(PW) | (Y)       |

| -20°C to 85°C | TL1454CD          | TL1454CN           | TL1454CPWLE   | TL1454Y   |

| −40°C to 85°C | TL1454ID          | TL1454IN           |               | _         |

<sup>†</sup> The D package is available taped and reeled. Add the suffix R to the device name (e.g., TL1454CDR). The PW package is available only left-end taped and reeled (indicated by the LE suffix on the device type; e.g., TL1454CPWLE).

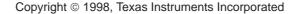

D, N OR PW PACKAGE

1

SLVS086B - APRIL 1995 - REVISED NOVEMBER 1997

### functional block diagram **VCC** RT CT |10 2 | 1 16 REF 1.25 V Voltage 1.8 V REF 2.5 V To Internal Circuitry GND 7 1.2 V VCC osc **PWM** COMP1 Comparator 1 IN1 + 4 8 OUT1 IN1-Error **Amplifier 1** PWM COMP2 11 Comparator 2 IN2+ 13 **VCC** IN2-Error Amplifier 2 UVLO 9 OUT2 and SCP Latch SCP Comparator 2 0.65 V 0.65 V SCP Comparator 1 1.25 V 15 3 14 SCP DTC1 DTC2

SLVS086B - APRIL 1995 - REVISED NOVEMBER 1997

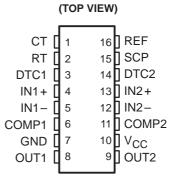

# **TL1454Y chip information**

This chip, when properly assembled, displays characteristics similar to the TL1454C. Thermal compression or ultrasonic bonding may be used on the doped aluminum bonding pads. The chips may be mounted with conductive epoxy or a gold-silicon preform.

SLVS086B - APRIL 1995 - REVISED NOVEMBER 1997

# theory of operation

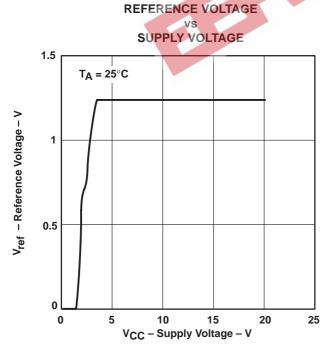

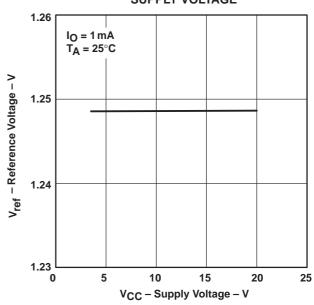

# reference voltage

A linear regulator operating from  $V_{CC}$  generates a 2.5-V supply for the internal circuits and the 1.25-V reference, which can source a maximum of 1 mA for external loads. A small ceramic capacitor (0.047  $\mu$ F to 0.1  $\mu$ F) between REF and ground is recommended to minimize noise pickup.

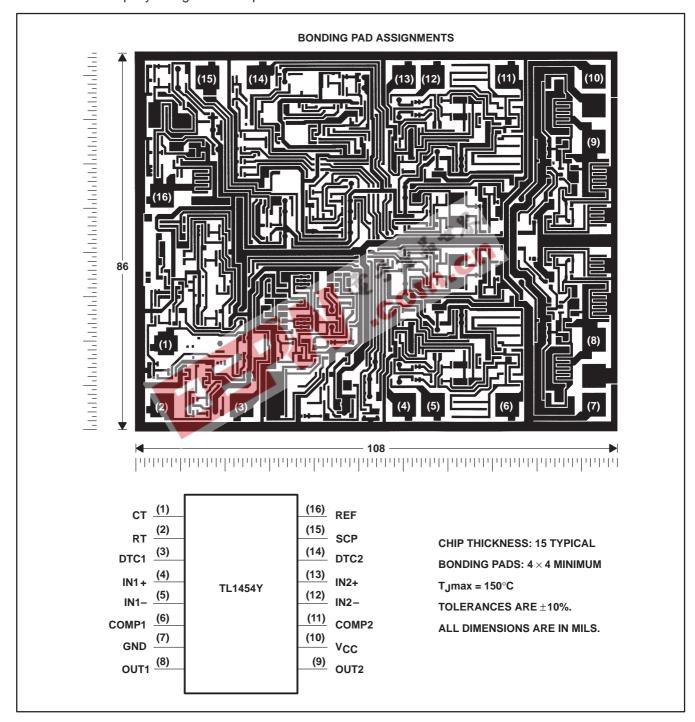

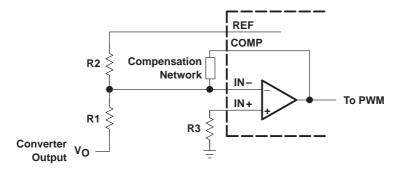

# error amplifier

The error amplifier generates the error signal used by the PWM to adjust the power-switch duty cycle for the desired converter output voltage. The signal is generated by comparing a sample of the output voltage to the voltage reference and amplifying the difference. An external resistive divider connected between the converter output and ground, as shown in Figure 1, is generally required to obtain the output voltage sample.

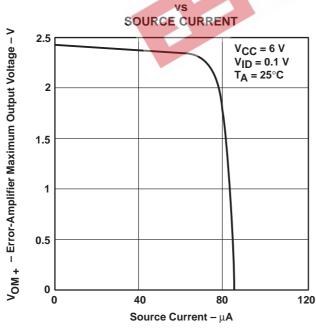

The amplifier output is brought out on COMP to allow the frequency response of the amplifier to be shaped with an external RC network to stabilize the feedback loop of the converter. DC loading on the COMP output is limited to  $45 \,\mu\text{A}$  (the maximum amplifier source current capability).

Figure 1 illustrates the sense-divider network and error-amplifier connections for converters with positive output voltages. The divider network is connected to the noninverting amplifier input because the PWM has a phase inversion; the duty cycle decreases as the error-amplifier output increases.

Figure 1. Sense Divider/Error Amplifier

Configuration for Converters with Positive Outputs

The output voltage is given by:

$$V_{O} = V_{ref} \left( 1 + \frac{R1}{R2} \right)$$

where  $V_{ref} = 1.25 \text{ V}$ .

The dc source resistance of the error-amplifier inputs should be 10 k $\Omega$  or less and approximately matched to minimize output voltage errors caused by the input-bias current. A simple procedure for determining appropriate values for the resistors is to choose a convenient value for R3 (10 k $\Omega$  or less) and calculate R1 and R2 using:

$$R_1 = \frac{R_3 V_0}{V_0 - V_{ref}}$$

$$R_2 = \frac{R_3 V_0}{V_{ref}}$$

SLVS086B - APRIL 1995 - REVISED NOVEMBER 1997

### error amplifier

R1 and R2 should be tight-tolerance ( $\pm 1\%$  or better) devices with low and/or matched temperature coefficients to minimize output voltage errors. A device with a  $\pm 5\%$  tolerance is suitable for R3.

Figure 2. Sense Divider/Error Amplifier Configuration for Converters with Negative Outputs

Figure 2 shows the divider network and error-amplifier configuration for negative output voltages. In general, the comments for positive output voltages also apply for negative outputs. The output voltage is given by:

$$V_{O} = -\frac{R_{1}V_{ref}}{R_{2}}$$

The design procedure for choosing the resistor value is to select a convenient value for R2 (instead of R3 in the procedure for positive outputs) and calculate R1 and R3 using:

$$R_1 = -\frac{R_2 V_0}{V_{ref}}$$

$$R_3 = \frac{R_1 R_2}{R_1 + R_2}$$

Values in the  $10-k\Omega$  to  $20-k\Omega$  range work well for R2. R3 can be omitted and the noninverting amplifier connected to ground in applications where the output voltage tolerance is not critical.

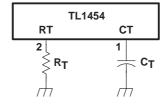

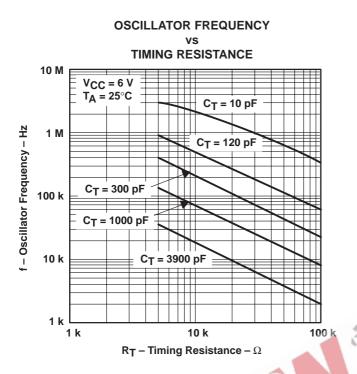

### oscillator

The oscillator frequency can be set between 50 kHz and 2 MHz with a resistor connected between RT and GND and a capacitor between CT and GND (see Figure 3). Figure 6 is used to determine  $R_T$  and  $C_T$  for the desired operating frequency. Both components should be tight-tolerance, temperature-stable devices to minimize frequency deviation. A 1% metal-film resistor is recommended for  $R_T$ , and a 10%, or better, NPO ceramic capacitor is recommended for  $C_T$ .

Figure 3. Oscillator Timing

SLVS086B - APRIL 1995 - REVISED NOVEMBER 1997

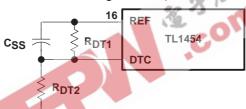

## dead-time control (DTC) and soft start

The two PWM channels have independent dead-time control inputs so that the maximum power-switch duty cycles can be limited to less then 100%. The dead-time is set with a voltage applied to DTC; the voltage is typically obtained from a resistive divider connected between the reference and ground as shown in Figure 4. Soft start is implemented by adding a capacitor between REF and DTC.

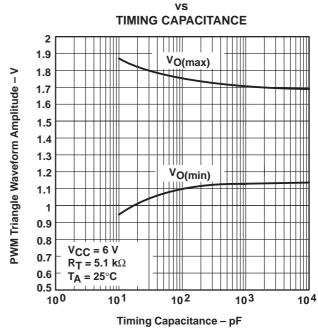

The voltage, V<sub>DT</sub>, required to limit the duty cycle to a maximum value is given by:

$$V_{DT} = V_{O(max)} - D(V_{O(max)} - V_{O(min)}) - 0.65$$

where  $V_{O(max)}$  and  $V_{O(min)}$  are obtained from Figure 9, and D is the maximum duty cycle.

Predicting the regulator startup or rise time is complicated because it depends on many variables, including: input voltage, output voltage, filter values, converter topology, and operating frequency. In general, the output will be in regulation within two time constants of the soft-start circuit. A five-to-ten millisecond time constant usually works well for low-power converters.

The DTC input can be grounded in applications where achieving a 100% duty cycle is desirable, such as a buck converter with a very low input-to-output differential voltage. However, grounding DTC prevents the implementation of soft start, and the output voltage overshoot at power-on is likely to be very large. A better arrangement is to omit  $R_{DT1}$  (see Figure 4) and choose  $R_{DT2} = 47 \, \mathrm{k}\Omega$ . This configuration ensures that the duty cycle can reach 100% and still allows the designer to implement soft start using  $C_{SS}$ .

Figure 4. Dead-Time Control and Soft Start

### **PWM** comparator

Each of the PWM comparators has dual inverting inputs. One inverting input is connected to the output of the error amplifier; the other inverting input is connected to the DTC terminal. Under normal operating conditions, when either the error-amplifier output or the dead-time control voltage is higher than that for the PWM triangle wave, the output stage is set inactive (OUT1 low and OUT2 high), turning the external power stage off.

# undervoltage-lockout (UVLO) protection

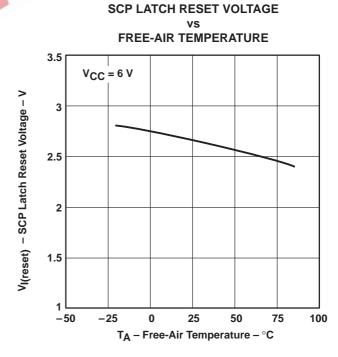

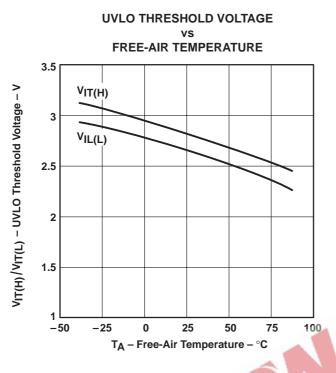

The undervoltage-lockout circuit turns the output circuit off and resets the SCP latch whenever the supply voltage drops too low (to approximately 2.9 V) for proper operation. A hysteresis voltage of 200 mV eliminates false triggering on noise and chattering.

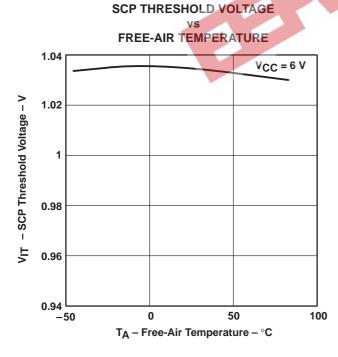

### short-circuit protection (SCP)

The TL1454 SCP function prevents damage to the power switches when the converter output is shorted to ground. In normal operation, SCP comparator 1 clamps SCP to approximately 185 mV. When one of the converter outputs is shorted, the error amplifier output (COMP) will be driven below 1 V to maximize duty cycle and force the converter output back up. When the error amplifier output drops below 1 V, SCP comparator 1 releases SCP, and capacitor,  $C_{SCP}$ , which is connected between SCP and GND, begins charging. If the error-amplifier output rises above 1 V before  $C_{SCP}$  is charged to 1 V, SCP comparator 1 discharges  $C_{SCP}$  and normal operation resumes. If  $C_{SCP}$  reaches 1 V, SCP comparator 2 turns on and sets the SCP latch, which turns off the output drives and resets the soft-start circuit. The latch remains set until the supply voltage is lowered to 2 V or less, or  $C_{SCP}$  is discharged externally.

SLVS086B - APRIL 1995 - REVISED NOVEMBER 1997

# short-circuit protection (SCP) (continued)

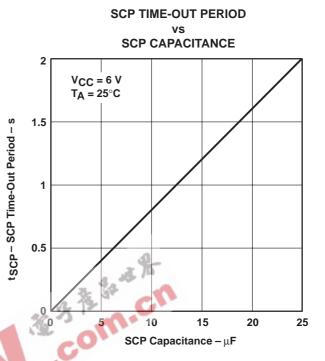

The SCP time-out period must be greater than the converter start-up time or the converter will not start. Because high-value capacitor tolerances tend to be  $\pm 20\%$  or more and IC resistor tolerances are loose as well, it is best to choose an SCP time-out period 10-to-15 times greater than the converter startup time. The value of  $C_{SCP}$  may be determined using Figure 6, or it can be calculated using:

$$C_{SCP} = \frac{T_{SCP}}{80.3}$$

where  $C_{SCP}$  is in  $\mu F$  and  $T_{SCP}$  is the time-out period in ms.

# output stage

The output stage of the TL1454 is a totem-pole output with a maximum source/sink current rating of 40 mA and a voltage rating of 20 V. The output is controlled by a complementary output AND gate and is turned on (sourcing current for OUT1, sinking current for OUT2) when all the following conditions are met: 1) the oscillator triangle wave voltage is higher than both the DTC voltage and the error-amplifier output voltage, 2) the undervoltage-lockout circuit is inactive, and 3) the short-circuit protection circuit is inactive.

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1)         | 23 V                         |

|------------------------------------------------------|------------------------------|

| Error amplifier input voltage: IN1+, IN1-, IN2+, IN2 |                              |

| Output voltage: OUT1, OUT2                           | 20 V                         |

| Continuous output current: OUT1, OUT2                | ±200 mA                      |

| Peak output current: OUT1, OUT2                      | 1 A                          |

| Continuous total dissipation                         | See Dissipation Rating Table |

| Operating free-air temperature range, TA: C suffix   | –20°C to 85°C                |

| I suffix                                             | 40°C to 85°C                 |

| Storage temperature range, T <sub>stq</sub>          | 65°C to 150°C                |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 | seconds 260°C                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to network GND.

# **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{\scriptsize A}} \le 25^{\circ}\mbox{\scriptsize C}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|----------------------------------------------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|

| D       | 950 mW                                                                     | 7.6 mW/°C                                      | 608 mW                                | 494 mW                                |

| N       | 1250 mW                                                                    | 10.0 mW/°C                                     | 800 mW                                | 650 mW                                |

| PW      | 500 mW                                                                     | 4.0 mW/°C                                      | 320 mW                                | 260 mW                                |

# TL1454, TL1454Y **DUAL-CHANNEL PULSE-WIDTH-MODULATION (PWM)** CONTROL CIRCUIT SLVS086B - APRIL 1995 - REVISED NOVEMBER 1997

# recommended operating conditions

|                                         |      |         | MIN  | MAX  | UNIT |

|-----------------------------------------|------|---------|------|------|------|

| Supply voltage, V <sub>CC</sub>         |      |         | 3.6  | 20   | V    |

| Error amplifier common-mode input volta | tage |         | -0.2 | 1.45 | V    |

| output voltage, VO                      |      |         | 20   | V    |      |

| Output current, IO                      |      |         |      | ±40  | mA   |

| COMP source current                     |      |         |      | -45  | μА   |

| COMP sink current                       |      |         |      | 100  | μА   |

| Reference output current                |      |         |      | 1    | mA   |

| COMP dc load resistance                 |      |         | 100  |      | kΩ   |

| Timing capacitor, C <sub>T</sub>        |      |         | 10   | 4000 | pF   |

| Timing resistor, R <sub>T</sub>         |      |         | 5.1  | 100  | kΩ   |

| Oscillator frequency                    |      |         | 50   | 2000 | kHz  |

| Operating free six temperature T.       | Т    | TL1454C | -20  | 85   | °C   |

| Operating free-air temperature, TA      | ī    | TL1454I | -40  | 85   | -0   |

electrical characteristics over recommended operating free-air temperature range,  $V_{CC}$  = 6 V,  $f_{osc}$  = 500 kHz (unless otherwise noted) reference

|                  | PARAMETER                              | TEST CONDITIONS                                                        |       | TL1454 |      | UNIT |

|------------------|----------------------------------------|------------------------------------------------------------------------|-------|--------|------|------|

|                  | PARAMETER                              | TEST CONDITIONS                                                        | MIN   | TYP    | MAX  | UNII |

| V .              | Output voltage, REF                    | $I_{O} = 1 \text{ mA}, 	 T_{A} = 25^{\circ}\text{C}$                   | 1.23  | 1.25   | 1.28 | V    |

| V <sub>ref</sub> | Output voltage, NEP                    | $I_O = 1 \text{ mA}$                                                   | 1.2   |        | 1.31 | V    |

|                  | Input regulation                       | $V_{OC} = 3.6 \text{ V to } 20 \text{ V}, \qquad I_{O} = 1 \text{ mA}$ |       | 2      | 6    | mV   |

|                  | Output regulation                      | I <sub>O</sub> = 0.1 mA to 1 mA                                        |       | 1      | 7.5  | mV   |

|                  | Output voltage change with temperature | $T_A = T_{A(min)}$ to 25°C, $I_O = 1$ mA                               | -12.5 | -1.25  | 12.5 | mV   |

|                  |                                        | $T_A = 25^{\circ}C \text{ to } 85^{\circ}C, \qquad I_O = 1 \text{ mA}$ | -12.5 | -2.5   | 12.5 | IIIV |

| los              | Short-circuit output current           | V <sub>ref</sub> = 0 V                                                 |       | 30     |      | mA   |

# undervoltage lockout (UVLO)

| PARAMETER        |                                                | TEST CONDITIONS       | •   | UNIT |     |      |

|------------------|------------------------------------------------|-----------------------|-----|------|-----|------|

|                  |                                                | TEST CONDITIONS       | MIN | TYP  | MAX | ONII |

| V <sub>IT+</sub> | Positive-going threshold voltage               |                       |     | 2.9  |     | V    |

| VIT-             | Negative-going threshold voltage               | T <sub>A</sub> = 25°C |     | 2.7  |     | V    |

| V <sub>hys</sub> | Hysteresis, V <sub>IT+</sub> – V <sub>IT</sub> |                       | 100 | 200  |     | mV   |

# short-circuit protection (SCP)

|                          | PARAMETER                    | TEST CONDITIONS                     |      | UNIT |      |      |

|--------------------------|------------------------------|-------------------------------------|------|------|------|------|

|                          | FARAMETER                    | TEST CONDITIONS                     | MIN  | TYP  | MAX  | UNIT |

| V <sub>IT</sub>          | Input threshold voltage      | T <sub>A</sub> = 25°C               | 0.95 | 1    | 1.05 | V    |

| V <sub>stby</sub> †      | Standby voltage              | No pullup                           | 140  | 185  | 230  | mV   |

| V <sub>I</sub> (latched) | Latched-mode input voltage   | No pullup                           |      | 60   | 120  | mV   |

| VIT(COMP)                | Comparator threshold voltage | COMP1, COMP2                        |      | 1    |      | V    |

|                          | Input source current         | $T_A = 25^{\circ}C, V_{O(SCP)} = 0$ | -5   | -15  | -20  | μΑ   |

<sup>†</sup> This symbol is not presently listed within EIA/JEDEC standards for semiconductor symbology.

# TL1454, TL1454Y **DUAL-CHANNEL PULSE-WIDTH-MODULATION (PWM)** CONTROL CIRCUIT SLVS086B - APRIL 1995 - REVISED NOVEMBER 1997

electrical characteristics over recommended operating free-air temperature range,  $V_{CC}$  = 6 V,  $f_{osc}$  = 500 kHz (unless otherwise noted) (continued)

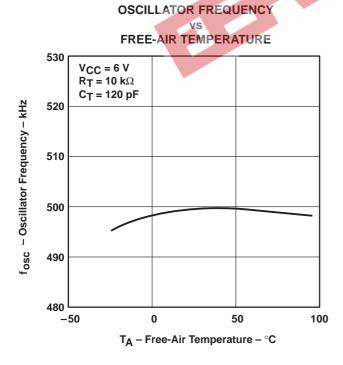

### oscillator

|      | PARAMETER                         | TEST COND                                  | TEST CONDITIONS            |     | TL1454 |     |        |  |

|------|-----------------------------------|--------------------------------------------|----------------------------|-----|--------|-----|--------|--|

|      | FARAINETER                        | TEST CONDITIONS                            |                            | MIN | TYP    | MAX | UNIT   |  |

| fosc | Frequency                         | C <sub>T</sub> = 120 pF,                   | $R_T = 10 \text{ k}\Omega$ |     | 500    |     | kHz    |  |

|      | Standard deviation of frequency   |                                            |                            |     | 50     |     | kHz    |  |

|      | Frequency change with voltage     | $V_{CC} = 3.6 \text{ V to } 20 \text{ V},$ | $T_A = 25^{\circ}C$        |     | 5      |     | kHz    |  |

|      | Francisco change with temperature | $T_A = T_{A(min)}$ to 25°C                 |                            |     | -2     | ±20 | lel I= |  |

|      | Frequency change with temperature | T <sub>A</sub> = 25°C to 85°C              |                            |     | -10    | ±20 | kHz    |  |

|      | Maximum ramp voltage              |                                            |                            |     | 1.8    |     | V      |  |

|      | Minimum ramp voltage              |                                            |                            |     | 1.1    |     | V      |  |

# dead-time control (DTC)

| PARAMETER                |                                | TEST CONDITIONS       | 7   | UNIT |     |      |

|--------------------------|--------------------------------|-----------------------|-----|------|-----|------|

|                          | PARAINETER                     | TEST CONDITIONS       | MIN | TYP  | MAX | UNIT |

| \/                       | Input threshold voltage        | Duty cycle = 0%       | 1   | 1.1  | 1.2 | V    |

| VIT                      | input threshold voltage        | Duty cycle = 100%     | 0.4 | 0.5  | 0.6 | V    |

| V <sub>I</sub> (latched) | Latched-mode input voltage     | 43                    |     | 1.2  |     | V    |

| I <sub>IB</sub>          | Common-mode input bias current | DTC1, IN1+ ≈ 1.2 V    |     |      | 4   | μΑ   |

|                          | Latched-mode (source) current  | T <sub>A</sub> = 25°C |     | -100 |     | μΑ   |

# error-amplifier

|                      | DADAMETER                     | TEST COMPITIONS                                         | TL1454       |      |      | TEST CONDITIONS TL145 |  | UNIT |

|----------------------|-------------------------------|---------------------------------------------------------|--------------|------|------|-----------------------|--|------|

|                      | PARAMETER                     | 1 1EST CONDITIONS                                       | MIN          | TYP  | MAX  | UNII                  |  |      |

| VIO                  | Input offset voltage          |                                                         |              |      | 6    | mV                    |  |      |

| lio                  | Input offset current          | $V_O = 1.25 \text{ V},  V_{IC} = 1.25 \text{ V}$        |              |      | 100  | nA                    |  |      |

| I <sub>IB</sub>      | Input bias current            |                                                         |              | -160 | -500 | nA                    |  |      |

| VICR                 | Input voltage range           | V <sub>CC</sub> = 3.6 V to 20 V                         | -0.2 to 1.40 |      |      | V                     |  |      |

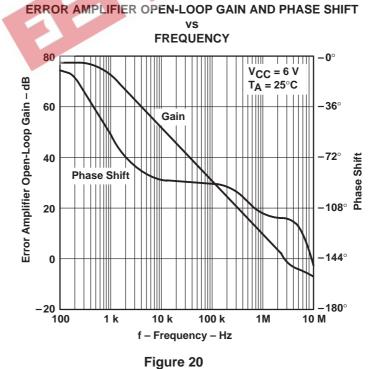

| Ay                   | Open-loop voltage gain        | R <sub>FB</sub> = 200 kΩ                                | 70           | 80   |      | dB                    |  |      |

|                      | Unity-gain bandwidth          |                                                         |              | 3    |      | MHz                   |  |      |

| CMRR                 | Common-mode rejection ratio   |                                                         | 60           | 80   |      | dB                    |  |      |

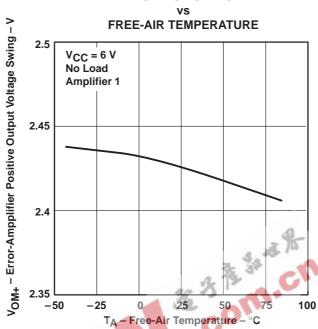

| V <sub>OM(max)</sub> | Positive output voltage swing |                                                         | 2.3          | 2.43 |      | V                     |  |      |

| VOM(min)             | Negative output voltage swing |                                                         |              | 0.63 | 0.8  | V                     |  |      |

| l <sub>O+</sub>      | Output sink current           | $V_{ID} = -0.1 \text{ V},  V_{O} = 1.20 \text{ V}$      | 0.1          | 0.5  |      | mA                    |  |      |

| I <sub>O</sub> -     | Output source current         | $V_{ID} = 0.1 \text{ V}, \qquad V_{O} = 1.80 \text{ V}$ | -45          | -70  |      | μΑ                    |  |      |

# output

|                               | PARAMETER                 | TEST CONDITIONS                                 | Т                  | UNIT |     |      |

|-------------------------------|---------------------------|-------------------------------------------------|--------------------|------|-----|------|

|                               | FARAMETER                 | TEST CONDITIONS                                 | MIN                | TYP  | MAX | UNIT |

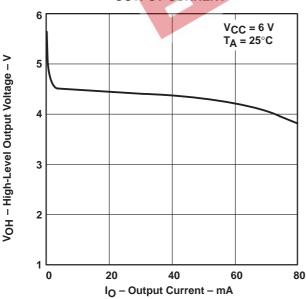

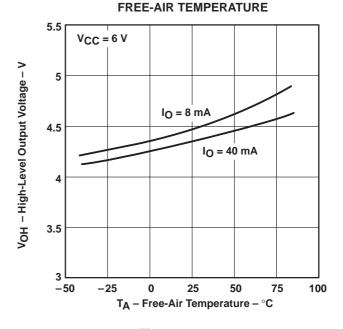

| VOH High-level output voltage | $I_O = -8 \text{ mA}$     | V <sub>CC</sub> -2                              | 4.5                |      | V   |      |

|                               | nign-ievei output voitage | $I_O = -40 \text{ mA}$                          | V <sub>CC</sub> -2 | 4.4  |     | V    |

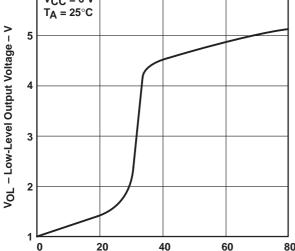

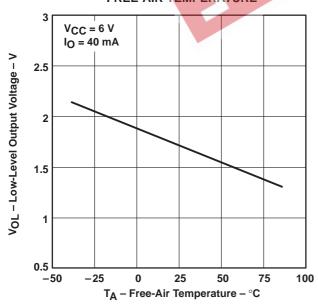

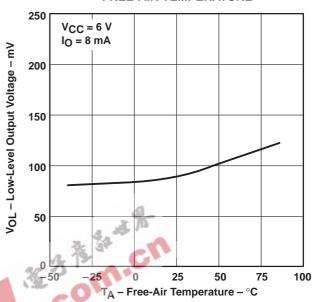

| Val                           | Low-level output voltage  | I <sub>O</sub> = 8 mA                           |                    | 0.1  | 0.4 | V    |

| VOL                           | Low-level output voltage  | I <sub>O</sub> = 40 mA                          |                    | 1.8  | 2.5 | V    |

| t <sub>rv</sub>               | Output voltage rise time  | C <sub>L</sub> = 2000 pF, T <sub>A</sub> = 25°C |                    | 220  |     | ns   |

| tfV                           | Output voltage fall time  | CL = 2000 μr, TA = 25 C                         |                    | 220  | ·   | 115  |

# TL1454, TL1454Y **DUAL-CHANNEL PULSE-WIDTH-MODULATION (PWM)** CONTROL CIRCUIT SLVS086B – APRIL 1995 – REVISED NOVEMBER 1997

electrical characteristics over recommended operating free-air temperature range,  $V_{CC}$  = 6 V,  $f_{OSC}$  = 500 kHz (unless otherwise noted) (continued)

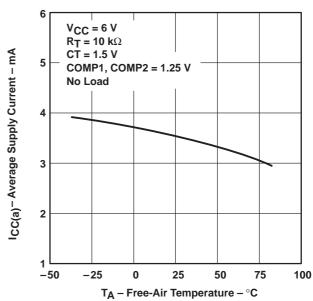

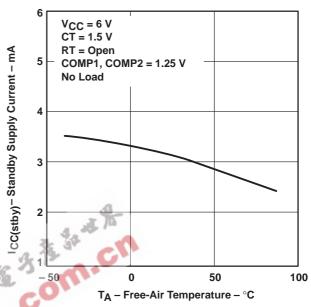

# supply current

| PARAMETER    |                        | TEST CONDITIONS                                                                     |     | TL1454 |     |      |

|--------------|------------------------|-------------------------------------------------------------------------------------|-----|--------|-----|------|

|              | PARAMETER              | TEST CONDITIONS                                                                     | MIN | TYP    | MAX | UNIT |

| ICC(stby)    | Standby supply current | RT open, $CT = 1.5 \text{ V}$ , No load, $V_O$ (COMP1, COMP2) = 1.25 V,             |     | 3.1    | 6   | mA   |

| ICC(average) | Average supply current | $R_T = 10 \text{ k}\Omega,$ $C_T = 120 \text{ pF},$ $50\%$ duty cycle, Outputs open |     | 3.5    | 7   | mA   |

# electrical characteristics, $V_{CC}$ = 6 V, $f_{osc}$ = 500 kHz, $T_A$ = 25°C (unless otherwise noted)

# reference

| PARAMETER        |                                        | TEST COMPITIONS                                                        | TL1454Y   | UNIT    |

|------------------|----------------------------------------|------------------------------------------------------------------------|-----------|---------|

|                  |                                        | TEST CONDITIONS                                                        | MIN TYP M | AX UNII |

| V <sub>ref</sub> | Output voltage, REF                    | I <sub>O</sub> = 1 mA,                                                 | 1.25      | V       |

|                  | Input regulation                       | $V_{OC} = 3.6 \text{ V to } 20 \text{ V}, \qquad I_{O} = 1 \text{ mA}$ | 2         | mV      |

|                  | Output regulation                      | I <sub>O</sub> = 0.1 mA to 1 mA                                        | 1         | mV      |

|                  | Output voltage change with temperature | I <sub>O</sub> = 1 mA                                                  | -1.25     | mV      |

|                  | Output voltage change with temperature | I <sub>O</sub> = 1 mA                                                  | -2.5      | IIIV    |

| los              | Short-circuit output current           | V <sub>ref</sub> = 0 V                                                 | 30        | mA      |

# undervoltage lockout (UVLO)

| PARAMETER         |                                                 |  | TEST CONDITIONS | TL1454Y         |     |     | UNIT |      |

|-------------------|-------------------------------------------------|--|-----------------|-----------------|-----|-----|------|------|

|                   | PARAWIETER                                      |  | `               | TEST CONDITIONS | MIN | TYP | MAX  | ONII |

| V <sub>IT+</sub>  | Positive-going threshold voltage                |  |                 |                 |     | 2.9 |      | V    |

| V <sub>IT</sub> - | Negative-going threshold voltage                |  |                 |                 |     | 2.7 |      | V    |

| V <sub>hys</sub>  | Hysteresis, V <sub>IT+</sub> - V <sub>IT-</sub> |  |                 |                 |     | 200 |      | mV   |

# short-circuit protection (SCP)

| PARAMETER                |                              | TEST CONDITIONS  | TL1454Y |     |     | UNIT |

|--------------------------|------------------------------|------------------|---------|-----|-----|------|

|                          |                              | TEST CONDITIONS  | MIN     | TYP | MAX | UNIT |

| VIT                      | Input threshold voltage      |                  |         | 1   |     | V    |

| ∨ <sub>stby</sub> †      | Standby voltage              | No pullup        |         | 185 |     | mV   |

| V <sub>I</sub> (latched) | Latched-mode input voltage   | No pullup        |         | 60  |     | mV   |

| VIT(COMP)                | Comparator threshold voltage | COMP1, COMP2     |         | 1   |     | V    |

|                          | Input source current         | $V_{O(SCP)} = 0$ |         | -15 |     | μΑ   |

<sup>†</sup> This symbol is not presently listed within EIA/JEDEC standards for semiconductor symbology.

# oscillator

| PARAMETER |                                     | TEST CONDITIONS                                    | TL1454Y |     |     | UNIT |     |

|-----------|-------------------------------------|----------------------------------------------------|---------|-----|-----|------|-----|

|           |                                     | TEST CONDITIONS                                    |         | MIN | TYP | MAX  |     |

| fosc      | Frequency                           | $C_T = 120 \text{ pF}, 	 R_T = 10 \text{ k}\Omega$ |         |     | 500 |      | kHz |

|           | Standard deviation of frequency     |                                                    |         |     | 50  |      | kHz |

|           | Frequency change with voltage       | V <sub>CC</sub> = 3.6 V to 20 V                    |         |     | 5   |      | kHz |

|           | Fragues at about a with temperature |                                                    | -2      |     |     | kHz  |     |

|           | Frequency change with temperature   |                                                    |         |     | -10 |      | KHZ |

|           | Maximum ramp voltage                |                                                    |         |     | 1.8 |      | V   |

|           | Minimum ramp voltage                |                                                    |         |     | 1.1 |      | V   |

# TL1454, TL1454Y DUAL-CHANNEL PULSE-WIDTH-MODULATION (PWM) CONTROL CIRCUIT SLVS086B – APRIL 1995 – REVISED NOVEMBER 1997

# electrical characteristics, $V_{CC}$ = 6 V, $f_{osc}$ = 500 kHz, $T_A$ = 25°C (unless otherwise noted) (continued) dead-time control (DTC)

| PARAMETER                |                               | TEST CONDITIONS   | TL1454Y |      |     | UNIT |  |

|--------------------------|-------------------------------|-------------------|---------|------|-----|------|--|

|                          | PARAMETER                     | TEST CONDITIONS   | MIN     | TYP  | MAX | UNII |  |

| \/                       | Input throughold voltage      | Duty cycle = 0%   |         | 1.1  |     | \/   |  |

| VIT                      | Input threshold voltage       | Duty cycle = 100% |         | 0.5  |     | 1 °  |  |

| V <sub>I</sub> (latched) | Latched-mode input voltage    |                   |         | 1.2  |     | V    |  |

|                          | Latched-mode (source) current |                   |         | -100 |     | μΑ   |  |

# error-amplifier

| PARAMETER            |                               | TEST CONDITIONS                                          | TL1454Y     | UNIT |

|----------------------|-------------------------------|----------------------------------------------------------|-------------|------|

|                      | PARAMETER                     | TEST CONDITIONS                                          | MIN TYP MAX | UNII |

| I <sub>IB</sub>      | Input bias current            | $V_O = 1.25 \text{ V}, \qquad V_{IC} = 1.25 \text{ V}$   | -160        | nA   |

| Ay                   | Open-loop voltage gain        | R <sub>FB</sub> = 200 kΩ                                 | 80          | dB   |

|                      | Unity-gain bandwidth          |                                                          | 3           | MHz  |

| CMRR                 | Common-mode rejection ratio   | 4                                                        | 80          | dB   |

| V <sub>OM(max)</sub> | Positive output voltage swing | - A 75                                                   | 2.43        |      |

| VOM(min)             | Negative output voltage swing | 2 32                                                     | 0.63        | ]    |

| I <sub>O+</sub>      | Output sink current           | $V_{ID} = -0.1 \text{ V}, \qquad V_{O} = 1.20 \text{ V}$ | 0.5         | mA   |

| I <sub>O</sub> _     | Output source current         | $V_{ID} = 0.1 \text{ V}, \qquad V_{O} = 1.80 \text{ V}$  | -70         | μΑ   |

# output

|                 | PARAMETER                    | TEST CONDITIONS |                          | TL1454Y     | UNIT |

|-----------------|------------------------------|-----------------|--------------------------|-------------|------|

|                 | PARAMETER                    |                 | TEST CONDITIONS          | MIN TYP MAX | UNIT |

| \/011           | High-level output voltage    |                 | $I_O = -8 \text{ mA}$    | 4.5         |      |

| VOH             | r light-level output voltage |                 | $I_O = -40 \text{ mA}$   | 4.4         | ]    |

| Val             | Low-level output voltage     | -               | $I_O = 8 \text{ mA}$     | 0.1         |      |

| VOL             | Low-level output voltage     |                 | $I_O = 40 \text{ mA}$    | 1.8         | ]    |

| t <sub>rv</sub> | Output voltage rise time     |                 | C. – 2000 pE             | 220         |      |

| tfv             | Output voltage fall time     |                 | C <sub>L</sub> = 2000 pF | 220         | ns   |

# supply current

| PARAMETER             |                        | TEST CONDITIONS                                                                     | TL1454Y |     |     | UNIT |

|-----------------------|------------------------|-------------------------------------------------------------------------------------|---------|-----|-----|------|

|                       | FARAINETER             | TEST CONDITIONS                                                                     | MIN     | TYP | MAX | UNIT |

| I <sub>CC(stby)</sub> | Standby supply current | RT open, CT = 1.5 V, No load, V <sub>O</sub> (COMP1, COMP2) = 1.25 V,               |         | 3.1 |     | mA   |

| ICC(average)          | Average supply current | $R_T = 10 \text{ k}\Omega,$ $C_T = 120 \text{ pF},$ $50\%$ duty cycle, Outputs open |         | 3.5 | ·   | mA   |

SLVS086B - APRIL 1995 - REVISED NOVEMBER 1997

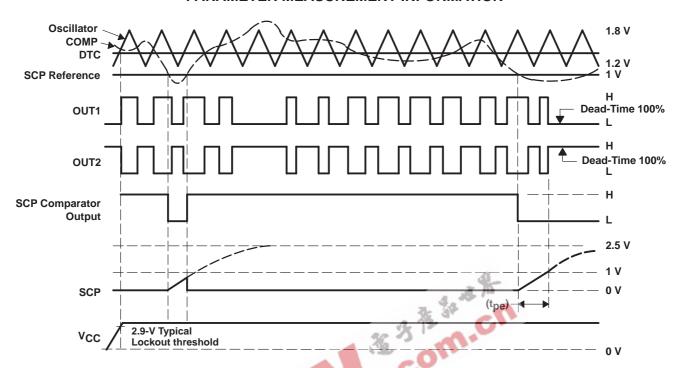

# PARAMETER MEASUREMENT INFORMATION

Figure 5. Timing Diagram

**OSCILLATOR PERIOD**

# **TYPICAL CHARACTERISTICS**

TIMING CAPACITANCE  $10^{2}$   $V_{CC} = 6 \text{ V}$   $R_{T} = 5.1 \text{ k}\Omega$   $T_{A} = 25^{\circ}\text{C}$   $10^{0}$   $10^{1}$   $10^{2}$   $10^{3}$   $10^{4}$   $10^{5}$   $C_{T} - \text{Timing Capacitance} - pF$

Figure 6

PWM TRIANGLE WAVEFORM AMPLITUDE

Figure 7

Figure 8

Figure 9

# DTC INPUT THRESHOLD VOLTAGE FREE-AIR TEMPERATURE $V_{CC} = 6 V$ $R_T = 5.1 \text{ k}\Omega$ $C_T = 1000 pF$ 1.2 DTC Input Threshold Voltage - V VIT (0% Duty Cycle) 1 8.0 0.6 V<sub>IT</sub> (100% Duty Cycle) 0.4 100 50 -50 $T_A$ – Free-Air Temperature – $^{\circ}C$

Figure 10

Figure 12

Figure 11

Figure 13

**DUTY CYCLE**

**DTC INPUT VOLTAGE**

# **TYPICAL CHARACTERISTICS**

120 VCC = 6 V $C_T = 120 pF$  $R_T = 10 \text{ k}\Omega$ 100 T<sub>A</sub> = 25°C 80 Duty Cycle - % 60 40 0.25 0.75 1.25 1.5 V<sub>I(DTC)</sub> - DTC Input Voltage - V

Figure 14

**ERROR-AMPLIFIER MAXIMUM OUTPUT VOLTAGE**

Figure 16

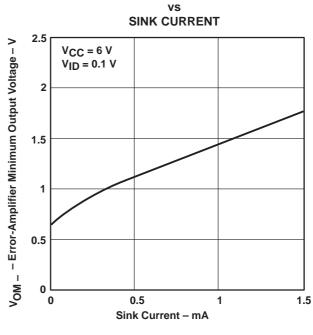

**ERROR-AMPLIFIER MINIMUM OUTPUT VOLTAGE**

Figure 15

Figure 17

### **ERROR AMPLIFIER MAXIMUM ERROR-AMPLIFIER MINIMUM OUTPUT VOLTAGE SWING** PEAK-TO-PEAK OUTPUT VOLTAGE SWING vs vs VOM+ - Error-Ampplifier Minimum Output Voltage Swing - V **FREQUENCY** FREE-AIR TEMPERATURE 2.5 0.8 $V_{CC} = 6 V$ V<sub>O</sub>(PP) – Error Amplifier Maximum Peak-to-Peak Output Voltage Swing – V VCC = 6 VTA = 25°C No Load **Amplifier 1** 0.7 0.6 1.5 0.5 1 0.4 0.5 0 0.3 1 k 10 k 1M 10 M 100 M 25 75 100 T<sub>A</sub> – Free-Air Temperature – °C f - Frequency - Hz

Figure 19

# **ERROR-AMPLIFIER POSITIVE OUTPUT VOLTAGE SWING**

Figure 21

# HIGH-LEVEL OUTPUT VOLTAGE

# **OUTPUT CURRENT**

Figure 22

### HIGH-LEVEL OUTPUT VOLTAGE

# vs

Figure 23

6

### TYPICAL CHARACTERISTICS

# LOW-LEVEL OUTPUT VOLTAGE vs LOW-LEVEL OUTPUT CURRENT VCC = 6 V TA = 25°C

Figure 24

IOL - Low-Level Output Current - mA

# LOW-LEVEL OUTPUT VOLTAGE vs FREE-AIR TEMPERATURE

Figure 26

# LOW-LEVEL OUTPUT VOLTAGE vs FREE-AIR TEMPERATURE

Figure 25

# AVERAGE SUPPLY CURRENT vs

# FREE-AIR TEMPERATURE

Figure 27

# STANDBY SUPPLY CURRENT SUPPLY VOLTAGE VCC = 6 VRT = Open CT = 1.5 V ICC(stby)- Standby Supply Current - mA **COMP1, COMP2 = 1.25 V** No Load T<sub>A</sub> = 25°C 3 2 0 5 25 10 15 20 V<sub>CC</sub> - Supply Voltage - V

STANDBY SUPPLY CURRENT vs FREE-AIR TEMPERATURE

Figure 28

REFERENCE VOLTAGE vs SUPPLY VOLTAGE

Figure 30 Figure 31

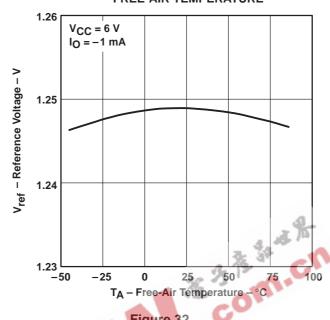

**REFERENCE VOLTAGE** FREE-AIR TEMPERATURE

Figure 32

SLVS086B - APRIL 1995 - REVISED NOVEMBER 1997

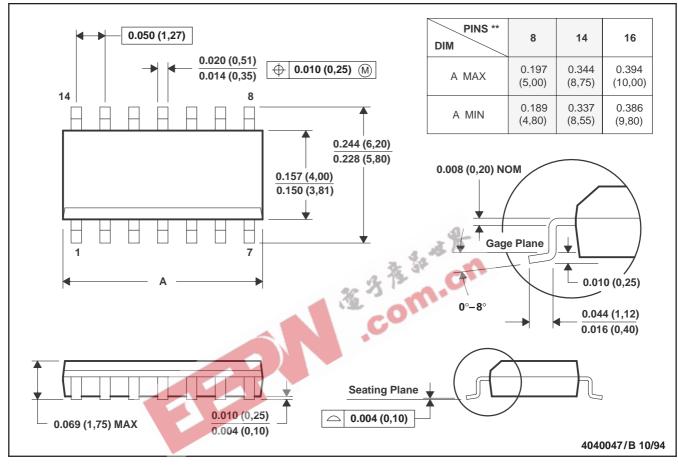

### **MECHANICAL DATA**

# D (R-PDSO-G\*\*)

### 14 PIN SHOWN

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Four center pins are connected to die mount pad

E. Falls within JEDEC MS-012

SLVS086B - APRIL 1995 - REVISED NOVEMBER 1997

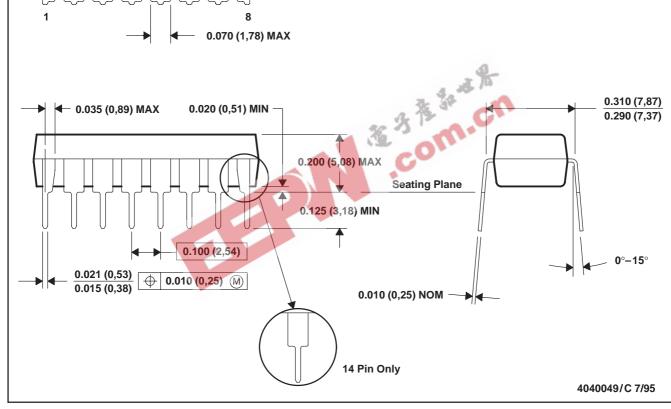

### **MECHANICAL DATA**

0.260 (6,60) 0.240 (6,10)

# N (R-PDIP-T\*\*)

# 16 PIN SHOWN

9

A \_\_\_\_

| PINS ** | 14      | 16      | 18      | 20      |

|---------|---------|---------|---------|---------|

| A MAX   | 0.775   | 0.775   | 0.920   | 0.975   |

|         | (19,69) | (19,69) | (23.37) | (24,77) |

| A MIN   | 0.745   | 0.745   | 0.850   | 0.940   |

|         | (18,92) | (18,92) | (21.59) | (23,88) |

PLASTIC DUAL-IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-001 (20-pin package is shorter than MS-001)

SLVS086B - APRIL 1995 - REVISED NOVEMBER 1997

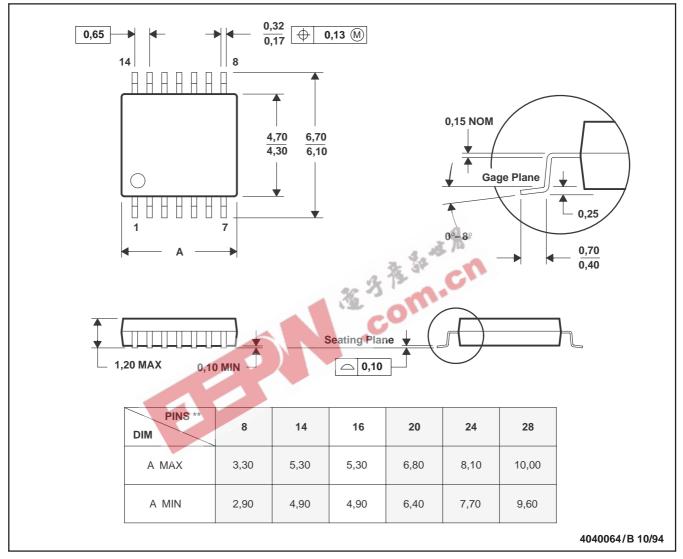

# **MECHANICAL DATA**

# PW (R-PDSO-G\*\*)

# 14 PIN SHOWN

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. This publication of information regarding any third party's products or services does not constitute This approval, warranty or endorsement thereof.