- Complete PCM Codec and Filtering Systems Includes:

- Transmit High-Pass and Low-Pass Filtering

- Receive Low-Pass Filter With (sin x)/x Correction

- Active RC Noise Filters

- μ-Law or A-Law Compatible Coder and Decoder

- Internal Precision Voltage Reference

- Serial I/O Interface

- Internal Autozero Circuitry

### description

The TP3054B, TP3057B, TP13054B, and TP13057B are comprised of a single-chip PCM codec (pulse-code-modulated encoder and de-coder) and PCM line filter. These devices provide all the functions required to interface a full-duplex (2-wire) voice telephone circuit with a TDM (time-division-multiplexed) system. These devices are pin-for-pin compatible with the National Semiconductor TP3054B and TP3057B, respectively. Primary applications include:

- Line interface for digital transmission and switching of T1 carrier, PABX, and central office telephone systems

- Subscriber line concentrators

- Digital-encryption systems

- Digital voice-band data-storage systems

- Digital signal processing

These devices are designed to perform the transmit encoding (A/D conversion) and receive decoding (D/A conversion) as well as the transmit and receive filtering functions in a PCM system. They are intended to be used at the analog termination of a PCM line or trunk. The devices require two transmit and receive master clocks that may be asynchronous (1.536 MHz, 1.544 MHz, or 2.048 MHz), transmit and receive data clocks that are synchronous with the master clock (but can vary from 64 kHz to 2.048 MHz), and transmit and receive frame-sync pulses. The TP3054B, TP3057B, TP13054B, and TP13057B provide the band-pass filtering of the analog signals prior to encoding and after decoding of voice and call progress tones. The TP3054B and TP13054B contain patented circuitry to achieve low transmit channel idle noise and are not recommended for applications in which the composite signals on the transmit side are below –55 dBm0.

The TP3054B and TP3057B are characterized for operation from 0°C to 70°C. The TP13054B and TP13057B are characterized for operation from -40°C to 85°C.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the CMOS gates.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

μ-Law – TP3054B and TP13054B

- A-Law TP3057B and TP13057B

- ±5-V Operation

- Low Operating Power . . . 50 mW Typ

- Power-Down Standby Mode . . . 3 mW Typ

- Automatic Power Down

- TTL- or CMOS-Compatible Digital Interface

- Maximizes Line Interface Card Circuit Density

- Improved Versions of National Semiconductor TP3054, TP3057, TP3054-X, TP3057-X

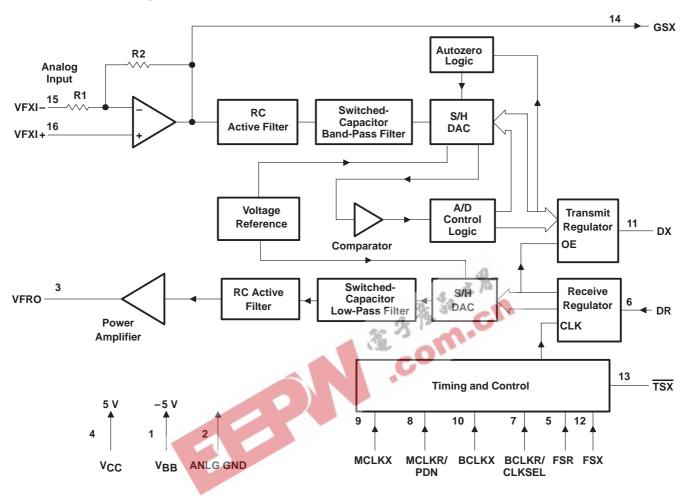

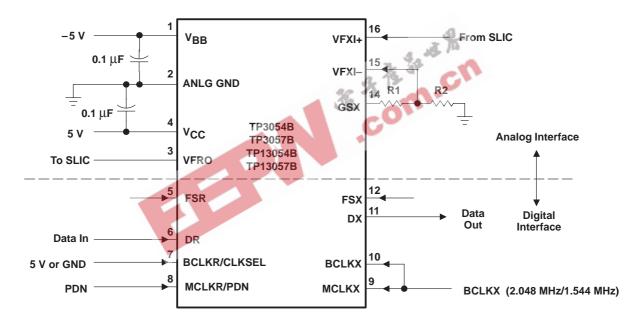

#### functional block diagram

#### **Terminal Functions**

| TERMINAL        |     | DECODIDEION                                                                                                                                                                                                                                                                                                                   |

|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO. | DESCRIPTION                                                                                                                                                                                                                                                                                                                   |

| ANLG GND        | 2   | Analog ground. All signals are referenced to ANLG GND.                                                                                                                                                                                                                                                                        |

| BCLKR/CLKSEL    | 7   | The bit clock that shifts data into DR after the FSR leading edge. May vary from 64 kHz to 2.048 MHz. Alternately, BCLKR/CLKSEL can be a logic input that selects either 1.536 MHz/1.544 MHz or 2.048 MHz for the master clock in the synchronous mode. BCLKX is used for both transmit and receive directions (see Table 1). |

| BCLKX           | 10  | The bit clock that shifts out the PCM data on DX. BCLKX can vary from 64 kHz to 2.048 MHz, but must be synchronous with MCLKX.                                                                                                                                                                                                |

| DR              | 6   | Receive data input. PCM data is shifted into DR following the FSR leading edge.                                                                                                                                                                                                                                               |

| DX              | 11  | The 3-state PCM data output that in enabled by FSX                                                                                                                                                                                                                                                                            |

| FSR             | 5   | Receive frame-sync pulse input that enables BCLKR to shift PCM data in DR. FSR is an 8-kHz pulse train (see Figures 1 and 2 for timing details).                                                                                                                                                                              |

| FSX             | 12  | Transmit frame-sync pulse that enables BCLKX to shift out the PCM data on DX. FSX is an 8-kHz pulse train (see Figures 1 and 2 for timing details).                                                                                                                                                                           |

| GSX             | 14  | Analog output of the transmit input amplifier. GSX is used to externally set gain.                                                                                                                                                                                                                                            |

| MCLKR/PDN       | 8   | Receive master clock (must be 1.536 MHz, 1.544 MHz, or 2.048 MHz). May be synchronous with MCLKX, but should be synchronous with MCLKX for best performance. When MCLKR is connected continuously low, MCLKX is selected for all internal timing. When MCLKR is connected continuously high, the device is powered down.      |

| MCLKX           | 9   | Transmit master clock (must be 1.536 MHz, 1.544 MHz, or 2.048 MHz). May be asynchronous with MCLKR.                                                                                                                                                                                                                           |

| TSX             | 13  | Open-drain output that pulses low during the encoder time slot                                                                                                                                                                                                                                                                |

| V <sub>BB</sub> | 1   | Negative power supply pin. V <sub>BB</sub> = $-5 V \pm 5\%$                                                                                                                                                                                                                                                                   |

| V <sub>CC</sub> | 4   | Positive power supply pin. $V_{CC} = 5 V \pm 5\%$                                                                                                                                                                                                                                                                             |

| VFRO            | 3   | Analog output of the receive filter                                                                                                                                                                                                                                                                                           |

| VFXI+           | 16  | Noninverting input of the transmit input amplifier                                                                                                                                                                                                                                                                            |

| VFXI-           | 15  | Inverting input of the transmit input amplifier                                                                                                                                                                                                                                                                               |

|                 |     |                                                                                                                                                                                                                                                                                                                               |

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>CC</sub> (see Note 1)                            |                                                          |

|-------------------------------------------------------------------------|----------------------------------------------------------|

| Supply voltage, V <sub>BB</sub> (see Note 1)                            |                                                          |

| Voltage range at any analog input or output                             | $\dots$ V <sub>CC</sub> +0.3 V to V <sub>BB</sub> –0.3 V |

| Voltage range at any digital input or output                            | . V <sub>CC</sub> +0.3 V to ANLG GND $-0.3$ V            |

| Continuous total dissipation                                            | See Dissipation Rating Table                             |

| Operating free-air temperature range, T <sub>A</sub> : TP3054B, TP3057B | 0°C to 70°C                                              |

| TP13054B, TP13057B                                                      | –40°C to 85°C                                            |

| Storage temperature range, T <sub>stg</sub>                             | 65°C to 150°C                                            |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: DW or N   | N package 260°C                                          |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. NOTE 1: All voltages are with respect to GND.

.....

| DISSIPATION RATING TABLE |                                       |                                                |                                       |                                       |  |  |  |  |

|--------------------------|---------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|--|--|--|--|

| PACKAGE                  | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |  |  |  |  |

| DW                       | 1025 mW                               | 8.2 mW/°C                                      | <b>6</b> 56 mW                        | 533 mW                                |  |  |  |  |

| N                        | 1150 mW                               | 9.2 mW/°C                                      | 736 mW                                | 598 mW                                |  |  |  |  |

|                          |                                       |                                                | 10C C21                               |                                       |  |  |  |  |

|                                                    |  | .0.              | MIN    | NOM | MAX   | UNIT |

|----------------------------------------------------|--|------------------|--------|-----|-------|------|

| Supply voltage, V <sub>CC</sub>                    |  |                  | 4.75   | 5   | 5.25  | V    |

| Supply voltage, V <sub>BB</sub>                    |  |                  | -4.75  | -5  | -5.25 | V    |

| High-level input voltage, VIH                      |  |                  | 2.2    |     |       | V    |

| Low-level input voltage, VIL                       |  |                  |        |     | 0.6   | V    |

| Common-mode input voltage range, VICR <sup>‡</sup> |  |                  |        |     | ±2.5  | V    |

| Load resistance, GSX, RL                           |  |                  | 10     |     |       | kΩ   |

| Load capacitance, GSX, CL                          |  |                  |        |     | 50    | pF   |

| Operating free-air temperature, TA                 |  | TP3054B, TP3057B | 0      |     | 70    | °C   |

| Operating nee-an temperature, 1A                   |  | TP13054B, TP1305 | 7B –40 |     | 85    |      |

$\ddagger$  Measured with CMRR > 60 dB.

NOTE 2: To avoid possible damage to these CMOS devices and resulting reliability problems, the power-up procedure described in the device power-up sequence paragraphs later in this document should be followed.

#### electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

#### supply current

| PARAMETER |                                     | TEST CONDITIONS | TP305xB         |     |     | TP1305xB |     |     | UNIT |            |

|-----------|-------------------------------------|-----------------|-----------------|-----|-----|----------|-----|-----|------|------------|

|           | FARAWETER                           |                 | TEST CONDITIONS | MIN | TYP | MAX      | MIN | TYP | MAX  | UNIT       |

|           | Supply ourropt from \/oo            | Power down      | No load         |     | 0.5 | 1        |     | 0.5 | 1.2  | <b>~</b> ^ |

| lcc       | Supply current from V <sub>CC</sub> | Active          |                 |     | 6   | 9        |     | 6   | 10   | mA         |

|           | Supply ourropt from \/==            | Power down      | Nie lees d      |     | 0.5 | 1        |     | 0.5 | 1.2  | m۸         |

| IBB       | BB Supply current from VBB Active   | No load         |                 | 6   | 9   |          | 6   | 10  | mA   |            |

## electrical characteristics at V<sub>CC</sub> = 5 V $\pm$ 5%, V<sub>BB</sub> = –5 V $\pm$ 5%, GND at 0 V, T<sub>A</sub> = 25°C (unless otherwise noted)

#### digital interface

|                              | PARAMETER                                      |                    | TEST CONDITIONS                                     | MIN | MAX | UNIT |  |

|------------------------------|------------------------------------------------|--------------------|-----------------------------------------------------|-----|-----|------|--|

| VOH                          | High-level output voltage                      | DX                 | I <sub>H</sub> = -3.2 mA                            | 2.4 |     | V    |  |

| VOI Low-level output voltage |                                                | DX                 | IL = 3.2 mA                                         |     | 0.4 | V    |  |

| VOL                          | Low-level output voltage                       | TSX                | IL = 3.2 mA, Drain open                             |     | 0.4 | V    |  |

| IIН                          | High-level input current                       | .0                 | V <sub>L</sub> = V <sub>IH</sub> to V <sub>CC</sub> |     | ±10 | μA   |  |

| ЦL                           | Low-level input current                        | All digital inputs | $V_{I} = GND$ to $V_{IL}$                           |     | ±10 | μA   |  |

| VOL                          | Output current in high-impedance state         | DX                 | $V_{O} = GND$ to $V_{CC}$                           |     | ±10 | μA   |  |

| analo                        | inalog interface with transmit amplifier input |                    |                                                     |     |     |      |  |

#### analog interface with transmit amplifier input

|                | PARAMETER                       |                 | TEST CONDITIONS           | MIN  | TYP <sup>†</sup> | MAX  | UNIT |

|----------------|---------------------------------|-----------------|---------------------------|------|------------------|------|------|

| Ц              | Input current                   | VFXI+ or VFXI-  | $V_{I} = -2.5 V$ to 2.5 V |      |                  | ±200 | nA   |

| r <sub>i</sub> | Input resistance                | VFXI+ or VFXI – | $V_{I} = -2.5 V$ to 2.5 V | 10   |                  |      | MΩ   |

| r <sub>o</sub> | Output resistance               |                 | Closed loop, Unity ga     | iin  | 1                | 3    | Ω    |

|                | Output dynamic range            | GSX             | $R_L \ge 10 \ k\Omega$    |      |                  | ±2.8 | V    |

| Av             | Open-loop voltage amplification | VFXI+ to GSX    |                           | 5000 |                  |      |      |

| Bl             | Unity-gain bandwidth            | GSX             |                           | 1    | 2                |      | MHz  |

| VIO            | Input offset voltage            | VFXI+ or VFXI-  |                           |      |                  | ±20  | mV   |

| CMRR           | Common-mode rejection ratio     |                 |                           | 60   |                  |      | dB   |

| KSVR           | Supply-voltage rejection ratio  |                 |                           | 60   |                  |      | dB   |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, V<sub>BB</sub> = -5 V, and T<sub>A</sub> =  $25^{\circ}$ C.

#### analog interface with receive filter

| PARAMETER                |             | TEST CONDITIONS | MIN | TYP† | MAX  | UNIT |

|--------------------------|-------------|-----------------|-----|------|------|------|

| Output resistance        | VFRO        |                 |     | 1    | 3    | Ω    |

| Load resistance          |             | VFRO = ±2.5 V   | 600 |      |      | Ω    |

| Load capacitance         | VFRO to GND |                 |     |      | 500  | pF   |

| Output dc offset voltage | VFRO to GND |                 |     |      | ±200 | mV   |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, V<sub>BB</sub> = -5 V, and T<sub>A</sub> =  $25^{\circ}$ C.

# operating characteristics, over operating free-air temperature range, V<sub>CC</sub> = 5 V ±5%, V<sub>BB</sub> = -5 V ±5%, GND at 0 V, V<sub>I</sub> = 1.2276 V, f = 1.02 kHz, transmit input amplifier connected for unity gain, noninverting (unless otherwise noted)

#### timing requirements

|                       | PARAMETER                                                                 |                    | TEST CONDITIONS                                                     | MIN | TYP†                    | MAX   | UNIT |

|-----------------------|---------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------|-----|-------------------------|-------|------|

| <sup>f</sup> clock(M) | Frequency of master clock                                                 | MCLKX and MCLKR    | Depends on the device used and<br>BCLKX/CLKSEL                      |     | 1.536<br>1.544<br>2.048 |       | MHz  |

| <sup>f</sup> clock(B) | Frequency of bit clock, transmit                                          | BCLKX              |                                                                     | 64  |                         | 2.048 | kHz  |

| tw1                   | Pulse duration, MCLKX and MCLKR high                                      | h                  |                                                                     | 160 |                         |       | ns   |

| t <sub>w2</sub>       | Pulse duration, MCLKX and MCLKR low                                       | -                  |                                                                     | 160 |                         |       | ns   |

| <sup>t</sup> r1       | Rise time of master clock                                                 | MCLKX and MCLKR    | Measured from 20% to 80%                                            |     |                         | 50    | ns   |

| <sup>t</sup> f1       | Fall time of master clock                                                 | MCLKX and<br>MCLKR | Measured from 20% to 80%                                            |     |                         | 50    | ns   |

| t <sub>r2</sub>       | Rise time of bit clock, transmit                                          | BCLKX              | Measured from 20% to 80%                                            |     |                         | 50    | ns   |

| <sup>t</sup> f2       | Fall time of bit clock, transmit                                          | BCLKX              | Measured from 20% to 80%                                            |     |                         | 50    | ns   |

| <sup>t</sup> su1      | Setup time, BCLKX high (and FSX in lon mode) before MCLKX $\downarrow$    | g-frame sync       | First bit clock after the leading edge of FSX                       | 100 |                         |       | ns   |

| t <sub>w3</sub>       | Pulse duration, BCLKX and BCLKR high                                      |                    | VIH = 2.2 V                                                         | 160 |                         |       | ns   |

| t <sub>w4</sub>       | Pulse duration, BCLKX and BCLKR low                                       |                    | $V_{IL} = 0.6 V$                                                    | 160 |                         |       | ns   |

| <sup>t</sup> h1       | Hold time, frame sync low after bit clock low (long frame only)           |                    | COT                                                                 | 0   |                         |       | ns   |

| <sup>t</sup> h2       | Hold time, BCLKX high after frame sync1<br>(short frame only)             |                    |                                                                     | 0   |                         |       | ns   |

| t <sub>su2</sub>      | Setup time, frame sync high before bit cl<br>(long frame only)            | ock↓               |                                                                     | 80  |                         |       | ns   |

| <sup>t</sup> d1       | Delay time, BCLKX high to data valid                                      |                    | Load = 150 pF plus 2 LSTTL loads <sup>‡</sup>                       | 0   |                         | 140   | ns   |

| td2                   | Delay time, BCLKX high to TSX low                                         |                    | Load = 150 pF plus 2 LSTTL loads <sup>‡</sup>                       |     |                         | 140   | ns   |

| <sup>t</sup> d3       | Delay time, BCLKX (or 8 clock FSX in lo only) low to data output disabled | ng frame           |                                                                     | 50  |                         | 165   | ns   |

| <sup>t</sup> d4       | Delay time, FSX or BCLKX high to data (long frame only)                   | valid              | C <sub>L</sub> = 0 pF to 150 pF                                     | 20  |                         | 165   | ns   |

| t <sub>su3</sub>      | Setup time, DR valid before $BCLKR{\downarrow}$                           |                    |                                                                     | 50  |                         |       | ns   |

| t <sub>h3</sub>       | Hold time, DR valid after BCLKR or BCL                                    | КХ↓                |                                                                     | 50  |                         |       | ns   |

| t <sub>su4</sub>      | Setup time, FSR or FSX high before BC BCLKR $\downarrow$                  | _KR or             | Short-frame sync pulse (1 or 2 bit clock periods long) (see Note 3) | 50  |                         |       | ns   |

| <sup>t</sup> h4       | Hold time, FSX or FSR high after BCLKX or BCLKR $\downarrow$              |                    | Short-frame sync pulse (1 or 2 bit clock periods long) (see Note 3) | 100 |                         |       | ns   |

| t <sub>h5</sub>       | Hold time, frame sync high after bit clock $\downarrow$                   |                    | Long-frame sync pulse (from 3 to 8 bit clock periods long)          | 100 |                         |       | ns   |

| t <sub>w5</sub>       | Minimum pulse duration of the frame syr (low level)                       | ic pulse           | 64 kbps operating mode                                              | 160 |                         |       | ns   |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, V<sub>BB</sub> = -5 V, and T<sub>A</sub> =  $25^{\circ}$ C.

<sup>‡</sup> Nominal input value for an LSTTL lead is 18 k $\Omega$ .

NOTE 3: For short-frame sync timing, FSR and FSX must go high while their respective bit clocks are high.

| PARAMETER                                              |                     | TEST CONDITIONS <sup>‡</sup>                                                                                                                                                             | MIN    | ΤΥΡ <sup>†</sup> ΜΑ)                |      |

|--------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------|------|

|                                                        | TP3054B, TP13054B   | 3.17 dBm0                                                                                                                                                                                |        | 2.501                               |      |

| Maximum peak transmit overload level                   | TP3057B, TP13057B   | 3.14 dBm0                                                                                                                                                                                |        | 2.492                               |      |

| Transmit filter gain, absolute (at 0 dBm0)             | •                   | T <sub>A</sub> = 25°C                                                                                                                                                                    | - 0.15 | 0.15                                | dB   |

|                                                        |                     | f = 16 Hz                                                                                                                                                                                |        | -40                                 | )    |

|                                                        |                     | f = 50 Hz                                                                                                                                                                                |        | -30                                 | 5    |

|                                                        |                     | f = 60 Hz                                                                                                                                                                                |        | -26                                 | 5    |

|                                                        |                     | f = 200 Hz                                                                                                                                                                               | -1.8   | -0.1                                |      |

| The second filler and a second structure to the second |                     | f = 300 Hz to 3000 Hz                                                                                                                                                                    | -0.15  | 0.15                                |      |

| Transmit filter gain, relative to absolute             |                     | f = 3300 Hz                                                                                                                                                                              | -0.35  | 0.05                                | dB   |

|                                                        |                     | f = 3400 Hz                                                                                                                                                                              | -0.8   | (                                   | ,    |

|                                                        |                     | f = 4000 Hz                                                                                                                                                                              |        | -14                                 | +    |

|                                                        |                     | $f \ge 4600 \text{ Hz}$ (measure response from 0 Hz to 4000 Hz)                                                                                                                          |        | -32                                 | 2    |

| Absolute transmit gain variation with tem voltage      | perature and supply | Relative to absolute transmit gain<br>See Note 4                                                                                                                                         | -0.1   | 0.1                                 | dB   |

| Transmit gain tracking error with level                |                     | Sinusoidal test method,<br>Reference level = $-10 \text{ dBm0}$<br>3 dBm0 ≥ input level ≥ $-40 \text{ dBm0}$<br>-40  dBm0 > input level ≥ $-50  dBm0-50  dBm0 > input level ≥ -55  dBm0$ |        | $\pm 0.2$<br>$\pm 0.4$<br>$\pm 0.4$ |      |

| Receive filter gain, absolute (at 0 dBm0)              |                     | Input is digital code sequence for<br>0 dBm0 signal, $T_A = 25^{\circ}C$                                                                                                                 | -0.15  | 0.1                                 |      |

|                                                        |                     | $f = 0$ Hz to 3000 Hz, $T_A = 25^{\circ}C$                                                                                                                                               | -0.15  | 0.1                                 | 5    |

|                                                        |                     | f = 3300 Hz                                                                                                                                                                              | -0.35  | 0.0                                 | 5    |

| Receive filter gain, relative to absolute              |                     | f = 3400 Hz                                                                                                                                                                              | -0.8   | (                                   | dB   |

|                                                        |                     | f = 4000 Hz                                                                                                                                                                              |        | -14                                 | +    |

| Absolute receive gain variation with temp voltage      | erature and supply  | T <sub>A</sub> = full range, See Note 4                                                                                                                                                  | -0.1   | 0.4                                 | dB   |

|                                                        |                     | Sinusoidal test method; reference<br>input PCM code corresponds to an<br>ideally encoded –10 dBm0 signal                                                                                 |        |                                     |      |

| Receive gain tracking error with level                 |                     | $3 \text{ dBm0} \ge \text{input level} \ge -40 \text{ dBm0}$                                                                                                                             |        | ±0.2                                | dB   |

|                                                        |                     | −40 dBm0 > input level ≥ −50 dBm0                                                                                                                                                        |        | ±0.4                                | ł    |

|                                                        |                     | −50 dBm0 > input level ≥ −55 dBm0                                                                                                                                                        |        | ±0.8                                | 3    |

| Receive output drive voltage                           |                     | $R_L = 10 \text{ k}\Omega$                                                                                                                                                               |        | ±2.5                                | 5 V  |

| Transmit and receive gain tracking error               | with level (A-law.  | Pseudo noise test method; reference<br>input PCM code corresponds to an<br>ideally encoded –10 dBm0 signal                                                                               |        |                                     |      |

| CCITT C 712)                                           | ( ,                 | $3 \text{ dBm0} \ge \text{input level} \ge -40 \text{ dBm0}$                                                                                                                             |        | ±0.25                               | ; dB |

|                                                        |                     | $-40 \text{ dBm0} > \text{input level} \ge -50 \text{ dBm0}$                                                                                                                             |        | ±0.3                                | 5    |

|                                                        |                     | –50 dBm0 > input level ≥ –55 dBm0                                                                                                                                                        |        | ±0.4                                | 5    |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, V<sub>BB</sub> = –5 V, and T<sub>A</sub> = 25°C.

<sup>‡</sup> Absolute rms signal levels are defined as follows:  $V_I = 1.2276$  V = 0 dBm0 = 4 dBm at f = 1.02 kHz with R<sub>L</sub> = 600  $\Omega$ .

NOTE 4: Full range for the TP3054B and TP3057B is 0°C to 70°C. Full range for the TP13054B and TP13057B is -40°C to 85°C.

#### envelope delay distortion with frequency

| PARAMETER                                                                                             | TEST CONDITIONS        | MIN | TYP† | MAX                                 | UNIT |

|-------------------------------------------------------------------------------------------------------|------------------------|-----|------|-------------------------------------|------|

| Transmit delay, absolute (at 0 dBm0)                                                                  | f = 1600 Hz            |     | 290  | 315                                 | μs   |

|                                                                                                       | f = 500 Hz to 600 Hz   |     | 195  | 220                                 |      |

|                                                                                                       | f = 600 Hz to 800 Hz   |     | 120  | 145                                 |      |

|                                                                                                       | f = 800 Hz to 1000 Hz  |     | 50   | 75                                  |      |

| Transmit delay, relative to absolute                                                                  | f = 1000 Hz to 1600 Hz |     | 20   | 40                                  | μs   |

|                                                                                                       | f = 1600 Hz to 2600 Hz |     | 55   | 75                                  |      |

|                                                                                                       | f = 2600 Hz to 2800 Hz |     | 80   | 105                                 |      |

|                                                                                                       | f = 2800 Hz to 3000 Hz |     | 130  | 315<br>220<br>145<br>75<br>40<br>75 |      |

| Receive delay, absolute (at 0 dBm0)                                                                   | f = 1600 Hz            |     | 180  | 200                                 | μs   |

|                                                                                                       | f = 500 Hz to 1000 Hz  | -40 | -25  |                                     |      |

|                                                                                                       | f = 1000 Hz to 1600 Hz | -30 | -20  |                                     |      |

| Receive delay, relative to absolute                                                                   | f = 1600 Hz to 2600 Hz |     | 70   | 90                                  | μs   |

|                                                                                                       | f = 2600 Hz to 2800 Hz |     | 100  | 125                                 | μο   |

|                                                                                                       | f = 2800 Hz to 3000 Hz |     | 140  | 175                                 |      |

| All typical values are at V <sub>CC</sub> = 5 V, V <sub>BB</sub> = $-5$ V, and T <sub>A</sub> = 25°C. | 2 State                |     |      |                                     |      |

#### noise

| loise & W                                          |                      |                                                                  |     |      |     |        |

|----------------------------------------------------|----------------------|------------------------------------------------------------------|-----|------|-----|--------|

| PARAMETER                                          |                      | TEST CONDITIONS                                                  | MIN | TYP† | MAX | UNIT   |

| Transmit noise, C-message weighted‡                | TP3054B,<br>TP13054B | VFXI = 0 V                                                       |     | 5    | 9   | dBrnC0 |

| Transmit noise, psophometric weighted (see Note 5) | TP3057B,<br>TP13057B | VFXI = 0 V                                                       |     | -74  | -69 | dBm0p  |

| Receive noise, C-message weighted                  | TP3054B,<br>TP13054B | PCM code equals alternating positive and negative zero           |     | 2    | 4   | dBrnC0 |

| Receive noise, psophometric weighted               | TP3057B,<br>TP13057B | PCM code equals positive zero                                    |     | -86  | -83 | dBm0p  |

| Noise, single frequency                            |                      | VFXI+ = 0 V,<br>f = 0 kHz to 100 kHz,<br>Loop-around measurement |     |      | -53 | dBm0   |

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $V_{BB} = -5 \text{ V}$ , and  $T_A = 25^{\circ}\text{C}$ . <sup>‡</sup> This parameter is achieved through use of patented circuitry and is not recommended for applications in which the composite signals on the transmit side are below -55 dBm0.

NOTE 5: Measured by extrapolation from the distortion test result.

#### power supply rejection

| PARAMETER                                 | TEST CONDITIONS                                                                          |                     |       | MIN | MAX | UNIT |

|-------------------------------------------|------------------------------------------------------------------------------------------|---------------------|-------|-----|-----|------|

|                                           | V <sub>CC</sub> = 5 V + 100 mVrms,<br>VFXI+ = -50 dBm0                                   | f = 0 Hz to 4 kHz   | A-law | 38  |     | dB   |

| Positive power-supply rejection, transmit |                                                                                          |                     | μ-law | 38  |     | dBC† |

|                                           |                                                                                          | f = 4 kHz to 50 kHz |       | 40  |     | dB   |

|                                           | $V_{BB} = -5 V + 100 mVrms,$<br>VFXI+ = -50 dBm0                                         | f = 0 Hz to 4 kHz   | A-law | 35  |     | dB   |

| Negative power-supply rejection, transmit |                                                                                          |                     | μ-law | 35  |     | dBC† |

|                                           |                                                                                          | f = 4 kHz to 50 kHz |       | 40  |     | dB   |

| Positive power-supply rejection, receive  | PCM code equals positive zero,<br>V <sub>CC</sub> = 5 V + 100 mVrms                      | f = 0 Hz to 4 kHz   | A-law | 40  |     | dB   |

|                                           |                                                                                          |                     | μ-law | 40  |     | dBC† |

|                                           |                                                                                          | f = 4 kHz to 50 kHz |       | 40  |     | dB   |

| Negative power-supply rejection, receive  | PCM code equals positive zero,<br>$V_{BB} = -5 V + 100 mVrms$                            | f = 0 Hz to 4 kHz   | A-law | 38  |     | dB   |

|                                           |                                                                                          |                     | μ-law | 38  |     | dBC† |

|                                           | ABB = -2.4 ± 100 mmula                                                                   | f = 4 kHz to 50 kHz |       | 40  |     | dB   |

| Spurious out-of-band signals at the       | 0 dBm0, 300-Hz to 3400-Hz input applied to DR (measure individual image signals at VFRO) |                     |       |     | -30 | dB   |

| channel output (VFRO)                     | f = 4600 Hz to 7600 Hz                                                                   |                     |       |     | -33 | dB   |

|                                           | f = 7600 Hz to 100 kHz                                                                   | 4.35                |       |     | -40 |      |

#### distortion

| distortion                                                                 |                                               | 3 3 T                                                                                                                               |          |      |      |      |

|----------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|------|

| PARAMETER                                                                  |                                               | TEST CONDITIC                                                                                                                       | DNS      | MIN  | MAX  | UNIT |

| Signal-to-distortion ratio, transmit or receive half-channel‡              | Level                                         | Level = 3 dBm0                                                                                                                      |          | 33   |      |      |

|                                                                            | Level                                         | Level = $0 \text{ dBm0 to} - 30 \text{ dBm0}$                                                                                       |          | 36   |      | ]    |

|                                                                            | Level = $-40 \text{ dBm0}$                    | Transmit                                                                                                                            | 29       |      | dBC† |      |

|                                                                            | Level                                         |                                                                                                                                     | Receive  | 30   |      | uber |

|                                                                            |                                               | Level = -55 dBm0                                                                                                                    | Transmit | 14   |      |      |

|                                                                            | Level                                         |                                                                                                                                     | Receive  | 15   |      |      |

| Single-frequency distortion products, transmit                             |                                               |                                                                                                                                     |          |      | -46  | dB   |

| Single-frequency distortion products, receive                              |                                               |                                                                                                                                     |          |      | -46  | dB   |

| Intermodulation distortion                                                 | VFXI+                                         | Loop-around measurement,<br>VFXI + = $-4 \text{ dBm0}$ to $-21 \text{ dBm0}$ ,<br>Two frequencies in the range of 300 Hz to 3400 Hz |          |      | -41  | dB   |

|                                                                            | Level = -3 dBm0                               |                                                                                                                                     | 33       |      | dB   |      |

|                                                                            | Level = $-6 \text{ dBm0 to} -27 \text{ dBm0}$ |                                                                                                                                     |          | 36   |      |      |

| Signal-to-distortion ratio, transmit half-channel (A-law) (CCITT G.714)§   | Level = -34 dBm0                              |                                                                                                                                     | 33.5     |      |      |      |

|                                                                            | Level = $-40 \text{ dBm0}$                    |                                                                                                                                     | 28.5     |      |      |      |

|                                                                            | Level = -55 dBm0                              |                                                                                                                                     |          | 13.5 |      |      |

| Signal-to-distortion ratio, receive half-channel (A-law)<br>(CCITT G.714)§ | Level = -3 dBm0                               |                                                                                                                                     | 33       |      |      |      |

|                                                                            | Level = $-6 \text{ dBm0 to} -27 \text{ dBm0}$ |                                                                                                                                     |          | 36   |      | dB   |

|                                                                            | Level = -34 dBm0                              |                                                                                                                                     | 34.2     |      |      |      |

|                                                                            | Level = -40 dBm0                              |                                                                                                                                     | 30       |      |      |      |

|                                                                            | Level = -55 dBm0                              |                                                                                                                                     |          | 15   |      |      |

<sup>†</sup> The unit dBC applies to C-message weighting.

<sup>‡</sup>Sinusoidal test method (see Note 6)

§ Pseudo-noise test method

NOTE 6: The TP3054B and TP13054B are measured using a C-message filter. The TP3057B and the TP13057B are measured using a psophometric weighted filter.

#### crosstalk

| PARAMETER                                   | TEST CONDITIONS        |                       | MIN | TYP† | MAX | UNIT |

|---------------------------------------------|------------------------|-----------------------|-----|------|-----|------|

| Crosstalk, transmit-to-receive              | f = 300 Hz to 3000 Hz, | DR at steady PCM code |     | -90  | -75 | dB   |

| Crosstalk, receive-to-transmit (see Note 7) | VFXI = 0 V,            | f = 300 Hz to 3000 Hz |     | -90  | -75 | dB   |

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $V_{BB} = -5 \text{ V}$ , and  $T_A = 25^{\circ}\text{C}$ .

NOTE 7: Receive-to-transmit crosstalk is measured with a - 50 dBm0 activation signal applied at VFXI+.

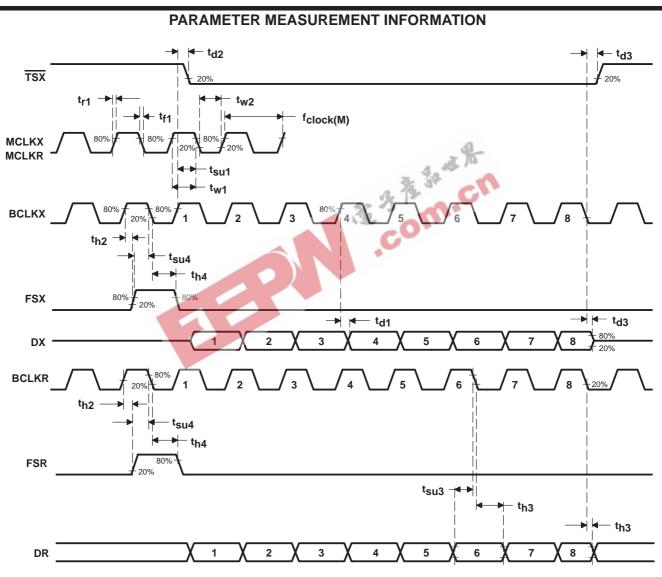

Figure 1. Short-Frame Sync Timing

#### PARAMETER MEASUREMENT INFORMATION

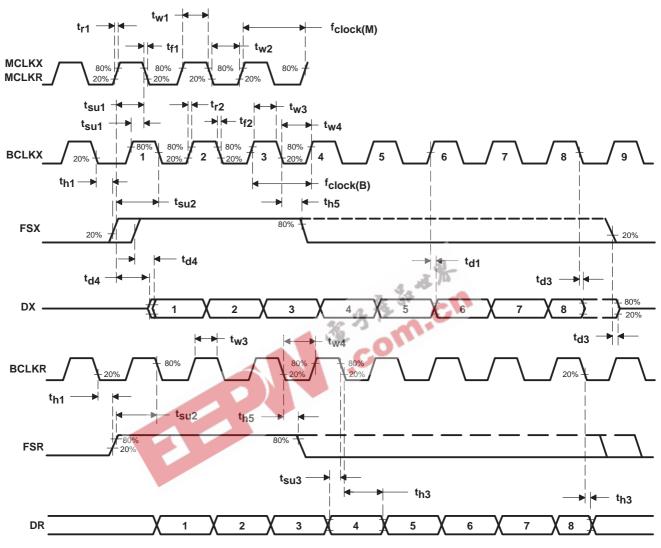

Figure 2. Long-Frame Sync Timing

#### PRINCIPLES OF OPERATION

#### system reliability and design considerations

TP305xB, TP1305xB system reliability and design considerations are described in the following paragraphs.

#### latch-up

Latch-up is possible in all CMOS devices. It is caused by the firing of a parasitic SCR that is present due to the inherent nature of CMOS. When a latch-up occurs, the device draws excessive amounts of current and will continue to draw heavy current until power is removed. Latch-up can result in permanent damage to the device if supply current to the device is not limited.

Even though the TP305xB and TP1305xB devices are heavily protected against latch-up, it is still possible to cause latch-up under certain conditions in which excess current is forced into or out of one or more terminals. Latch-up can occur when the positive supply voltage drops momentarily below ground, when the negative supply voltage rises momentarily above ground, or possibly if a signal is applied to a terminal after power has been applied but before the ground is connected. This can happen if the device is hot-inserted into a card with the power applied, or if the device is mounted on a card that has an edge connector and the card is hot-inserted into a system with the power on.

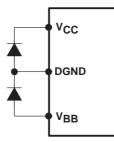

To help ensure that latch-up does not occur, it is considered good design practice to connect a reverse-biased Schottky diode (with a forward voltage drop of less than or equal to 0.4 V – 1N5711 or equivalent) between the power supply and GND (see Figure 3). If it is possible that a TP305xB- or TP1305xB-equipped card that has an edge connector could be hot-inserted into a powered-up system, it is also important to ensure that the ground edge connector traces are longer than the power and signal traces so that the card ground is always the first to make contact.

#### device power-up sequence

Latch-up can also occur if a signal source is connected without the device being properly grounded. A signal applied to one terminal could then find a ground through another signal terminal on the device. To ensure proper operation of the device and as a safeguard against this sort of latch-up, it is recommended that the following power-up sequence always be used:

- 1. Ensure that no signals are applied to the device before the power-up sequence is complete.

- 2. Connect GND.

- 3. Apply V<sub>BB</sub> (most negative voltage).

- 4. Apply V<sub>CC</sub> (most positive voltage).

- 5. Force a power down condition in the device.

- 6. Connect clocks.

- 7. Release the power down condition.

- 8. Apply FS synchronization pulses.

- 9. Apply the signal inputs.

When powering down the device, this procedure should be followed in the reverse order.

#### PRINCIPLES OF OPERATION

Figure 3. Latch-Up Protection Diode Connection

#### internal sequencing

Power-on reset circuitry initializes the TP3054B, TP3057B, TP13054B, and TP13057B devices when power is first applied, placing it into the power-down mode. DX and VFRO outputs go into high-impedance states and all nonessential circuitry is disabled. A low level or clock applied to MCLKR/PDN powers up the device and activates all circuits. DX, a 3-state PCM data output, remains in the high-impedance state until the arrival of the 30 - 5 K second FSX pulse.

#### synchronous operation

For synchronous operation, a clock is applied to MCLKX. MCLKR/PDN is used as a power-down control. A low level on MCLKR powers up the device and a high level powers it down. In either case, MCLKX is selected as the master clock for both receive and transmit direction, BCLKX must also have a bit clock applied to it. The selection of the proper internal divider for a master-clock frequency of 1.536 MHz, 1.544 MHz, or 2.048 MHz can be done via BCLKR/CLKSEL. The device automatically compensates for the 193rd clock pulse of each frame.

A fixed level on BCLKR/CLKSEL selects BCLKX as the bit clock for both the transmit and receive directions. Table 1 indicates the frequencies of operation that can be selected depending on the state of BCLKR/CLKSEL. In the synchronous mode, BCLKX may be in the range from 64 kHz to 2.048 MHz but must be synchronous with MCLKX.

| BCLKR/CLKSEL                             | MASTER-CLOCK FREQUENCY SELECTED |                        |  |  |

|------------------------------------------|---------------------------------|------------------------|--|--|

| BOLKK/OLKSEL                             | TP13054B, TP3054B               | TP13057B, TP3057B      |  |  |

| Clock Input                              | 1.536 MHz or 1.544 MHz          | 2.048 MHz              |  |  |

| Logic Input L<br>(sync mode only)        | 2.048 MHz                       | 1.536 MHz or 1.544 MHz |  |  |

| Logic Input H (open)<br>(sync mode only) | 1.536 MHz or 1.544 MHz          | 2.048 MHz              |  |  |

#### **Table 1. Selection of Master-Clock Frequencies**

The encoding cycle begins with each FSX pulse, and the PCM data from the previous cycle is shifted out of the enabled DX output on the rising edge of BCLKX. After eight bit-clock periods, the 3-state DX output is returned to the high-impedance state. With an FSR pulse, PCM data is latched via DR on the falling edge of BCLKX (or BCLKR, if running). FSX and FSR must be synchronous with MCLKX and MCLKR.

#### PRINCIPLES OF OPERATION

#### asynchronous operation

For asynchronous operation, separate transmit and receive clocks can be applied. MCLKX and MCLKR must be 2.048 MHz for the TP3057B and TP13057B, 1.536 MHz or 1.544 MHz for the TP3054B and TP13054B and need not be synchronous. However, for best performance, MCLKR should be synchronous with MCLKX. This is easily achieved by applying only static logic levels to MCLKR/PDN. This connects MCLKX to all internal MCLKR functions. For 1.544-MHz operation, the device compensates for the 193rd clock pulse of each frame. Each encoding cycle is started with FSX and FSX must be synchronous with MCLKX. The logic levels shown in Table 1 are not valid in the asynchronous mode. BCLKX and BCLKR can operate from 64 kHz to 2.048 MHz.

#### short-frame sync operation

The device can operate with either a short- or a long-frame sync pulse. On power up, the device automatically goes into the short-frame mode where both FSX and FSR must be one bit-clock period long with timing relationships specified in Figure 1. With FSX high during a falling edge of BCLKX, the next rising edge of BCLKX enables the 3-state output buffer, DX, which outputs the sign bits. The remaining seven bits are clocked out on the following seven rising edges and the next falling edge disables DX. With FSR high during a falling edge of BCLKR (BCLKX in synchronous mode), the next falling edge of BCLKR latches in the sign bit. The following seven falling edges latch in the seven remaining bits. The short-frame sync pulse may be utilized in either the synchronous or asynchronous mode.

#### long-frame sync operation

Both FSX and FSR must be three or more bit-clock periods long to use the long-frame sync mode with timing relationships as shown in Figure 2. Using the transmit frame sync (FSX), the device detects whether a shortor long-frame sync pulse is being used. For 64-kHz operation, the frame-sync pulse must be kept low for a minimum of 160 ns. The rising edge of FSX or BCLKX, which ever occurs later, enables the DX 3-state output buffer. The first bit clocked out is the sign bit. The next seven rising edge of BCLKX edges clock out the remaining seven bits. The falling edge of BCLKX following the eighth rising edge or FSX going low, whichever occurs later, disables DX. A rising edge on FSR, the receive-frame sync pulse, causes the PCM data at DR to be latched in on the next eight falling edges of BCLKR (BCLKX in synchronous mode). The long-frame sync pulse can be utilized in either the synchronous or asynchronous mode.

#### transmit section

The transmit section input is an operational amplifier with provision for gain adjustment using two external resistors. The low noise and wide bandwidth characteristics of these devices provide gains in excess of 20 dB across the audio passband. The operational amplifier drives a unity-gain filter consisting of an RC active prefilter followed by an eighth-order switched-capacitor band-pass filter clocked at 256 kHz. The output of this filter directly drives the encoder sample-and-hold circuit. As per  $\mu$ -law (TP3054B and TP13054B) or A-law (TP3057B and TP13057B) coding conventions, the ADC is a companding type. A precision voltage reference provides a nominal input overload of 2.5 V peak. The sampling of the filter output is controlled by the FSX frame-sync pulse. Then the successive-approximation encoding cycle begins. The 8-bit code is loaded into a buffer and shifted out through DX at the next FSX pulse. The total encoding delay is approximately 290  $\mu$ s. Any offset voltage due to the filters or comparator is cancelled by sign-bit integration.

#### **PRINCIPLES OF OPERATION**

#### receive section

The receive section consists of an expanding DAC that drives a fifth-order low-pass filter clocked at 256 kHz. The decoder is  $\mu$ -law (TP3054B and TP13054B) or A-law (TP3057B and TP13057B) and the fifth-order low-pass filter corrects for the (sin x)/x attenuation caused by the 8-kHz sample/hold. The filter is followed by a second-order RC active post-filter/power amplifier capable of driving a 600- $\Omega$  load to a level of 7.2 dBm. The receive section is unity gain. At FSR, the data at DR is clocked in on the falling edge of the next eight BCLKR (BCLKX) periods. At the end of the decoder time slot, the decoding cycle begins and 10  $\mu$ s later, the decoder DAC output is updated. The decoder delay is about 10  $\mu$ s (decoder update) plus 110  $\mu$ s (filter delay) plus 62.5  $\mu$ s (1/2 frame), or a total of approximately 180  $\mu$ s.

#### **APPLICATION INFORMATION**

#### power supplies

While the pins of the TP1305xB and TP305xB families are well protected against electrical misuse, it is recommended that the standard CMOS practice be followed, ensuring that ground is connected to the device before any other connections are made. In applications where the printed-circuit board can be plugged into a hot socket with power and clocks already present, an extra long ground pin in the connector should be used.

All ground connections to each device should meet at a common point as close as possible to ANLG GND. This minimizes the interaction of ground return currents flowing through a common bus impedance. V<sub>CC</sub> and V<sub>BB</sub> supplies should be decoupled by connecting 0.1- $\mu$ F decoupling capacitors to this common point. These bypass capacitors must be connected as close as possible to V<sub>CC</sub> and V<sub>BB</sub>.

For best performance, the ground point of each codec/filter on a card should be connected to a common card ground in star formation, rather than via a ground bus. This common ground point should be decoupled to  $V_{CC}$  and  $V_{BB}$  with 10-µF capacitors.

NOTE A: Transmit gain = 20 log  $\left(\frac{R1 + R2}{R2}\right)$ ,  $(R1 + R2) \ge 10 \text{ k}\Omega$

Figure 4. Typical Synchronous Application

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated