## PASSIVE USB-ISDN S/T-CONTROLLER

The information described in this document is the exclusive intellectual property of Winbond Electronics Corp and shall not be reproduced without permission from Winbond.

Winbond is providing this document only for reference purposes for W6694-based system design. Winbond assumes no responsibility for errors or omissions. All data and specifications are subject to change without notice.

# Electronics Corp.

# Table of Contents-

| 1. | GENERAL DESCRIPTION                                                                                            | 4   |

|----|----------------------------------------------------------------------------------------------------------------|-----|

| 2. | FEATURES                                                                                                       | 4   |

|    | ISDN                                                                                                           | 4   |

|    | USB                                                                                                            | 4   |

|    | Other Features                                                                                                 | 4   |

| 3. | PIN CONFIGURATION                                                                                              | 5   |

| 4. | PIN DESCRIPTION                                                                                                | 6   |

| 5. | SYSTEM DIAGRAM AND APPLICATIONS                                                                                | 8   |

| 6. | BLOCK DIAGRAM                                                                                                  | 9   |

| 7. | FUNCTIONAL DESCRIPTIONS                                                                                        | 9   |

|    | FUNCTIONAL DESCRIPTIONS         7.1 USB Descriptions                                                           | 9   |

|    | 7.1.1 Control-IN Transactions (Endpoint 0)                                                                     | 10  |

|    | 7.1.1 Control-IN Transactions (Endpoint 0)<br>7.1.2 Control-OUT Transactions (Endpoint 0)                      | 13  |

|    | 7.1.3 Bulk-OUT Transaction (Endpoint 1)                                                                        | .13 |

|    | 7.1.4 Bulk-IN Transaction (Endpoint 2)                                                                         | .14 |

|    | 7.1.5 Interrupt-IN Transaction (Endpoint 3)                                                                    |     |

|    | 7.1.6 Isochronous-OUT Transaction (Endpoint 4)                                                                 |     |

|    | 7.1.7 Isochronous-IN Transaction (Endpoint 5)                                                                  |     |

|    | 7.1.8 Suspend and Resume                                                                                       |     |

|    | 7.2 Configuration EEPROM                                                                                       |     |

| 8. | REGISTER DESCRIPTIONS                                                                                          |     |

|    | 8.1 Interrupt Registers                                                                                        |     |

|    | 8.1.1 Interrupt Status Register ISTA Read_clear                                                                |     |

|    | 8.1.2 Layer 1 Command/Indication Register CIR Read                                                             |     |

|    | 8.1.3 Monitor Channel Interrupt Status MOIR Read_clear                                                         |     |

|    | 8.1.4 PIO Input Change Register PICR Read_clear                                                                |     |

|    | 8.2 Chip and FIFO Control Registers                                                                            |     |

|    | 8.2.1 Interrupt Mask Register IMASK Read/Write Address 00h<br>8.2.2 Command Register 1 CMDR1 Write Address 01h |     |

|    | 8.2.3 Command Register 2 CMDR1 Write Address 011                                                               |     |

|    | 8.2.4 Control Register CTL Read/Write Address 03h                                                              |     |

|    | 8.2.5 Layer 1 Command/Indication Register CIX Read/Write Address 04h                                           |     |

|    | 8.2.6 U-layer1 Ready Code L1_RC Read/Write Address 05h                                                         |     |

|    | 8.3 GCI Mode Registers                                                                                         |     |

|    | 8.3.1 GCI Mode Command Register GCR Read/Write Address 06h                                                     |     |

|    | 8.3.2 Monitor Channel Control Register MOCR Read/Write Address 07h                                             |     |

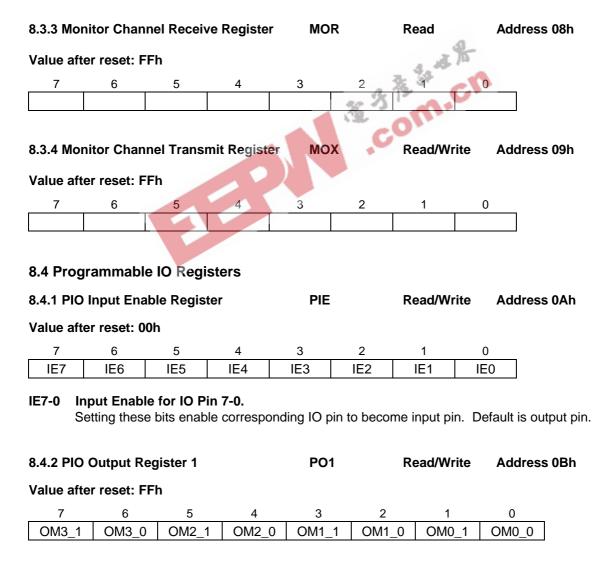

|    | 8.3.3 Monitor Channel Receive Register MOR Read Address 08h                                                    |     |

# Electronics Corp.

| 8.3.4                                                                                                | Monitor Channel Transmit Register                                                                                                                                                          | MOX Read/Write Address 09h       | 24                                                                   |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------|

| 8.4 Progra                                                                                           | mmable IO Registers                                                                                                                                                                        |                                  | 24                                                                   |

| 8.4.1                                                                                                | PIO Input Enable Register PIE F                                                                                                                                                            | Read/Write Address 0Ah           | 24                                                                   |

| 8.4.2                                                                                                | PIO Output Register 1 PO1 Rea                                                                                                                                                              | ad/Write Address 0Bh             | 24                                                                   |

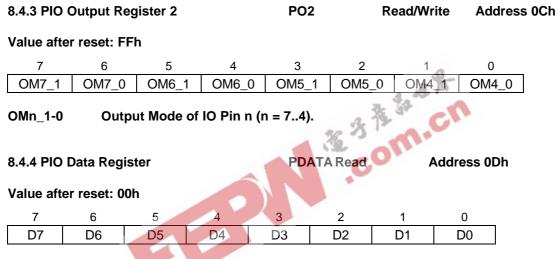

| 8.4.3                                                                                                | PIO Output Register 2 PO2 Rea                                                                                                                                                              | ad/Write Address 0Ch             |                                                                      |

| 8.4.4                                                                                                | PIO Data Register PDATA Read                                                                                                                                                               | d Address 0Dh                    | 25                                                                   |

| 8.5 B Char                                                                                           | nnel Switch Registers                                                                                                                                                                      |                                  | 25                                                                   |

|                                                                                                      |                                                                                                                                                                                            | er L1B1RS Read/Write Address 0Eh |                                                                      |

| 8.5.2 l                                                                                              | Layer1 B2 Receiver Select Registe                                                                                                                                                          | er L1B2RS Read/Write Address 0Fh |                                                                      |

| 8.5.3                                                                                                | USB B1 Receiver Select Register                                                                                                                                                            | USBB1RS Read/Write Address 10h   |                                                                      |

| 8.5.4                                                                                                | USB B2 Receiver Select Register                                                                                                                                                            | USBB2RS Read/Write Address 11h   |                                                                      |

| 8.5.5                                                                                                | PCM1 Receiver Select Register I                                                                                                                                                            | PCM1RS Read/Write Address 12h    |                                                                      |

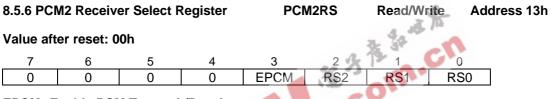

| 8.5.6                                                                                                | PCM2 Receiver Select Register I                                                                                                                                                            | PCM2RS Read/Write Address 13h    |                                                                      |

|                                                                                                      | 0                                                                                                                                                                                          |                                  |                                                                      |

| 9. ELECTRIC                                                                                          |                                                                                                                                                                                            | A                                | 27                                                                   |

| 9. ELECTRIC<br>9.1 Absolu                                                                            |                                                                                                                                                                                            | A                                | 27                                                                   |

| 9. ELECTRIC<br>9.1 Absolu<br>9.2 Power                                                               |                                                                                                                                                                                            | A                                | 27                                                                   |

| 9. ELECTRIC<br>9.1 Absolu<br>9.2 Power<br>9.3 DC Ch                                                  |                                                                                                                                                                                            | A                                | 27                                                                   |

| 9.1 Absolu<br>9.2 Power<br>9.3 DC Ch<br>9.4 Prelimi                                                  | CAL CHARACTERISTICS                                                                                                                                                                        |                                  |                                                                      |

| 9.1 Absolu<br>9.2 Power<br>9.3 DC Ch<br>9.4 Prelimi                                                  | CAL CHARACTERISTICS                                                                                                                                                                        |                                  |                                                                      |

| 9.1 Absolu<br>9.2 Power<br>9.3 DC Ch<br>9.4 Prelimi<br>9.4.1                                         | CAL CHARACTERISTICS<br>Ite Maximum Rating<br>Supply<br>aracteristics<br>inary Switching Characteristics<br>PCM Interface Timing                                                            | A                                | 27<br>27<br>28<br>28<br>28<br>30<br>30                               |

| 9.1 Absolu<br>9.2 Power<br>9.3 DC Ch<br>9.4 Prelimi<br>9.4.1 I<br>9.4.2 3                            | CAL CHARACTERISTICS<br>te Maximum Rating<br>Supply<br>aracteristics<br>inary Switching Characteristics<br>PCM Interface Timing<br>Serial EEPROM Timing                                     |                                  | 27<br>27<br>28<br>28<br>28<br>30<br>30<br>30<br>31                   |

| 9.1 Absolu<br>9.2 Power<br>9.3 DC Ch<br>9.4 Prelimi<br>9.4.1 I<br>9.4.2 3                            | CAL CHARACTERISTICS<br>te Maximum Rating<br>Supply<br>aracteristics<br>inary Switching Characteristics<br>PCM Interface Timing<br>Serial EEPROM Timing<br>NG INFORMATION                   |                                  | 27<br>27<br>28<br>28<br>28<br>30<br>30<br>31<br>31<br>32             |

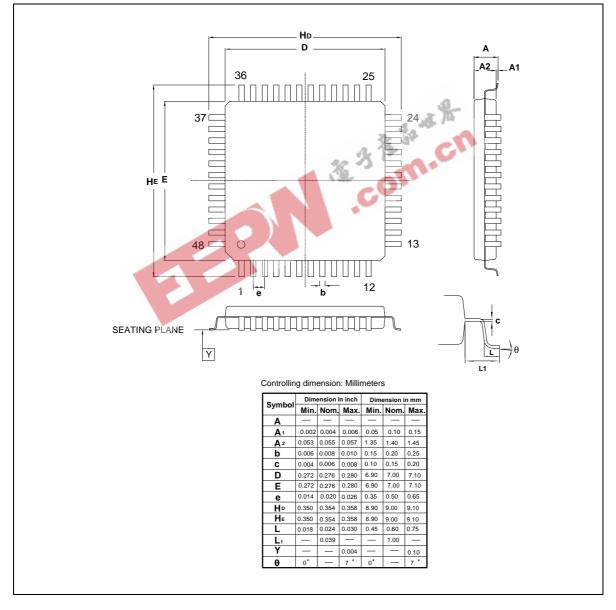

| 9.1 Absolu<br>9.2 Power<br>9.3 DC Ch<br>9.4 Prelimi<br>9.4.1<br>9.4.2 3<br>10. ORDERII<br>11. PACKAG | CAL CHARACTERISTICS<br>te Maximum Rating<br>Supply<br>aracteristics<br>inary Switching Characteristics<br>PCM Interface Timing<br>Serial EEPROM Timing<br>NG INFORMATION<br>BE INFORMATION |                                  | 27<br>27<br>28<br>28<br>28<br>30<br>30<br>30<br>31<br>31<br>32<br>33 |

| 9.1 Absolu<br>9.2 Power<br>9.3 DC Ch<br>9.4 Prelimi<br>9.4.1<br>9.4.2 3<br>10. ORDERII<br>11. PACKAG | CAL CHARACTERISTICS<br>te Maximum Rating<br>Supply<br>aracteristics<br>inary Switching Characteristics<br>PCM Interface Timing<br>Serial EEPROM Timing<br>NG INFORMATION<br>BE INFORMATION |                                  | 27<br>27<br>28<br>28<br>28<br>30<br>30<br>30<br>31<br>31<br>32<br>33 |

# Electronics Corp.

### **1. GENERAL DESCRIPTION**

The Winbond's single chip USB bus ISDN S/T interface controller W6694 is an all-in-one device suitable for ISDN Internet access. The integrated USB and ISDN design provides low cost, pure passive solution for USB-IDSN application.

W6694 also provides two PCM CODEC interfaces for the ability to access ISDN through voice channel.

·Com.cn

### 2. FEATURES

#### ISDN

- Full duplex 2B+D S/T-interface transceiver compatible with ITU-T I.430 Recommendation

- -Four wire operation

- Received clock recovery

- -Layer 1 activation/deactivation procedure

- D channel access control

- Transparent data transmission of 2B+D channels

- Test functions

#### USB

- USB Specification version 1.0/1.1 compliant

- Full-speed, bus-powered USB device

- Integrated transceiver, PLL, SIE, SIL and voltage regulator

- · Built-in fully automatic enumeration procedure

- Support suspend mode

- Suspend current requirement

- -Wake-up by ISDN (remote) and PC (host)

#### **Other Features**

- GCI bus interface (slave mode) for connecting to ISDN U transceiver chip.

- PCM port provides two 64K clear channels to connect to PCM CODEC chips.

- B channel data switching function for selective connection between ISDN/GCI interface, USB and PCM.

- EEPROM interface for retrieving customized USB device identification data.

- IO pins with LED current drive capability.

- Reset pin for whole-chip reset.

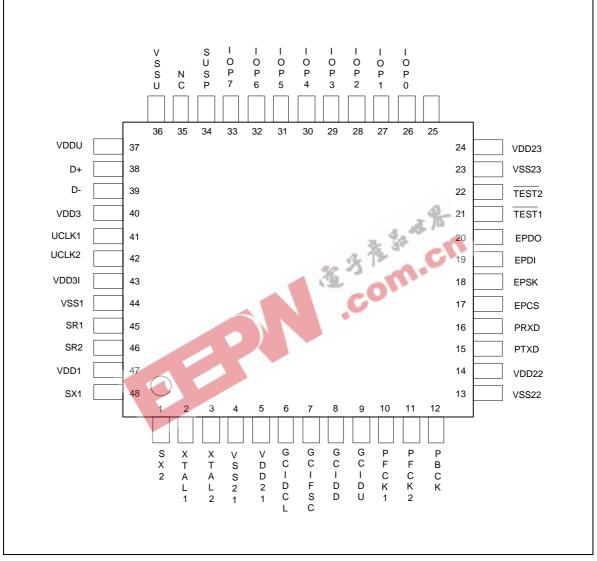

## **3. PIN CONFIGURATION**

FIG.3.1 W6694 Pin Out

## 4. PIN DESCRIPTION

## Table 4.1 W6694 Pin Descriptions

| SYMBOL                      | PIN NO. | I/O    | FUNCTION                                                                                 |  |  |  |

|-----------------------------|---------|--------|------------------------------------------------------------------------------------------|--|--|--|

| USB Bus                     |         |        |                                                                                          |  |  |  |

| D+ 38 I/O USB D+ data line. |         |        |                                                                                          |  |  |  |

| D-                          | 39      | I/O    | USB D- data line.                                                                        |  |  |  |

| UCLK1                       | 41      | -      | 24 MHz crystal/oscillator clock input.                                                   |  |  |  |

| UCLK2                       | 42      | 0      | 24 MHz crystal clock output. Left unconnected if use oscillator.                         |  |  |  |

|                             |         | ISDN S | Signals and External Crystal                                                             |  |  |  |

| SR1                         | 45      | I      | S/T bus receiver input (-). This is normal polarity. Reverse polarity is also OK.        |  |  |  |

| SR2                         | 46      | I      | S/T bus receiver input (+).                                                              |  |  |  |

| SX1                         | 48      | 0      | S/T bus transmitter output(+).                                                           |  |  |  |

| SX2                         | 1       | 0      | S/T bus transmitter output(-).                                                           |  |  |  |

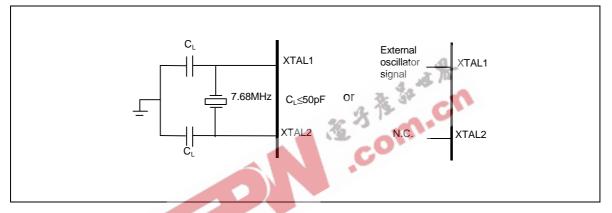

| XTAL1                       | 2       |        | Crystal or Oscillator clock input. The clock frequency: 7.68 MHz $\pm 100$ PPM.          |  |  |  |

| XTAL2                       | 3       | 0      | Crystal clock output. Left unconnected when using oscillator.                            |  |  |  |

|                             |         |        | GCI Bus                                                                                  |  |  |  |

| GCIDCL                      | 6       | I      | GCI bus data clock 1.536 MHz.                                                            |  |  |  |

| GCIFSC                      | 7       | Ι      | GCI bus frame synchronization clock.                                                     |  |  |  |

| GCIDD                       | 8       | -      | GCI bus data downstream. (input)                                                         |  |  |  |

| GCIDU                       | 9       | 0      | GCI bus data upstream. (output)                                                          |  |  |  |

|                             |         |        | PCM Bus                                                                                  |  |  |  |

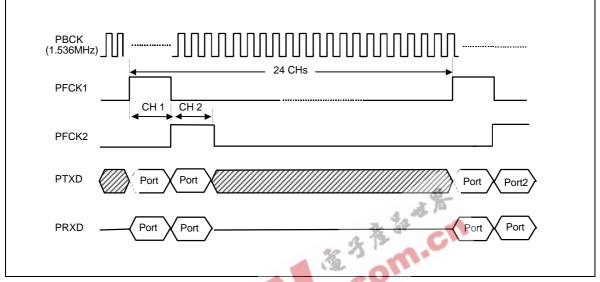

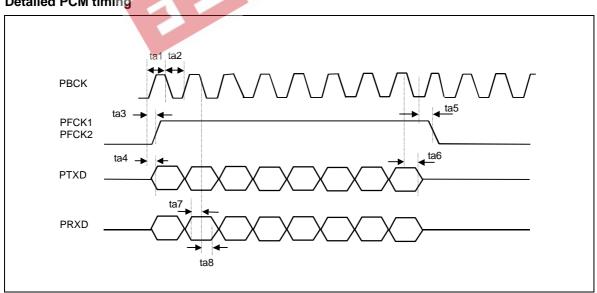

| PFCK1                       | 10      | 0      | PCM port 1 frame synchronization signal with 8 KHz repetition rate and 8 bit pulse width |  |  |  |

| PFCK2                       | 11      | 0      | PCM port 2 frame synchronization signal with 8 KHz repetition rate and 8 bit pulse width |  |  |  |

| РВСК                        | 12      | 0      | PCM bit clock of 1.536 MHz.                                                              |  |  |  |

| PTXD                        | 15      | 0      | PCM data output.                                                                         |  |  |  |

| PRXD                        | 16      | I      | PCM data input.                                                                          |  |  |  |

| . Pin Description, continued     |                                            |     |                                                                                     |  |  |  |

|----------------------------------|--------------------------------------------|-----|-------------------------------------------------------------------------------------|--|--|--|

| SYMBOL                           | PIN NO.                                    | I/O | FUNCTION                                                                            |  |  |  |

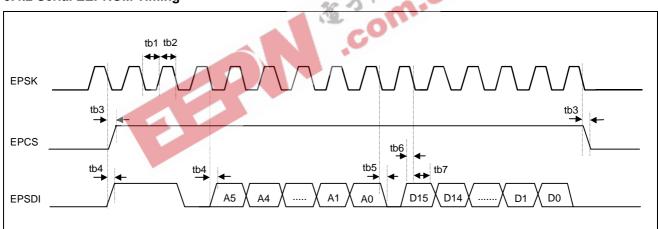

| External Serial EEPROM Interface |                                            |     |                                                                                     |  |  |  |

| EPCS                             | EPCS   17   O   Serial EEPROM chip select. |     |                                                                                     |  |  |  |

| EPSK                             | 18                                         | 0   | Serial EEPROM data clock.                                                           |  |  |  |

| EPDI                             | 19                                         | -   | Serial EEPROM data input                                                            |  |  |  |

| EPDO                             | 20                                         | 0   | Serial EEPROM data output                                                           |  |  |  |

|                                  |                                            | Pov | ver and Ground                                                                      |  |  |  |

| VDD1,VSS1                        | 47, 44                                     | I   | ISDN S/T analog power (5V), Ground                                                  |  |  |  |

| VDD21, VSS21                     | 5, 4                                       | I   | Digital power (5V), Ground                                                          |  |  |  |

| VDD22, VSS22                     | 14, 13                                     |     |                                                                                     |  |  |  |

| VDD23, VSS23                     | 24, 23                                     |     |                                                                                     |  |  |  |

| VDDU, VSSU                       | 37, 36                                     | Ι   | USB core power (5V), Ground                                                         |  |  |  |

| VDD3                             | 40                                         | 0   | Regulator output (3.3V)                                                             |  |  |  |

| VDD3I                            | 43                                         | Ι   | Regulator input (3.3V)                                                              |  |  |  |

|                                  |                                            |     | IO Pins                                                                             |  |  |  |

| IOP0                             | 26                                         | I/O | IO pin capable of driving LED.                                                      |  |  |  |

| IOP1                             | 27                                         | 1/0 |                                                                                     |  |  |  |

| IOP2                             | 28                                         | 1/0 |                                                                                     |  |  |  |

| IOP3                             | 29                                         | 1/0 |                                                                                     |  |  |  |

| IOP4                             | 30                                         | 1/0 |                                                                                     |  |  |  |

| IOP5                             | 31                                         | I/O |                                                                                     |  |  |  |

| IOP6                             | 32                                         | I/O |                                                                                     |  |  |  |

| IOP7                             | 33                                         | I/O |                                                                                     |  |  |  |

|                                  | -                                          |     | Others                                                                              |  |  |  |

| RESET                            | 25                                         | Ι   | External reset. Cause internal circuit reset. Internal 10k ohm pull-up is provided. |  |  |  |

| TEST1, TEST2                     | 21, 22                                     | Ι   | Test mode enable. Connected to HIGH for normal operation.                           |  |  |  |

| SUSP                             | 34                                         | 0   | USB suspended. Active HIGH                                                          |  |  |  |

|                                  |                                            |     | NC                                                                                  |  |  |  |

| NC                               | 35                                         |     | No connection. Internal pull-up is provided.                                        |  |  |  |

# Winbond Electronics Corp.

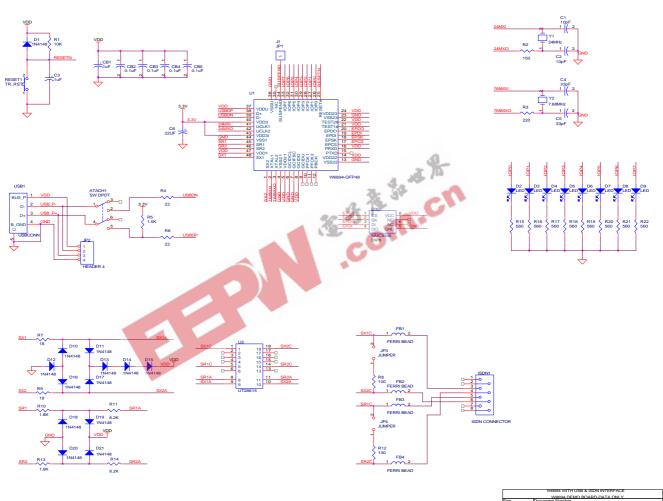

## **5. SYSTEM DIAGRAM AND APPLICATIONS**

Typical applications include:

- •

- USB passive TA for data only service USB passive TA with one data plus one voice •

ize 15.20X12

Fig. 5.1 USB Passive TA Orcad Schematic

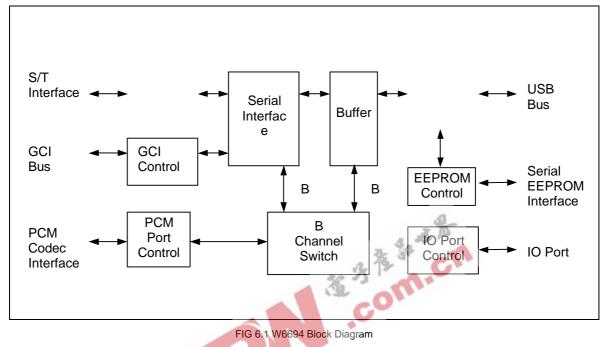

## 6. BLOCK DIAGRAM

## 7. FUNCTIONAL DESCRIPTIONS

### 7.1 USB Descriptions

| END<br>POINT | TYPE      | DIRECTION* | MAX. PACKET SIZE<br>(BYTES) | INTERNAL BUFFER TYPE AND<br>SIZE |

|--------------|-----------|------------|-----------------------------|----------------------------------|

|              |           |            |                             | (BYTES)                          |

| 0            | Control   | IN/OUT     | 8/8                         | 8, single port x 2               |

| 1            | Bulk      | OUT        | 8                           | 8, single port x 1               |

| 2            | Bulk      | IN         | 8                           | 8, single port x 1               |

| 3            | Interrupt | IN         | 5                           | 5, single port x 1               |

| 4            | Isoch.    | OUT        | (1+3) +                     | 96, dual port x 1                |

|              |           |            | (1+18) = 23                 |                                  |

| 5            | lsoch.    | IN         | 1+ (1+7) + (1+15) +         | 96, dual port x 1                |

|              |           |            | (1+15) = 41                 |                                  |

\* Direction: IN - device to host, OUT - host to device

USB standard requests are supported by W6694, and W6694 will respond to requests according to USB specification revesion 1.1. These includes "CLEAR\_FEATURE, GET\_CONFIGURATION, GET\_DESCRIPTOR, GET\_INTERFACE, GET\_STATUS, SET\_ADDRESS, SET\_CONFIGURATION, SET\_DESCRIPTOR, SET\_FEATURE, SET\_INTERFACE". The "SYNC\_FRAME" request is not supported.

### 7.1.1 Control-IN Transactions (Endpoint 0)

| OFFSET | FIELD             | SIZE | DEFAULT VALUE<br>(HEX) | UPDATED BY EEPROM                                                                                               |

|--------|-------------------|------|------------------------|-----------------------------------------------------------------------------------------------------------------|

| 0      | bLength           | 1    | 12                     |                                                                                                                 |

| 1      | bDescriptorType   | 1    | 01                     |                                                                                                                 |

| 2      | bcdUSB            | 2    | 0110                   | A                                                                                                               |

| 4      | bDeviceClass      | 1    | FF 🔥 👗                 | The second se |

| 5      | bDeviceSubClass   | 1    | 00                     | -0-                                                                                                             |

| 6      | bDeviceProtocol   | 1    | 00                     |                                                                                                                 |

| 7      | bMaxPacketSize    | 1    | 80.8                   |                                                                                                                 |

| 8      | idVendor          | 2    | 1046                   | Yes *                                                                                                           |

| 10     | idProduct         | 2    | 6694                   | Yes *                                                                                                           |

| 12     | bcdDevice         | 2    | 0100                   | Yes *                                                                                                           |

| 14     | iManufacturer     | 1    | 00                     |                                                                                                                 |

| 15     | iProduct          | 1    | 01                     |                                                                                                                 |

| 16     | iSerialNumber     | 1    | 00                     |                                                                                                                 |

| 17     | bNumConfiguration | 1    | 01                     |                                                                                                                 |

7.1.1.1 Get Device Descriptor

\* Note: Refer to EEPROM session for its layout of contents.

#### 7.1.1.2 Get Configuration Descriptor

| OFFSET | FIELD                    | SIZE | VALUE (HEX) | REMARK        |  |  |  |  |

|--------|--------------------------|------|-------------|---------------|--|--|--|--|

|        | Configuration Descriptor |      |             |               |  |  |  |  |

| 0      | bLength                  | 1    | 09          |               |  |  |  |  |

| 1      | bDescriptorType          | 1    | 02          |               |  |  |  |  |

| 2      | wTotalLength             | 2    | 003E        | 62            |  |  |  |  |

| 4      | bNumInterface            | 1    | 01          |               |  |  |  |  |

| 5      | bConfigurationValue      | 1    | 01          |               |  |  |  |  |

| 6      | iConfiguration           | 1    | 00          |               |  |  |  |  |

| 7      | bmAttributes             | 1    | A0          | Bus Powered,  |  |  |  |  |

|        |                          |      |             | Remote Wakeup |  |  |  |  |

| 8      | MaxPower                 | 1    | 32          | 100 mA        |  |  |  |  |

### **Winbond** Electronics Corp.

#### 7.1.1.2 Get Configuration Descriptor, continued

| OFFSET | FIELD              | SIZE      | VALUE (HEX)          | REMARK |

|--------|--------------------|-----------|----------------------|--------|

|        | ·                  | Interfa   | ce 0 Descriptor      |        |

| 0      | bLength            | 1         | 09                   |        |

| 1      | bDescriptorType    | 1         | 04                   |        |

| 2      | bInterfaceNumber   | 1         | 00                   |        |

| 3      | bAlternateSetting  | 1         | 00                   |        |

| 4      | bNumEndpoints      | 1         | 00                   |        |

| 5      | bInterfaceClass    | 1         | FF                   |        |

| 6      | bInterfaceSubClass | 1         | 00                   |        |

| 7      | bInterfaceProtocol | 1         | 00                   |        |

| 8      | iInterface         | 1         | 00                   |        |

|        | Alte               | ernate In | terface 0 Descriptor | e_     |

| 0      | bLength            | 1         | 09                   | Ju .   |

| 1      | bDescriptorType    | 1         | 04                   | 15     |

| 2      | bInterfaceNumber   | 1         | 00                   |        |

| 3      | bAlternateSetting  | 1         | 01_0                 |        |

| 4      | bNumEndpoints      | 1         | 05                   |        |

| 5      | bInterfaceClass    | 1         | FF                   |        |

| 6      | bInterfaceSubClass | 1         | 00                   |        |

| 7      | bInterfaceProtocol | 1         | 00                   |        |

| 8      | iInterface         | 1         | 00                   |        |

|        |                    | Endpo     | int 1 Descriptor     |        |

| 0      | bLength            | 1         | 07                   |        |

| 1      | bDescriptorType    | 1         | 05                   |        |

| 2      | bEndpointAddress   | 1         | 01                   | OUT    |

| 3      | bmAttributes       | 1         | 02                   | Bulk   |

| 4      | wMaxPacketSize     | 2         | 0008                 |        |

| 6      | bInterval          | 1         | 00                   |        |

|        |                    | Endpo     | int 2 Descriptor     |        |

| 0      | bLength            | 1         | 07                   |        |

| 1      | bDescriptorType    | 1         | 05                   |        |

| 2      | bEndpointAddress   | 1         | 82                   | IN     |

| 3      | bmAttributes       | 1         | 02                   | Bulk   |

| 4      | wMaxPacketSize     | 2         | 0008                 |        |

| 6      | bInterval          | 1         | 00                   |        |

### **Winbond** Electronics Corp.

| OFFSET                | FIELD            | SIZE  | VALUE (HEX)      | REMARK      |  |  |  |

|-----------------------|------------------|-------|------------------|-------------|--|--|--|

| Endpoint 3 Descriptor |                  |       |                  |             |  |  |  |

| 0                     | bLength          | 1     | 07               |             |  |  |  |

| 1                     | bDescriptorType  | 1     | 05               |             |  |  |  |

| 2                     | bEndpointAddress | 1     | 83               | IN          |  |  |  |

| 3                     | bmAttributes     | 1     | 03               | Interrupt   |  |  |  |

| 4                     | wMaxPacketSize   | 2     | 0005             |             |  |  |  |

| 6                     | bInterval        | 1     | 01               |             |  |  |  |

|                       |                  | Endpo | int 4 Descriptor |             |  |  |  |

| 0                     | bLength          | 1     | 07               |             |  |  |  |

| 1                     | bDescriptorType  | 1     | 05               |             |  |  |  |

| 2                     | bEndpointAddress | 1     | 04               | 🚛 OUT       |  |  |  |

| 3                     | bmAttributes     | 1     | 01               | Isochronous |  |  |  |

| 4                     | wMaxPacketSize   | 2     | 0017             | 25          |  |  |  |

| 6                     | bInterval        | 1     | 01               |             |  |  |  |

|                       |                  | Endpo | int 5 Descriptor |             |  |  |  |

| 0                     | bLength          | 1     | 07               |             |  |  |  |

| 1                     | bDescriptorType  | 1     | 05               |             |  |  |  |

| 2                     | bEndpointAddress | 1     | 85               | IN          |  |  |  |

| 3                     | bmAttributes     | 1     | 01               | Isochronous |  |  |  |

| 4                     | wMaxPacketSize   | 2     | 0029             |             |  |  |  |

| 6                     | bInterval        | 1     | 01               |             |  |  |  |

Note: After W6694 is successfully enumerated by the USB host, software must issue SET\_INTERFACE request with alternate setting 1, to enable all endpoints. When in default state (alternate setting 0), only endpoint 0 is functioning.

#### 7.1.1.3 Get String Descriptor 0

| OFFSET | FIELD           | SIZE | VALUE (HEX) | DESCRIPTION  |

|--------|-----------------|------|-------------|--------------|

| 0      | bLength         | 1    | 04          |              |

| 1      | bDescriptorType | 1    | 03          |              |

| 2      | wLanguage ID    | 2    | 0409        | U.S. English |

### 7.1.1.4 Get String Descriptor 1 (Product)

| OFFSET | FIELD           | SIZE (HEX) | VALUE (HEX) | STRING (UNICODE) |

|--------|-----------------|------------|-------------|------------------|

| 0      | bLength         | 1          | 18          |                  |

| 1      | bDescriptorType | 1          | 03          |                  |

| 2      | bString         | 16         |             | "USB ISDN TA"    |

### 7.1.2 Control-OUT Transactions (Endpoint 0)

#### 7.1.2.1 Device Clear Feature, Remote Wake-up

| BmRequestType | bRequest      | wValue | wIndex | wLength | Data |

|---------------|---------------|--------|--------|---------|------|

| 00H           | CLEAR_FEATURE | 1      | 0      | 0       | None |

On received this request from host, W6694 will not detect the incoming ISDN broadcast message.

#### 7.1.2.2 Device Set Feature, Remote Wake-up

| BmRequestType | bRequest    | wValue | wIndex | wLength | Data |

|---------------|-------------|--------|--------|---------|------|

| 00H           | SET_FEATURE | 1      | 0      | 0       | None |

On received this request from host, W6694 will detect the incoming ISDN broadcast message. This is default setting.

2 32 3

#### 7.1.2.3 Set Interface 0, Alternate Setting 0

| bmRequestType | bRequest      | wValue | windex | wLength | Data |

|---------------|---------------|--------|--------|---------|------|

| 01H           | SET_INTERFACE | 0      | 0      | 0       | None |

On received this request from host, all endpoints except endpoint 0 are disabled. Also the B1/B2 channel FIFOs are reset and disabled. This is default setting.

#### 7.1.2.4 Set Interface 0, Alternate Setting 1

| bmRequestType | bRequest      | wValue | wIndex | wLength | Data |

|---------------|---------------|--------|--------|---------|------|

| 01H           | SET_INTERFACE | 1      | 0      | 0       | None |

On received this request from host, W6694 will enable the B1/B2 channel XFIFO and RFIFO.

#### 7.1.3 Bulk-OUT Transaction (Endpoint 1)

Bulk-OUT endpoint is used to write data to register or/and index which register to be read in following Bulk-IN transaction. A pare of two bytes (Address, Data) in Bulk-OUT data packet represents a read or write command on one register. A maximum of 8 bytes consist one Bulk-OUT transaction. W6694 perform the read/write commands following their order in the packet.

#### Data packet for Bulk-OUT transaction:

| Offset 0     | 1     | 2            | 3     | 4            | 5     | 6            | 7     |

|--------------|-------|--------------|-------|--------------|-------|--------------|-------|

| address<br>1 | data1 | address<br>2 | data2 | address<br>3 | data3 | address<br>4 | data4 |

Address byte will indicate the read or write action to that register, by assigning highest order bit (bit 7) to 0 (read) or 1 (write).

#### Contents of address byte:

| Bit 7 | 6 | 5 | 4  | 3  | 2  | 1  | 0  |

|-------|---|---|----|----|----|----|----|

| 0/1   | 0 | 0 | A4 | A3 | A2 | A1 | A0 |

Bit 7: 0/1 = Read/Write

Bit 4-0: Address offset of register.

The data byte is the write data (write operation) or 00h (read operation).

#### 7.1.4 Bulk-IN Transaction (Endpoint 2)

Bulk-IN endpoint is for retrieving register data of W6694. It returns the registers data that are requested by most recent Bulk-OUT data-read request. Inside the data packet, one register occupies 2 bytes. The first is register's offset address, the 2<sup>nd</sup> byte is date. A maximum of 4 register data can be sent to host in one Bulk-IN packet.

| Offset 0     | 1     | 2            | 3     | 4            | 5 🔔   | 6            | 7     |

|--------------|-------|--------------|-------|--------------|-------|--------------|-------|

| address<br>1 | data1 | address<br>2 | data2 | address<br>3 | data3 | address<br>4 | data4 |

#### 7.1.5 Interrupt-IN Transaction (Endpoint 3)

Interrupt-IN endpoint is used to periodically poll device interrupt data. W6694 use this endpoint to report interrupt status of all interrupt sources. All four bytes data of interrupt registers will be sent to host if ISTA is not 0. If no interrupt is detected by W6694 when received Interrupt-IN token, A NAK token will return to the USB host.

Data packet for Interrupt-IN transaction:

| Offset 0 | 1   | 2    | 3     | 4    |

|----------|-----|------|-------|------|

| ISTA     | CIR | PICR | PDATA | MOIR |

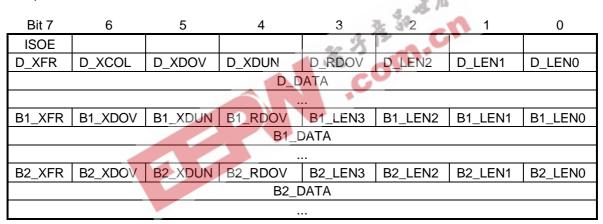

#### 7.1.6 Isochronous-OUT Transaction (Endpoint 4)

After power-on or hardware reset, all B and D channels transmit FIFO (XFIFO) are disabled. A disabled XFIFO can not receive data from USB. But the transmitter will automatically send inter frame time fill pattern (all 1's) to ISDN interface. The disabled XFIFO can be enabled by command XEN on each channel. An enabled XFIFO can receive data from USB, and send data to the USB host.

Software decides the size of data to transmit depending on available XFIFO space, which is indicated by XFR flag carried by Isochronous-IN packet. When XFR is reported to host, it means that XFIFO has at least half of the total XFIFO size available for that channel. Each channel has its own XFIFO and status flags.

If the incoming Isochronous-OUT packet is detected error, some action will be automatically taken for D and B channel XFIFO. For D channel, the XFIFO is reset and automatically enabled. For B channel, the XFIFO are not reset, and the data remained in XFIFO are still valid and will be transmitted to ISDN later. But the new incoming B channel data will be replaced by FFh, and stored

into XFIFO. The continuous FFh will later be transmitted to corresponding B channel of ISDN interface. This Isochronous-OUT packet error will be reported to host, by setting bit ISOE of Isochronous-IN packet to 1. D channel FIFO will recognize and only accept data within HDLC frame (including opening and closing flag), all other data outside HDLC frame are ignored and not stored in FIFO. B channel FIFO accept any data after it is enabled.

Note: Because B1 and B2 channel data are of the same length (B\_LEN), both channels should be reset/enabled at the same time.

| Bit 7                         | 6                             | 5 | 4   | 3                        | 2      | 1      | 0      |  |  |

|-------------------------------|-------------------------------|---|-----|--------------------------|--------|--------|--------|--|--|

|                               |                               |   |     |                          |        | D_LEN1 | D_LEN0 |  |  |

|                               |                               |   |     | A (1 <sup>st</sup> byte) |        |        |        |  |  |

|                               | D_DATA (2 <sup>nd</sup> byte) |   |     |                          |        |        |        |  |  |

| D_DATA (3 <sup>rd</sup> byte) |                               |   |     |                          |        |        |        |  |  |

|                               |                               |   |     | B_LEN3                   | B_LEN2 | B_LEN1 | B_LEN0 |  |  |

|                               |                               |   | B1_ | DATA                     | -ðc    | 34     |        |  |  |

|                               |                               |   |     |                          | 272    | 6      |        |  |  |

|                               | B2_DATA                       |   |     |                          |        |        |        |  |  |

|                               |                               |   |     |                          | CO     | -      |        |  |  |

|                               |                               |   |     |                          |        |        |        |  |  |

The packet format of Isochronous-OUT is as below:

#### D\_LEN1-0 D Channel Data Length

These bits indicate the data length of the subsequent data for D channel. The typical value is 1 to 3, if D channel message is sending; or 0 if no message to send. Once the opening flag of D channel message is sent, W6694 will move the data in D-XFIFO to S interface at the rate of 16K bps. The software must carefully assign proper length for each packet, otherwise a D-XFIFO under-run or overflow condition may occur. The only valid data are HDLC frame, including opening and closing flag (7Eh), and bit-stuffed data in between. Note that software should transmit the first data byte as opening flag in byte (8-bits) boundary. Due to the nature of HDLC framing, the closing flag may not be in byte-boundary. Software should stuff the remaining bit positions (if any) with binary '1', to fill the last byte, unless the last byte is 7Eh.

#### D\_DATA D Channel Data

These are D channel data space, which always occupy 3 bytes in the packet. Software should put actual data length in D\_LEN. If the data length D\_LEN is less then 3, the remaining data bytes should be all FFh.

#### B\_LEN3-0 B Channel Data Length

These bits indicate the data length of subsequent data for each B channel. Once the B-XFIFO is enabled (CMDR2:BnXEN), the length should be from 7 to 9 bytes inclusively, otherwise a transmit FIFO under run or overflow condition may occur. If there is no data for B1/B2 channel, the length can be 0. Note that the two B channels have same data length, but can be reset and enabled separately.

#### B1\_DATA B1 Channel Data

These are B1 channel data, the length is indicated by B\_LEN.B2\_DATAB2 Channel Data

These are B2 channel data, the length is indicated by B\_LEN.

#### 7.1.7 Isochronous-IN Transaction (Endpoint 5)

After power on or reset, all B and D channels receive FIFO (RFIFO) are disabled. A disabled RFIFO can not receive data from ISDN, and will always return zero-length data for Isochronous-IN transaction. RFIFO can only be enabled by command CMDR:REN. Once enabled, an Isochronous-IN transaction can read data from RFIFO of that channel. The data packet also carries XFIFO status for that channel, and the most recent Isochronous-OUT packet error status (if error ever occurred). Note that since B1 and B2 channel output length is the same in Isochronous-OUT packet, the XFIFO status of B1/B2 channels are the same.

The packet format of Isochronous-IN is as below:

#### ISOE Isochronous-OUT Error

This bit is set to indicate that the most recent received Isochronous-OUT packet has CRC error. This bit will remain set, until a CMDR1:CISOE clears it.

#### XCOL Transmit Collision (D channel only)

This bit indicates a D channel collision on the S-bus has been detected. The data in D channel XFIFO will be automatically re-transmitted, until the whole HDLC frame are successfully transmitted. This bit will remain set, until software issue CMDR1:DXEN to clear this bit.

#### XFR Transmit FIFO Ready

It is set when XFIFO has at least half of the XFIFO size available for incoming USB data.

#### XDUN Transmit Data Under-run

The corresponding XFIFO has run out of data. For D and B channel, the XFIFO is reset and disabled for that channel. This bit is cleared when XFIFO is enabled by XEN bit.

# Electronics Corp.

#### **XDOV Transmit Data Overflow**

The corresponding XFIFO has overflow condition. Data in XFIFO are overwritten by incoming USB data. For D and B channel, the XFIFO is reset and disabled for that channel. This bit is cleared when XFIFO is enabled by XEN bit.

#### **RDOV Receive Data Overflow**

The corresponding RFIFO has overflow condition. Data in RFIFO are overwritten by incoming ISDN data. When overflow condition occurred, the D and B channel RFIFO is reset and disabled for that channel. This bit is cleared when RFIFO is enabled by REN bit.

#### 7.1.8 Suspend and Resume

W6694 supports USB suspend and resume function as described in USB specification 1.1. When there is more than three millisecond period of inactivity on the USB, W6694 will automatically enter into a low-power suspend state. In this state, most of the ISDN and USB module will be powered off to consume minimum power. But the internal register values are preserved. Therefore it is recommended that the software perform necessary control to W6694 before power-down. The W6694 will leave suspend mode only when one of the two condition happens: host or device wake-up. A ISTA:WAKE bit will indicate to software which source the wake-up event is originated from.

#### (i). Host-Initiated Wake-up

The USB host may wake-up W6694 by sending traffic on USB. On detected this wake-up signal, W6694 will automatically resume to normal operation.

#### (ii). Device Remote Wake-up

In suspend mode, W6694 will ignore any ISDN traffic on S/T bus, except for incoming broadcast messages. When there is an incoming broadcast message from ISDN switch, such as SETUP message, W6694 will automatically wake-up, and signal the USB host that it has left suspend mode. The incoming SETUP message will be saved in D channel RFIFO. After returning from suspend mode, software should immediately read the RFIFO, and perform necessary operation as specified in ISDN protocol.

#### 7.2 Configuration EEPROM

**EEPROM** wire connection:

A 9346/93C46 type serial EEPROM can be used to store customized USB device configuration data. These configuration data will be read by W6694 after power on or reset, and sent to the USB host during enumeration. If EEPROM is not presented, or the first 16 bits in EEPROM is FFFFh, the default value in W6694 will be sent to the USB host instead.

#### W6694 EEPROM EPCS EPSK EPD EPDI EPDI EPDI EPDI EPDI EPCS Data In Data Out

#### **EEPROM Contents :**

| Offse | Size   | Contents              |

|-------|--------|-----------------------|

| t     |        | 15                    |

|       | (Byte) | 0                     |

| 0     | 2      | Vendor ID             |

| 2     | 2      | Device ID             |

| 4     | 2      | Device release number |

#### 8. REGISTER DESCRIPTIONS

#### 8.1 Interrupt Registers

These registers will be read by Interrupt-IN packet only, so the USB host will periodically receive these data. These registers can not be read by Bulk-IN transfer.

# 8.1.1 Interrupt Status Register ISTA Read\_clear

This register indicates interrupt occurred in various interrupt sources. This register is cleared automatically after it is read and successfully ACKed by the USB host.

#### Values after reset: 00h

| 7   | 6   | 5     | 4 | )`a | 2 | 1 | 0 |

|-----|-----|-------|---|-----|---|---|---|

| ICC | MOC | PIOIC | 0 |     | 0 | 0 | 0 |

#### ICC Layer 1 Indication Code Change

A change of value in the received indication code has been detected. The new code is in Layer 1 Command/Indication Register (CIR) register.

#### MOC Monitor Channel Status Change

A change of value in the GCI mode Monitor Channel Interrupt Register (MOIR) has occurred.

#### PIOIC Programmable IO Port Input Signal Changed

A change of value in at least one input IO pin is detected. The input IO pins that change value can be identified in PIO Input Change Register (PICR) register.

#### 8.1.2 Layer 1 Command/Indication Register CIR Read

#### Value after reset: 0Fh

| 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|---|---|---|---|------|------|------|------|

| 0 | 0 | 0 | 0 | CIR3 | CIR2 | CIR1 | CIR0 |

#### CIR3-0 Layer 1 Indication Code

Value of the received layer 1 indication code for S/T interface. Note these bits have a buffer size of two.

**Note:** If S/T layer 1 function is disabled and GCI bus is enabled (GE = 1 in GCR register), CIR register is used to receive layer 1 indication code from U transceiver. In this case, the supported indication codes are:

| Indication                | Symbol | Code | Descriptions               |

|---------------------------|--------|------|----------------------------|

| Deactivation Confirmation | DC     | 1111 | Idle code on GCI interface |

| Power-up Indication       | PU     | 0111 | U transceiver power up     |

| 8.1.3 Mo                             | 8.1.3 Monitor Channel Interrupt Status MOIR Read_clear                                                       |    |    |     |     |     |     |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------|----|----|-----|-----|-----|-----|

| Value aft                            | Value after reset: 00h                                                                                       |    |    |     |     |     |     |

| 7 6 5 4 3 2                          |                                                                                                              |    |    | 1   | 0   |     |     |

| 0                                    | 0                                                                                                            | 0  | 0  | MDR | MER | MDA | MAB |

| MER M<br>MDA M<br>MAB M<br>8.1.4 PIC | MER       Monitor Channel End of Reception         MDA       Monitor Channel Data Acknowledged               |    |    |     |     |     |     |

| Value af                             | ter reset: 0                                                                                                 | 0h |    |     |     |     |     |

| 7                                    | 6                                                                                                            | 5  | 4  | 3   | 2   | 1   | 0   |

| P7                                   | P6                                                                                                           | P5 | P4 | P3  | P2  | P1  | P0  |

| 0                                    | P7-0 Indicator of IO Pin Input Status<br>0: This IO pin is either output pin, or did not change input value. |    |    |     |     |     |     |

1: This IO pin changed value.

NOTE : Registers in sections 8.2 to 8.5 are written/read by Bulk-OUT/Bulk-IN transactions.

#### 8.2 Chip and FIFO Control Registers

8.2.1 Interrupt Mask Register IMASK Read/Write Address 00h

#### Value after reset: E1h

| 7   | 6   | 5     | 4 | 3 | 2 | 1 | 0 |

|-----|-----|-------|---|---|---|---|---|

| ICC | MOC | PIOIC | 0 | 0 | 0 | 0 | 1 |

Setting '1' to each bits masks the corresponding interrupt sources in ISTA register.

# Electronics Corp.

#### 8.2.2 Command Register 1 CMDR1Write Address 01h

#### Value after reset: 00h

Writing 1 to the following bits will activate each corresponding function. Writing 0 to these bits has no effect.

| 7     | 6     | 5    | 4    | 3    | 2     | 1   | 0   |

|-------|-------|------|------|------|-------|-----|-----|

| DXRST | DRRST | DXEN | DREN | SRST | CISOE | DLP | RLP |

#### **DXRSTD Channel Transmitter Reset**

Setting this bit resets D channel transmitter, and clear transmit FIFO (XFIFO). The transmitter will immediately transmit inter frame time fill pattern (all 1's) to D channel in ISDN layer 1, but the XFIFO is disabled (not active). Software must issue DXEN to enable (activate) D channel XFIFO. After reset is done, this bit becomes 0. If this bit and other bits are set at the same time, the reset action will be performed first and completed, then other actions will follow.

#### **DRRSTD Channel Receiver Reset**

Setting this bit resets D channels receiver, and clear receive FIFO (RFIFO). The D channels is disabled (not active). Software must issue DREN to enable (activate) D channel RFIFO, in order to receive D channel data from ISDN, and send data to USB. After reset is done, this bit becomes 0. If this bit and other bits are set at the same time, the reset action will be performed first and completed, then other actions will follow.

#### DXEN D Channel Transmit FIFO Enable

Setting this bit enables D channel transmit FIFO (XFIFO). After enabled, the D channel XFIFO will begin to receive D channel data from USB, and send data to ISDN. After enabled, this bit becomes 0.

#### DREN D Channel Receive FIFO Enable

Setting this bit enables D channel receive FIFO (RFIFO). After enabled, the D channel RFIFO will begin to receive D channel data from ISDN, and send data to USB. After enabled, this bit becomes 0.

#### SRST Software Reset

Setting this bit internally generates a software reset signal. The effect of this reset signal is equivalent to hardware reset pin, except that the USB circuit and all USB configured data are not reset. This bit must be set along, i.e., all other bits in this register must not set at the same time. This bit is not auto-clear, once this bit is set to '1', software must write '0' to this bit to exit from the reset mode. In the reset-mode the chip will not function properly.

#### **CISOE Clear Isochronous-OUT Error**

Setting this bit clears error indication bit ISOE of Isochronous-OUT error. This bit is carried by Isochronous-IN packet. After bits are cleared, this bit becomes 0.

#### DLP Digital Loopback

Setting this bit activates the digital loopback function. The transmitted digital 2B+D channels are looped to the received 2B+D channels. Note that after hardware reset, the internal clocks will turn off if the S bus is not connected or if there is no signal on the S bus. In this case, the C/I command ECK must be issued to enable loopback function. This bit remains set, until cleared by software reset (SRST).

# Electronics Corp.

#### RLP Remote Loopback

Setting this bit activates the remote loopback function. The received 2B channels from the S interface are looped to the transmitted 2B channels of S/T interface. The D channel is not looped in this loopback function.

This bit remains set, until cleared by software reset (SRST).

#### 8.2.3 Command Register 2 CMDR2Write Address 02h

#### Value after reset: 00h

Bits in this register act similar to that of CMDR1 register, except that the effect is on B1 or B2 channel XFIFO/RFIFO, instead of on D channel XFIFO/RFIFO.

| 7                                                                        | 6                                                                                                                                                                                                           | 5     | 4     | 3      | 2         | 1     | 0         |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|--------|-----------|-------|-----------|

| B1XRST                                                                   | B1RRST                                                                                                                                                                                                      | B1XEN | B1REN | B2XRST | B2RRST    | B2XEN | B2REN     |

| B1XRST<br>B1RRST<br>B1XEN<br>B1REN<br>B2XRST<br>B2RRST<br>B2XEN<br>B2REN | B1RRSTB1 Channel Receiver ResetB1XENB1 Channel Transmit FIFO EnableB1RENB1 Channel Receive FIFO EnableB2XRSTB2 Channel Transmitter ResetB2RRSTB2 Channel Receiver ResetB2XENB2 Channel Transmit FIFO Enable |       |       |        |           |       |           |

|                                                                          | trol Register<br>r reset: 00H                                                                                                                                                                               |       | CTL   | R      | ead/Write | Ad    | dress 03h |

| 7                                                                        | 6                                                                                                                                                                                                           | 5 4   | 3     | 2      | 1         | 0     |           |

| 0                                                                        | 0                                                                                                                                                                                                           | 0 0   | 0     | 0      | OPS1 OI   | PS0   |           |

#### **OPS1-0** Output Phase Delay Compensation Select1-0

These two bits select the output phase delay compensation.

| OPS1 | OPS0 | Effect                                  |  |  |  |

|------|------|-----------------------------------------|--|--|--|

| 0    | 0    | No output phase delay compensation      |  |  |  |

| 0    | 1    | Output phase delay compensation 260 nS  |  |  |  |

| 1    | 0    | Output phase delay compensation 520 nS  |  |  |  |

| 1    | 1    | Output phase delay compensation 1040 nS |  |  |  |

# Electronics Corp.

## 8.2.5 Layer 1 Command/Indication Register CIX R

#### 0

Read/Write Address 04h

#### Value after reset: 0Fh

| 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|---|---|---|---|------|------|------|------|

| 0 | 0 | 0 | 0 | CIX3 | CIX2 | CIX1 | CIX0 |

#### CIX3-0 Layer 1 Command Code

Value of the command code transmitted to layer 1. A read to this register returns the previous written value.

Note: If S/T layer 1 function is disabled and GCI bus is enabled (GE = 1 in GCR register), CIX register is used to issue layer 1 command code to U transceiver. In this case, the supported command code is:

|   |                          | Comma                     | nd | Symbol | Code     | Descriptions |              |     |

|---|--------------------------|---------------------------|----|--------|----------|--------------|--------------|-----|

|   | Activate Request Command |                           |    | AR     | 1000     | Activate rec | quest comman | id  |

|   |                          | iyer1 Read<br>er reset: 0 |    | L      | .1_RC Re | ead/Write    | Address      | 05h |

| 7 | 7                        | 6                         | 5  | 4      | 3        | 2 🖸          | 1            | 0   |

| ( | )                        | 0                         | 0  | 0      | RC3      | RC2          | RC1          | RC0 |

|   |                          |                           |    |        |          |              | -            | •   |

#### **RC3-0** Ready Code

When GCI bus is being enabled, these four programmable bits are allowed to program different Layer 1\_Ready Code (AI: Activation Indication) by user. For example: Siemens PEB2091: AI = 1100, Motorola MC145572: AI = 1100.

#### 8.3 GCI Mode Registers

| 8.3.1 GCI Mode Command Register | GCR | Read/Write | Address 06h |

|---------------------------------|-----|------------|-------------|

|---------------------------------|-----|------------|-------------|

#### Value after reset: 00h

| 7   | 6 | 5 | 4   | 3    | 2   | 1  | 0  |

|-----|---|---|-----|------|-----|----|----|

| MAC | 0 | 0 | TLP | GRLP | SPU | PD | GE |

#### MAC Monitor Transmit Channel Active (Read Only)

Data transmission is in progress in GCI mode Monitor channel. 0: The previous transmission has been terminated. Before starting a transmission, software should verify that the transmitter is inactive. 1: The previous transmission is in progress.

# Electronics Corp.

#### TLP Test Loopback

When set this bit both the GCIDU and GCIDD lines are internally connected together. The GCI mode loopback test function: GCIDU is internally connected with GCIDD, external input on GCIDD is ignored.

#### GRLP GCI Mode Remote Loopback

Setting this bit to 1 activates the remote loopback function. The 2B+D channels data received from the GCI bus interface are looped to the transmitted channels.

#### SPU Software Power Up

#### PD Power Down

| SPU | PD | DESCRIPTION                                                                                                                                                                                                                                                                                   |

|-----|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 1  | After U transceiver power down, W6694 will receive the indication DC (Deactivation Confirmation) from GCI bus and then software has to set SPU $\rightarrow$ 0, PD $\rightarrow$ 1 to acknowledge U transceiver, by pulling GCIDU line to HIGH. W6694 remains normal operation.               |

| 1   | 0  | Setting SPU $\rightarrow$ 1, PD $\rightarrow$ 0 will pull the GCI bus GCIDU line to LOW. This will enforce connected layer 1 devices (U transceiver) to deliver GCI bus clocking.                                                                                                             |

| 0   | 0  | After reception of the indication PU (Power Up indication) the reaction of the microprocessor should be:<br>- To write an AR (Activate Request command) as C/I command code in the CIX register.<br>- To reset the SPU bit and wait for the following ICC (indication code change) interrupt. |

| 1   | 1  | Unused.                                                                                                                                                                                                                                                                                       |

#### GE GCI Mode Enable

Setting this bit to 1 will enable the GCI bus interface. In the same time, the S/T layer 1 function is disabled.

#### 8.3.2 Monitor Channel Control Register

MOCR Read/Write Address 07h

#### Value after reset: 00h

| 7 | 6 | 5 | 4 | 3    | 2   | 1    | 0   |

|---|---|---|---|------|-----|------|-----|

| 0 | 0 | 0 | 0 | MRIE | MRC | MXIE | MXC |

#### MRIE Monitor Channel 0 Receive Interrupt Enable

Monitor channel interrupt status MDR, MER generation is enabled (1) or masked (0).

#### MRC MR Bit Control

Determines the value of the MR bit:

# Electronics Corp.

0: MR bit always 1. In addition, the MDR interrupt is blocked, except for the first byte of a packet (if MRIE = 1).

1: MR internally controlled according to Monitor channel protocol. In addition, the MDR interrupt is enabled for all bytes according to the Monitor channel protocol (if MRIE = 1).

#### MXIE Monitor Channel Transmit Interrupt Enable

Monitor interrupt status MDA, MAB generation is enabled (1) or masked (0).

#### MXC MX Bit Control

Determines the value of the MX bit:

0: MX always 1.

1: MX internally controlled according to Monitor channel protocol.

# Electronics Corp.

#### OMn\_1-0 Output Mode of IO Pin n (n = 3...0).

Setting corresponding bits drive output pin with different output mode. Possible modes are: 00: always LOW 01: 0.5 second HIGH/LOW cycle 10: 1 second HIGH/LOW cycle 11: always HIGH These bits have no effect on input pin. The default value of this register makes pin PIO0 flash if ISDN clock is enabled.

#### D7-0 Read Data of IO Pins 7-0

The corresponding bits are the present values of IO pins 7-0 (LOW=0, HIGH=1).

#### 8.5 B Channel Switch Registers

| 8.5.1 Laye | er1 B1 Re   | ceiver Sel | ect Register | L11 | B1RS | Read/Writ | e Address 0Eh |

|------------|-------------|------------|--------------|-----|------|-----------|---------------|

| Value afte | er reset: 0 | 4h         |              |     |      |           |               |

| 7          | 6           | 5          | 4            | 3   | 2    | 1         | 0             |

0

#### **RS2-0** Receiver Select

0

0

These bits select the source where layer 1 B1 channel will receive data from. Possible values are:

RS2

RS1

- 000 (0): receive from PCM1

- 001 (1): receive from PCM2

- 010 (2): receive from Layer1 B1

0

0

100 (4): receive from USB B1

RS0

# Electronics Corp.

| 8.5.2 L                                        | ayer1 B2                                                                                                                                                                                           |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                          |                                 | B2RS                                        | Read/Write                                                                                                                                                                                                                                                                                                  | Address 0Fh                              |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|