# Skew Controlled SDRAM Buffer

#### Features

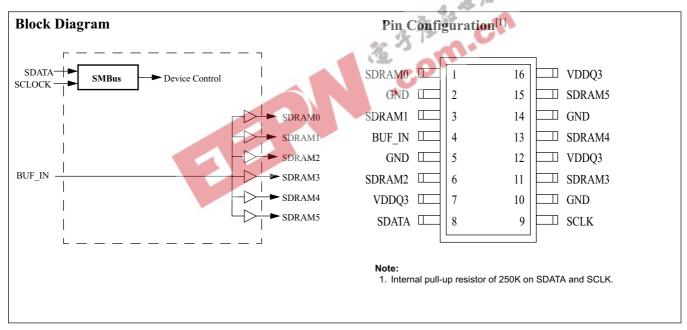

- · Six skew controlled CMOS outputs

- Output skew between any two outputs is less than 150 ps

- SMBus Serial configuration interface

- 2.5 ns to 5 ns propagation delay

- DC to 133 MHz operation (Commercial)

- DC to 100 MHz operation (Industrial)

- Single 3.3V supply voltage

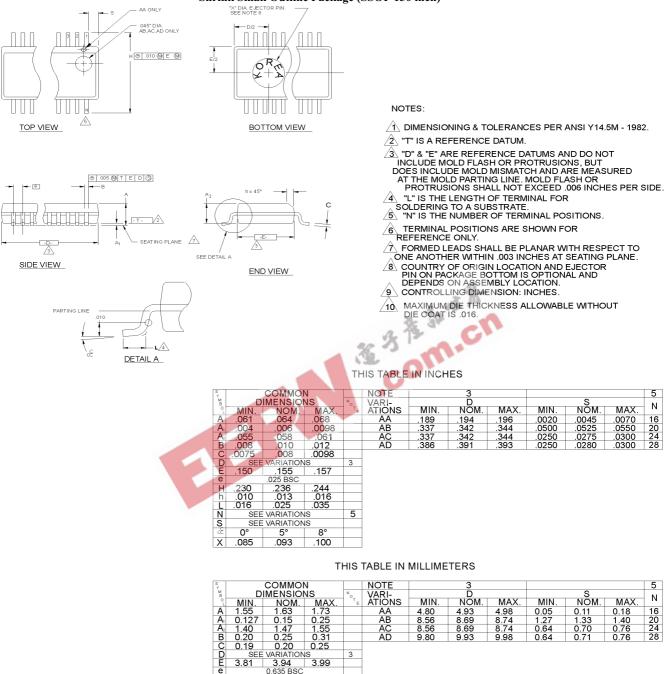

- Low power CMOS design packaged in a 16-pin SSOP (Small Shrink Outline Package)

#### **Key Specifications**

| Supply Voltages:                                    |

|-----------------------------------------------------|

| Operating Temperature: (Commercial)0°C to +70°C     |

| Operating Temperature: (Industrial)40°C to +85°C    |

| Input Threshold:1.5V typical                        |

| Maximum Input Voltage:V <sub>DDQ3</sub> + 0.5V      |

| Input Frequency: (Commercial)0 to 133 MHz           |

| Input Frequency: (Industrial)0 to 100 MHz           |

| BUF_IN to SDRAM0:5 Propagation Delay:2.5 ns to 5 ns |

| Min. Output Edge Rate: 1.0V/ns                      |

| Max. Output Skew: 150 ps                            |

| Output Duty Cycle:45/55% worst case                 |

| Output Impedance:                                   |

# **Pin Definitions**

| Pin Name | Pin No.                | Pin<br>Type | Pin Description                                                                                                                                                                                           |  |

|----------|------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SDRAM0:5 | 1, 3, 6,<br>11, 13, 15 | 0           | <b>SDRAM Outputs:</b> Provides buffered copy of BUF_IN. The propagation delay fro rising input edge to a rising output edge is 2.5 to 5 ns. All outputs are skew controt to within ±150 ps of each other. |  |

| BUF_IN   | 4                      | I           | Clock Input: This clock input has an input threshold voltage of 1.5V (typ).                                                                                                                               |  |

| SDATA    | 8                      | I/O         | <i>SMBus Data input:</i> Data should be presented to this input as described in the SMBus section of this data sheet. Internal $250-k\Omega$ pull-up resistor.                                            |  |

| SCLOCK   | 9                      | Ι           | <b>SMBus clock input:</b> The SMBus Data clock should be presented to this input as described in the SMBus section of this data sheet. Internal 250-k $\Omega$ pull-up resistor.                          |  |

| VDDQ3    | 7, 12, 16              | Р           | <b>Power Connection:</b> Power supply for core logic and output buffers. Connected to 3.3V supply.                                                                                                        |  |

| GND      | 2, 5, 10,<br>14        | G           | Ground Connection: Connect all ground pins to the common system ground plane.                                                                                                                             |  |

#### Overview

The W191 is a skew controlled fanout buffer optimized for interface with registered DIMMs.

#### **Functional Description**

#### **Output Drivers**

The W191 output buffers are CMOS type which deliver a rail-to-rail (GND to VDD) output voltage swing into a nominal capacitive load. Thus, output signaling is both TTL and CMOS level compatible. Nominal output buffer impedance is  $15\Omega$ .

#### Table 1. Byte Writing Sequence

#### Serial Control

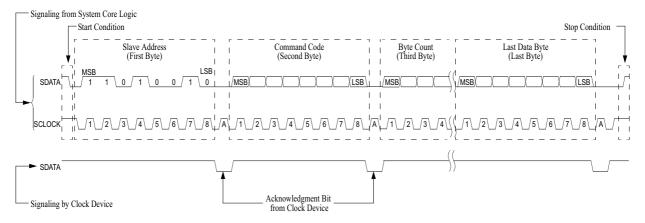

Serial control data is written to the W191 in ten bytes of eight bits each. Bytes are written in the order shown in *Table 1*

#### Writing Data Bytes

Each bit in the data bytes control a particular device function. Bits are written MSB (most significant bit) first, which is bit 7. *Table 1* gives the bit formats for registers located in Data Bytes 0-2.

| Byte<br>Sequence | Byte Name     | Bit Sequence | Byte Description                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|---------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | Slave Address | 11010010     | Commands the W191 to accept the bits in Data Bytes 0-6 for internal register configuration. Since other devices may exist on the same common serial data bus, it is necessary to have a specific slave address for each potential receiver. The slave receiver address for the W191 is 11010010. Register setting will not be made if the Slave Address is not correct (or is for an alternate slave receiver). |

| 2                | Command Code  | Don't Care   | Unused by the W191, therefore bit values are ignored (don't care). This byte must be included in the data write sequence to maintain proper byte allocation. The Command Code Byte is part of the standard serial communication protocol and may be used when writing to another addressed slave receiver on the serial data bus.                                                                               |

| 3                | Byte Count    | Don't Care   | Unused by the W191, therefore bit values are ignored (don't care). This byte must be included in the data write sequence to maintain proper byte allocation. The Byte Count Byte is part of the standard serial communication protocol and may be used when writing to another addressed slave receiver on the serial data bus.                                                                                 |

| 4                | Data Byte 0   | Refer to     | The data bits in these bytes set internal W191 registers that control device                                                                                                                                                                                                                                                                                                                                    |

| 5                | Data Byte 1   | Table 2      | operation. The data bits are only accepted when the Address Byte bit sequence is 11010010, as noted above. For description of bit control                                                                                                                                                                                                                                                                       |

| 6                | Data Byte 2   |              | functions, refer to <i>Table</i> 2.                                                                                                                                                                                                                                                                                                                                                                             |

| 7                | Data Byte 3   | Don't Care   |                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8                | Data Byte 4   |              |                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9                | Data Byte 5   |              |                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10               | Data Byte 6   |              |                                                                                                                                                                                                                                                                                                                                                                                                                 |

# Table 2. Data Bytes 0–2 Serial Configuration $\mathrm{Map}^{[2]}$

| Affected Pin                                                         |             | Affected Pin      |                                 | Bit Control |        |  |

|----------------------------------------------------------------------|-------------|-------------------|---------------------------------|-------------|--------|--|

| Bit(s)                                                               | Pin No.     | Pin Name          | Control Function                | 0           | 1      |  |

| Data Byte 0 SDRAM Active/Inactive Register (1 = Enable, 0 = Disable) |             |                   |                                 |             |        |  |

| 7                                                                    | 6           | SDRAM2            | Clock Output Disable            | Low         | Active |  |

| 6                                                                    |             |                   | (Reserved)                      |             |        |  |

| 5                                                                    |             |                   | (Reserved)                      |             |        |  |

| 4                                                                    |             |                   | (Reserved)                      |             |        |  |

| 3                                                                    |             |                   | (Reserved)                      |             |        |  |

| 2                                                                    | 3           | SDRAM1            | Clock Output Disable            | Low         | Active |  |

| 1                                                                    |             |                   | (Reserved)                      |             |        |  |

| 0                                                                    | 1           | SDRAM0            | Clock Output Disable            |             |        |  |

| Data Byte                                                            | 1 SDRAM Act | tive/Inactive Reg | ister (1 = Enable, 0 = Disable) |             |        |  |

| 7                                                                    |             |                   | Clock Output Disable            |             |        |  |

| 6                                                                    | 15          | SDRAM5            | Clock Output Disable            | Low         | Active |  |

| 5                                                                    |             |                   | Clock Output Disable            | J. 15       |        |  |

| 4                                                                    |             |                   | (Reserved)                      | a 34 - A    |        |  |

| 3                                                                    | 13          | SDRAM4            | Clock Output Disable            | Low         | Active |  |

| 2                                                                    |             |                   | (Reserved)                      |             |        |  |

| 1                                                                    |             |                   | (Reserved)                      | <u> </u>    |        |  |

| 0                                                                    |             |                   | (Reserved)                      |             |        |  |

| Data Byte                                                            | 2 SDRAM Act | tive/Inactive Reg | ister (1 = Enable, 0 = Disable) |             |        |  |

| 7                                                                    | 11          | SDRAM3            | Clock Output Disable            | Low         | Active |  |

| 6                                                                    |             | -                 | (Reserved)                      |             |        |  |

| 5                                                                    |             |                   | (Reserved)                      |             |        |  |

| 4                                                                    |             |                   | (Reserved)                      |             |        |  |

| 3                                                                    |             |                   | (Reserved)                      |             |        |  |

| 2                                                                    |             |                   | (Reserved)                      |             |        |  |

| 1                                                                    |             |                   | (Reserved)                      |             |        |  |

| 0                                                                    |             |                   | (Reserved)                      |             |        |  |

**Note:** 2. At power up all SDRAM outputs are enabled and active. Program Reserved bits to 0.

## Absolute Maximum Ratings<sup>[3]</sup>

Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.

| Parameter                           | Description                            | Rating        | Unit |

|-------------------------------------|----------------------------------------|---------------|------|

| V <sub>DDQ3</sub> , V <sub>IN</sub> | Voltage on any pin with respect to GND | –0.5 to + 7.0 | V    |

| T <sub>STG</sub>                    | Storage Temperature                    | –65 to + 150  | °C   |

| T <sub>B</sub>                      | Ambient Temperature under Bias         | –55 to + 125  | °C   |

| T <sub>A</sub>                      | Operating Temperature (Commercial)     | 0 to + 70     | °C   |

| T <sub>A</sub>                      | Operating Temperature (Industrial)     | -40 to + 85   | °C   |

DC Electrical Characteristics: T<sub>A</sub> = 0°C to +70°C (Commercial), V<sub>DDQ3</sub> = 3.3V ± 5%, T<sub>A</sub> = -40°C to +85°C (Industrial), V<sub>DDQ3</sub> = 3.3V ± 5% <sup>[4]</sup>

| Parame-<br>ter     | Description                           | Test Condition          | Min.    | Тур. | Max.                   | Unit |

|--------------------|---------------------------------------|-------------------------|---------|------|------------------------|------|

| I <sub>DD</sub>    | 3.3V Supply Current                   | BUF_IN = 100 MHz        |         | 173  |                        | mA   |

| I <sub>DD</sub>    | 3.3V Supply Current in three-state    | BUF_IN = 100 MHz        | A       | 5    |                        | mA   |

| Logic Inpu         | uts (BUF_IN, OE, SCLOCK, SDATA)       | 4                       | AN      |      |                        |      |

| V <sub>IL</sub>    | Input Low Voltage                     | 、花                      | GND-0.3 |      | 0.8                    | V    |

| V <sub>IH</sub>    | Input High Voltage                    | 36 3                    | 2.0     |      | V <sub>DDQ3</sub> +0.5 | V    |

| I <sub>ILEAK</sub> | Input Leakage Current, BUF_IN         | 0.                      | -5      |      | +5                     | μA   |

| I <sub>ILEAK</sub> | Input Leakage Current <sup>[5]</sup>  |                         | -20     |      | +5                     | μA   |

| Logic Out          | puts (SDRAM0:5)                       |                         |         |      |                        |      |

| V <sub>OL</sub>    | Output Low Voltage                    | I <sub>OL</sub> = 1 mA  |         |      | 50                     | mV   |

| V <sub>OH</sub>    | Output High Voltage                   | I <sub>OH</sub> = –1 mA | 3.1     |      |                        | V    |

| I <sub>OL</sub>    | Output Low Current                    | V <sub>OL</sub> = 1.5V  | 65      | 100  | 160                    | mA   |

| I <sub>OH</sub>    | Output High Current                   | V <sub>OH</sub> = 1.5V  | 70      | 110  | 185                    | mA   |

| Pin Capac          | itance/Inductance                     |                         |         |      |                        | -    |

| C <sub>IN</sub>    | Input Pin Capacitance (Except BUF_IN) |                         |         |      | 5                      | pF   |

| C <sub>OUT</sub>   | Output Pin Capacitance                |                         |         |      | 6                      | pF   |

| L <sub>IN</sub>    | Input Pin Inductance                  |                         |         |      | 7                      | nH   |

Notes:

Multiple supplies: The voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is NOT required.

Outputs loaded by 6" 60 Ω transmission lines with 20 pF capacitors.

OE, SCLOCK, and SDATA logic pins have a 250-kΩ internal pull-up resistor (not CMOS level).

# AC Electrical Characteristics: $T_A = 0^{\circ}C$ to +70°C (Commercial), $V_{DDQ3} = 3.3V \pm 5\%$ , $T_A = -40^{\circ}C$ to +85°C (Industrial), $V_{DDQ3} = 3.3V \pm 5\%$ (Lump Capacitance Test Load = 30pF)

| Parameter        | Description                    | Test Condition                | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------|-------------------------------|------|------|------|------|

| f <sub>IN</sub>  | Input Frequency (Commercial)   |                               | 0    |      | 133  | MHz  |

| f <sub>IN</sub>  | Input Frequency (Industrial)   |                               | 0    |      | 100  | MHz  |

| t <sub>R</sub>   | Output Rise Edge Rate          | Measured from 0.4V<br>to 2.4V | 1.0  |      | 4.0  | V/ns |

| t <sub>F</sub>   | Output Fall Edge Rate          | Measured from 2.4V<br>to 0.4V | 1.0  |      | 4.0  | V/ns |

| t <sub>SR</sub>  | Output Skew, Rising Edges      |                               |      |      | 150  | ps   |

| t <sub>SF</sub>  | Output Skew, Falling Edges     |                               |      |      | 150  | ps   |

| t <sub>EN</sub>  | Output Enable Time             |                               | 1.0  |      | 8.0  | ns   |

| t <sub>DIS</sub> | Output Disable Time            |                               | 1.0  |      | 8.0  | ns   |

| t <sub>PR</sub>  | Rising Edge Propagation Delay  |                               | 2.5  |      | 5.0  | ns   |

| t <sub>PF</sub>  | Falling Edge Propagation Delay |                               | 2.5  |      | 5.0  | ns   |

| t <sub>D</sub>   | Duty Cycle                     | Measured at 1.5V              | 45   |      | 55   | %    |

| Zo               | AC Output Impedance            |                               | 15   | 15   |      | Ω    |

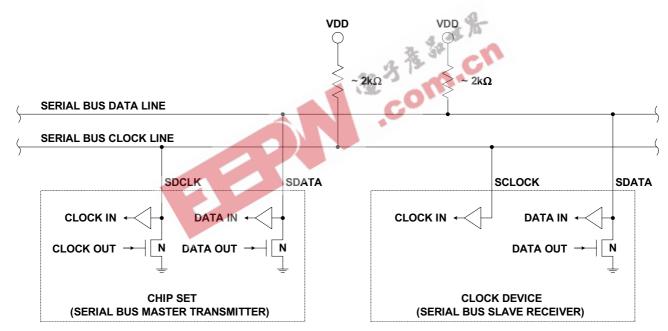

#### **Electrical Requirements**

*Figure 1* illustrates electrical characteristics for the serial interface bus used with the W191. Devices send data over the bus with an open drain logic output that can (a) pull the bus line low, or (b) let the bus default to logic 1. The pull-up resistor on the bus (both clock and data lines) establish a default logic 1. All bus devices generally have logic inputs to receive data.

Although the W191 is a receive-only device (no data write-back capability), it does transmit an "acknowledge" data pulse after each byte is received. Thus, the SDATA line can both transmit and receive data.

The pull-up resistor should be sized to meet the rise and fall times specified in AC parameters, taking into consideration total bus line capacitance.

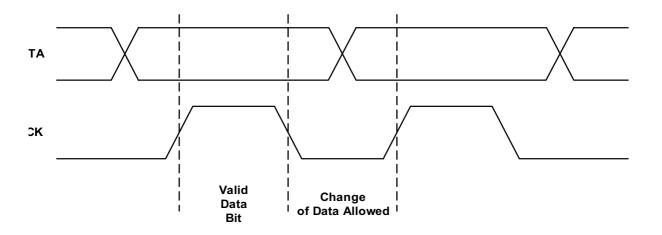

#### **Signaling Requirements**

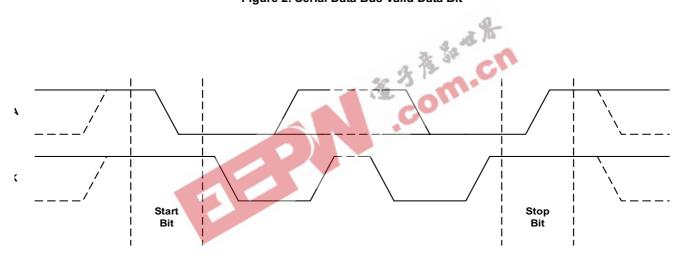

As shown in *Figure 2*, valid data bits are defined as stable logic 0 or 1 condition on the data line during a clock HIGH (logic 1)

pulse. A transitioning data line during a clock high pulse may be interpreted as a start or stop pulse (it will be interpreted as a start or stop pulse if the start/stop timing parameters are met).

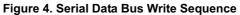

A write sequence is initiated by a "Start Bit" as shown in *Figure 3.* A "Stop Bit" signifies that a transmission has ended.

As stated previously, the W191 sends an "acknowledge" pulse after receiving eight data bits in each byte as shown in *Figure 4.*

#### Sending Data to the W191

The device accepts data once it has detected a valid start bit and address byte sequence. Device functionality is changed upon the receipt of each data bit (registers are not double buffered). Partial transmission is allowed meaning that a transmission can be truncated as soon as the desired data bits are transmitted (remaining registers will be unmodified). Transmission is truncated with either a stop bit or new start bit (restart condition).

Figure 1. Serial Interface Bus Electrical Characteristics

Figure 3. Serial Data Bus Start and Stop Bit

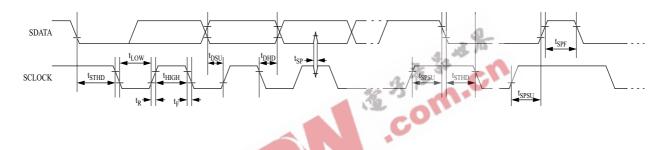

### Figure 5. Serial Data Bus Timing Diagrams

# **Ordering Information**

| Ordering Code | Package Type            | Temperature Range |

|---------------|-------------------------|-------------------|

| W191HI        | 16 pin = SSOP (150 mil) | I = Industrial    |

| W191H         | 16 pin = SSOP (150 mil) | Commercial        |

While SLI has reviewed all information herein for accuracy and reliability, Spectra Linear Inc. assumes no responsibility for the use of any circuitry or for the infringement of any patents or other rights of third parties which would result from each use. This product is intended for use in normal commercial applications and is not warranted nor is it intended for use in life support, critical medical instruments, or any other application requiring extended temperature range, high reliability, or any other extraordinary environmental requirements unless pursuant to additional processing by Spectra Linear Inc., and expressed written agreement by Spectra Linear Inc. Spectra Linear Inc. reserves the right to change any circuitry or specification without notice.

6.20 0.41 0.89

8

254

5

5.99 0.33 0.64 VARIATIONS

SEE VARIATIONS

5°

2.36

H 5. .84 .25 0.41 NS

Х 2.16

0°