# 256Kx72 Synchronous Pipeline SRAM

## FEATURES

- Fast clock speed: 100, 133, 150, 166 and 200\*\* MHz

- Fast access time: 5.0, 4.0, 3.8, 3.5, 3.1ns

- +3.3V power supply (Vcc)

- +2.5V output buffer supply (Vccq)

- Single-cycle deselect

- Common data inputs and data outputs

- Clock-controlled and registered addresses, data I/Os and control signals

- SNOOZE MODE for reduced-power standby

- Individual BYTE WRITE control and GLOBAL WRITE

- Six chip enables for simple depth expansion and address pipeline

- Internally self-timed WRITE cycle

- Burst control (interleaved or linear burst)

- Packaging:

- 159-bump PBGA package, 14mm x 22mm

- Commercial, industrial, and military temperature ranges

- User configurable as 512K x 36, or 1M x 18

\*\*200 MHz for commercial and industrial temperature only.

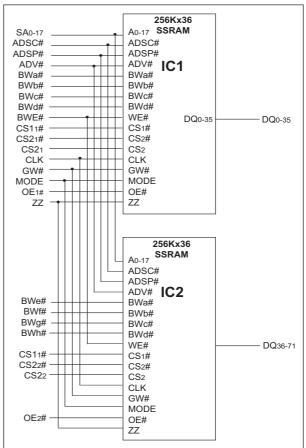

# DESCRIPTION

The WEDPY256K72V-XBX employs high-speed, lowpower CMOS designs that are fabricated using an advanced CMOS process. The 16Mb Synchronous SRAMs integrate two 256K x 36 SRAMs into a single PBGA package to provide 256K x 72 configuration. All synchronous inputs are controlled by a positive-edgetriggered single-clock input (CLK). The synchronous inputs include all addresses, all data inputs, and active LOW chip selects (CS#). Asynchronous inputs include the output enable (OE1#/OE2#), clock (CLK).

This product is subject to change without notice.

### FIGURE 1 – BLOCK DIAGRAM

# WHITE ELECTRONIC DESIGNS \_\_\_\_\_\_ WEDPY256K72V-XBX

|   |                    |                    |      |      | (Top View |      |      |      |        |      |

|---|--------------------|--------------------|------|------|-----------|------|------|------|--------|------|

|   | 1                  | 2                  | 3    | 4    | 5         | 6    | 7    | 8    | 9      | 10   |

| Α | _                  | DQ16               | DQ14 | DQ12 | DQ10      | ZZ   | DQ6  | DQ4  | DQØ    | DQ8  |

| В | ADV#               | DQ17               | DQ15 | DQ11 | DQ9       | DQ7  | DQ5  | DQ3  | DQ1    | SA13 |

| С | OE1#               | ADSP#              | GW#  | DQ13 | DNU       | GND  | DQ29 | DQ2  | - SA12 | SA10 |

| D | CS21#              | CLK                | BWa# | GND  | GND       | Vcc  | Vccq | SA11 | SA9    | SA6  |

| E | BWc#               | BWb#               | BWd# | GND  | Vcc       | GND  | GND  | SA8  | SA7    | SAØ  |

| F | CS21               | DQ18               | DQ22 | Vcc  | Vccq      | GND  | Vcc  | DQ30 | DQ34   | SA1  |

| G | CS1 <sub>1</sub> # | DQ19               | DQ23 | GND  | Vcc       | Vccq | GND  | DQ31 | DQ33   | SA5  |

| н | DQ26               | DQ20               | DQ24 | Vccq | Vccq      | Vcc  | Vcc  | DQ28 | DQ32   | DQ35 |

| J | SA17               | DQ21               | DQ25 | Vcc  | Vcc       | Vccq | Vccq | DQ27 | DQ39   | DQ37 |

| к | SA16               | DQ52               | DQ49 | GND  | Vccq      | Vcc  | GND  | DQ40 | DQ38   | DQ36 |

| L | SA14               | DQ51               | DQ50 | Vcc  | GND       | Vccq | Vcc  | DQ42 | DQ41   | DQ44 |

| М | SA15               | DQ53               | DQ48 | GND  | GND       | Vcc  | GND  | DQ43 | SA3    | DNU  |

| N | OE2#               | ADSC#              | DQ47 | Vccq | Vcc       | GND  | GND  | MODE | SA2    | SA4  |

| Р | BWE#               | CS2 <sub>2</sub> # | DQ46 | DQ45 | GND       | DNU  | DQ59 | DQ64 | DQ66   | DQ70 |

| R | BWh#               | BWg#               | BWf# | BWe# | DQ56      | DQ60 | DQ61 | DQ65 | DQ69   | DQ71 |

| т | CS12#              | CS22               | DQ62 | DQ54 | DQ55      | DQ57 | DQ58 | DQ63 | DQ67   | DQ68 |

### **PIN CONFIGURATION**

DNU = DO NOT USE. RESERVED FOR FUTURE UPGRADES.

WHITE ELECTRONIC DESIGNS \_\_\_\_\_\_ WEDPY256K72V-XBX

### INTERLEAVED BURST ADDRESS TABLE (MODE = NC OR HIGH)

| First Address (External) | Second Address (Internal) | Third Address (Internal) | Fourth Address (Internal) |  |  |  |  |  |  |  |

|--------------------------|---------------------------|--------------------------|---------------------------|--|--|--|--|--|--|--|

| XX00                     | XX01                      | XX10                     | XX11                      |  |  |  |  |  |  |  |

| XX01                     | XX00                      | XX11                     | XX10                      |  |  |  |  |  |  |  |

| XX10                     | XX11                      | XX00                     | XX01                      |  |  |  |  |  |  |  |

| XX11                     | XX10                      | XX01                     | XX00                      |  |  |  |  |  |  |  |

|                          | ·                         |                          |                           |  |  |  |  |  |  |  |

## LINEAR BURST ADDRESS TABLE (MODE = LOW

| First Address (External) | Second Address (Internal) | Third Address (Internal) | Fourth Address (Internal) |

|--------------------------|---------------------------|--------------------------|---------------------------|

| XX00                     | XX01                      | XX10                     | XX11                      |

| XX01                     | XX10                      | XX11                     | XX00                      |

| XX10                     | XX11                      | XX00                     | XX01                      |

| XX11                     | XX00                      | XX01                     | XX10                      |

### PARTIAL TRUTH TABLE FOR WRITE COMMANDS (X36)

| Function        | GW# | BWE# | BWa# | BWb# | BWc# | BWd# |

|-----------------|-----|------|------|------|------|------|

| READ            | н   | Н    | Х    | Х    | Х    | Х    |

| READ            | Н   | L    | Н    | Н    | Н    | н    |

| WRITE Byte "a"  | Н   | L    | L    | Н    | Н    | н    |

| WRITE All Bytes | Н   | L    | L    | L    | L    | L    |

| WRITE All Bytes | L   | Х    | Х    | Х    | Х    | Х    |

NOTE:

1. Using BWE# and BWa# through BWd#, any one or more bytes may be written.

2. Insert BWe# through BWh# for DQ36-71 control.

# WHITE ELECTRONIC DESIGNS \_\_\_\_\_ WEDPY256K72V-XBX

| Operation                    | Address Used | CS1 | CS2 | CS2 | ZZ  | ADSP | ADSC | ADV    | WRITE | OE | CLK | DQ     |

|------------------------------|--------------|-----|-----|-----|-----|------|------|--------|-------|----|-----|--------|

| Deselected Cycle, Power-Down | None         | Н   | Х   | Х   | L   | Х    | L    | Х      | Х     | Х  | L-H | HIGH Z |

| Deselected Cycle, Power-Down | None         | L   | Х   | L   | L   | L    | Х    | Х      | Х     | Х  | L-H | HIGH Z |

| Deselected Cycle, Power-Down | None         | L   | н   | Х   | L   | L    | Х    | Х      | Х     | Х  | L-H | HIGH Z |

| Deselected Cycle, Power-Down | None         | L   | Х   | L   | L   | н    | L    | Х      | X     | Х  | L-H | HIGH Z |

| Deselected Cycle, Power-Down | None         | L   | н   | Х   | L   | Н    | L    | X 🍕    | Х     | Х  | L-H | HIGH Z |

| SNOOZE MODE, Power-Down      | None         | Х   | Х   | Х   | н   | Х    | Х    | X<br>X | X     | X  | Х   | HIGH Z |

| READ Cycle, Begin Burst      | External     | L   | L   | н   | L   | L    | X    | Х      | X     | Ĺ  | L-H | Q      |

| READ Cycle, Begin Burst      | External     | L   | L   | н   | L   | L V  | Х    | X      | Х     | Н  | L-H | HIGH Z |

| WRITE Cycle, Begin Burst     | External     | L   | L   | Н   | L   | Н    | LC   | Х      | L     | Х  | L-H | D      |

| READ Cycle, Begin Burst      | External     | L   | L   | H   | L   | Н    | Ľ    | Х      | Н     | L  | L-H | Q      |

| READ Cycle, Begin Burst      | External     | L   | L   | Н   | 2 L | Н    | L    | Х      | Н     | Н  | L-H | HIGH Z |

| READ Cycle, Continue Burst   | Next         | Х   | X   | X   |     | Н    | н    | L      | Н     | L  | L-H | Q      |

| READ Cycle, Continue Burst   | Next         | X   | Х   | X   | L   | н    | н    | L      | Н     | Н  | L-H | HIGH Z |

| READ Cycle, Continue Burst   | Next         | Н   | Х   | Х   | L   | Х    | н    | L      | Н     | L  | L-H | Q      |

| READ Cycle, Continue Burst   | Next         | Н   | Х   | Х   | L   | Х    | н    | L      | Н     | Н  | L-H | HIGH Z |

| WRITE Cycle, Continue Burst  | Next         | X   | Х   | Х   | L   | Н    | Н    | L      | L     | Х  | L-H | D      |

| WRITE Cycle, Continue Burst  | Next         | Н   | Х   | Х   | L   | Х    | н    | L      | L     | Х  | L-H | D      |

| READ Cycle, Suspend Burst    | Current      | Х   | Х   | Х   | L   | н    | н    | Н      | Н     | L  | L-H | Q      |

| READ Cycle, Suspend Burst    | Current      | Х   | Х   | Х   | L   | н    | н    | Н      | Н     | Н  | L-H | HIGH Z |

| READ Cycle, Suspend Burst    | Current      | Н   | Х   | Х   | L   | Х    | Н    | Н      | Н     | L  | Н   | Q      |

| READ Cycle, Suspend Burst    | Current      | Н   | Х   | Х   | L   | Х    | н    | Н      | Н     | Н  | L-H | HIGH Z |

| WRITE Cycle, Suspend Burst   | Current      | Х   | Х   | Х   | L   | н    | н    | Н      | L     | Х  | L-H | D      |

| WRITE Cycle, Suspend Burst   | Current      | Н   | Х   | Х   | L   | Х    | н    | Н      | L     | Х  | L-H | D      |

### **TRUTH TABLE**

NOTE:

1. X means "Don't Care." # means active LOW. H means logic HIGH. L means logic LOW.

2. For WRITE#, L means any one or more byte write enable signals (BWa#, BWb#, BWc#, or WE#) are LOW or GW# is LOW. WRITE# = H for all BWx#, BWE#, GW# High.

- 3. BWa enables WRITEs to DQ0-8. BWb# enables WRITEs to DQ9-17. BWc enables WRITEs to DQ18-26. BWd# enables WRITE to DQ27-35.

- 4. All inputs excepts OE# and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

5. Wait states are inserted by suspending bursts.

- 6. For a WRITE operation following a READ operation, OE# must be HIGH before the input data setup time and held HIGH

- throughout the input data hold time.

This device contains circuitry that will ensure the outputs will be held in High-Z during power-up.

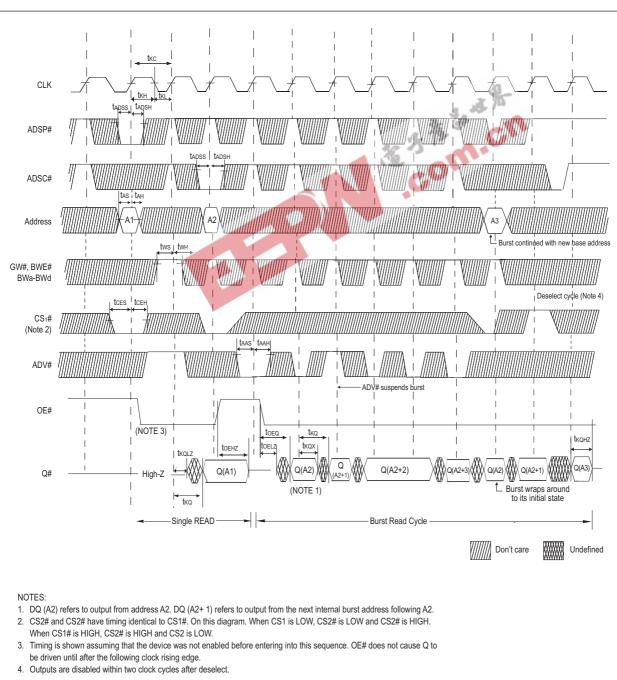

ADSP# LOW always initiates an internal READ at the L-H edge of CLK. A WRITE is performed by setting one or more byte write enable signals and BWE# LOW or GW# LOW for the subsequent L-H edge of CLK. Refer to WRITE timing diagram for clarification.

# WHITE ELECTRONIC DESIGNS \_\_\_\_\_ WEDPY256K72V-XBX

### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Vcc Supply relative to Vss  | -0.5V to +4.6V      |

|----------------------------------------|---------------------|

| Voltage on Vcco Supply relative to Vss | -0.5V to +4.6V      |

| VIN (DQx)                              | -0.5V to Vccq +0.5V |

| V <sub>IN</sub> (Inputs)               | -0.5V to Vcc +0.5V  |

| Storage Temperature (BGA)              | -55°C to +150°C     |

| Short Circuit Output Current           | 100 mA              |

\* Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### ELECTRICAL CHARACTERISTICS AND OPERATING CONDITIONS

|                             |        | $-55^\circ C \le T_A \le +125^\circ C$              | 3. 1  | C         |       |       |

|-----------------------------|--------|-----------------------------------------------------|-------|-----------|-------|-------|

| Description                 | Symbol | Conditions                                          | Min   | Max       | Units | Notes |

| Input High (Logic 1)Voltage | Vih    | Inputs                                              | 1.7   | Vcc +0.3  | V     | 1     |

|                             | VIHQ   | Data (DQ)                                           | 1.7   | Vccq +0.3 | V     | 1     |

| Input Low (Logic 0) Voltage | VIL    |                                                     | -0.3  | 0.7       | V     | 1     |

| Input Leakage Current       | ILI    | $0V \le V_{IN} \le V_{CC}$                          | -2.0  | 2.0       | μA    | 2     |

| Ouptut Leakage Current      | ILO    | Outputs disabled, $0V \le V_{IN} \le V_{CCQ}$ (DQX) | -1.0  | 1.0       | μA    |       |

| Output High Voltage         | Vон    | Iон = -1.0mA                                        | 2.0   | —         | V     | 1     |

| Output Low Voltage          | Vol    | IoL = 1.0mA                                         | —     | 0.4       | V     | 1     |

| Supply Voltage              | Vcc    |                                                     | 3.135 | 3.6       | V     | 1     |

| Output Buffer Supply        | Vccq   |                                                     | 2.375 | 2.9       | V     | 1     |

NOTES:

1. All voltages referenced to Vss (GND).

### **DC CHARACTERISTICS**

$-55^{\circ}C \le T_A \le +125^{\circ}C$

| Description                        |                  | Conditions                                                                                                                                                          | 100 MHz | 133 MHz | 150 MHz | 160 MHz | 200 MHz | Units | Notes |

|------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|-------|-------|

| Power Supply<br>Current: Operating | lod              | Device selected; All inputs $\leq V_{IL}$ or $\geq V_{IH}$ ; Cycle time $\geq t_{KC}$ MIN; V <sub>CC</sub> = MAX; Outputs open                                      | 600     | 750     | 950     | 950     | 1050    | mA    | 1.2   |

| CMOS Standby                       | I <sub>SB2</sub> | Device deselected; Vcc = MAX; All inputs $\leq$ Vss + 0.2                                                                                                           | 20      | 20      | 20      | 20      | 20      | mA    | 2     |

| Clock Running                      | I <sub>SB4</sub> | Device deselected; $V_{CC}$ = MAX; All inputs $\leq$ Vss + 0.2 or $\geq$ Vcc -0.2; Cycle time $\geq$ tcc MIN; ADSC#, ADSP#, GW#, BWx#, ADV#, $\geq$ V <sub>IH</sub> | 170     | 180     | 220     | 220     | 240     | mA    | 2     |

NOTES:

1. Ibb is specified with no output current and increases with faster cycle times. Ibb increases with faster cycle times and greater output loading.

2. "Device deselected" means device is in power-down mode as defined in the truth table. "Device selected" means device is active (not in power-down mode).

## **BGA CAPACITANCE**

| T <sub>A</sub> = +25°C, F = 1 | MHz |

|-------------------------------|-----|

|-------------------------------|-----|

| Description                          | Symbol | Max | Units | Notes |

|--------------------------------------|--------|-----|-------|-------|

| Control Input Capacitance            | CI     | 6   | pF    | 1     |

| Common Control Input Capacitance (2) | CIC    | 15  | pF    | 1     |

| Input/Output Capacitance (DQ)        | CO     | 10  | pF    | 1     |

| Address Capacitance (SA)             | CsA    | 15  | pF    | 1     |

| Clock Capacitance (CLK)              | Сск    | 12  | pF    | 1     |

| NOTES:                               |        |     |       |       |

NOTES: 1. This parameter is guaranteed by design but not tested.

### 2. Common Inputs = zz, ADV#, ADSP#, GW#, ADSC#, MODE#, BWE#.

### **BGA THERMAL RESISTANCE**

| Description                      | Symbol   | Max  | Units | Notes |

|----------------------------------|----------|------|-------|-------|

| Junction to Ambient (No Airflow) | Theta JA | 30.5 | °C/W  | 1     |

| Junction to Ball                 | Theta JB | 17.3 | °C/W  | 1     |

| Junction to Case (Top)           | Theta JC | 9.8  | °C/W  | 1     |

NOTE 1: Refer to BGA Thermal Resistance Correlation application note at www.wedc. com in the application notes section for modeling conditions.

# WHITE ELECTRONIC DESIGNS \_\_\_\_\_ WEDPY256K72V-XBX

### **AC CHARACTERISTICS**

$-55^\circ C \le T_A \le +125^\circ C$

|                                    | Symbol | 100  | MHz | 133 | MHz | 150 | MHz   | 166 | MHz    | 200 | MHz* |       |

|------------------------------------|--------|------|-----|-----|-----|-----|-------|-----|--------|-----|------|-------|

| Parameter                          |        | Min. | Max | Min | Max | Min | Max   | Min | Max    | Min | Max  | Units |

| Clock                              |        |      |     |     |     |     |       |     |        |     |      |       |

| Clock Cycle Time                   | tкc    | 10   |     | 7.5 |     | 7.0 |       | 6.0 |        | 5.0 |      | ns    |

| Clock Frequency                    | tĸr    |      | 100 |     | 133 |     | 150   |     | 166    |     | 200  | MHz   |

| Clock HIGH Time (6)                | tкн    | 3.0  |     | 2.5 |     | 2.5 |       | 2.3 |        | 2.0 |      | ns    |

| Clock LOW Time (6)                 | tкL    | 3.0  |     | 2.5 |     | 2.5 |       | 2.3 | C. Com | 2.0 |      | ns    |

| Output Times                       |        |      |     |     |     |     |       | A 4 | T h    |     |      |       |

| Clock to output valid              | tкq    |      | 5.0 |     | 4.0 |     | 3.8   | 6.2 | 3.5 📹  |     | 3.1  | ns    |

| Clock to output invalid (2)        | tках   | 1.5  |     | 1.5 |     | 1.5 | 1. 19 | 15  |        | 1.0 |      | ns    |

| Clock to output on Low-Z (2,3,4)   | tkqlz  | 1.5  |     | 0   |     | 0   | 2     | 0   |        | 0   |      | ns    |

| Clock to output in High-Z (2,3,4)  | tконz  |      | 5.0 |     | 4.2 | 132 | 4.0   | 114 | 3.5    |     | 3.1  | ns    |

| OE# to output valid (5)            | toeq   |      | 5.0 |     | 4.2 |     | 4.0   |     | 3.5    |     | 3.1  | ns    |

| OE# to output in Low-Z (2,3,4)     | toelz  | 0    |     | 0   |     | 0   |       | 0   |        | 0   |      | ns    |

| OE# to output in High Z (2,3,4)    | toeнz  |      | 4.5 |     | 4.2 |     | 4.0   |     | 3.5    |     | 3.0  | ns    |

| Setup Time                         |        |      |     |     |     |     |       |     |        |     |      |       |

| Address (6,7)                      | tas    | 2.0  |     | 1.5 |     | 1.5 |       | 1.5 |        | 1.5 |      | ns    |

| Write Enable (WE#) (7)             | tws    | 2.0  |     | 1.5 |     | 1.5 |       | 1.5 |        | 1.5 |      | ns    |

| Address status, (ADSC#, ADSP#) (7) | tadss  | 2.0  |     | 1.5 |     | 1.5 |       | 1.5 |        | 1.5 |      | ns    |

| Address advance (ADV#) (7)         | taas   | 2.0  |     | 1.5 |     | 1.5 |       | 1.5 |        | 1.5 |      | ns    |

| Data-in (6,7)                      | tos    | 2.0  |     | 1.5 |     | 1.5 |       | 1.5 |        | 1.5 |      | ns    |

| Chip enable (CE#) (7)              | tces   | 2.0  |     | 1.5 |     | 1.5 |       | 1.5 |        | 1.5 |      | ns    |

| Hold Times                         |        |      |     |     |     |     |       |     |        |     |      |       |

| Address (7) (7)                    | tан    | 0.5  |     | 0.5 |     | 0.5 |       | 0.5 |        | 0.5 |      | ns    |

| Address status (ADSC#, ADSP#) (7)  | tadsh  | 0.5  |     | 0.5 |     | 0.5 |       | 0.5 |        | 0.5 |      | ns    |

| Address advance (ADV) (7)          | tаан   | 0.5  |     | 0.5 |     | 0.5 |       | 0.5 |        | 0.5 |      | ns    |

| Write Enable (WE#) (7)             | twн    | 0.5  |     | 0.5 |     | 0.5 |       | 0.5 |        | 0.5 |      | ns    |

| Data-in (6,7)                      | toн    | 0.5  |     | 0.5 |     | 0.5 |       | 0.5 |        | 0.5 |      | ns    |

| Chip Enable (CS) (7)               | tceн   | 0.5  |     | 0.5 |     | 0.5 |       | 0.5 |        | 0.5 |      | ns    |

NOTES:

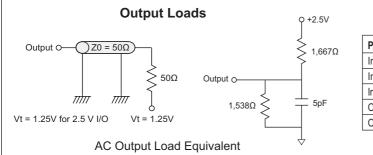

1. Test conditions as specified with the output loading as shown in test conditions unless otherwise noted.

This parameter is measured with output load as shown in test conditions. 2.

3. This parameter is not tested.

4. Transition is measured ±500mV from steady state voltage.

5. OE# is a "Don't Care" when a byte write enable is sampled LOW.

6. Measured at HIGH above  $V_{\text{IH}}$  and LOW below  $V_{\text{IL}}$

This is a synchronous device. All addresses must meet the specified setup and hold times for all rising edges of CLK. All other synchronous inputs must meet the setup and hold 7. times with stable logic levels for all rising edges of clock (CLK) when the chip is enabled. Chip enable must be valid at each rising edge of CLK to remain enabled.

| AC Test Conditions             |                      |      |  |  |  |

|--------------------------------|----------------------|------|--|--|--|

| Parameter                      | 2.5V I/O             | Unit |  |  |  |

| Input Pulse Levels             | Vss to 2.5           | V    |  |  |  |

| Input Rise and Fall Times      | 1                    | ns   |  |  |  |

| Input Timing Reference Levels  | 1.25                 | V    |  |  |  |

| Output Timing Reference Levels | 1.25                 | V    |  |  |  |

| Output Load                    | See figures, at left |      |  |  |  |

# WEDPY256K72V-XBX

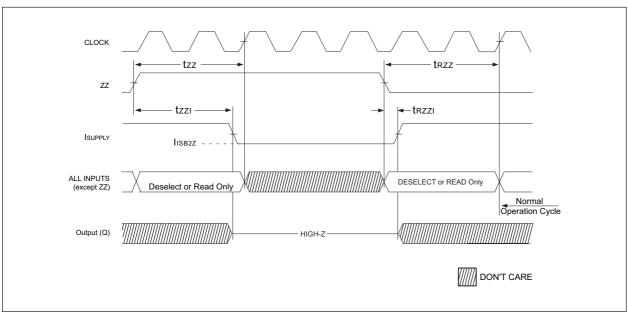

## SNOOZE MODE

SNOOZE MODE is a low-current, "power-down" mode in which the device is deselected and current is reduced to ISB2Z. The duration of SNOOZE MODE is dictated by the length of time ZZ is in a HIGH state. After the device enters SNOOZE MODE, all inputs except ZZ become gated inputs and a ignored.

ZZ is an asynchronous, active HIGH input that causes the device to enter SNOOZE MODE. When ZZ becomes a logic HIGH, ISB2Z is guaranteed after the setup time tzz is met. Any READ or WRITE operation pending when the device enters SNOOZE MODE is not guaranteed to complete successfully. Therefore, SNOOZE MODE must not be initiated until valid pending operations are completed.

### SNOOZE MODE ELECTRICAL CHARACTERISTICS

| Description                        | Conditions | Symbol           | Min     | Max     | Units | Notes |

|------------------------------------|------------|------------------|---------|---------|-------|-------|

| Current during SNOOZE MODE         | ZZ ≥ ViH   | ISB2Z            |         | 20      | mA    |       |

| ZZ active to input ignored         |            | tzz              |         | 2 (tкс) | ns    | 1     |

| ZZ inactive to input sampled       |            | t <sub>RZZ</sub> | 2 (tкс) |         | ns    | 1     |

| ZZ active to snooze current        |            | tzzi             |         | 2 (tкс) | ns    | 1     |

| ZZ inactive to exit snooze current |            | trzzi            | 0       |         | ns    | 1     |

NOTES:

1. This parameter is sampled.

7

### SNOOZE MODE WAVEFORM

# WEDPY256K72V-XBX

8

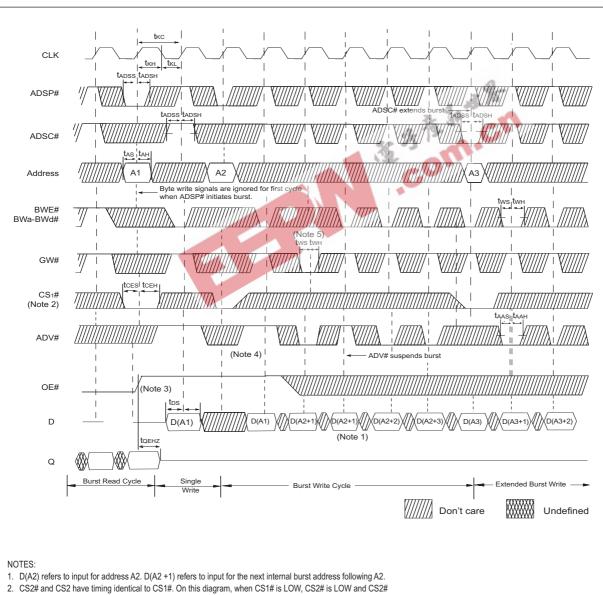

### FIGURE 2 – READ TIMING<sup>3</sup>

# White Electronic Designs

# WEDPY256K72V-XBX

9

## FIGURE 3 – WRITE TIMING

- is HIGH. When CS1# is HIGH, CS2 is HIGH and CS2 is LOW.

- 3. OE# msut be HIGH before the input data setup and held HIGH throughout the data hold time. This prevents input/output data contentinon for th etime period prior to the byte write enable inputs being sampled.

- 4. ADV# must be HIGH to permit a WRITE to the loaded address.

- 5. Full-width WRITE can be initiated by GW# LOW; or GW# HIGH, BWE# LOW and BWa#-BWd# LOW.

# WEDPY256K72V-XBX

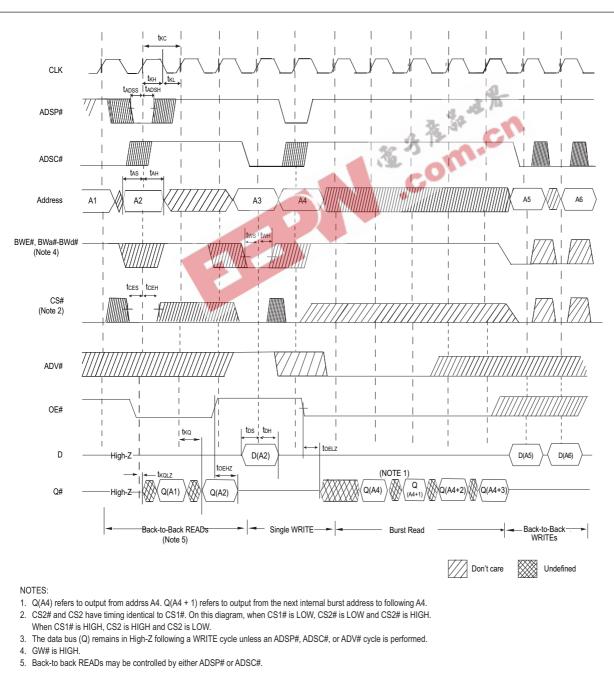

### FIGURE 5 – READ/WRITE TIMING<sup>3</sup>

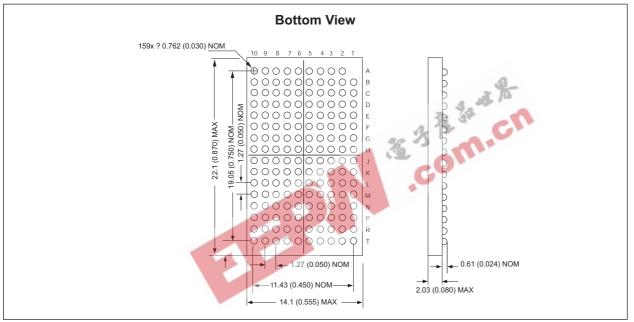

### **PACKAGE DIMENSION – 159 BUMP PBGA**

ALL LINEAR DIMENSIONS ARE MILLIMETERS AND PARENTHETICALLY IN INCHES

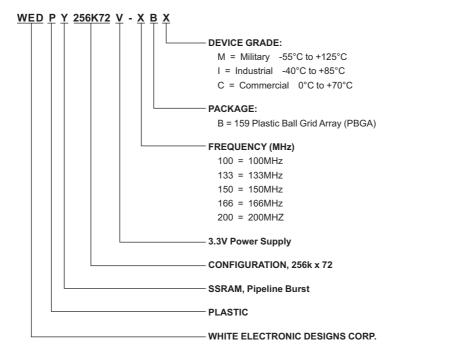

### **ORDERING INFORMATION**

11

WHITE ELECTRONIC DESIGNS \_\_\_\_\_\_ WEDPY256K72V-XBX

## **Document Title**

256K x 72 Synchronous SRAM

## **Revision History**

| Rev # His   | story                                                                               | Release Date              | Status      |

|-------------|-------------------------------------------------------------------------------------|---------------------------|-------------|

| Rev 0 Initi | ial Release                                                                         | July 2001                 | Advanced    |

|             | anges (Pg. 1, 5)<br>Add speed grades (100MHz-200MHz) to DC<br>Characteristics Table | Release Date<br>July 2001 | 0           |

| Rev 2 Cha   | ange (Pg. 1)                                                                        | January 2002              | Preliminary |

| 1.1         | Change product status from Advanced to Preliminary.                                 |                           |             |

| Rev 3 Cha   | ange (Pg. 1, 11)                                                                    | September 2002            | Preliminary |

| 1.1         | Change Package Dimension title from Top View to<br>Bottom View                      |                           |             |

| Rev 4 Cha   | anges (Pg. 1, 5)                                                                    | November 2002             | Preliminary |

| 1.1         | BGA Capacitance: Change CI from 10pF to 6pF                                         |                           |             |

| 1.2         | Change $C_{IP}$ to $C_{IC}$ , capacitance from 20pF to 15pF                         |                           |             |

| 1.3         | Change сск from 20pF to 12pF                                                        |                           |             |

| 1.4         | Change Co from 12pF to 10pF                                                         |                           |             |

| 1.5         | Change C <sub>SA</sub> from 20pF to 15pF                                            |                           |             |

| 1.6         | Add Note 2: Control Inputs = zz, ADV#, ADSP#, GW#, ADSC#, MODE#, BWE#.              |                           |             |

| Rev 5 Cha   | anges (Pg. 1, 5, 7, 12)                                                             | May 2003                  | Preliminary |

| 1.1         | Add Thermal Resistance Table                                                        |                           |             |

| 1.2         | Correct formatting on page 7                                                        |                           |             |

| Rev 6 Cha   | anges (Pg. 1, 11, 12)                                                               | November 2003             | Preliminary |

| 1.1         | Change mechanical drawing to new style                                              |                           |             |

| Rev 7 Cha   | anges (Pg. 1, 12                                                                    | August 2004               | Final       |

| 1.1         | Change status to Final                                                              |                           |             |