### PRELIMINARY

#### GENERAL DESCRIPTION

W83628F is a PCI-to-ISA bus conversion IC. W83629D is a condensed centralizer IC for IRQ and DMA control. W83628F and W83629D together form a complete set for the PCI-to-ISA bridge.

For the new generation Intel chipset Camino and Whitney, featuring LPC bus, there is no support for ISA bus and slots. However the demand of ISA devices still exist. For such case, W83628F plus W83629D are the best companion solution for the non-ISA chipset. Also the packages of W83628F (128-QFP) and W83629D (48-LQFP) had been chosen to be the most economic solution for save the M/B board layout size and cost.

For the new generation chipset featuring LPC interface and support no ISA bus, W83627HF/F (Winbond LPC I/O) together with the set of W83628F and W83629D is the complete solution.

#### FEATURES

PCI to ISA Bridge

- Full ISA Bus Support including ISA Masters

- 5V ISA and 3.3V PCI interfaces

- PC/PCI DMA protocol for Software Transparent

- IRQ Serializer for ISA Parallel IRQ transfer to Serial IRQ

- Supports 3 fully ISA Compatible Slots without Buffering

- PCI Bus at 25MHz, 33MHz and up to 40MHz

- Supports Programmable ISA Bus Divide the PCI Bus Clock into 3 or 4

- All ISA Signals can be Isolate

- Supports Configuration registers for programming performance

#### PACKAGE

- 128-pin PQFP for W83628F

- 48-pin LQFP for W83629D

#### PRELIMINARY

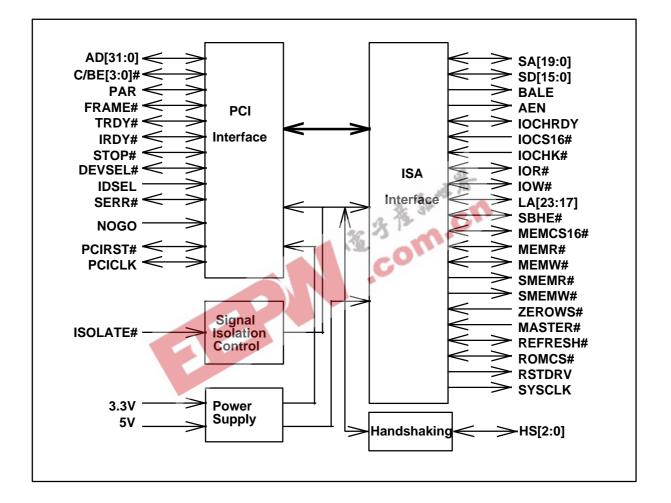

#### **BLOCK DIAGRAM OF W83628F**

#### PRELIMINARY

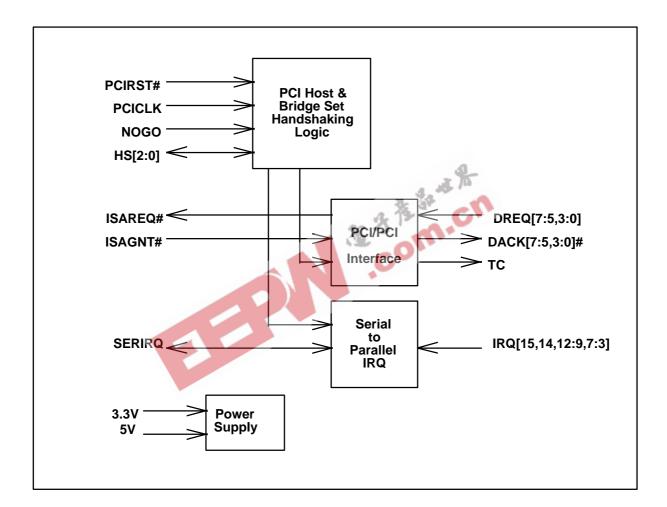

#### **BLOCK DIAGRAM OF W83629D**

#### PRELIMINARY

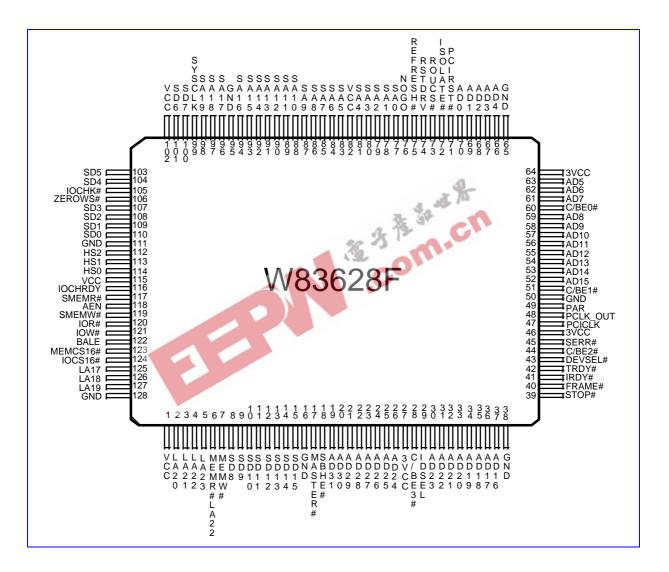

#### **PIN CONFIGURATION FOR 628F**

#### PRELIMINARY

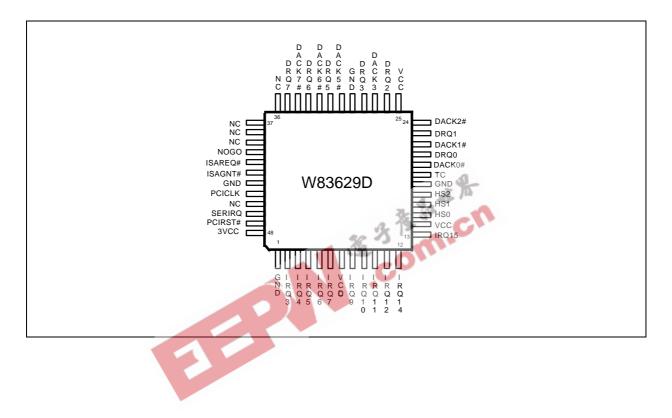

#### PIN CONFIGURATION FOR 629D

#### PRELIMINARY

#### **1. PIN DESCRIPTION**

Note: Please refer to Section 13.2 DC CHARACTERISTICS for details.

| I/O <sub>12t</sub>   | - TTL level bi-directional pin with 12 mA source-sink capability                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O24t               | - TTL level bi-directional pin with 24 mA source-sink capability                                                                                                                                                                                                                                                                                                                                                       |

| I/O <sub>12tp3</sub> | - 3.3V TTL level bi-directional pin with 12 mA source-sink capability                                                                                                                                                                                                                                                                                                                                                  |

| I/O <sub>24tp3</sub> | - 3.3V TTL level bi-directional pin with 24 mA source-sink capability                                                                                                                                                                                                                                                                                                                                                  |

| I/OD <sub>12t</sub>  | - TTL level bi-directional pin open drain output with 12 mA sink capability                                                                                                                                                                                                                                                                                                                                            |

| I/O <sub>24t</sub>   | - TTL level bi-directional pin with 24 mA source-sink capability                                                                                                                                                                                                                                                                                                                                                       |

| OUT <sub>12t</sub>   | - TTL level output pin with 12 mA source-sink capability                                                                                                                                                                                                                                                                                                                                                               |

| OUT <sub>24t</sub>   | - TTL level output pin with 24 mA source-sink capability                                                                                                                                                                                                                                                                                                                                                               |

| OUT <sub>12tp3</sub> | - 3.3V TTL level output pin with 12 mA source-sink capability                                                                                                                                                                                                                                                                                                                                                          |

| OUT <sub>24tp3</sub> | - 3.3V TTL level output pin with 24 mA source-sink capability                                                                                                                                                                                                                                                                                                                                                          |

| OD <sub>12</sub>     | - Open-drain output pin with 12 mA sink capability                                                                                                                                                                                                                                                                                                                                                                     |

| OD <sub>24</sub>     | - Open-drain output pin with 24 mA sink capability                                                                                                                                                                                                                                                                                                                                                                     |

| IN <sub>CS</sub>     | - CMOS level Schmitt-trigger input pin                                                                                                                                                                                                                                                                                                                                                                                 |

| INt                  | - TTL level input pin                                                                                                                                                                                                                                                                                                                                                                                                  |

| INtd                 | <ul> <li>3.3V TTL level output pin with 24 mA source-sink capability</li> <li>Open-drain output pin with 12 mA sink capability</li> <li>Open-drain output pin with 24 mA sink capability</li> <li>Open-drain output pin with 24 mA sink capability</li> <li>CMOS level Schmitt-trigger input pin</li> <li>TTL level input pin with internal pull down resistor</li> <li>TTL level Schmitt-trigger input pin</li> </ul> |

| INts                 | - TTL level Schmitt-trigger input pin                                                                                                                                                                                                                                                                                                                                                                                  |

| IN <sub>tsp3</sub>   | - 3.3V TTL level Schmitt-trigger input pin                                                                                                                                                                                                                                                                                                                                                                             |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                        |

### 1.1 W83628F PIN DESCRIPTION

#### 1.1.1 PCI Interface

| SYMBOL     | PIN   | I/O                | FUNCTION                                                                                                                                                                                                                   |

|------------|-------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31:0]   | 19-26 | I/O24tp3           | PCI Bus Address and Data Signals. The standard PCI address                                                                                                                                                                 |

|            | 30-37 |                    | and data lines. Address is driven with FRAME# assertion, data is                                                                                                                                                           |

|            | 52-59 |                    | driven or received in following clocks.                                                                                                                                                                                    |

|            | 61-63 |                    |                                                                                                                                                                                                                            |

|            | 66-70 |                    |                                                                                                                                                                                                                            |

| C/BE[3:0]# | 28,45 | I/O24tp3           | PCI Bus Command and Byte Enables. During the address                                                                                                                                                                       |

|            | 51,60 |                    | phase of a transaction C/BE[3:0]# define the bus command.<br>During the data phase C/BE[3:0]# are used as Byte Enables.                                                                                                    |

| PCICLK     | 47    | INt                | <b>PCI Bus System Clock</b> . PCICLK provides timing for all transactions on the PCI bus. All other PCI signals are sampled on the rising edge of PCICLK, and all timing parameters are defined with respect to this edge. |

| PCLK_OUT   | 48    | OUT <sub>12t</sub> | PCI Bus System Clock DPLL Output. The PCLK_OUT can reduce the PCICLK Loading and it produced from internal DPLL.                                                                                                           |

#### PRELIMINARY

| 1.1.1 PCI Interface, | continued |                       |                                                                                                                                                                                                       |

|----------------------|-----------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL               | PIN       | I/O                   | FUNCTION                                                                                                                                                                                              |

| FRAME#               | 40        | I/O24tp3              | <b>Frame Signal</b> . FRAME# is driven by the current PCI bus master to indicate the beginning and duration of an access.                                                                             |

| IDSEL                | 29        | INt                   | <b>Initialization Device Select.</b> IDSEL is used as a chip select during configuration read and write transactions. This signal should be externally tied to one of the upper 21 address signals.   |

| STOP#                | 39        | I/O <sub>12tp3</sub>  | <b>Bus Stop#.</b> STOP# indicates the current target is requesting the master to stop the current PCI bus transaction.                                                                                |

| IRDY#                | 41        | I/O <sub>12tp3</sub>  | <b>Initiator Ready.</b> IRDY# indicates the initiating agent ability to complete the current data phase of the PCI bus transaction.                                                                   |

| TRDY#                | 42        | I/O <sub>12tp</sub> 3 | <b>Target Ready.</b> TRDY# indicates the target agent's ability to complete the current data phase of the PCI bus transaction.                                                                        |

| DEVSEL#              | 43        | I/O <sub>12tp3</sub>  | <b>Device Select.</b> W83628F drives DEVSEL# to indicate that it is the target of the current PCI bus transaction. W83628F uses subtractive decoding and the NOGO protocol to claim PCI transactions. |

| SERR#                | 45        | OD <sub>12</sub>      | <b>System Error.</b> SERR# can be pulsed active by any PCI agent that detects a system error condition.                                                                                               |

| PAR                  | 49        | I/O12tp3              | <b>Parity Signal.</b> W83628F generates even parity across AD[31:0] and C/BE[3:0]#.                                                                                                                   |

| PCIRST#              | 71        | INt                   | PCI Reset. W83628F receives PCIRST# as a reset from the PCI Bus.                                                                                                                                      |

#### 1.1.2 Control Logic and Handshaking Signals

| SYMBOL   | PIN  | I/O               | FUNCTION                                                                                                                                                                                                                                               |

|----------|------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HS[2:0]  | 112- | I/O <sub>12</sub> | Handshaking Signals. HS[2:0] connected to W83629D for PCI to ISA SET handshaking signals.                                                                                                                                                              |

|          | 114  |                   | <u>HS1 is handshaking Signal 1, this pin weak pulled-down</u><br><u>during PCIRST# is asserted, and apply a pull-up</u><br><u>resistor(4.7Kohm) to this pin disables ISA bridge</u><br><u>subtraction decoder.</u>                                     |

| ISOLATE# | 72   | INt               | <b>Isolation Control Input. Isolate#</b> is an active low signal by user programming to control the W83628F all output signals to Isolation and Tri-state.                                                                                             |

| NOGO     | 76   | INt               | <b>NOGO,</b> This signal indicates which master initiated the current transaction and also indicates whether or not the current bus cycle is targeted for the ISA bus. This signal is a point-to-point connection between PCI HOST Bridge and W83628F. |

- 7 -

#### PRELIMINARY

#### 1.1.3 ISA Interface Signals

| SYMBOL    | PIN                                                  | I/O                | FUNCTION                                                                                                                                                                                      |

|-----------|------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SA[19:17] | 98-96                                                | OUT24t             | <b>System Address Bus.</b> These are the upper address lines that define the ISA's byte granular address space (up to 1 Mbyte). SA[19:17] are at an unknown state upon PCIRST#.               |

| SA[16:0]  | 94-83<br>81-77                                       | I/O <sub>24t</sub> | <b>System Address Bus.</b> These are the bi-directional lower address lines that define the ISA's byte granular address space (up to 1 Mbyte). SA[16:0] are at an unknown state upon PCIRST#. |

| SD[15:0]  | 110-<br>107,<br>104,<br>103,<br>101,<br>100,<br>8-15 | I/O24t             | System Data. SD[15:0] provide the 16-bit data path for devices<br>residing on the ISA Bus. The W83628F tri-states SD[15:0] during<br>PCIRST#.                                                 |

| AEN       | 118                                                  | OUT <sub>24t</sub> | Address Enable. AEN is asserted during DMA cycles. This signal is also driven high during W83628F initiated refresh cycles. AEN is driven low upon PCIRST#.                                   |

| IOR#      | 120                                                  | I/O24t             | <b>I/O Read.</b> IOR# is the command to an ISA I/O slave device that the slave may drive data on to the ISA data bus (SD[15:0]).                                                              |

| IOW#      | 121                                                  | I/O24t             | <b>I/O Write.</b> IOW# is the command to an ISA I/O slave device that the slave may latch data from the ISA data bus (SD[15:0]).                                                              |

| IOCHRDY   | 116                                                  | I/O24t             | <b>I/O Channel Ready.</b> Resources on the ISA Bus negate<br>IOCHRDY to indicate that additional time (wait states) is required<br>to complete the cycle.                                     |

| SYSCLK    | 99                                                   | OUT <sub>24t</sub> | <b>ISA System Clock.</b> SYSCLK is the reference clock for the ISA bus. The SYSCLK is generated by dividing PCICLK by 3 or 4.                                                                 |

| RSTDRV    | 74                                                   | OUT24t             | <b>Reset Drive.</b> W83628F asserts RSTDRV to reset devices that reside on the ISA Bus. The W83628F asserts this signal while the PCIRST# is asserted.                                        |

| IOCS16#   | 124                                                  | INt                | <b>16-bit I/O Chip Select.</b> This signal is driven by I/O devices on the ISA Bus to indicate that they support 16-bit I/O bus cycles.                                                       |

| SBHE#     | 18                                                   | I/O24t             | <b>System Byte High Enable.</b> SBHE# asserted indicates that a byte is being transferred on the upper byte (SD[15:8]) of the data bus. SBHE# is at an unknown state upon PCIRST#.            |

| IOCHK#    | 105                                                  | INt                | <b>I/O Channel Check.</b> IOCHK# can be driven by any resource on the ISA bus during on detection of an error.                                                                                |

#### PRELIMINARY

| SYMBOL    | PIN                | I/O                | FUNCTION                                                                                                                                                                                                                                                                                                                                          |  |

|-----------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MEMR#     | 6                  | I/O24t             | <b>Memory Read.</b> MEMR# asserted indicates the current ISA bus cycle is a memory read.                                                                                                                                                                                                                                                          |  |

| MEMW#     | 7                  | I/O24t             | <b>Memory Write.</b> MEMW# asserted indicates the current ISA bus cycle is a memory write.                                                                                                                                                                                                                                                        |  |

| MASTER#   | 17                 | INt                | <b>MASTER#.</b> This signal is used with a DREQ line by an ISA master to gain control of the ISA Bus.                                                                                                                                                                                                                                             |  |

| LA[23:17] | 5-2<br>127-<br>125 | I/O24t             | <b>Unlatched Address.</b> The LA[23:17] address lines are bi-<br>directional. These address lines allow accesses to physical<br>memory on the ISA Bus up to 16 Mbytes. LA[23:17] are outputs<br>when the W83628F owns the ISA Bus.                                                                                                                |  |

| ROMCS#    | 73                 | I/O <sub>12</sub>  | ROMCS#, this pin weak pulled-down during PCIRST is<br>asserted, and apply a pull-up resistor (4.7 Kohm) to this pin<br>enable positive decoder of BIOS address range (depend on<br>Configure register 70, bit 3.2). When BIOS assress range is<br>enabled, the PIN is BIOS ROM CS# output.                                                        |  |

| REFRESH#  | 75                 | I/O24t             | <b>Refresh.</b> REFRESH# asserted indicates that a refresh cycle is in progress, or that an ISA master is requesting W83628F to generate a refresh cycle. Upon PCIRST#, this signal is tri-stated.                                                                                                                                                |  |

| ZEROWS#   | 106                | INt                | <b>Zero Wait States.</b> An ISA slave asserts ZEROWS# after its address and command signals have been decoded to indicate that the current cycle can be executed as an ISA zero wait state cycle. ZEROWS# has no effect during 16-bit I/O cycles.                                                                                                 |  |

| SMEMR#    | 117                | OUT24t             | <b>Standard Memory Read.</b> SMEMR# asserted indicates the current ISA bus cycle is a memory read cycle to an address below 1 Mbyte.                                                                                                                                                                                                              |  |

| SMEMW#    | 119                | OUT <sub>24t</sub> | <b>Standard Memory Write.</b> SMEMW# asserted indicates the current ISA bus cycle is a memory write cycle to an address below 1 Mbyte.                                                                                                                                                                                                            |  |

| BALE      | 122                | OUT24t             | <b>Bus Address Latch Enable.</b> BALE is an active high signal asserted by the W83628F to indicate that the address (SA[19:0], LA[23:17]) and SBHE# signal lines are valid.<br>The LA[23:17] address lines are latched on the trailing edge of BALE. BALE remains asserted throughout DMA and ISA master cycles. BALE is driven low upon PCIRST#. |  |

| MEMCS16#  | 123                | OD <sub>24</sub>   | <b>Memory Chip Select 16.</b> MEMCS16# asserted indicates that the memory slave supports 16-bit accesses.                                                                                                                                                                                                                                         |  |

#### 1.1.4 Power Signals

| SYMBOL | PIN             | I/O | FUNCTION     |

|--------|-----------------|-----|--------------|

| VCC    | 1, 82, 102, 115 | PWR | 5V Supply.   |

| 3VCC   | 27, 46, 64      | PWR | 3.3V Supply. |

#### PRELIMINARY

| GND | 16, 38, 50, 65, 95,<br>111, 128 | PWR | Ground. |

|-----|---------------------------------|-----|---------|

|-----|---------------------------------|-----|---------|

#### PRELIMINARY

#### 1.2 W83629D PIN DESCRIPTION

#### 1.2.1 Control Logic and Handshaking Signals

| SYMBOL  | PIN   | I/O               | FUNCTION                                                                                                                                                                                                                                                |  |  |

|---------|-------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| HS[2:0] | 17-15 | I/O <sub>12</sub> | <b>Handshaking Signals.</b> HS[2:0] connected to W83628F for PCI to ISA SET handshaking signals.                                                                                                                                                        |  |  |

| NOGO    | 40    | INt               | <b>NO GO.</b> This signal indicates which master initiated the current transaction and also indicates whether or not the current bus cycle is targeted for the ISA bus. This signal is a point-to-point connection between PCI HOST Bridge and W83628F. |  |  |

| PCICLK  | 44    | INt               | PCI Bus System Clock. PCICLK provides timing for all transactions on the PCI bus. All other PCI signals are sampled on the rising edge of PCICLK, and all timing parameters are defined with respect to this edge.                                      |  |  |

| PCIRST# | 47    | INt               | PCI Reset. W83628F receives PCIRST# as a reset from the PCI Bus.                                                                                                                                                                                        |  |  |

|         |       |                   |                                                                                                                                                                                                                                                         |  |  |

#### 1.2.2 PC/PCI Interface

| SYMBOL     | PIN   | 1/0                | FUNCTION                                                                                                                                                                                                    |  |

|------------|-------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ISAREQ#    | 41    | OUT24t             | <b>ISA Bus Request.</b> This signal is a point-to-point signal between W83629D and a PCI HOST arbiter . The W83629D asserts this signal according to the PC/PCI protocol.                                   |  |

| ISAGNT#    | 42    | INt                | <b>ISA Bus Grant.</b> This signal is a point-to-point signal between<br>W83629D and a PCI HOST Bridge's secondary bus<br>PCPCIGNT# signal. W83629D asserts this signal according to<br>the PC/PCI protocol. |  |

| DRQ        | 35,33 | INt                | DMA Request. The DREQ signal indicates that either a slave                                                                                                                                                  |  |

| [7:5,3:0]  | 31,28 |                    | DMA device is requesting DMA services, or an ISA bus master is requesting use of the ISA bus.                                                                                                               |  |

|            | 26,23 |                    | requesting use of the ISA bus.                                                                                                                                                                              |  |

|            | 21    |                    |                                                                                                                                                                                                             |  |

| DACK       | 34,32 | OUT <sub>24t</sub> | DMA Acknowledge. The DACK# signal indicates that either a                                                                                                                                                   |  |

| [7:5,3:0]# | 30,27 |                    | DMA channel or an ISA bus master has been granted the ISA bus.                                                                                                                                              |  |

|            | 24,22 |                    | bus.                                                                                                                                                                                                        |  |

|            | 20    |                    |                                                                                                                                                                                                             |  |

| тс         | 19    | OUT <sub>24t</sub> | <b>Terminal Count.</b> The W83628F asserts TC to DMA slaves as a terminal count indicator.                                                                                                                  |  |

#### PRELIMINARY

#### 1.2.3 IRQ Serializer Interface

| SYMBOL               | PIN  | I/O                 | FUNCTION                                                                                                     |

|----------------------|------|---------------------|--------------------------------------------------------------------------------------------------------------|

| SERIRQ               | 46   | I/OD <sub>12t</sub> | Serial Interrupt Requested Signals. This signal is for transfer IRQ mode between parallel IRQ to serial IRQ. |

| IRQ                  | 2-6  | INt                 | Parallel Interrupt Requested Input.                                                                          |

| [3:7,9:12,14,<br>15] | 8-13 |                     |                                                                                                              |

#### 1.2.4 Power Signals

| SYMBOL | PIN           | I/O | FUNCTION     |

|--------|---------------|-----|--------------|

| VCC    | 7, 14, 25     | PWR | 5V Supply.   |

| 3VCC   | 48            | PWR | 3.3V Supply. |

| GND    | 1, 18, 29, 43 | PWR | Ground.      |

|        |               |     |              |

#### 1.2.5 NC Pins

| SYMBOL | PIN               | 1/0 | FUNCTION       |

|--------|-------------------|-----|----------------|

| NC     | 36, 37,38, 39, 45 |     | No Connection. |

#### PRELIMINARY

#### 2. PCI CONFIGURATION REGISTERS

#### 2.1 VID-VENDOR IDENTIFICATION REGISTER

Address Offset: 00-01h

**Default Value:** 1050h

Attribute: Read only

This register is read-only and contains Winbond vendor identification number(1050h).

#### 2.2 DID-DEVICE IDENTIFICATION REGISTER

Address Offset: 02-03h Default Value: 0628h Attribute: Read only

N SA SA This register is read-only and contains the device identification number(0628h).

#### 2.3 PCICMD-PCI COMMAND REGISTER

Address Offset: 04-05h Default Value: 0007h Attribute: Read/Write

This register provides control over ISA bridge to generate and response to PCI cycles properly. When a 0 is written to this register, ISA bridge is to be disconnected from PCI bus for all accesses except configuration accesses.

| Bit 15:10 | Reserved.                                          |  |

|-----------|----------------------------------------------------|--|

| Bit 9     | Fast Back to Back. This bit always returns a zero. |  |

| Bit 8     | SERR# Enable.                                      |  |

|           | =1 Enable.                                         |  |

|           | =0 Disable.                                        |  |

| Bit 7     | Wait Cycle Control(Not supported).                 |  |

|           | Hardwired to zero.                                 |  |

| Bit 6     | Parity Error Response(Not supported).              |  |

|           | Hardwired to zero.                                 |  |

| Bit 5     | VGA Palette Snoop Enable(Not supported).           |  |

|           | Hardwired to zero.                                 |  |

| Bit 4     | Memory Write and Invalidate Enable(Not supported). |  |

|           | Hardwired to zero.                                 |  |

|           |                                                    |  |

#### PRELIMINARY

| Bit 3 | Parity Error Response(Not supported).                                                                 |

|-------|-------------------------------------------------------------------------------------------------------|

|       | Hardwired to zero.                                                                                    |

| Bit 2 | Bus Master Enable.                                                                                    |

|       | Hardwired to one. The ISA bridge Bus Masters are always supported to generate a PCI Bus master cycle. |

| Bit 1 | Memory Space Enable.                                                                                  |

|       | Hardwired to one. The ISA bridge Memory space is always enabled.                                      |

| Bit 0 | I/O Space Enable.                                                                                     |

|       | Hardwired to one. The ISA bridge I/O space is always enabled.                                         |

| Address Offset:       | 06-07h              |

|-----------------------|---------------------|

| Default Value:        | 0200h               |

| Attribute:            | Read/Write          |

| This was data a share | atation information |

| 2.4 PCISTS-PCI STATUS REGISTERAddress Offset:06-07hDefault Value:0200hAttribute:Read/WriteThis register shows status information for PCI bus related events. |                                                                                                                                        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| Address Offset                                                                                                                                               | : 06-07h                                                                                                                               |  |

| Default Value:                                                                                                                                               | 0200h                                                                                                                                  |  |

| Attribute:                                                                                                                                                   | Read/Write                                                                                                                             |  |

| This register sh                                                                                                                                             | ows status information for PCI bus related events.                                                                                     |  |

| Bit 15                                                                                                                                                       | Detected Parity Error.                                                                                                                 |  |

|                                                                                                                                                              | Hardwired to zero. The ISA bridge does not check bus parity.                                                                           |  |

| Bit 14                                                                                                                                                       | Signaled System Error.                                                                                                                 |  |

|                                                                                                                                                              | This bit is set when ISA bridge asserts SERR# on PCI bus.                                                                              |  |

| Bit 13                                                                                                                                                       | Received Master Abort Status.                                                                                                          |  |

|                                                                                                                                                              | This bit is set when the ISA bridge is target aborted as a master on the PCI bus. Software sets this bit to 0 by writing a 1 to it.    |  |

| Bit 12                                                                                                                                                       | Received Target Abort Status.                                                                                                          |  |

|                                                                                                                                                              | This bit is set when the ISA bridge target aborts a PCI transaction as a target.<br>Software sets this bit to 0 by writing a 1 to it.  |  |

| Bit 11                                                                                                                                                       | Signaled Target Abort Status.                                                                                                          |  |

|                                                                                                                                                              | This bit is set when the ISA bridge signals a target abort for a PCI transaction.<br>Software sets this bit to 0 by writing a 1 to it. |  |

| Bit 10:9                                                                                                                                                     | DEVSEL# Timing. This 2 bits always return a 01b(medium decode).                                                                        |  |

| Bit 8                                                                                                                                                        | Data Parity Detected(Not supported).                                                                                                   |  |

|                                                                                                                                                              | Hardwired to zero.                                                                                                                     |  |

| Bit 7                                                                                                                                                        | Fast Back-to-Back(Not supported).                                                                                                      |  |

|                                                                                                                                                              | Hardwired to zero.                                                                                                                     |  |

#### PRELIMINARY

| Bit 6   | 66 MHz/ 33 MHz(Only support 33 MHz).                       |

|---------|------------------------------------------------------------|

|         | Hardwired to zero.                                         |

| Bit 5   | User Defineable Features(Not supported).                   |

|         | Hardwired to zero.                                         |

| Bit 4:0 | Reserved.                                                  |

|         | Reserved and will returns zero when reading this register. |

#### 2.5 REVID-REVISION IDENTIFICATION REGISTER

| Address Offset:                                                    | 08h                                    |  |

|--------------------------------------------------------------------|----------------------------------------|--|

| Default Value:                                                     | See lastest stepping information       |  |

| Attribute:                                                         | Read Only                              |  |

| This register shows status information for PCI bus related events. |                                        |  |

| Bit 7:0 Re                                                         | evision Identification Number. 🚽 🕉 🔭 🔨 |  |

|                                                                    |                                        |  |

| 2.6 CCODE-CALSS CODE REGISTER                                      |                                        |  |

| Address Offset:                                                    | 09-0Bh                                 |  |

#### 2.6 CCODE-CALSS CODE REGISTER

| Address Offset: | 09-0Bh                                                                |

|-----------------|-----------------------------------------------------------------------|

| Default Value:  | 060100h                                                               |

| Attribute:      | Read Only                                                             |

| The class code  | register is a read-only register and used to identify the ISA bridge. |

| Bit 23:16       | Base Class Code.                                                      |

|                 | 06h = Bus Bridge                                                      |

| Bit 15:8        | Sub-Class Code.                                                       |

| Bit foio |                         |

|----------|-------------------------|

|          | 01h = PCI to ISA Bridge |

| Bit 7:0  | Programming Interface.  |

|          | 00h                     |

#### 2.7 HEADT-HEAD TYPE REGISTER

| Address Offset: | 0Eh       |

|-----------------|-----------|

| Default Value:  | 00h       |

| Attribute:      | Read Only |

The register is a read-only register and used to indicate that the ISA bridge configuration space adheres to PCI local bus specification. It also indicates that ISA bridge is not a multifunction device.

#### Bit 7 **Multifunction Indicator.**

0 = Not a multifunction device.

#### Bit 6:0 Layout Code.

00h = PCI layout type.

#### PRELIMINARY

#### 2.8 IO\_RCVR-IO RECOVERY REGISTER

| Address Offset |                                                                                |  |

|----------------|--------------------------------------------------------------------------------|--|

| Default Value: |                                                                                |  |

| Attribute:     | Read/Write                                                                     |  |

| Bit 7          | SYSCLK Divider.                                                                |  |

|                | 0 = SYSCLK is equal to PCICLK divided by 4.                                    |  |

|                | 1 = SYSCLK is equal to PCICLK divided by 3.                                    |  |

| Bit 6          | 8-bit I/O Recovery Enable                                                      |  |

|                | 0 = Disable bits 5:3 setting and uses 3.5 SYSCLKs for 8 bit I/O recovery time. |  |

|                | 1 = Enable bits 5:3 setting.                                                   |  |

| Bit 5:3        | 8-bit I/O RecoveryTimes.                                                       |  |

|                | When bit 6=1 ,this 3-bit field defines the additional number of SYSCLKs added  |  |

|                | to standard 3.5 SYSCLK recovery time for 8 bit I/O                             |  |

|                | 000 =0 SYSCLK                                                                  |  |

|                | 001 =1 SYSCLK                                                                  |  |

|                | 010 =2 SYSCLKs                                                                 |  |

|                | 011 =3 SYSCLKs                                                                 |  |

|                | 100 =4 SYSCLKs                                                                 |  |

|                | 101 =5 SYSCLKs                                                                 |  |

|                | 110 =6 SYSCLKs                                                                 |  |

|                | 111 = 7 SYSCLKs                                                                |  |

| Bit 2          | 16-bit I/O Recovery Enable.                                                    |  |

|                | = 0 Ignore bits 1:0 setting and uses 3.5 SYSCLKs for 16-bit I/O recovery time. |  |

|                | = 1 The 16-bit I/O recovery time is decided by bits 1:0.                       |  |

| Bit 1:0        | 16-bit I/O Recovery Times.                                                     |  |

|                | When bit 2=1 ,this 2-bit field defines the additional number of SYSCLKs added  |  |

|                | to standard 3.5 SYSCLK recovery time for 16 bit I/O                            |  |

|                | = 01 1 SYSCLK                                                                  |  |

|                | = 10 2 SYSCLKs                                                                 |  |

|                | = 11 3 SYSCLKs                                                                 |  |

|                | = 00 4 SYSCLKs                                                                 |  |

|                |                                                                                |  |

| 2.9 WISA_\$    | STS-ISA BRIDGE ERROR STATUS REGISTER                                           |  |

| Address Offeet | t. 10h                                                                         |  |

Address Offset:42hDefault Value:00h

#### PRELIMINARY

| Attribute: | Read/Write                                                                                       |

|------------|--------------------------------------------------------------------------------------------------|

| Bit 7:3    | Reserved.                                                                                        |

| Bit 2      | IOCHK# Pin State.                                                                                |

|            | This bit reflects the inverse state of IOCHK# pin on the ISA bus.                                |

| Bit 1      | Reserved.                                                                                        |

| Bit 0      | Byte Lane Error.                                                                                 |

|            | This bit is set if the ISA bridge detects an illegal byte lane combination for a PCI I/O cycles. |

#### 2.10 WISA\_FADC-ISA BRIDGE FAST DECODERS CONTROL REGISTER

| Address Offset | 50h                                          |

|----------------|----------------------------------------------|

| Default Value: | 00h                                          |

| Attribute:     | Read/Write                                   |

| Bit 7          | Enable/Disable Fast I/O Address Decoder # 7. |

| Bit 6          | Enable/Disable Fast I/O Address Decoder # 6. |

| Bit 5          | Enable/Disable Fast I/O Address Decoder # 5. |

| Bit 4          | Enable/Disable Fast I/O Address Decoder # 4. |

| Bit 3          | Enable/Disable Fast I/O Address Decoder # 3. |

| Bit 2          | Enable/Disable Fast I/O Address Decoder # 2. |

| Bit 1          | Enable/Disable Fast I/O Address Decoder # 1. |

| Bit 0          | Enable/Disable Fast I/O Address Decoder # 0. |

# 2.11 WISA\_FAD0MC-ISA BRIDGE FAST DECODERS # 0 MASK CONTROL REGISTER

| Address Offset: | 58h        |

|-----------------|------------|

| Default Value:  | 00h        |

| Attribute:      | Read/Write |

This register is used to mask address bits(A7~A0) for fast address decoder # 0, if the corresponding bit of this register is set to a 1, the corresponding address bit(A7~A0) is ignore by the faster address decoder # 0.

#### PRELIMINARY

#### 2.12 WISA FAD0MC-ISA BRIDGE FAST DECODERS # 1 MASK CONTROL REGISTER

Address Offset: 59h Default Value: 00h Attribute: Read/Write

This register is used to mask address bits(A7~A0) for fast address decoder # 1, if the corresponding bit of this register is set to a 1, the corresponding address bit(A7~A0) is ignore by the faster address decoder # 1.

# ·爱方養養 2.13 WISA FAD0MC-ISA BRIDGE FAST DECODERS # 2 MASK CONTROL REGISTER m.cr

Address Offset: 5Ah Default Value: 00h Attribute: Read/Write

This register is used to mask address bits(A7~A0) for fast address decoder # 2, if the corresponding bit of this register is set to a 1, the corresponding address bit(A7~A0) is ignore by the faster address decoder # 2.

#### 2.14 WISA FADOMC-ISA BRIDGE FAST DECODERS # 3 MASK CONTROL REGISTER

Address Offset: 5Bh **Default Value:** 00h Attribute: Read/Write

This register is used to mask address bits(A7~A0) for fast address decoder # 3, if the corresponding bit of this register is set to a 1, the corresponding address bit(A7~A0) is ignore by the faster address decoder # 3.

#### 2.15 WISA FAD0MC-ISA BRIDGE FAST DECODERS # 4 MASK CONTROL REGISTER

Address Offset: 5Ch Default Value: 00h Attribute: Read/Write

This register is used to mask address bits(A7~A0) for fast address decoder # 4, if the corresponding bit of this register is set to a 1, the corresponding address bit(A7~A0) is ignore by the faster address decoder # 4.

#### PRELIMINARY

#### 2.16 WISA FAD0MC-ISA BRIDGE FAST DECODERS # 5 MASK CONTROL REGISTER

Address Offset: 5Dh Default Value: 00h Attribute: Read/Write

This register is used to mask address bits(A7~A0) for fast address decoder # 5, if the corresponding bit of this register is set to a 1, the corresponding address bit(A7~A0) is ignore by the faster address decoder # 5.

# 2.17 WISA FAD0MC-ISA BRIDGE FAST DECODERS # 6 MASK CONTROL

REGISTER

Address Offset:

5Eh

Default Value:

00h

Attribute:

Read/Write

This register is used to mask address bits(A7~A0) for fast address decoder # 6, if the corresponding

bit of this register is set to a 1, the corresponding address bit(A7~A0) is ignore by the faster address

# 2.18 WISA FAD0MC-ISA BRIDGE FAST DECODERS # 7 MASK CONTROL

#### REGISTER

decoder # 6.

Address Offset: **Default Value:**

00h

5Fh

Attribute:

decoder # 7.

Read/Write This register is used to mask address bits(A7~A0) for fast address decoder # 7, if the corresponding bit of this register is set to a 1, the corresponding address bit(A7~A0) is ignore by the faster address

# 2.19 WISA FADCB0-ISA BRIDGE FAST DECODERS # 0 BASE ADDRESS REGISTER

60-61h\*\* Address Offset: Default Value: 0000h Attribute: Read/Write This register contains the base address for fast address decoder # 0.A

\*\*Note: 60h is lower byte and 61h is upper byte.

#### PRELIMINARY

# 2.20 WISA\_FADCB1-ISA BRIDGE FAST DECODERS # 1 BASE ADDRESS REGISTER

Address Offset:62-63hDefault Value:0000hAttribute:Read/WriteThis register contains the base address for fast address decoder # 1.

# 2.21 WISA\_FADCB2-ISA BRIDGE FAST DECODERS # 2 BASE ADDRESS REGISTER

Address Offset:64-65hDefault Value:0000hAttribute:Read/WriteThis register contains the base address for fast address decoder # 2

#### 2.22 WISA\_FADCB3-ISA BRIDGE FAST DECODERS # 3 BASE ADDRESS REGISTER

Address Offset:66-67hDefault Value:0000hAttribute:Read/WriteThis register contains the base address for fast address decoder # 3.

#### 2.23 WISA\_FADCB4-ISA BRIDGE FAST DECODERS # 4 BASE ADDRESS REGISTER

Address Offset:68-69hDefault Value:0000hAttribute:Read/WriteThis register contains the base address for fast address decoder # 4.

#### 2.24 WISA\_FADCB5-ISA BRIDGE FAST DECODERS # 5 BASE ADDRESS REGISTER

| Address Offset:                                                       | 6A-6Bh     |  |

|-----------------------------------------------------------------------|------------|--|

| Default Value:                                                        | 0000h      |  |

| Attribute:                                                            | Read/Write |  |

| This register contains the base address for fast address decoder # 5. |            |  |

#### PRELIMINARY

# 2.25 WISA\_FADCB6-ISA BRIDGE FAST DECODERS # 6 BASE ADDRESS REGISTER

Address Offset:6C-6DhDefault Value:0000hAttribute:Read/WriteThis register contains the base address for fast address decoder # 6.

### 2.26 WISA\_FADCB7-ISA BRIDGE FAST DECODERS # 6 BASE ADDRESS REGISTER

| Address Offset:                                                       | 6E-6Fh     | 1 15 15  |

|-----------------------------------------------------------------------|------------|----------|

| Default Value:                                                        | 0000h      | 1 3ª - C |

| Attribute:                                                            | Read/Write | 3        |

| This register contains the base address for fast address decoder # 0. |            |          |

### 2.27 WISA\_CTRLREG1-ISA BRIDGE CONTROL REGISTER 1

| Address Offset                            | : 70h                                                                       |  |

|-------------------------------------------|-----------------------------------------------------------------------------|--|

| Default Value:                            | 0000 <u>01s</u> sb                                                          |  |

| Attribute:                                | Read/Write                                                                  |  |

| Power-on sett                             | ing bits bit 1:0 are power-on set by ROMCS# and HS1.                        |  |

| Bit 7-6                                   | Reserved.                                                                   |  |

| Bit 5-4                                   | = 00 Send AD Bus with no STEP                                               |  |

|                                           | = 01 Send AD Bus with 2 STEP                                                |  |

|                                           | = 10 Send AD Bus with 4 STEP                                                |  |

|                                           | = 11 Reverse                                                                |  |

| <u>Bit 3-2</u>                            | = 00 1MB BIOS ROM positive decode.                                          |  |

| = 01 2MB BIOS ROM positive decode.        |                                                                             |  |

| <u>= 10 4MB BIOS ROM positive decode.</u> |                                                                             |  |

|                                           | = 11 8MB BIOS ROM positive decode.                                          |  |

|                                           |                                                                             |  |

| <u>Bit 1</u>                              | =0 Disable High-Address BIOS ROM decoder.                                   |  |

|                                           | =1 Enable High-Address BIOS ROM decoder.                                    |  |

|                                           | This bit can be set/reset by ROMCS# power-on setting during PCIRST# assert. |  |

| Bit 0                                     | =0 Normal mode.                                                             |  |

|                                           | =1 Disable ISA Bridge subtraction decoder.                                  |  |

|                                           | This bit can be set/reset by HS1 power-on setting during PCIRST# assert.    |  |

|                                           |                                                                             |  |

#### PRELIMINARY

#### 2.28 WISA\_CTRLREG2-ISA BRIDGE CONTROL REGISTER 2

| : 71h                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h                                                                                                                                                                  |

| Read/Write                                                                                                                                                           |

| =0 Enable IRQ11.                                                                                                                                                     |

| =1 Disable IRQ11.                                                                                                                                                    |

| =0 Enable IRQ10.                                                                                                                                                     |

| =1 Disable IRQ10.                                                                                                                                                    |

| =0 Enable IRQ9.                                                                                                                                                      |

| =1 Disable IRQ9.                                                                                                                                                     |

| <ul> <li>=1 Disable IRQ10.</li> <li>=0 Enable IRQ9.</li> <li>=1 Disable IRQ9.</li> <li>=0 Enable IRQ7.</li> <li>=1 Disable IRQ7.</li> <li>=0 Enable IRQ7.</li> </ul> |

| =1 Disable IRQ7.                                                                                                                                                     |

| =0 Enable IRQ6.                                                                                                                                                      |

| =1 Disable IRQ6.                                                                                                                                                     |

| =0 Enable IRQ5.                                                                                                                                                      |

| =1 Disable IRQ5.                                                                                                                                                     |

| =0 Enable IRQ4.                                                                                                                                                      |

| =1 Disable IRQ4.                                                                                                                                                     |

| =0 Enable IRQ3.                                                                                                                                                      |

| =1 Disable IRQ3.                                                                                                                                                     |

|                                                                                                                                                                      |

### 2.29 WISA\_CTRLREG3-ISA BRIDGE CONTROL REGISTER 3

| Address Offset: | 72h               |

|-----------------|-------------------|

| Default Value:  | 00h               |

| Attribute:      | Read/Write        |

| Bit 7-3         | Reserved.         |

| Bit 2           | =0 Enable IRQ15.  |

|                 | =1 Disable IRQ15. |

| Bit 1           | =0 Enable IRQ14.  |

|                 | =1 Disable IRQ14. |

| Bit 0           | =0 Enable IRQ12.  |

|                 | =1 Disable IRQ12. |

#### PRELIMINARY

#### 2.30 WISA\_CTRLREG4-ISA BRIDGE CONTROL REGISTER 4

| Address Offset: | 73h                             |                    |

|-----------------|---------------------------------|--------------------|

| Default Value:  | 00h                             |                    |

| Attribute:      | Read/Write                      |                    |

| Bit7            | =0 Enable DRQ 7.                |                    |

|                 | =1 Disable DRQ 7.               |                    |

| Bit 6           | =0 Enable DRQ6.                 |                    |

|                 | =1 Disable DRQ6.                |                    |

| Bit 5           | =0 Enable DRQ5.                 | a.                 |

|                 | =1 Disable DRQ5.                | E 3 to the CON. CN |

| Bit 4           | Reserved.                       | 1. 1. 1.           |

| Bit 3           | =0 Enable DRQ 3.                | 3 3 m              |

|                 | =1 Disable DRQ 3.               | C C                |

| Bit 2           | =0 Enable DRQ 2.                |                    |

|                 | =1 Disable DRQ 2.               |                    |

| Bit 1           | =0 Enable DRQ 1.                |                    |

|                 | =1 Disable DRQ 1.               |                    |

| Bit 0           | =0 Enable DRQ 0.                |                    |

|                 | =1 Dis <mark>able</mark> DRQ 0. |                    |

|                 |                                 |                    |

#### 2.31 WISA\_TSTREG-ISA BRIDGE TEST REGISTER

| Address Offset:                                     | 80h                                                                         |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| Default Value:                                      | 04h                                                                         |  |  |

| Attribute:                                          | Read/Write                                                                  |  |  |

| Bit 7-5                                             | Reserved and should not write data to this register.                        |  |  |

| Bit 4                                               | =0 80h port decoding on subtrastive cycles of LPC I/F.                      |  |  |

| =1 80h port decoding on positive cycles of LPC I/F. |                                                                             |  |  |

|                                                     | This Bit must be set 1 when LPC I/F is only decoding on positive cycles,but |  |  |

|                                                     | when the bridge is used in PIIX4 for test set the bit to 0.                 |  |  |

| Bit 3                                               | Reserved and should not write data to this register.                        |  |  |

|                                                     |                                                                             |  |  |

|                                                     |                                                                             |  |  |

|                                                     |                                                                             |  |  |

Bit 2-0

000

- 0.8 nS.

For Winbond Internal Reference only.

001

- 0.6 nS.

#### PRELIMINARY

| 010 | - 0.4 nS. |

|-----|-----------|

| 011 | - 0.2 nS. |

| 100 | 0 nS.     |

| 101 | +0.2 nS.  |

| 110 | +0.4 nS.  |

| 111 | +0.6 nS.  |

#### PRELIMINARY

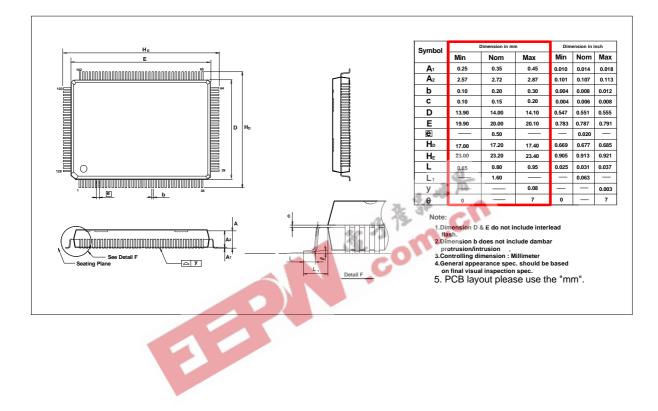

#### 3. PACKAGE DIMENSIONS 1 FOR W83628F (128-PIN PQFP)

#### PRELIMINARY

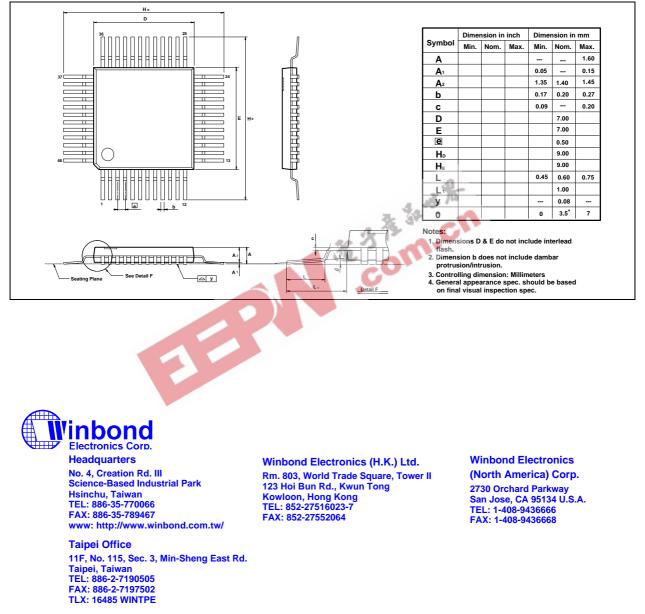

#### 4. PACKAGE DIMENSIONS 2 FOR W83629D (48-PIN LQFP)

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this data sheet belong to their original owners

#### PRELIMINARY

#### 5. REVISION NOTICES.

| 1998.11.16         | Add High-Address BIOS ROM decoder function(CS#/HS3). (Page 7 & Page 20)      |

|--------------------|------------------------------------------------------------------------------|

| 1998.11.19         | Change decode range to #FFF00000~#FFFFFFF & #000E0000~#000FFFFF.             |

| 1999.01.17         | Supports 3 fully ISA Compatible Slots without Buffering                      |

|                    | Rename HS3. it is renamed to ROMCS# in W83628F,and NC in W83629D.            |

| 1999.04.21<br>when | Indicate the Bit 4 of offset address 80h is used to enable 80h port decoding |

only positive decoding switched of LPC I/F.