# ADVANCED VL-IDE DISK CONTROLLER

### GENERAL DESCRIPTION

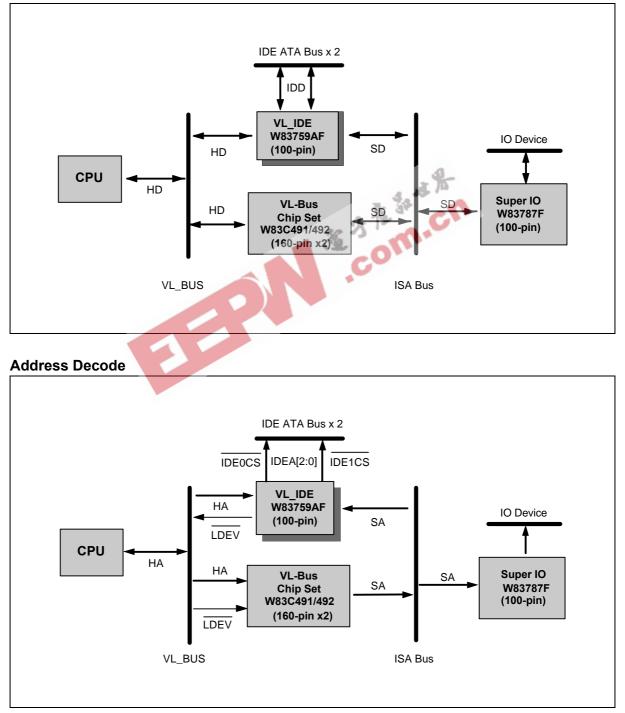

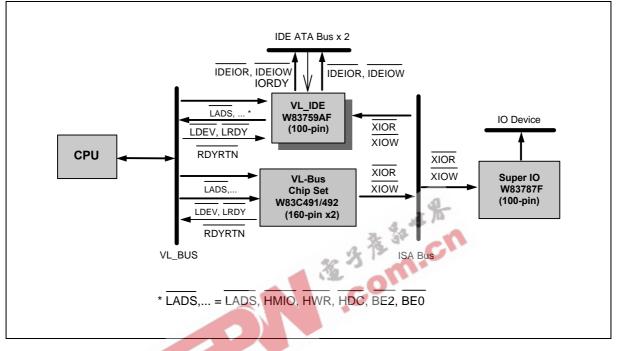

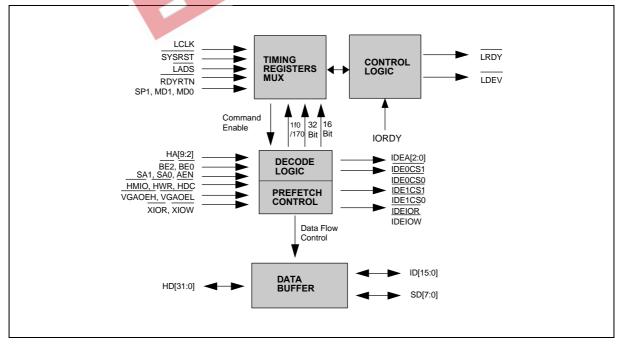

The W83759A is an advanced version of Winbond's popular VL-IDE interface chip, the W83759. The W83759A retains all of the features and compatibility of the W83759 (the chip meets the ANSI ATA 4.0 specification for IDE hard disk operation and the VESA VL-Bus 2.0 specification for PC local bus devices) while incorporating new features to meet Enhanced IDE, SFF-8011, ATA-2, and Fast-ATA specifications.

### Supports Disk Capacity of Greater than 528 MB

The W83759A's driver can handle remapping from BIOS CHS mode to HDD LBA mode. This scheme enables users to break the 528 MB per drive barrier, allowing full use of BLOS INT13 CHS information 子養養 in drives with a capacity of up to 8.4 GB.

### **High Speed Host Transfer Rate**

The W83759A supports Enhanced IDE PIO mode 3 and Fast ATA PIO mode 3 and 4 timing; jumper settings or driver programming can be used to select the PIO mode and a 33 or 50 MHz VL-Bus clock. Different programming timing can be selected for different drives in the same system. The burst transfer rate is shown in the following table.

| ATA PIO<br>MODE | IDE COMMAND CYCLE<br>TIME (nS) | BURST TRANSFER<br>RATE (MB/sec) | IORDY THROTTLE<br>CONTROL |

|-----------------|--------------------------------|---------------------------------|---------------------------|

| 0               | 600                            | 3.33                            | Option                    |

| 1               | 383                            | 5.22                            | Option                    |

| 2               | 240                            | 8.33                            | Option                    |

| 3               | 180                            | 11.1                            | Required                  |

| 4               | 120                            | 16.6                            | Required                  |

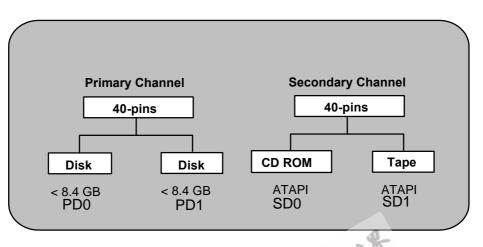

#### **Dual IDE Channels**

Like the W83759, the W83759A supports a secondary IDE address (170h-177h/376h) and IRQ15 for applications with four hard disk drives. Additionally, the primary and secondary channels can be independently enabled or disabled by jumper settings or software programming.

#### Non-disk IDE Peripherals

Because the command cycle can be programmed individually for each drive and dual IDE channels are supported, non-disk IDE peripherals (such as an ATAPI CD-ROM or tape drive) can be attached to the secondary IDE without affecting the transfer rate of the ATA disk drive. Sales of ATAPI IDE CD-ROMs are expected to grow rapidly as these devices become a standard part of many users' desktop PC setup.

#### **Winbond** Electronics Corp.

The W83759A provides all of the next-generation ATA-IDE requirements, including support for high capacity disk drives, high speed host transfers, multiple IDE peripherals, and non-disk IDE peripherals. It makes high-performance, low-cost, easy-to-use IDE machines possible.

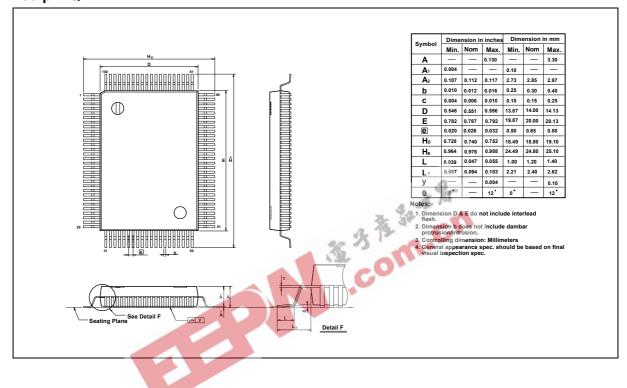

The W83759A is pin-to-pin backward compatible with the W83759. In addition to the advanced features described above, the W83759A supports automatic power-down, standby, and suspend APM power management states for green PC applications. This new chip is packaged in a 100-pin QFP.

The table below compares the W83759 and W83759A:

|                       | W83759           | W83759A           |

|-----------------------|------------------|-------------------|

| Dual Channel IDE      | Yes              | Yes               |

| 8.4 G Max. Cap.       | Software Driving | Software Driving  |

| PIO Mode 3, 4 Control | No               | Yes*              |

| DMA Mode Control      | No               | Yes*              |

| IOCHRDY Control       | No               | Yes*              |

| IDE Timing Control    | Jumper           | Jumper or Driver* |

| Prefetch Control      | n Control No     |                   |

| Power Saving Control  | aving Control No |                   |

| ATAPI Protocol        | Software Driving | Software Driving  |

\* All control is drive-by-drive (per drive selectability)

### FEATURES

- Pin-to-pin backward compatible with W83759 VL-IDE Interface chip

- · VESA VL-Bus Rev 2.0 compatible, connects directly to local bus and four IDE drives

- Direct interface to various ANSI ATA/ATA-2/FAST ATA/IDE-2/Enhanced IDE drives

- Supports 32 and 16-bit data transfer

- Fully software programmable for command active/recovery time and address setup, data hold time

- Built-in VL-Bus to 16-bit IO data buffer for special applications

- Fully supports Enhanced IDE features, including Fast PIO, Mode 3/4, IORDY flow control, prefetch control

- Supports dual channels to allow up to four drives or non-disk devices (ATAPI CD-ROM and tape drives)

- · Pipeline pre-fetched reads and posted writes for concurrent disk and host operations

- Independent access timing for all drives (primary/secondary and master/slave)

- All Enhanced IDE new features may be disabled/enabled via driver or power-on setting by per drive selectability

- ATA/Mode 0-4 PIO speed may be set as default timing of each drive via power-on jumper setting

- Supports slave DMA mode protocol (reserved)

- Supports auto power-down, standby, suspend APM power management state for green PCs

- Primary and secondary channel can be independently enabled/disabled by software or jumper setting

- Supports drivers for DOS, Windows, OS/2, UNIX, and Netware

- Packaged in 100-pin QFP

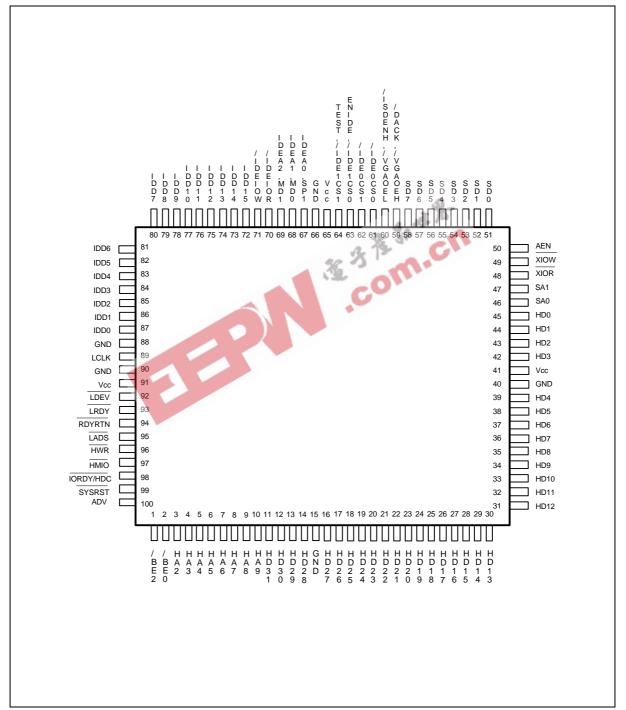

### **PIN CONFIGURATION**

### PIN DESCRIPTION

| SYMBOL        | PIN    | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |        |       | VL-Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ADV           | 100    | I-PU  | Advanced mode indicator.<br>When high, chip is in W83759A mode. When low, chip is in<br>W83759 mode.                                                                                                                                                                                                                                                                                                                                                                                                         |

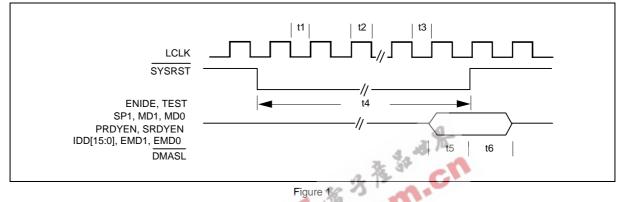

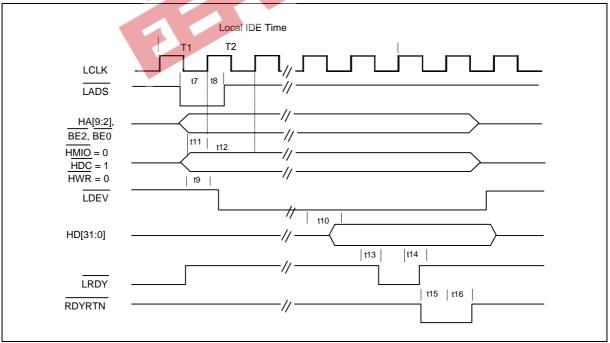

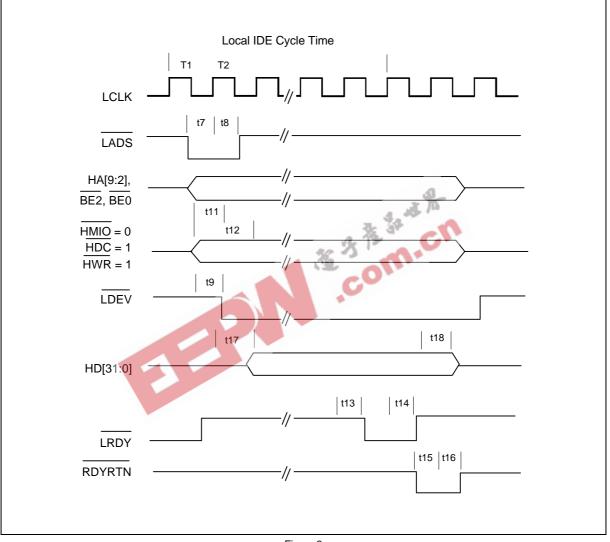

| LCLK          | 89     | I     | VL-Bus clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SYSRST        | 99     | I     | System reset.<br>When active, the power-on setting pin acts as input.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

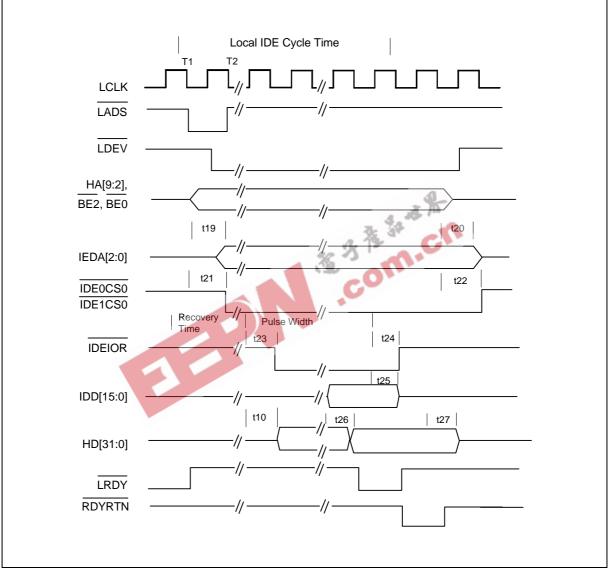

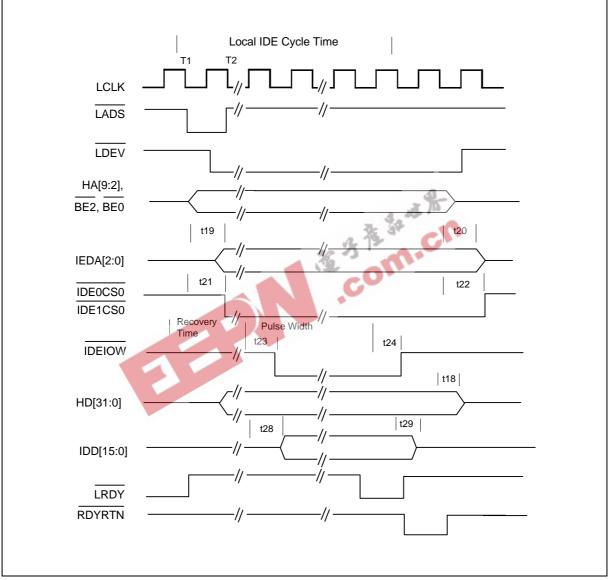

| LADS          | 95     | I     | Address data strobe.<br>An active low input signal indicates that there is a valid address<br>and command on the bus.                                                                                                                                                                                                                                                                                                                                                                                        |

| IORDY<br>/HDC | 98     | I     | In W83759A mode: Enhanced IDE IORDY flow control input. Used to throttle disk's PIO data transfers to improve PIO mode.<br>In W83759 mode: Host data or code status. Used to distinguish between IO and interrupt or halt cycles.                                                                                                                                                                                                                                                                            |

| НМІО          | 97     | I-PU  | Host memory or I/O status.<br>Used to distinguish between memory and I/O cycles.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| HWR           | 96     |       | Host write or read status.<br>Used to distinguish between write and read cycles.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BE2<br>BE0    | 1<br>2 | -     | Byte enable bits 2 and 0 from the host CPU address bus.<br>These active low inputs specify which bytes will be valid for host<br>read and write data transfers. When $\overline{BE2}$ is low, the host performs<br>a 32-bit hard disk data transfer cycle when $\overline{LDEV}$ is active.                                                                                                                                                                                                                  |

| LDEV          | 92     | 0     | Local device.<br>An active low output signal which indicates that the current host<br>CPU command cycle is a valid W83759A I/O address (1F0h or<br>170h).                                                                                                                                                                                                                                                                                                                                                    |

| LRDY          | 93     | Tri-O | Local ready.<br>An active low output that indicates when a CPU transfer has been<br>completed. During a cycle LRDY will first be enabled and driven<br>high. When the cycle is completed, LRDY will immediately be<br>pulled low and will remain active for one T-state. Then it will drive<br>high for one T-state before finally being disabled to end the<br>sequence.<br>This signal is shared with all other VL-Bus targets and driven by<br>W83759A only during cycles W83759A has claimed as its own. |

| Pin Description, co | ontinued                |            |                                                                                                                                                                                                                                       |

|---------------------|-------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL              | PIN                     | TYPE       | DESCRIPTION                                                                                                                                                                                                                           |

| RDYRTN              | 94                      | I          | Ready return.<br>An active low signal that indicates the end of the current host<br>CPU transfer.<br>Usually RDYRTN is tied directly to the RDY signal of the host<br>CPU.                                                            |

| HA[9:2]             | 10-3                    | I          | Host address bits 9 through 2 from the host address bus.                                                                                                                                                                              |

| HD[31:0]            | 11–14<br>19–39<br>42–45 | I/O        | Host data.<br>This is the 32-bit bidirectional data bus that connects to the host CPU. HD[7:0] define the lowest data byte, while D[31:24] define the most significant byte by the $\overline{\text{BE}[2:0]}$ signals. The HD bus is |

|                     |                         |            | normally in a high-impedance state and is driven by the W83759A only during data register (1F0h or 170h) read cycles and VGA ( $\overline{VGAOEH} = 0$ or $\overline{VGAOEL} = 0$ ) read cycles.                                      |

|                     |                         |            | Drive Interface                                                                                                                                                                                                                       |

| PRDYEN<br>/IDE0CS0  | 61                      | I/O<br>-PU | When SYSRST is active, this is an input that latches on the rising edge of SYSRST.                                                                                                                                                    |

|                     |                         | 1          | PRDYEN: A high input enables the IORDY flow control function of the primary channel (IDE0) and a low input disables the IDE0's flow control function.                                                                                 |

|                     |                         |            | IDE0CS0 : When SYSRST is inactive, this pin is an active low output used to select the command block registers in the IDE0 drive (1F0h–1F7h).                                                                                         |

| SRDYEN              | 62                      | I/O<br>-PU | When $\overline{SYSRST}$ is active, this is an input that latches on the rising edge of $\overline{SYSRST}$ .                                                                                                                         |

|                     |                         |            | SRDYEN: A high input enables the IORDY flow control function of the secondary channel (IDE1) and a low disables the IDE1's flow control function.                                                                                     |

|                     |                         |            | <b>IDE0CS1</b> : When <b>SYSRST</b> is inactive, this pin is an active low output used to select the alternate status register of the control block registers in the IDE0 drive (3F6).                                                |

| Pin | Description, | continued |

|-----|--------------|-----------|

|     | Booonpaon,   | oomanaoa  |

| SYMBOL            | PIN | TYPE       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENIDE<br>/IDE1CS0 | 63  | I/O<br>-PU | When $\overline{\text{SYSRST}}$ is active, this is an input that latches on the rising edge of $\overline{\text{SYSRST}}$ .                                                                                                                                                                                                                                   |

|                   |     |            | ENIDE: In W83759 mode (ADV = low), this power-on-setting pin controls if the chip enable or disable. In W83759A mode (ADV = high), this pin controls if the IDE0 channel enable or disable. A high input enables and a low input disables the IDE0 channel.                                                                                                   |

|                   |     |            | IDE1CS0 : When SYSRST is inactive, this pin is an active low output and is used to select the command block registers in the IDE1 drive (170h–177h).                                                                                                                                                                                                          |

| TEST<br>/IDE1CS1  | 64  | I/O<br>-PU | When $\overrightarrow{\text{SYSRST}}$ is active, this is an input that latches on the rising edge of $\overrightarrow{\text{SYSRST}}$ .                                                                                                                                                                                                                       |

|                   |     |            | TEST: In W83759 mode, this power-on-setting pin controls whether<br>both dual channels are enabled or only the primary channel is<br>enabled. A high input enables IDE0 and IDE1 simultaneously and a<br>low input enables IDE0 only. In W83759A mode, this pin controls<br>whether the IDE1 channel enable or disable controls the IDE0<br>channel as ENIDE. |

|                   |     | -          | <b>IDE1CS1:</b> When <b>SYSRST</b> is inactive, this pin is an active low output used to select the alternate status register of the control block registers in the IDE1 drive (376).                                                                                                                                                                         |

| EMD1<br>/IDEIOR   | 70  | 1/0<br>-PU | When $\overline{\text{SYSRST}}$ is active, this is an input that latches on the rising edge of $\overline{\text{SYSRST}}$ .                                                                                                                                                                                                                                   |

|                   |     |            | EMD1: This power-on-setting pin combines with EMD0 to set the initial enhanced timing mode of hard disk access cycles when the enhanced mode is selected via the POSS3 configuration register.                                                                                                                                                                |

|                   |     |            | IDEIOR : Drive I/O read. An active low output that enables data to<br>be read from the drive. The duration and repetition rate of IDEIOR<br>cycles are determined by the type of IDE drive, as specified by<br>MD1 and MD0, in W83759 mode or by EMD1 and EMD0 in<br>W83759A enhanced mode.                                                                   |

| Pin Description, continued | Pin | Descri | otion. | continued |  |

|----------------------------|-----|--------|--------|-----------|--|

|----------------------------|-----|--------|--------|-----------|--|

| SYMBOL          | PIN | TYPE       |                             | DE             | SCRIPT    | ΓΙΟΝ      |                                                                      |

|-----------------|-----|------------|-----------------------------|----------------|-----------|-----------|----------------------------------------------------------------------|

| EMD0<br>/IDEIOW | 71  | I/O<br>-PU | When SYSRS<br>edge of SYSRS |                | s is an i | nput that | latches on the rising                                                |

|                 |     |            | initial enhanced            | d timing mode  | of hard   | disk acce | ith EMD1 to set the<br>ess cycles when the<br>enfiguration register. |

|                 |     |            | ATA PIO mode                | Access Time    | EMD1      | EMD0      |                                                                      |

|                 |     |            | 2                           | 240 nS         | 1         | 1         |                                                                      |

|                 |     |            | 3                           | 180 nS         | 1         | 0         |                                                                      |

|                 |     |            | 3                           | 180 nS         | 0         | 1         |                                                                      |

|                 |     |            | 4                           | 120 n <b>S</b> | 0         | 0         |                                                                      |

|                 |     |            | be written to th            | e drive. The d | uration a | and repet | t that enables data to<br>ition rate of IDEIOW<br>e, as specified by |

| MD1<br>/IDEA2,  | 69  | I/O<br>-PD | When SYSRS                  |                |           | function  | as inputs and latch                                                  |

| MD0<br>/IDEA1   | 68  |            | U                           | A mode of IDE  | E Drive.  | MD0 and   | MD1 are used to                                                      |

|                 |     |            | ATA PIO mode                | Access Time    | EMD1      | EMD0      |                                                                      |

|                 |     |            | 0                           | 600 nS         | 0         | 0         |                                                                      |

|                 |     |            | 0+                          | 500 nS         | 0         | 1         |                                                                      |

|                 |     |            | 1                           | 400 nS         | 1         | 0         |                                                                      |

|                 |     |            | 2                           | 240 nS         | 1         | 1         |                                                                      |

|                 |     |            |                             |                |           |           | . Drive address bits 2<br>ister selection in the                     |

| Pin Description, continued |

|----------------------------|

|----------------------------|

| SYMBOL        | PIN    | TYPE       | DESCRIPTION                                                                                                                                               |

|---------------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| SP1<br>/IDEA0 | 67     | I/O<br>-PD | When $\overline{\text{SYSRST}}$ is active, this pin is an input that latches on the rising edge of $\overline{\text{SYSRST}}$ .                           |

|               |        |            | SP1: VL-Bus speed select. A high input configures the W83759A to run at from 33 MHz to 50 MHz; a low input configures the W83759A to run at under 33 MHz. |

|               |        |            | IDEA0: IDE drive address bit 0. Drive address bit 0 is output to the IDE connector for register selection in the drive.                                   |

| IDD[15:0]     | 72–87  | I/O<br>-PU | When $\overline{\text{SYSRST}}$ is active, these pins function as inputs and latch on the rising edge of $\overline{\text{SYSRST}}$ .                     |

|               |        |            | As power-on setting pins, IDD[15:8] are latched to the POSS3 register and IDD[7:0] are latched to the POSS2 register.                                     |

|               |        |            | As the drive data bus, bits 15 through 0 are the 16-bit bidirectional data bus that connects to the IDE drive.                                            |

|               |        |            | IDD[7:0] define the lowest data byte. The IDD bus is normally in a pull-high state and is driven with valid data by the W83759A only                      |

|               |        |            | during IDE or VGA (VGAOEH = 0 or $\overrightarrow{VGAOEL} = 0$ ) write cycles.                                                                            |

|               |        |            | ISA-Bus Interface                                                                                                                                         |

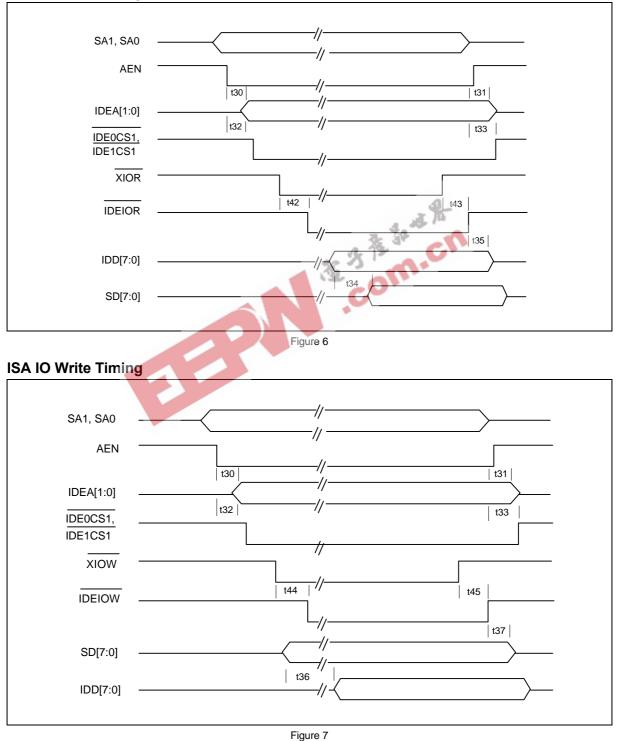

| SA[1:0]       | 47, 46 |            | ISA address bits 1 and 0.<br>Used to select the hard disk I/O registers.                                                                                  |

| SD[7:0]       | 58-51  | 1/0        | These signals provide data bus bits 0 through 7 for the CPU and IDE I/O devices. SD0 is the least significant bit and SD7 is the most significant bit.    |

| XIOR          | 48     | I          | $\overline{\text{XIOR}}$ instructs the hard disk I/O device to drive its data onto the SD data bus.                                                       |

| XIOW          | 49     | I          | $\overline{\text{XIOW}}$ instructs the hard disk I/O device to read the data on the SD data bus.                                                          |

| AEN           | 50     | I          | When this line is active (high), the DMA controller has control of the address bus. A low is the address enable.                                          |

| Pin Descri | otion, | continued |

|------------|--------|-----------|

|            |        |           |

| SYMBOL           | PIN                      | TYPE       | DESCRIPTION                                                                                                                                                                            |

|------------------|--------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                          |            | Special Bus Control Interface                                                                                                                                                          |

| SUSP,            | 59                       | I-PU       | This pin is a multi-function input pin.                                                                                                                                                |

| DACK,<br>VGAOEH  |                          |            | $\overline{\text{SUSP}}$ : In suspend enable mode, indicates that the W83759A will enter the suspend state when low and resume operation when high.                                    |

|                  |                          |            | DACK: In DMA transfer enable mode, used to indicate when the DMA transfer cycle occurs.                                                                                                |

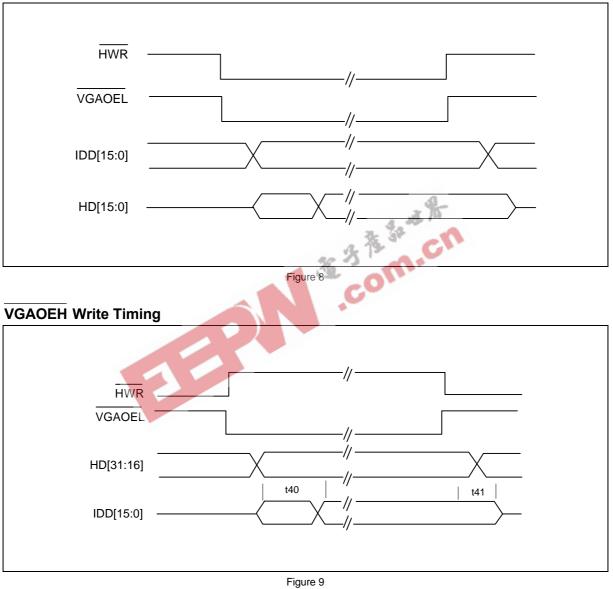

|                  |                          |            | VGAOEH: In VGA buffer enable mode, this active low input controls the input enable for the data transceivers that connect the ID[15:0] pins to the HD[31:16] pins.                     |

| DMASL,<br>VGAOEL | 60                       | I/O<br>-PU | When SYSRST is active, this pin is an input that latches on the rising edge of SYSRST.                                                                                                 |

| /ISDENH          |                          |            | DMASL: This power-on setting pin combines with SUSPEN<br>(IDD11 power-on setting pin) to determine which mode the<br>W83759A is in.                                                    |

|                  |                          |            | DMASL SUSPEN Mode                                                                                                                                                                      |

|                  |                          |            | 1 X VGA buffer enable                                                                                                                                                                  |

|                  |                          |            | 0 1 Suspend enable                                                                                                                                                                     |

|                  |                          |            | 0 0 DMA transfer enable                                                                                                                                                                |

|                  |                          |            | $\overline{\text{VGAOEL}}$ : In VGA buffer enable mode, this active low input controls the input enable for the data transceivers that connect the ID[15:0] pins to the HD[15:0] pins. |

|                  |                          |            | <b>ISDENH</b> : In DMA transfer enable mode, this output pin controls the activity of the high byte buffer between IDD[15:8] and SD[15:8].                                             |

| Vcc              | 41, 65,<br>91            |            | +5V power supply                                                                                                                                                                       |

| GND              | 15, 40,<br>66, 88,<br>90 |            | Ground reference                                                                                                                                                                       |

### **CONFIGURATION REGISTERS**

Several configuration registers are implemented in the W83759A. These registers are accessible in single-chip mode through the index/data port. The index/data port address is 1B4h/1B8h or 134h/138h, depending on whether pin IDD0 is high or low at power-on.

When the W83759A is in multi-chip mode (IDD1 is low at power-on setting), an ID code should be written to 1B0h/130h (IDIN port). The W83759A will then enter the programming sequence if the ID code matches the chip ID (determined by IDD2, IDD3 at power-on setting) or leave the programming sequence if the ID code does not match. After the chip has entered the programming sequence, the chip ID can be read by reading 1BCh/13Ch (IDOUT port).

|                  | IDD0_P is HIGH | IDD0_P is LOW |

|------------------|----------------|---------------|

| IDIN port (W/O)  | 1B0h*          | 130h**        |

| Index port (R/W) | 1B4h           | 134h          |

| data port (R/W)  | 1B8h 🔤 🔩       | 138h          |

| IDOUT port (R/O) | 1BCh           | 13Ch          |

\* The alias base addresses of 1B0h are XB0h and YB0h, where "X" means 0, 4, 8, C and "Y" means 1, 5, 9, D.

\*\* The alias base addresses of 130h are X30h and Y30h, where "X" means 0, 4, 8, C and "Y" means 1, 5, 9, D.

| INDEX               | Bit 7        | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1   | Bit 0   | Default<br>Value |

|---------------------|--------------|----------|----------|----------|----------|----------|---------|---------|------------------|

| 80h(R/O)<br>POSS1   | ADV          | SP1      | MD1      | MD0      | PRDYEN   | SRDYEN   | IDEN1   | IDEN0   | 8Fh              |

| 81h(R/W)<br>POSP1   | ADV_P        | SP1_P    | MD1_P    | MD0_P    | PRDYEN_P | SRDYEN_P | IDEN1_P | IDEN0_P | 8Fh              |

| 82h(R/O)<br>POSS2   | PD0LEN       | PD1LEN   | SD0LEN   | SD1LEN   | DSL1     | DSL0     | CRLK#   | CRSL    | FFh              |

| 83h(R/W)<br>POSP2   | PD0LE_P      | PD1LEN_P | SD0LEN_P | SD1LEN_P | DSL1_P   | DSL0_P   | CRLK#_P | CRSL_P  | FFh              |

| 84h(R/O)<br>POSS3   | PD0EM#       | PD1EM#   | SD0EM#   | SD1EM#   | SUSPEN   | STBY#    | APD     | SWAP#   | FFh              |

| 85h(R/W)<br>POSP3   | PD0EM#_P     | PD1EM#_P | SD0EM#_P | SD1EM#_P | SUSPEN_P | STBY#_P  | APD_P   | SWAP#_P | FFh              |

| 86h(R/W)<br>ALTCTL  | DMASL#_<br>P | Reserved | EMD1     | EMD0     | PEMD1_P  | PEMD0_P  | SEMD1_P | SEMD0_P | 80h              |

| 87h(R/O)<br>REVID   | DMASL#       | Reserved | PDRV     | SDRV     | Rev 3    | Rev 2    | Rev 1   | Rev 0   | 8Ah              |

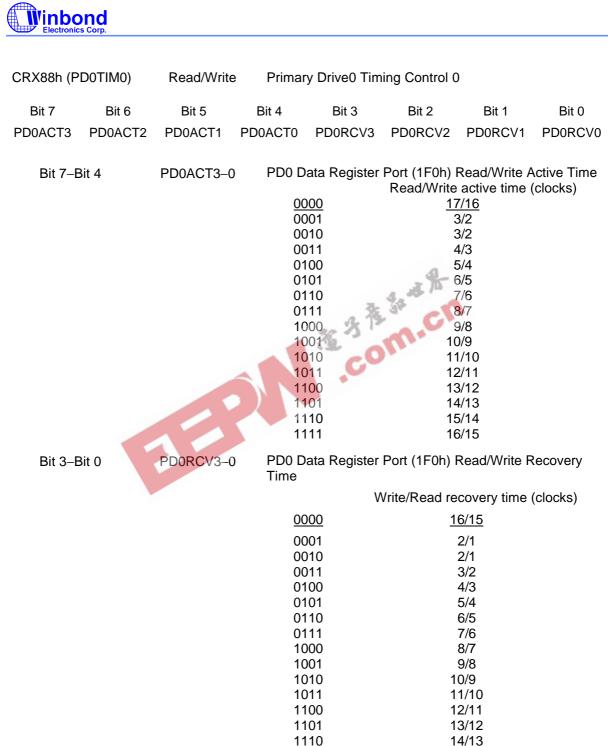

| 88h(R/W)<br>PD0TIM0 | PD0ACT3      | PD0ACT2  | PD0ACT1  | PD0ACT0  | PD0RCV3  | PD0RCV2  | PD0RCV1 | PD0RCV0 | 00h              |

| 89h(R/W)<br>PD0TIM1 | PD0AST1      | PD0AST0  | PD0DHT1  | PD0DHT0  | PD0PRE#  | PD0DMA#  | PD0RDY# | PD0ADV  | 00h              |

| 8Ah(R/W)<br>PD1TIM0 | PD1ACT3      | PD1ACT2  | PD1ACT1  | PD1ACT0  | PD1RCV3  | PD1RCV2  | PD1RCV1 | PD1RCV0 | 00h              |

| 8Bh(R/W)<br>PD1TIM1 | PD1AST1      | PD1AST0  | PD1DHT1  | PD1DHT0  | PD1PRE#  | PD1DMA#  | PD1RDY# | PD1ADV  | 00h              |

| 8Ch(R/W)<br>SD0TIM0 | SD0ACT3      | SD0ACT2  | SD0ACT1  | SD0ACT0  | SD0RCV3  | SD0RCV2  | SD0RCV1 | SD0RCV0 | 00h              |

| 8Dh(R/W)<br>SD0TIM1 | SD0AST1      | SD0AST0  | SD0DHT1  | SD0DHT0  | SD0PRE#  | SD0DMA#  | SD0RDY# | SD0ADV  | 00h              |

| 8Eh(R/W)<br>SD1TIM0 | SD1ACT3      | SD1ACT2  | SD1ACT1  | SD1ACT0  | SD1RCV3  | SD1RCV2  | SD1RCV1 | SD1RCV0 | 00h              |

| 8Fh(R/W)<br>SD1TIM1 | SD1AST1      | SD1AST0  | SD1DHT1  | SD1DHT0  | SD1PRE#  | SD1DMA#  | SD1RDY# | SD1ADV  | 00h              |

#### Index map of configuration registers:

| CRX80h (F   | POSS1)  | Read Only     | Power                                                         | on Setting S                     | tatus 1                       |                    |              |  |

|-------------|---------|---------------|---------------------------------------------------------------|----------------------------------|-------------------------------|--------------------|--------------|--|

| Bit7        | Bit6    | Bit5          | Bit4                                                          | Bit3                             | Bit2                          | Bit1               | Bit0         |  |

| ADV         | SP1     | MD1           | MD0                                                           | PRDYEN                           | SRDYEN                        | IDEN1              | IDEN0        |  |

| Bit         | 7       | ADV           | Power-on setting value of ADV pin<br>Initial application mode |                                  |                               |                    |              |  |

|             |         | 0             | No ad                                                         | vanced mode                      | application                   |                    |              |  |

|             |         | <u>1</u>      | <u>Advan</u>                                                  | ced mode ap                      | plication                     |                    |              |  |

| Bit 6       | 6       | SP1           |                                                               | -on setting va<br>VESA bus o     |                               |                    |              |  |

|             |         | <u>0</u><br>1 | -                                                             | <u>&lt; 33 MHz</u><br>< > 33 MHz | Sa CI                         |                    |              |  |

| Bit 5, 4 MD | D1, MD0 |               |                                                               | -on setting va<br>t HDD host tr  |                               | 2, IDEA1 pin       |              |  |

|             |         |               | MD1                                                           | MD0                              |                               |                    |              |  |

|             |         |               | 0                                                             | 0 Mode                           | 0 (cycle tim                  | <u>e = 600 nS)</u> |              |  |

|             |         |               | 0                                                             | 1 Mode                           | Mode 0+ (cycle time = 500 nS) |                    |              |  |

|             |         |               | 1                                                             | 0 Mode                           | 1 (cycle tim                  | e = 400 nS)        |              |  |

|             |         |               | 1                                                             | 1 Mode                           | 2 (cycle tim                  | e = 240 nS)        |              |  |

| Bit 3       | 3       | PRDYEN        |                                                               | -on setting va<br>state of prima |                               |                    | w control    |  |

|             |         |               | 0                                                             | Disable IOC                      | HRDY flow co                  | ontrol             |              |  |

|             |         |               | <u>1</u>                                                      | Enable IOCI                      | HRDY flow co                  | ontrol             |              |  |

| Bit 2       | 2       | SRDYEN        |                                                               | -on setting va<br>state of secor |                               |                    | flow control |  |

|             |         |               | 0                                                             | Disable IO                       | CHRDY flow                    | control            |              |  |

|             |         |               | <u>1</u>                                                      | Enable IOC                       | HRDY flow o                   | <u>control</u>     |              |  |

| Bit 1,      | , 0     | IDEN1, IDEN   |                                                               | -on setting va<br>state of IDE E |                               |                    | 0 pins       |  |

|             |         | hen ADV_P     | IDEN1                                                         | IDEN0                            | Primary II                    | DE Secor           | ndary IDE    |  |

|             | =       | 0             | Х                                                             | 0                                | disabled                      | disa               | abled        |  |

|             |         |               | 0                                                             | 1                                | enabled                       | disa               | abled        |  |

|             |         |               | <u>1</u>                                                      | <u>1</u>                         | enabled                       | ena                | abled        |  |

Continued

|                             |       | when ADV_P |       | /_P IDEN1 IDEN0 Primary II |             | DE Secondary IDE |         |         |

|-----------------------------|-------|------------|-------|----------------------------|-------------|------------------|---------|---------|

|                             |       | = 1        |       | -                          | 0           | disabled         |         | bled    |

|                             |       |            |       |                            | 0           | disabled         |         | bled    |

|                             |       |            |       | 0                          | 1 enabled   |                  |         | abled   |

|                             |       |            |       | <u>1</u>                   | <u>1</u>    | <u>enabled</u>   | ena     | bled    |

| CRX81h (POSP1) Read / Write |       | Write      | P     | ower-on                    | Setting Pro | ogramming 1      |         |         |

| Bit 7                       | Bit 6 | Bit 5      | Bit 4 | Bit 3                      |             | Bit 2            | Bit 1   | Bit 0   |

| ADV_P                       | SP1_P | MD1_P      | MD0_P | PRDYEN_                    | P SRI       | DYEN_P           | IDEN1_P | IDEN0_P |

After power-on, the content of the POSP1 register is equal to that of the POSS1 register. The host can program POSP1 to modify the power-on settings.

| Bit 7    | ADV_P               | Programming application mode                                                                    |  |  |  |  |  |  |

|----------|---------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|          |                     | 0 No advanced mode application                                                                  |  |  |  |  |  |  |

|          |                     | <u>1</u> Advanced mode application                                                              |  |  |  |  |  |  |

| Bit 6    | SP1_P               | Select VESA bus operating CLK                                                                   |  |  |  |  |  |  |

|          |                     | VLCLK 33 MHz                                                                                    |  |  |  |  |  |  |

|          |                     | 1 VLCLK > 33 MHz                                                                                |  |  |  |  |  |  |

| Bit 5, 4 | MD1_P,              | Select default HDD host transfer mode                                                           |  |  |  |  |  |  |

|          | MD0_P               | MD1_P MD0_P                                                                                     |  |  |  |  |  |  |

|          |                     | $\underline{0} \qquad \underline{0} \qquad \underline{Mode \ 0}  (cycle time = 600 \text{ nS})$ |  |  |  |  |  |  |

|          |                     | 0 1 Mode 0+ (cycle time = 500 nS)                                                               |  |  |  |  |  |  |

|          |                     | 1 0 Mode 1 (cycle time = 400 nS)                                                                |  |  |  |  |  |  |

|          |                     | 1 1 Mode 2 (cycle time = 240 nS)                                                                |  |  |  |  |  |  |

| Bit 3    | PRDYEN_P            | Primary channel IOCHRDY flow control                                                            |  |  |  |  |  |  |

|          |                     | 0 Disable IOCHRDY flow control                                                                  |  |  |  |  |  |  |

|          |                     | <u>1</u> Enable IOCHRDY flow control                                                            |  |  |  |  |  |  |

| Bit 2    | SRDYEN_P            | Secondary channel IOCHRDY flow control                                                          |  |  |  |  |  |  |

|          |                     | 0 Disable IOCHRDY flow control                                                                  |  |  |  |  |  |  |

|          |                     | 1 Enable IOCHRDY flow control                                                                   |  |  |  |  |  |  |

| Bit 1, 0 | IDEN1_P,<br>IDEN0_P | IDE ENable control                                                                              |  |  |  |  |  |  |

|                        |                                                                                                       | hen ADV_P | IDEN1_                                                                         | P IDEN0_P                                                                                                                                               | Primary                                                                                                     | IDE Seco                                   | ndary IDE |  |

|------------------------|-------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------|--|

|                        | = 0                                                                                                   |           |                                                                                | 0                                                                                                                                                       | disabled                                                                                                    | disa                                       | bled      |  |

|                        |                                                                                                       |           | 0                                                                              | 0 1 enabled                                                                                                                                             |                                                                                                             | disa                                       | bled      |  |

|                        |                                                                                                       |           | <u>1</u>                                                                       | <u>1</u>                                                                                                                                                | enabled                                                                                                     | enat                                       | bled      |  |

|                        |                                                                                                       | hen ADV_P | IDEN1_                                                                         | P IDEN0_P                                                                                                                                               | Primary                                                                                                     | IDE Seco                                   | ndary IDE |  |

|                        | =                                                                                                     | 1         | 0                                                                              | 0                                                                                                                                                       | disabled                                                                                                    | disal                                      | bled      |  |

|                        |                                                                                                       |           | 1                                                                              | 0                                                                                                                                                       | disabled                                                                                                    | enab                                       | led       |  |

|                        |                                                                                                       |           | 0                                                                              | 1                                                                                                                                                       | enabled                                                                                                     | disa                                       | bled      |  |

|                        |                                                                                                       |           | <u>1</u>                                                                       | <u>1</u>                                                                                                                                                | enabled                                                                                                     | enat                                       | bled      |  |

|                        |                                                                                                       |           |                                                                                |                                                                                                                                                         | AN                                                                                                          |                                            |           |  |

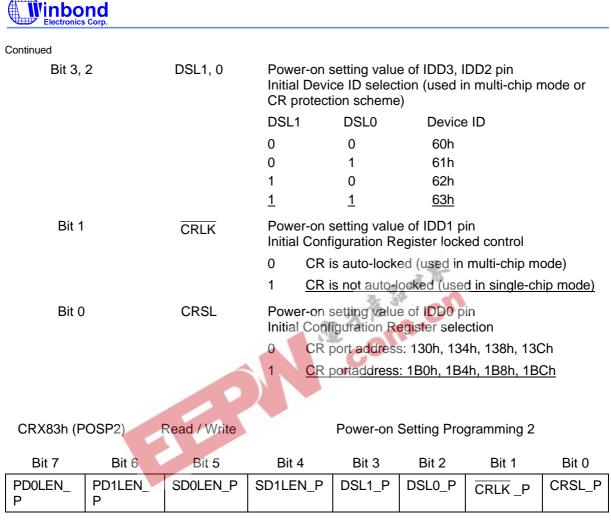

| CRX82h (F              | POSS2)                                                                                                | Read Only |                                                                                | Power                                                                                                                                                   | -on Setting                                                                                                 | Status 2                                   |           |  |

| 0.0.00(.               | ,                                                                                                     |           |                                                                                | 26 3                                                                                                                                                    | 0.                                                                                                          |                                            |           |  |

| Bit 7                  | Bit 6                                                                                                 | Bit 5     | Bit 4                                                                          | Bit 3                                                                                                                                                   | Bit 2                                                                                                       | Bit 1                                      | Bit 0     |  |

| PD0LEN                 | PD1LEN                                                                                                | SD0LEN    | SD1LEN                                                                         | DSL1                                                                                                                                                    | DSL0                                                                                                        | CRLK                                       | CRSL      |  |

| Bit                    | 7                                                                                                     | PDOLEN    | Dowor                                                                          | on setting valu                                                                                                                                         |                                                                                                             | ain                                        |           |  |

| DIL                    |                                                                                                       | FDOLLIN   |                                                                                | rimary Drive 0                                                                                                                                          |                                                                                                             |                                            | ntrol     |  |

|                        |                                                                                                       |           | 0                                                                              | Disable local                                                                                                                                           | device                                                                                                      |                                            |           |  |

|                        |                                                                                                       |           | <u>1</u>                                                                       | Enable local                                                                                                                                            | <u>device</u>                                                                                               |                                            |           |  |

| Bit 6                  | 6                                                                                                     | PD1LEN    |                                                                                |                                                                                                                                                         |                                                                                                             |                                            |           |  |

|                        | Bit 6 PD1LEN Power-on setting value of IDD6 pin<br>Initial Primary Drive 1 (PD1) local device control |           |                                                                                |                                                                                                                                                         |                                                                                                             |                                            |           |  |

| 0 Disable local device |                                                                                                       |           |                                                                                |                                                                                                                                                         |                                                                                                             |                                            | ntrol     |  |

|                        |                                                                                                       |           | Initial P                                                                      | rimary Drive 1                                                                                                                                          | (PD1) loca                                                                                                  |                                            | ntrol     |  |

|                        |                                                                                                       | TDILLN    | Initial P                                                                      | rimary Drive 1                                                                                                                                          | (PD1) loca<br>device                                                                                        |                                            | ntrol     |  |

| Bit s                  | 5                                                                                                     | SDOLEN    | Initial P<br>0<br><u>1</u><br>Power-o                                          | rimary Drive 1<br>Disable local<br><u>Enable local</u><br>on setting valu                                                                               | (PD1) loca<br>device<br>device<br>e of IDD5 p                                                               | al device cor<br>Din                       |           |  |

| Bit \$                 | 5                                                                                                     |           | Initial P<br>0<br><u>1</u><br>Power-o<br>Initial S                             | rimary Drive 1<br>Disable local<br><u>Enable local</u><br>on setting valu<br>econdary Driv                                                              | (PD1) loca<br>device<br>device<br>e of IDD5 p<br>e 0 (SD0) l                                                | al device cor<br>Din                       |           |  |

| Bit \$                 | 5                                                                                                     |           | Initial P<br>0<br><u>1</u><br>Power-o<br>Initial S<br>0                        | rimary Drive 1<br>Disable local<br><u>Enable local</u><br>on setting valu<br>econdary Driv<br>Disable local                                             | (PD1) loca<br>device<br>device<br>e of IDD5 p<br>e 0 (SD0) l<br>device                                      | al device cor<br>Din                       |           |  |

|                        | -                                                                                                     | SDOLEN    | Initial P<br>0<br><u>1</u><br>Power-o<br>Initial S<br>0<br><u>1</u>            | rimary Drive 1<br>Disable local<br><u>Enable local</u><br>on setting valu<br>econdary Driv<br>Disable local<br><u>Enable local</u>                      | (PD1) loca<br>device<br>device<br>e of IDD5 p<br>e 0 (SD0) l<br>device<br>device                            | al device cor<br>Din<br>ocal device        |           |  |

| Bit 4<br>Bit 4         | -                                                                                                     |           | Initial P<br>0<br><u>1</u><br>Power-o<br>Initial S<br>0<br><u>1</u><br>Power-o | rimary Drive 1<br>Disable local<br><u>Enable local</u><br>on setting valu<br>econdary Driv<br>Disable local                                             | (PD1) loca<br>device<br>e of IDD5 p<br>e 0 (SD0) l<br>device<br><u>device</u><br>e of IDD4 p                | al device cor<br>Din<br>Ocal device<br>Din | control   |  |

|                        | -                                                                                                     | SDOLEN    | Initial P<br>0<br><u>1</u><br>Power-o<br>Initial S<br>0<br><u>1</u><br>Power-o | rimary Drive 1<br>Disable local<br><u>Enable local</u><br>on setting value<br>econdary Driv<br>Disable local<br><u>Enable local</u><br>on setting value | (PD1) loca<br>device<br>e of IDD5 p<br>e 0 (SD0) l<br>device<br><u>device</u><br>e of IDD4 p<br>e 1 (SD1) l | al device cor<br>Din<br>Ocal device<br>Din | control   |  |

After power-on, the content of the POSP2 register is equal to that of the POSS2 register. The host can program POSP2 to modify the power-on settings.

| Bit 7 | PD0LEN_P | Primary Drive 0 (PD0) local device control   |

|-------|----------|----------------------------------------------|

|       |          | 0 Disable local device                       |

|       |          | <u>1</u> Enable local device                 |

| Bit 6 | PD1LEN_P | Primary Drive 1 (PD1) local device control   |

|       |          | 0 Disable local device                       |

|       |          | 1 Enable local device                        |

| Bit 5 | SD0LEN_P | Secondary Drive 0 (SD0) local device control |

|       |          | 0 Disable local device                       |

|       |          | <u>1</u> Enable local device                 |

|           | s Corp. |              |            |                                                                       |               | •••           | 03737A       |  |  |

|-----------|---------|--------------|------------|-----------------------------------------------------------------------|---------------|---------------|--------------|--|--|

| Continued |         |              |            |                                                                       |               |               |              |  |  |

| Bit 4     | 4       | SD1LEN_P     | Secon      | dary Drive 1(                                                         | SD1) local d  | evice control |              |  |  |

|           |         |              | 0          | 0 Disable local device                                                |               |               |              |  |  |

|           |         |              | <u>1</u>   | <u>1</u> <u>Enable local device</u>                                   |               |               |              |  |  |

| Bit 3,    | , 2     | DSL1, 0_P    |            | Device ID selection (used in multi-chip mode or CR protection scheme) |               |               |              |  |  |

|           |         |              | DSL1_      | P DSL0_F                                                              | Device        | ID            |              |  |  |

|           |         |              | 0          | 0                                                                     | 60h           |               |              |  |  |

|           |         |              | 0          | 1                                                                     | 61h           |               |              |  |  |

|           |         |              | 1          | 0                                                                     | 62h           |               |              |  |  |

|           |         |              | <u>1</u>   | <u>1</u>                                                              | <u>63h</u>    |               |              |  |  |

| Bit       | 1       | CRLK _P      | Config     | uration Regis                                                         | ter locked co | ontrol        |              |  |  |

|           |         | _            | 0          | CR is auto-                                                           | locked (mult  | -chip mode)   |              |  |  |

|           |         |              | <u>1</u>   | <u>CR is not a</u>                                                    | uto-locked (s | single-chip m | ode <u>)</u> |  |  |

| Bit (     | 0       | CRSL P       | Config     | uration Regis                                                         | ter selection |               |              |  |  |

|           |         | _            | - 0 Ŭ      |                                                                       |               | 134h, 138h,   | 13Ch         |  |  |

|           |         |              | ) <u>1</u> |                                                                       |               | 1B4h, 1B8h,   |              |  |  |

|           |         |              | -          | <u></u>                                                               |               | ,,            |              |  |  |

|           |         |              |            |                                                                       |               |               |              |  |  |

| CRX84h (F | POSS3)  | Read Only    |            | Powe                                                                  | er-on Setting | Status 3      |              |  |  |

| Bit 7     | Bit 6   | Bit 5        | Bit 4      | Bit 3                                                                 | Bit 2         | Bit 1         | Bit 0        |  |  |

| PD0EM     | PD1EM   | <b>SD0EM</b> | SD1EM      | SUSPEN                                                                | STBY#         | APD           | SWAP         |  |  |

| Bit       | 7       | PD0EM        |            | -on setting va<br>setting of PD0<br>Enhanced t                        | ) enhanced t  |               |              |  |  |

|           |         |              | <u>1</u>   | Programma                                                             | able timing   |               |              |  |  |

| Bit 6     | 6       | PD1EM        |            | -on setting va<br>setting of PD1                                      |               |               |              |  |  |

|           |         |              | 0          | Enhanced t                                                            | iming         |               |              |  |  |

|           |         |              | <u>1</u>   | Programma                                                             | able timing   |               |              |  |  |

| Bit \$    | 5       | SD0EM        |            | -on setting va<br>setting of SD0                                      |               |               |              |  |  |

|           |         |              | 0          | Enhanced t                                                            | iming         |               |              |  |  |

|           |         |              | <u>1</u>   | Programma                                                             | able timing   |               |              |  |  |

|           |         |              |            |                                                                       |               |               |              |  |  |

| Continued |        |                                                                                            |

|-----------|--------|--------------------------------------------------------------------------------------------|

| Bit 4     | SD1EM  | Power-on setting value of IDD12 pin<br>Initial setting of SD1 enhanced timing enable       |

|           |        | 0 Enhanced timing                                                                          |

|           |        | 1 Programmable timing                                                                      |

| Bit 3     | SUSPEN | Power-on setting value of IDD11 pin<br>Initial setting of SUSPend function                 |

|           |        | 0 Support DMA mode if $\overline{DMASL} P = 0$ and $ADV_P = 1$                             |

|           |        | 1 Support suspend function if $\overline{DMASL} P = 0$<br>and $ADV_P = 1$ .                |

| Bit 2     | STBY   | Power-on setting value of IDD10 pin<br>Initial setting of STandBy state                    |

|           |        | 0 W83759A is in standby state                                                              |

|           |        | 1 W83759A is in normal state                                                               |

| Bit 1     | APD    | Power-on setting value of IDD9 pin<br>Initial setting of auto Power-down                   |

|           |        | 0 Auto power-down off                                                                      |

|           |        | 1 Auto power-down on                                                                       |

| Bit 0     | SWAP   | Power-on setting value of IDD8 pin<br>Initial primary, secondary channel connection select |

|           |        | 0 Primary channel connect to IDE1<br>Secondary channel connect to IDE0                     |

|           |        | 1 Primary channel connect to IDE0<br>Secondary channel connect to IDE1                     |

| CRX85h (F | POSP3)  | Read/ Write | Power-on Setting Programming 3 |                                    |         |       |           |  |

|-----------|---------|-------------|--------------------------------|------------------------------------|---------|-------|-----------|--|

| Bit 7     | Bit 6   | Bit 5       | Bit 4                          | Bit 3                              | Bit 2   | Bit 1 | Bit 0     |  |

| PD0EM_P   | PD1EM_P | SD0EM_P     | SD1EM_P                        | SUSPEN_P                           | STBY _P | APD_P | SWAP_P    |  |

| Bit 7     | 7       | PD0EM_P     |                                | setting prograr<br>able setting of |         |       | ig enable |  |

|           |         |             | 0 Enhanced timing              |                                    |         |       |           |  |

|           |         |             | <u>1</u> Pr                    | ogrammable ti                      | ming    |       |           |  |

| Winbond<br>Electronics Corp. |          |          | VV 05 / 57                                                                          |

|------------------------------|----------|----------|-------------------------------------------------------------------------------------|

| ontinued                     |          |          |                                                                                     |

| Bit 6                        | PD1EM_P  |          | on setting programming of IDD14 pin<br>nmable setting of PD1 enhanced timing enable |

|                              |          | 0        | Enhanced timing                                                                     |

|                              |          | <u>1</u> | Programmable timing                                                                 |

| Bit 5                        | SD0EM_P  |          | on setting programming of IDD13 pin<br>nmable setting of SD0 enhanced timing enable |

|                              |          | 0        | Enhanced timing                                                                     |

|                              |          | <u>1</u> | Programmable timing                                                                 |

| Bit 4                        | SD1EM_P  |          | on setting programming of IDD12 pin<br>nmable setting of SD1 enhanced timing enable |

|                              |          | 0        | Enhanced timing                                                                     |

|                              |          | <u>1</u> | Programmable timing                                                                 |

| Bit 3                        | SUSPEN_P |          | on setting value of IDD11 pin<br>nmable setting of SUSPend function                 |

|                              |          |          | Support suspend function if $\overline{DMASL} P = 0$<br>and $ADV_P = 1$             |

|                              |          |          | <u>Support DMA transfer if</u> $\overline{DMASL} = 0$<br>and $\overline{ADV} = 1$   |

| Bit 2                        | STBY_P   |          | on setting value of IDD10 pin<br>nmable setting of STandBy state                    |

|                              |          | 0        | W83759A is in standby state                                                         |

|                              |          | <u>1</u> | W83759A is in normal state                                                          |

| Bit 1                        | APD_P    |          | on setting value of IDD9 pin<br>tting of auto power-down                            |

|                              |          | 0        | Auto power-down off                                                                 |

|                              |          | 1        | Auto power-down on                                                                  |

| Bit 0                        | SWAP_P   |          | on setting programming of IDD8 pin<br>nmable primary, secondary channel connectior  |

|                              |          |          | Primary channel connect to IDE1<br>Secondary channel connect to IDE0                |

|                              |          |          | Primary channel connect to IDE0<br>Secondary channel connect to IDE1                |

| Electronics Co           | rp.                                                                                                                                                                                 |                       |                   |                                                   |                |              |              |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------|---------------------------------------------------|----------------|--------------|--------------|--|--|

| Continued<br>CRX86h (ALT | Continued<br>CRX86h (ALTCTL) Read / Write Alternative Control Register                                                                                                              |                       |                   |                                                   |                |              |              |  |  |

| Bit 7                    | Bit 6                                                                                                                                                                               | Bit 5                 | Bit 4             | Bit 3                                             | Bit 2          | Bit 1        | Bit 0        |  |  |

| DMASL _P                 | Reserved                                                                                                                                                                            | EMD1                  | EMD0              | PEMD1_P                                           | PEMD0_P        | SEMD1_P      | SEMD0_P      |  |  |

| Bit 7                    | DMASL _P Power-on setting value of VGAOEL pin.   After power-on, this bit can be programmed to mo the DMA disable/enable power-on setting.   0 DMA mode enabled if SUSPEN_P = 0 and |                       |                   |                                                   |                | -            |              |  |  |

|                          |                                                                                                                                                                                     |                       | 1                 | ADV_P = 1<br>DMA mode                             |                |              |              |  |  |

| Bit 6                    |                                                                                                                                                                                     | Reserved              | <u>1</u><br>0 (de | fault)                                            | ulsableu       |              |              |  |  |