# WM2636 12-bit Serial Input Voltage Output DAC with Internal Reference

Production Data, July 1999, Rev 1.0

## DESCRIPTION

The WM2636 is a 12-bit voltage output, resistor string digital-toanalogue converter that can be powered down under software control. Power down reduces current consumption to 10nA.

An internal precision voltage reference is provided which can source up to 1mA. This can therefore be used as an external system reference.

The device has been designed to interface efficiently to industry standard microprocessors and DSPs, including the TMS320 family. The WM2636 is programmed with a 16-bit serial word comprising 4 control bits and 12 data bits.

Excellent performance is delivered with a typical DNL of 0.5 LSBs. The settling time of the DAC is programmable to allow the designer to optimize speed versus power dissipation. The output stage is buffered by a x2 gain near rail-to-rail amplifier.

The device is available in an 8-pin SOIC package. Commercial temperature (0° to 70°C) and Industrial temperature (-40° to 85°C) variants are supported.

## FEATURES

- 12-bit voltage output DAC

- Single supply from 2.7V to 5.5V

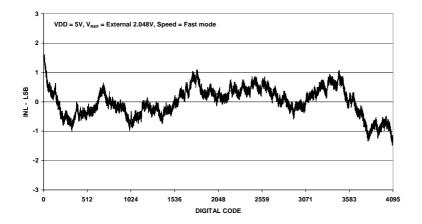

- DNL ±0.5 LSBs, INL ±2.0 LSBs

- Very low power consumption (3V supply):

- 4.2mW, slow mode

- 8.1mW, fast mode

- TMS320, (Q)SPI™, and Microwire™ compatible serial interface

- Programmable settling time of 3.5µs or 1µs typical

- · High impedance reference input buffer

- Power down mode 10nA

## **APPLICATIONS**

- Battery powered test instruments

- · Digital offset and gain adjustment

- · Battery operated/remote industrial controls

- Machine and motion control devices

- Wireless telephone and communication systems

- Speech synthesis

- Arbitrary waveform generation

## **ORDERING INFORMATION**

| DEVICE   | TEMP. RANGE  | PACKAGE    |

|----------|--------------|------------|

| WM2636CD | 0° to 70°C   | 8-pin SOIC |

| WM2636ID | -40° to 85°C | 8-pin SOIC |

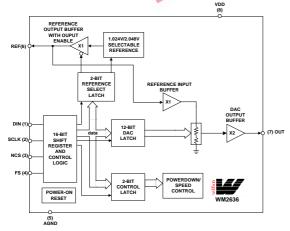

# **BLOCK DIAGRAM**

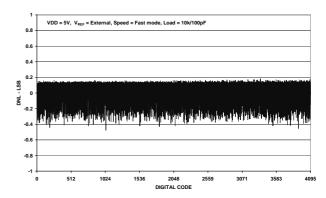

# **TYPICAL PERFORMANCE**

**Production Data**

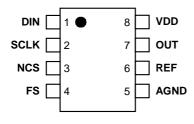

## **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| PIN NO | NAME    | TYPE            | DESCRIPTION                                  |  |  |  |  |

|--------|---------|-----------------|----------------------------------------------|--|--|--|--|

| 1      | DIN     | Digital input   | Serial data input.                           |  |  |  |  |

| 2      | SCLK    | Digital input   | Serial clock input.                          |  |  |  |  |

| 3      | NCS     | Digital input   | Chip select. This pin is active low.         |  |  |  |  |

| 4      | FS      | Digital input   | Frame synchronisation for serial input data. |  |  |  |  |

| 5      | AGND    | Supply          | Analogue ground.                             |  |  |  |  |

| 6      | REF     | Analogue I/O    | Analogue reference voltage input/output.     |  |  |  |  |

| 7      | OUT     | Analogue output | DAC analogue output                          |  |  |  |  |

| 8      | VDD     | Supply          | Positive power supply.                       |  |  |  |  |

| ABSOL  | UTE MA) |                 | NGS                                          |  |  |  |  |

# **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

| CONDITION                                   |                        | MIN          | MAX          |

|---------------------------------------------|------------------------|--------------|--------------|

| Supply voltage, VDD to AGND                 |                        |              | 7V           |

| Digital input voltage                       |                        | -0.3V        | VDD + 0.3V   |

| Reference input voltage                     |                        | -0.3V        | VDD + 0.3V   |

| Operating temperature range, T <sub>A</sub> | WM2636CD<br>WM2636ID   | 0°C<br>-40°C | 70°C<br>85°C |

| Storage temperature                         |                        | -65°C        | 150°C        |

| Lead temperature 1.6mm (1/16 inch) so       | Idering for 10 seconds |              | 260°C        |

## **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                        | SYMBOL            | TEST CONDITIONS    | MIN | TYP | MAX       | UNIT |

|----------------------------------|-------------------|--------------------|-----|-----|-----------|------|

| Supply voltage                   | VDD               |                    | 2.7 |     | 5.5       | V    |

| High-level digital input voltage | VIH               | VDD = 2.7V to 5.5V | 2   |     |           | V    |

| Low-level digital input voltage  | VIL               | VDD = 2.7V to 5.5V |     |     | 0.8       | V    |

| Reference voltage to REF         | V <sub>REF</sub>  | See Note           |     |     | VDD - 1.5 | V    |

| Load resistance                  | RL                |                    | 2   | 10  |           | kΩ   |

| Load capacitance                 | CL                |                    |     |     | 100       | pF   |

| Serial clock rate                | F <sub>SCLK</sub> |                    |     |     | 20        | MHz  |

| Operating free-air temperature   | T <sub>A</sub>    | WM2636CD           | 0   |     | 70        | °C   |

|                                  |                   | WM2636ID           | -40 |     | 85        | °C   |

Note: Reference voltages greater than VDD/2 will cause saturation for large DAC codes.

# **ELECTRICAL CHARACTERISTICS**

### **Test Conditions:**

$R_L = 10k\Omega$ ,  $C_L = 100pF$ . VDD = 5V ± 10%,  $V_{REF} = 2.048V$  and VDD = 3V ± 10%,  $V_{REF} = 1.024V$  over recommended operating free-air temperature range (unless noted otherwise).

| PARAMETER                                    | SYMBOL          | TEST CONDITIONS                                                  | MIN    | TYP      | MAX       | UNIT   |

|----------------------------------------------|-----------------|------------------------------------------------------------------|--------|----------|-----------|--------|

| Static DAC Specifications                    | J               |                                                                  |        | 1        |           | _!     |

| Resolution                                   |                 |                                                                  | 12     |          |           | bits   |

| Integral non-linearity                       | INL             | See Note 1                                                       |        | ±2.0     | ±4.0      | LSB    |

| Differential non-linearity                   | DNL             | See Note 2                                                       |        | ±0.5     | ±1.0      | LSB    |

| Zero code error                              | ZCE             | See Note 3                                                       |        |          | ±20       | mV     |

| Gain error                                   | GE              | See Note 4                                                       |        |          | ±0.6      | % FSR  |

| D.c. power supply rejection ratio            | DC PSRR         | See Note 5                                                       |        | 0.5      |           | mV/V   |

| Zero code error temperature coefficient      |                 | See Note 6                                                       |        | 10       |           | ppm/°C |

| Gain error temperature coefficient           |                 | See Note 6                                                       |        | 10       |           | ppm/°C |

| DAC Output Specifications                    | <u></u>         |                                                                  |        | <u></u>  |           |        |

| Output voltage range                         |                 |                                                                  | 0      |          | VDD - 0.1 | V      |

| Output load regulation                       |                 | 2kΩ to 10kΩ load                                                 | *      | ±0.1     | ±0.25     | %      |

|                                              |                 | See Note 7                                                       | 18- 1- | _0.1     | _0.20     |        |

| Power Supplies                               |                 | 2 3                                                              | C      | <u> </u> |           |        |

| Active supply current                        | I <sub>DD</sub> | No load, $V_{IH} = VDD$ , $V_{IL} = 0V$                          | 1      |          |           |        |

|                                              |                 | VDD = 5V,<br>V <sub>REF</sub> = 2.048 <b>V</b> Slow              |        | 1.6      | 1.9       | mA     |

|                                              |                 | VDD = 5V,<br>V <sub>REF</sub> = 2.048V Fast                      |        | 2.9      | 3.4       | mA     |

|                                              |                 | VDD = 3V,                                                        |        | 1.4      |           | mA     |

|                                              |                 | V <sub>REF</sub> = 1.024V Slow<br>VDD = 3V,                      |        | 0.7      |           |        |

|                                              |                 | VDD = 3V,<br>$V_{REF} = 1.024V$ Fast                             |        | 2.7      |           | mA     |

|                                              |                 | See Note 8                                                       |        |          |           |        |

| Power down supply current                    |                 | No load,                                                         |        | 0.01     | 10        | μA     |

|                                              |                 | all digital inputs 0V or VDD<br>See Note 9                       |        |          |           |        |

| Dynamic DAC Specifications                   | J               |                                                                  |        | J        |           | _[     |

| Slew rate                                    |                 | DAC code 128 to 4095,                                            |        |          |           |        |

|                                              |                 | 10%-90% See Note 10                                              |        |          |           |        |

|                                              |                 | Slow<br>Fast                                                     |        | 2        |           | V/µs   |

| Settling time                                |                 | DAC code 128 to 4095                                             |        | 14       |           | V/µs   |

|                                              |                 | See Note 11                                                      |        |          |           |        |

|                                              |                 | Slow                                                             |        | 3.5      |           | μs     |

|                                              |                 | Fast                                                             |        | 1.0      |           | μs     |

| Glitch energy                                |                 | Code 2047 to 2048                                                |        | 10       |           | nV-s   |

| Signal to noise ratio                        | SNR             | $fs = 400ksps, f_{OUT} = 1kHz,$<br>BW = 20kHz                    | 71     | 75       |           | dB     |

| Signal to poice and distortion acting (NIDD) |                 | See Note 12<br>fs = 400ksps, f <sub>OUT</sub> = 1kHz,            | 59     | 66       |           | dB     |

| Signal to noise and distortion ratio         | SNRD            | BW = 20kHz See Note 12                                           | - 59   |          |           |        |

| Total harmonic distortion                    | THD             | $fs = 400ksps, f_{OUT} = 1kHz,$<br>BW = 20kHz See Note 12        |        | -67      | -59       | dB     |

| Spurious free dynamic range                  | SPFDR           | fs = 400ksps, f <sub>OUT</sub> = 1kHz,<br>BW = 20kHz See Note 12 | 59     | 69       |           | dB     |

### WM2636

#### **Test Conditions:**

$R_L$  = 10k $\Omega$ ,  $C_L$  = 100pF. VDD = 5V ± 10%,  $V_{REF}$  = 2.048V and VDD = 3V ± 10%,  $V_{REF}$  = 1.024V over recommended operating free-air temperature range (unless noted otherwise).

| PARAMETER                      | SYMBOL              | TEST CONDITIONS                                                                    | MIN   | TYP        | MAX   | UNIT       |

|--------------------------------|---------------------|------------------------------------------------------------------------------------|-------|------------|-------|------------|

| Reference Configured as Input  |                     |                                                                                    | 1     | 1          | 1     | [          |

| Reference input resistance     | R <sub>REFIN</sub>  |                                                                                    |       | 10         |       | MΩ         |

| Reference input capacitance    | CREFIN              |                                                                                    |       | 55         |       | pF         |

| Reference feedthrough          |                     | V <sub>REF</sub> = 1V <sub>PP</sub> at 1kHz<br>+ 1.024V dc, DAC code 0             |       | -65        |       | dB         |

| Reference input bandwidth      |                     | V <sub>REF</sub> = 0.2V <sub>PP</sub> + 1.024V dc<br>DAC code 2048<br>Slow<br>Fast |       | 1.0<br>1.0 |       | MHz<br>MHz |

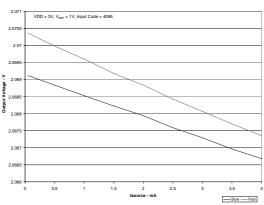

| Reference configured as output |                     |                                                                                    | 1     | 1          | 1     | [          |

| Low reference voltage          | VREFOUTL            |                                                                                    | 1.003 | 1.024      | 1.045 | V          |

| High reference voltage         | VREFOUTH            | VDD > 4.75V                                                                        | 2.027 | 2.048      | 2.069 | V          |

| Output source current          | I <sub>REFSRC</sub> |                                                                                    |       | -          | 1     | mA         |

| Output sink current            | I <sub>REFSNK</sub> |                                                                                    | -1    |            |       | mA         |

| Load Capacitance               |                     |                                                                                    | I TA  |            | 100   | pF         |

| PSRR                           |                     | 7. St                                                                              |       | -48        |       | dB         |

| Digital Inputs                 |                     | 2372                                                                               | C     |            | 1     | [          |

| High level input current       | I <sub>IH</sub>     | Input voltage = VDD                                                                |       |            | 1     | μΑ         |

| Low level input current        | l <sub>IL</sub>     | Input voltage = 0V                                                                 |       |            | -1    | μΑ         |

| Input capacitance              | CI                  |                                                                                    |       | 8          |       | pF         |

1. Integral non-linearity (INL) is the maximum deviation of the output from the line between zero and full scale (excluding the effects of zero code and full scale errors).

2. Differential non-linearity (DNL) is the difference between the measured and ideal 1LSB amplitude change of any adjacent two codes. A guarantee of monotonicity means the output voltage changes in the same direction (or remains constant) as a change in digital input code.

- 3. Zero code error is the voltage output when the DAC input code is zero.

- 4. Gain error is the deviation from the ideal full scale output excluding the effects of zero code error.

5. Power supply rejection ratio is measured by varying VDD from 4.5V to 5.5V and measuring the proportion of this signal imposed on the zero code error and the gain error.

- 6. Zero code error and Gain error temperature coefficients are normalised to full scale voltage.

- 7. Output load regulation is the difference between the output voltage at full scale with a  $10k\Omega$  load and  $2k\Omega$  load. It is expressed as a percentage of the full scale output voltage with a  $10k\Omega$  load.

- 8. Ipp is measured while continuously writing code 2048 to the DAC. For V<sub>IH</sub> < VDD 0.7V and V<sub>IL</sub> > 0.7V supply current will increase.

- 9. Typical supply current in power down mode is 10nA. Production test limits are wider for speed of test.

- 10. Slew rate results are for the lower value of the rising and falling edge slew rates

- 11. Settling time is the time taken for the signal to settle to within 0.5LSB of the final measured value for both rising and falling edges. Limits are ensured by design and characterisation, but are not production tested.

- 12. SNR, SNRD, THD and SPFDR are measured on a synthesised sinewave at frequency four generated with a sampling frequency fs.

## WM2636

## SERIAL INTERFACE

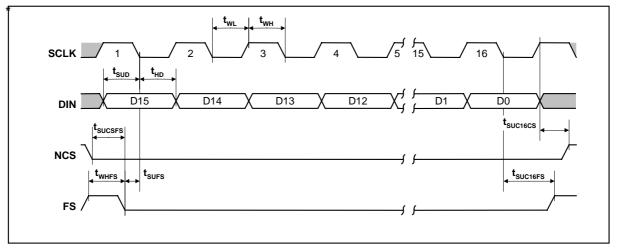

## Figure 1 Timing Diagram

### Test Conditions:

$R_L = 10k\Omega$ ,  $C_L = 100pF$ . VDD = 5V ± 10%,  $V_{REF} = 2.048V$  and VDD = 3V ± 10%,  $V_{REF} = 1.024V$  over recommended operating free-air temperature range (unless noted otherwise).

| SYMBOL                | TEST CONDITIONS                                                                                                                                                                                                                                                   | MIN TYP | MAX UNIT |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|

| tSUCSFS               | Setup time NCS low before negative FS edge.                                                                                                                                                                                                                       | 10      | ns       |

| t <sub>SUFS</sub>     | Setup time FS low before first negative SCLK edge.                                                                                                                                                                                                                | 8       | ns       |

| t <sub>SUC16FS</sub>  | Setup time, sixteenth negative edge after FS low on which D0 is sampled before rising edge of FS.                                                                                                                                                                 | 10      | ns       |

| t <sub>SUC16</sub> CS | Setup time, sixteenth positive SCLK edge (first<br>positive after D0 sampled) before NCS rising edge. If<br>FS is used instead of the sixteenth positive edge to<br>update the DAC, then the setup time is between the<br>FS rising edge and the NCS rising edge. | 10      | ns       |

| t <sub>WH</sub>       | Pulse duration, SCLK high.                                                                                                                                                                                                                                        | 25      | ns       |

| t <sub>WL</sub>       | Pulse duration, SCLK low.                                                                                                                                                                                                                                         | 25      | ns       |

| t <sub>SUD</sub>      | Setup time, data ready before SCLK falling edge.                                                                                                                                                                                                                  | 8       | ns       |

| t <sub>HD</sub>       | Hold time, data held valid after SCLK falling edge.                                                                                                                                                                                                               | 5       | ns       |

| twhes                 | Pulse duration, FS high.                                                                                                                                                                                                                                          | 20      | ns       |

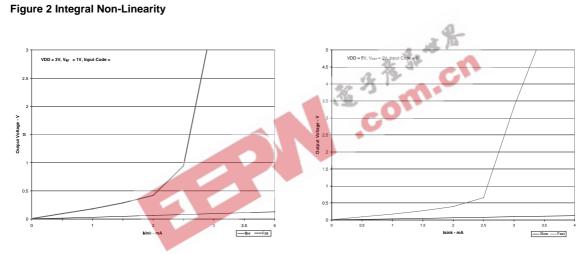

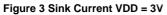

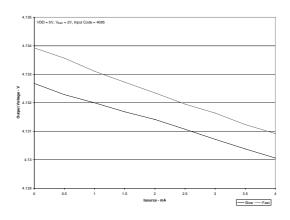

## **TYPICAL PERFORMANCE GRAPHS**

Figure 4 Sink Current VDD = 5V

Figure 5 Source Current VDD = 3V

Figure 6 Source Current VDD = 5V

## **DEVICE DESCRIPTION**

### **GENERAL FUNCTION**

The device uses a resistor string network buffered with an op amp to convert 12-bit digital data to analogue voltage levels (see Block Diagram). The output voltage is determined by the reference input voltage and the input code according to the following relationship:

Output voltage =

$$2(V_{REF}) \frac{CODE}{4096}$$

|      | INPUT |      | OUTPUT                                             |

|------|-------|------|----------------------------------------------------|

| 1111 | 1111  | 1111 | $2(V_{REF})\frac{4095}{4096}$                      |

|      | :     |      | :                                                  |

| 1000 | 0000  | 0001 | $2\left(V_{\text{REF}}\right)\frac{2049}{4096}$    |

| 1000 | 0000  | 0000 | $2\left(V_{REF}\right)\frac{2048}{4096} = V_{REF}$ |

| 0111 | 1111  | 1111 | $2(V_{REF})\frac{2047}{4096}$                      |

|      | :     |      | 38. 3                                              |

| 0000 | 0000  | 0001 | 2(VREF) 1<br>4096                                  |

| 0000 | 0000  | 0000 | ٥V                                                 |

Table 1 Binary Code Table (0V to 2V<sub>REF</sub> Output), Gain = 2

#### **POWER ON RESET**

An internal power-on-reset circuit resets the DAC register to all 0s on power-up.

### **BUFFER AMPLIFIER**

The output buffer has a near rail-to-rail output with short circuit protection and can reliably drive a  $2k\Omega$  load with a 100pF load capacitance.

## SERIAL INTERFACE

Explanation of data transfer:

First, the device has to be enabled with NCS set to low. Then, a falling edge of FS starts shifting the data bit-per-bit (starting with the MSB) to the internal register on the falling edges of SCLK. After 16 bits have been transferred or FS rises, the content of the shift register is moved to the DAC latch which updates the voltage output to the new level.

The serial interface of the device can be used in two basic modes:

- four wire (with chip select)

- three wire (without chip select)

Using chip select (four wire mode), it is possible to have more than one device connected to the serial port of the data source (DSP or microcontroller). If there is no need to have more than one device on the serial bus, then NCS can be tied low.

### SERIAL CLOCK AND UPDATE RATE

Figure 1 shows the device timing. The maximum serial rate is:

$f_{SCLK}max = \frac{1}{t_{WCH min} + t_{WCL min}} = 20MHz$

The digital update rate is limited to an 800ns period, or 1.25MHz frequency. However, the DAC settling time to 12 bits limits the update rate for large input step transitions.

#### SOFTWARE CONFIGURATION OPTIONS

The 16 bits of data can be transferred with the sequence shown in Table 2. D11-D0 contains the 12-bit data word. D15-D12 hold the programmable options.

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8    | D7      | D6       | D5      | D4    | D3     | D2  | D1 | D0 |

|-----|-----|-----|-----|-----|-----|----|-------|---------|----------|---------|-------|--------|-----|----|----|

| R1  | SPD | PWR | R0  |     |     | Ne | w DAC | c or co | ntrol re | eaister | value | (12 bi | ts) |    |    |

#### Table 2 Serial Word Format

#### **PROGRAMMABLE SETTLING TIME**

Settling time is a software selectable 3.5µs or 1µs, typical to within ±0.5LSB of final value. This is controlled by the value of D14. A ONE defines a settling time of 1µs, a ZERO defines a settling time of 3.5µs.

#### **PROGRAMMABLE POWER DOWN**

The power down function is controlled by D13. A ZERO configures the device as active, or fully powered up, a ONE configures the device into power down mode. When the power down function is released the device reverts to the DAC code set prior to power down.

#### **REGISTER ADDRESSING**

A separate internal control register is available. This is accessed from the register access bits R1 (Bit D15) and R0 (Bit D12).

| R1                             | R0        | REGISTER                       |  |  |  |  |  |  |

|--------------------------------|-----------|--------------------------------|--|--|--|--|--|--|

| (BIT D15)                      | (BIT D12) | 4 15 14                        |  |  |  |  |  |  |

| 0                              | 0         | Write data to DAC              |  |  |  |  |  |  |

| 0                              | 1         | Reserved                       |  |  |  |  |  |  |

| 1                              | 0         | Reserved                       |  |  |  |  |  |  |

| 1                              | 1         | Write data to control register |  |  |  |  |  |  |

| able 3 Register Access Control |           |                                |  |  |  |  |  |  |

The contents of the control register, shown below in Table 4, are used to program the internal reference function.

| D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1   | D0   |

|-----|-----|----|----|----|----|----|----|----|----|------|------|

| x   | x   | X  | х  | х  | х  | х  | х  | х  | Х  | REF1 | REF0 |

Table 4 Control Register Contents

#### **PROGRAMMABLE INTERNAL REFERENCE**

The reference can be sourced internally or externally under software control. If an external reference voltage is applied to the REF pin, the device must be configured to accept this.

If an external reference is selected, the reference voltage input is buffered which makes the DAC input resistance independent of code. The REF pin has an input resistance of  $10M\Omega$  and an input capacitance of typically 55pF. The reference voltage determines the DAC full-scale output.

If an internal reference is selected, a voltage of 1.024V or 2.048 is available. The internal reference can source up to 1mA and can therefore be used as an external system reference.

| REF1 | REF0) | REGISTER |

|------|-------|----------|

| 0    | 0     | External |

| 0    | 1     | 1.024V   |

| 1    | 0     | 2.048V   |

| 1    | 1     | External |

Table 5 Programmable Internal Reference

## Examples:

1. Set internal reference voltage to 2.048V

| D15                                          | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2         | D1 | D0 |

|----------------------------------------------|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|------------|----|----|

| 1                                            | х   | 0   | 1   | х   | х   | х  | х  | х  | х  | х  | х  | х  | х          | 1  | 0  |

| 2. Write new DAC value and update DAC output |     |     |     |     |     |    |    |    |    |    |    |    |            |    |    |

|                                              |     |     |     |     |     |    |    |    |    |    |    |    |            |    |    |

| DIE                                          | D14 | D12 | D10 | D11 | D10 | DO | 00 | D7 | DC | DE | D4 | D2 | <b>D</b> 2 |    | DO |

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6    | D5     | D4 | D3 | D2 | D1 | D0 |

|-----|-----|-----|-----|-----|-----|----|----|----|-------|--------|----|----|----|----|----|

| 0   | х   | 0   | 0   |     |     |    |    | N  | ew DA | C valu | ie |    |    |    |    |

## WM2636

**Production Data**

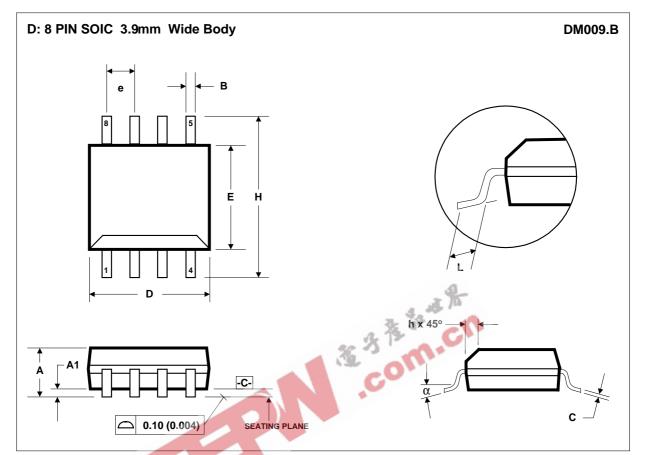

## **PACKAGE DIMENSIONS**

| Symbols               |                  | nsions<br>m) | Dimensions<br>(Inches) |        |  |  |  |

|-----------------------|------------------|--------------|------------------------|--------|--|--|--|

|                       | MIN              | MAX          | MIN                    | MAX    |  |  |  |

| Α                     | 1.35             | 1.75         | 0.0532                 | 0.0688 |  |  |  |

| <b>A</b> <sub>1</sub> | 0.10             | 0.25         | 0.0040                 | 0.0098 |  |  |  |

| В                     | 0.33             | 0.51         | 0.0130                 | 0.0200 |  |  |  |

| С                     | 0.19             | 0.25         | 0.0075                 | 0.0098 |  |  |  |

| D                     | 4.80             | 5.00         | 0.1890                 | 0.1968 |  |  |  |

| е                     | 1.27             | BSC          | 0.050 BSC              |        |  |  |  |

| E                     | 3.80             | 4.00         | 0.1497                 | 0.1574 |  |  |  |

| h                     | 0.25             | 0.50         | 0.0099                 | 0.0196 |  |  |  |

| Н                     | 5.80             | 6.20         | 0.2284                 | 0.2440 |  |  |  |

| L                     | 0.40             | 1.27         | 0.0160                 | 0.0500 |  |  |  |

| α                     | 0°               | 8°           | 0°                     | 8°     |  |  |  |

|                       | •                | •            | •                      | •      |  |  |  |

| REF:                  | JEDEC.95, MS-012 |              |                        |        |  |  |  |

NOTES: A. ALL LINEAR DIMENSIONS ARE IN MILLIMETERS (INCHES). B. THIS DRAWING IS SUBJECT TO CHANGE WITHOUT NOTICE. C. BODY DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSION, NOT TO EXCEED 0.25MM (0.010IN). D. MEETS JEDEC.95 MS-012, VARIATION = AA. REFER TO THIS SPECIFICATION FOR FURTHER DETAILS.