256 Bit X25401 16 x 16 Bit

# SPI Serial AUTOSTORE™ NOVRAM

### **FEATURES**

- 1MHz Clock Rate

- AUTOSTORE™ NOVRAM

- Automatically Performs a Store Operation

Upon Loss of V<sub>CC</sub>

- Single 5 Volt Supply

- Ideal for use with Single Chip Microcomputers

- -Minimum I/O Interface

- —SPI Mode (0,0 & 1,1) Serial Port Compatible

- -Easily Interfaced to Microcontroller Ports

- Software and Hardware Control of Nonvolatile Functions

- Auto Recall on Power-Up

- TTL and CMOS Compatible

- Low Power Dissipation

- -Active Current: 10mA

- -Standby Current: 50μA

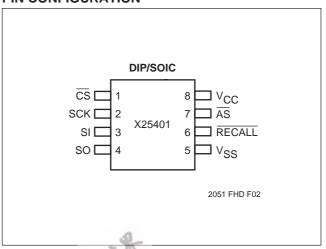

- 8-Lead PDIP and 8-Lead SOIC Packages

- High Reliability

- -Store Cycles: 1,000,000

- -Data Retention: 100 Years

# **DESCRIPTION**

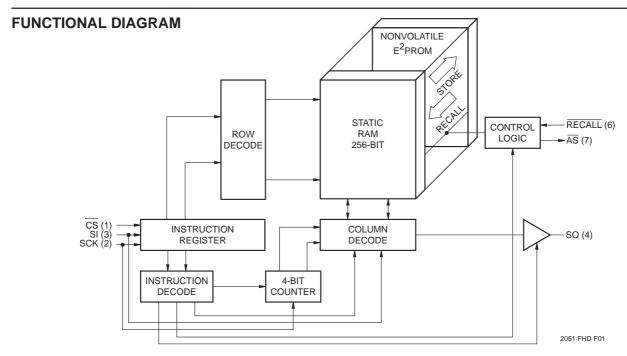

The Xicor X25401 is a serial 256 bit NOVRAM featuring a static RAM configured 16 x 16, overlaid bit-by-bit with a nonvolatile E²PROM array. The X25401 features a Serial Peripheral Interface (SPI) and software protocol allowing operation on a simple three-wire bus. The bus signals are a clock input (SCK) plus separate data in (SI) and data out (SO) lines. Access to the device is controlled through a chip select (CS) input, allowing any number of devices to share the same bus.

The Xicor NOVRAM design allows data to be transferred between the two memory arrays by means of software commands or external hardware inputs. A store operation (RAM data to E²PROM) is completed in 5ms or less and a recall operation (E²PROM data to RAM) is completed in  $2\mu s$  or less.

The X25401 also includes the AUTOSTORE feature, a user selectable feature that automatically performs a store operation when V<sub>CC</sub> falls below a preset threshold.

Xicor NOVRAMs are designed for unlimited write operations to RAM, either from the host or recalls from E<sup>2</sup>PROM and a minimum 1,000,000 store operations. Inherent data retention is specified to be greater than 100 years.

AUTOSTORE™ NOVRAM is a trademark of Xicor, Inc. COPS is a trademark of National Semiconductor Corp.

### PIN DESCRIPTIONS

# Chip Select (CS)

The Chip Select input must be LOW to enable all read/ write operations. CS must remain LOW following a Read or Write command until the data transfer is complete. CS HIGH places the X25401 in the low power standby mode and resets the instruction register. Therefore,  $\overline{\text{CS}}$  must be brought HIGH after the completion of an operation in order to reset the instruction register in preparation for the next command.

# Serial Clock (SCK)

The Serial Clock input is used to clock all data into and out of the device.

### Serial Data In (SI)

SI is the serial data input.

# Serial Data Out (SO)

SO is the serial data output. It is in the high impedance state except during data output cycles in response to a READ instruction.

# **AUTOSTORE Output (**AS)

AS is an open drain output which, when asserted indicates V<sub>CC</sub> has fallen below the AUTOSTORE threshold (V<sub>ASTH</sub>). AS may be wire-ORed with multiple open drain outputs and used as an interrupt input to a microcontroller or as an input to a low power reset circuit.

# **RECALL**

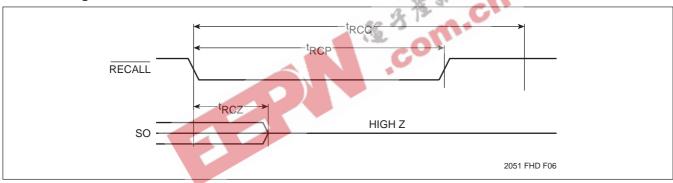

RECALL LOW will initiate an internal transfer of data from E<sup>2</sup>PROM to the RAM array.

### **PIN CONFIGURATION**

| 2_              |                  |  |  |  |

|-----------------|------------------|--|--|--|

| PIN NAMES       | No.              |  |  |  |

| Symbol          | Description      |  |  |  |

| CS              | Chip Enable      |  |  |  |

| SCK             | Serial Clock     |  |  |  |

| SI              | Serial Data In   |  |  |  |

| SO              | Serial Data Out  |  |  |  |

| RECALL          | Recall Input     |  |  |  |

| ĀS              | AUTOSTORE Output |  |  |  |

| V <sub>CC</sub> | +5V              |  |  |  |

| V <sub>SS</sub> | Ground           |  |  |  |

|                 | 2054 DOM TO      |  |  |  |

2051 PGM T01

### **DEVICE OPERATION**

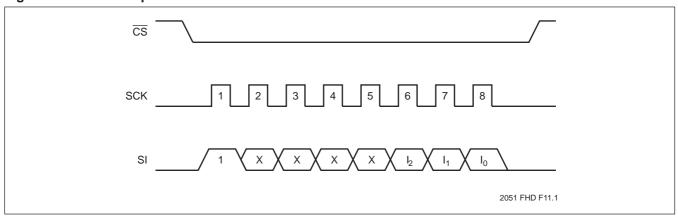

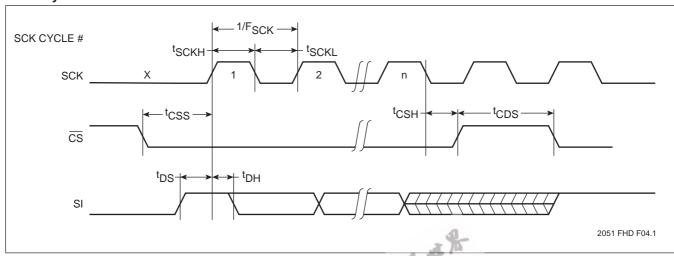

The X25401 contains an 8-bit instruction register. It is accessed via the SI input, with data being clocked in on the rising edge of SCK.  $\overline{\text{CS}}$  must be LOW during the entire data transfer operation.

Table 1 contains a list of the instructions and their operation codes. The most significant bit (MSB) of all instructions is a logic one (HIGH), bits 6 through 3 are either RAM address bits (A) or don't cares (X) and bits 2 through 0 are the operation codes. The X25401 requires the instruction to be shifted in with the MSB first.

After  $\overline{\text{CS}}$  is LOW, the X25401 will not begin to interpret the data stream until a logic "1" has been shifted in on SI. Therefore,  $\overline{\text{CS}}$  may be brought LOW with SCK running and SI LOW. SI must then go HIGH to indicate the start condition of an instruction before the X25401 will begin any action.

In addition, the SCK clock is totally static. The user can completely stop the clock and data shifting will be stopped. Restarting the clock will resume shifting of data.

# **RCL** and RECALL

Either a software RCL instruction or a LOW on the RECALL input will initiate a transfer of E<sup>2</sup>PROM data into RAM. This software or hardware recall operation sets an internal "previous recall" latch. This latch is

reset upon power-up and must be intentionally set by the user to enable any write or store operations. Although a recall operation is performed upon power-up, the previous recall latch is not set by this operation.

#### **WRDS and WREN**

Internally the X25401 contains a "write enable" latch. This latch must be set for either writes to the RAM or store operations to the E<sup>2</sup>PROM. The WREN instruction sets the latch and the WRDS instruction resets the latch, disabling both RAM writes and E<sup>2</sup>PROM stores, effectively protecting the nonvolatile data from corruption. The write enable latch is automatically reset on power-up.

### STO

The software STO instruction will initiate a transfer of data from RAM to E<sup>2</sup>PROM. In order to safeguard against unwanted store operations, the following conditions must be true:

- STO instruction issued.

- The internal "write enable" latch must be set

(WREN instruction issued).

- The "previous recall" latch must be set (either a software or hardware recall operation).

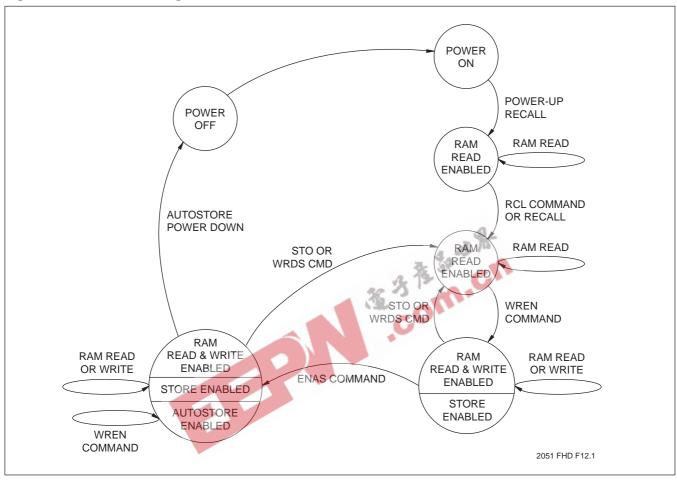

Once the store cycle is initiated, all other device functions are inhibited. Upon completion of the store cycle, the write enable latch is reset. Refer to Figure 4 for a state diagram description of enabling/disabling conditions for store operations.

**TABLE 1. INSTRUCTION SET**

| Instruction      | Format, I <sub>2</sub> I <sub>1</sub> I <sub>0</sub> | Operation                                             |  |

|------------------|------------------------------------------------------|-------------------------------------------------------|--|

| WRDS (Figure 3)  | 1XXXX000                                             | Reset Write Enable Latch (Disables Writes and Stores) |  |

| STO (Figure 3)   | 1XXXX001                                             | Store RAM Data in E <sup>2</sup> PROM                 |  |

| ENAS             | 1XXXX010                                             | Enable AUTOSTORE Feature                              |  |

| WRITE (Figure 2) | 1AAAA011                                             | Write Data into RAM Address AAAA                      |  |

| WREN (Figure 3)  | 1XXXX100                                             | Set Write Enable Latch (Enables Writes and Stores)    |  |

| RCL (Figure 3)   | 1XXXX101                                             | Recall E <sup>2</sup> PROM Data into RAM              |  |

| READ (Figure 1)  | 1AAAA11X                                             | Read Data from RAM Address AAAA                       |  |

2051 PGM T11

X = Don't Care A = Address

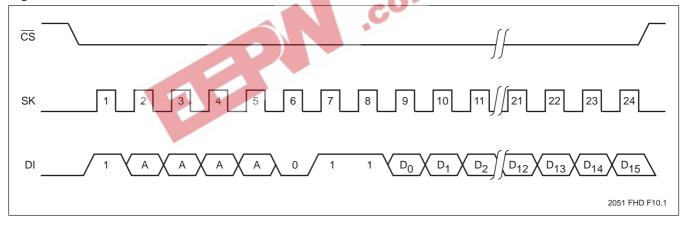

#### **WRITE**

The WRITE instruction contains the 4-bit address of the word to be written. The write instruction is immediately followed by the 16-bit word to be written.  $\overline{CS}$  must remain LOW during the entire operation.  $\overline{CS}$  must go HIGH before the next rising edge of SCK. If  $\overline{CS}$  is brought HIGH prematurely (after the instruction but before 16 bits of data are transferred), the instruction register will be reset and the data that was shifted-in will be written to RAM.

If  $\overline{\text{CS}}$  is kept LOW for more than 24 SCK clock cycles (8-bit instruction plus 16-bit data), the data already shifted-in will be overwritten.

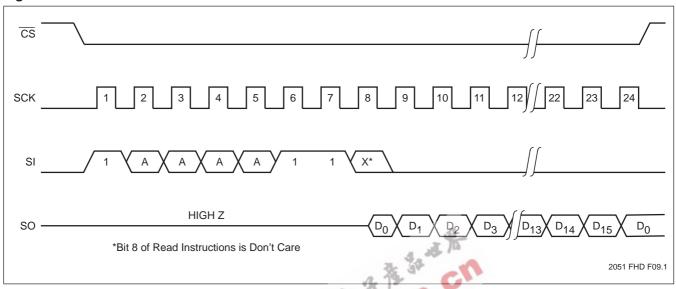

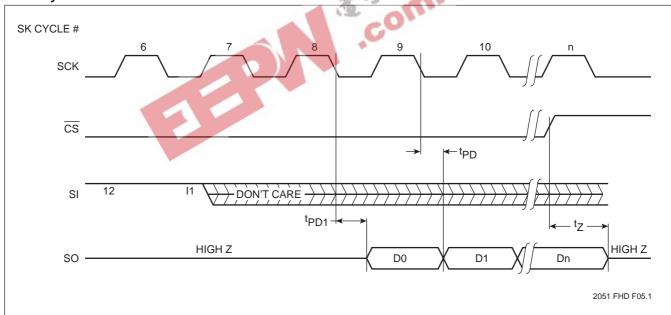

#### **READ**

The READ instruction contains the 4-bit address of the word to be accessed. Unlike the other six instructions,  $I_0$  of the instruction word is a "don't care". This provides two advantages. In a design that ties both SI and SO together, the absence of an eighth bit in the instruction allows the host time to convert an I/O line from an output to an input. Secondly, it allows for valid data output during the ninth SCK clock cycle.

All data bits are clocked by the falling edge of SCK (refer to Read Cycle Diagram).

# **LOW POWER MODE**

When  $\overline{\text{CS}}$  is HIGH, non-critical internal devices are powered-down, placing the device in the standby power mode, thereby minimizing power consumption.

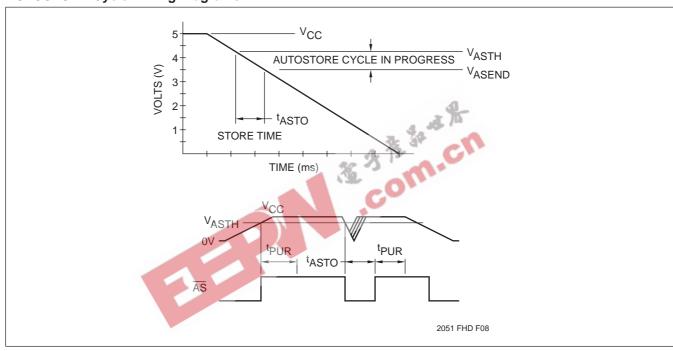

### **AUTOSTORE Feature**

The AUTOSTORE instruction (ENAS) sets the "AUTOSTORE enable" latch, allowing the X25401 to automatically perform a store operation when  $V_{CC}$  falls below the AUTOSTORE threshold ( $V_{ASTH}$ ).

# WRITE PROTECTION

The X25401 provides two software write protection mechanisms to prevent inadvertent stores of unknown data.

### **Power-Up Condition**

Upon power-up the "write enable" and "AUTOSTORE enable" latches are in the reset state, disabling any store operation.

### Unknown Data Store

The "previous recall" latch must be set after power-up. It may be set only by performing a software or hardware recall operation, which assures that data in all RAM locations is valid.

### SYSTEM CONSIDERATIONS

# Power-Up Recall

The X25401 performs a power-up recall that transfers the E²PROM contents to the RAM array. Although the data may be read from the RAM array, this recall does not set the "previous recall" latch. During this power-up recall operation, all commands are ignored. Therefore, the host should delay any operations with the X25401 a minimum of  $t_{PUR}$  after  $V_{CC}$  is stable.

Figure 1. RAM Read

Figure 2. RAM Write

Figure 3. Non-Data Operations

Figure 4. X25401 State Diagram

### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature under Bias  | . –65°C to +135°C |

|-------------------------|-------------------|

| Storage Temperature     | . –65°C to +150°C |

| Voltage on any Pin with |                   |

| Respect to VSS          | 1V to +7V         |

| D.C. Output Current     | 5mA               |

| Lead Temperature        |                   |

| (Soldering, 10 seconds) | 300°C             |

#### RECOMMENDED OPERATING CONDITIONS

| Temperature | Min.  | Max.   |

|-------------|-------|--------|

| Commercial  | 0°C   | +70°C  |

| Industrial  | −40°C | +85°C  |

| Military    | −55°C | +125°C |

2051 PGM T02.1

#### \*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Supply Voltage | Limits  |

|----------------|---------|

| X25401         | 5V ±10% |

|                |         |

2051 PGM T03.2

D.C. OPERATING CHARACTERISTICS (Over recommended operating conditions unless otherwise specified.)

|                     |                                                                | Limits |                     | 在分    | CIT                                                                             |  |

|---------------------|----------------------------------------------------------------|--------|---------------------|-------|---------------------------------------------------------------------------------|--|

| Symbol              | Parameter                                                      | Min.   | Max.                | Units | Test Conditions                                                                 |  |

| I <sub>CC1</sub>    | V <sub>CC</sub> Supply Current (TTL Inputs)                    |        | 10                  | mA    | SCK = 0.4V/2.4V Levels @ 1MHz,<br>SO = Open, All Other Inputs = V <sub>IH</sub> |  |

| I <sub>CC2</sub>    | V <sub>CC</sub> Supply Current (During AUTOSTORE)              |        | 2                   | mA    | All Inputs = $V_{IH}$ , $\overline{CS} = V_{IL}$<br>SO = Open, $V_{CC} = 4.3V$  |  |

| I <sub>SB1</sub>    | V <sub>CC</sub> Standby Current<br>(TTL Input <mark>s</mark> ) |        | 1                   | mA    | SO = Open, $\overline{CS} = V_{IL}$ ,<br>All Other Inputs = $V_{IH}$            |  |

| I <sub>SB2</sub>    | V <sub>CC</sub> Standby Current<br>(CMOS Inputs)               |        | 50                  | μΑ    | SO = Open, $\overline{CS} = V_{SS}$<br>All Other Inputs = $V_{CC} - 0.3V$       |  |

| ILI                 | Input Load Current                                             |        | 10                  | μΑ    | $V_{IN} = V_{SS}$ to $V_{CC}$                                                   |  |

| I <sub>LO</sub>     | Output Leakage Current                                         |        | 10                  | μΑ    | $V_{OUT} = V_{SS}$ to $V_{CC}$                                                  |  |

| V <sub>IL</sub> (1) | Input LOW Voltage                                              | -1     | 0.8                 | V     |                                                                                 |  |

| V <sub>IH</sub> (1) | Input HIGH Voltage                                             | 2      | V <sub>CC</sub> + 1 | V     |                                                                                 |  |

| V <sub>OL</sub>     | Output LOW Voltage                                             |        | 0.4                 | V     | $I_{OL} = 4.2 \text{mA}$                                                        |  |

| V <sub>OH</sub>     | Output HIGH Voltage                                            | 2.4    |                     | V     | $I_{OH} = -2mA$                                                                 |  |

| V <sub>OL(AS)</sub> | Output LOW Voltage (AS)                                        |        | 0.4                 | V     | $I_{OL (AS)} = 1mA$                                                             |  |

|                     | ENDURANCE AND DATA RETENTION                                   |        |                     |       |                                                                                 |  |

# **ENDURANCE AND DATA RETENTION**

ParameterMin.UnitsEndurance100,000Data Changes Per BitStore Cycles1,000,000Store CyclesData Retention100Years

2051 PGM T05

# **CAPACITANCE** $T_A = +25^{\circ}C$ , f = 1MHz, $V_{CC} = 5V$

| Symbol               | Parameter          | Max. | Units | Test Conditions       |

|----------------------|--------------------|------|-------|-----------------------|

| C <sub>OUT</sub> (2) | Output Capacitance | 8    | pF    | V <sub>OUT</sub> = 0V |

| C <sub>IN</sub> (2)  | Input Capacitance  | 6    | pF    | $V_{IN} = 0V$         |

Notes: (1)  $V_{IL}$  min. and  $V_{IH}$  max. are for reference only and are not tested.

2051 PGM T06.2

<sup>(2)</sup> This parameter is periodically sampled and not 100% tested.

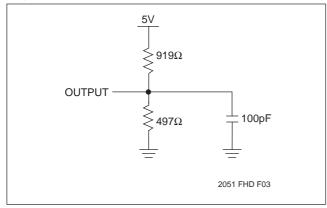

# **EQUIVALENT A.C. LOAD CIRCUIT**

# **A.C. CONDITIONS OF TEST**

| Input Pulse Levels             | 0V to 3V |

|--------------------------------|----------|

| Input Rise and Fall Times      | 10ns     |

| Input and Output Timing Levels | 1.5V     |

2051 PGM T07.1

# A.C. CHARACTERISTICS (Over the recommended operating conditions unless otherwise specified.)

# **Read and Write Cycle Limits**

| Symbol                         | Parameter                    | Min. | Max. | Units |

|--------------------------------|------------------------------|------|------|-------|

| F <sub>SK</sub> <sup>(3)</sup> | SCK Frequency                | CO   | 1    | MHz   |

| t <sub>SCKH</sub>              | SCK Positive Pulse Width     | 400  |      | ns    |

| t <sub>SCKL</sub>              | SCK Negative Pulse Width     | 400  |      | ns    |

| t <sub>DS</sub>                | Data Setup Time              | 400  |      | ns    |

| t <sub>DH</sub>                | Data Hold Time               | 80   |      | ns    |

| t <sub>PD1</sub>               | SCK to Data Bit 0 Valid      |      | 375  | ns    |

| t <sub>PD</sub>                | SCK to Data Valid            |      | 375  | ns    |

| t <sub>Z</sub>                 | Chip Select to Output High Z |      | 1    | μs    |

| t <sub>CSS</sub>               | Chip Select Setup            | 800  |      | ns    |

| t <sub>CSH</sub>               | Chip Select Hold             | 350  |      | ns    |

| t <sub>CDS</sub>               | Chip Deselect                | 800  |      | ns    |

2051 PGM T08.1

# **POWER-UP TIMING**

| Symbol               | Parameter                            | Max. | Units |

|----------------------|--------------------------------------|------|-------|

| t <sub>PUR</sub> (4) | Power-up to Read Operation           | 200  | μs    |

| t <sub>PUW</sub> (4) | Power-up to Write or Store Operation | 5    | ms    |

2051 PGM T09

Notes: (3) SCK rise and fall times must be less than 50ns.

(4) t<sub>PUR</sub> and t<sub>PUW</sub> are the delays required from the time V<sub>CC</sub> is stable until the specified operation can be initiated. These parameters are periodically sampled and not 100% tested.

# Write Cycle

# Read Cycle

# **NONVOLATILE OPERATIONS**

| Operation       | RECALL | Software<br>Instruction | Write Enable<br>Latch State | Previous<br>Recall Latch<br>State |

|-----------------|--------|-------------------------|-----------------------------|-----------------------------------|

| Hardware Recall | 0      | NOP(5)                  | X                           | X                                 |

| Software Recall | 1      | RCL                     | X                           | X                                 |

| Software Store  | 1      | STO                     | SET                         | SET                               |

2051 PGM T10

# **ARRAY RECALL LIMITS**

| Symbol           | Parameter                         | Min. | Max. | Units |

|------------------|-----------------------------------|------|------|-------|

| t <sub>RCC</sub> | Recall Cycle Time                 | 2    |      | μs    |

| t <sub>RCP</sub> | Recall Pulse Width <sup>(6)</sup> | 500  |      | ns    |

| t <sub>RCZ</sub> | Recall to Output in High Z        |      | 500  | ns    |

2051 PGM T11

# **Recall Timing**

# **SOFTWARE STORE CYCLE LIMITS**

| Symbol          | Parameter                               | Min. | Typ.(7) | Max. | Units |

|-----------------|-----------------------------------------|------|---------|------|-------|

| t <sub>ST</sub> | Store Time After Clock 8 of STO Command |      | 2       | 5    | ms    |

2051 PGM T12.1

Notes: (5) NOP designates when the X25401 is not currently executing an instruction. (6) Recall rise time must be <10 $\mu$ s. (7) Typical values are for  $T_A = 25^{\circ}$ C and nominal supply voltage.

# **AUTOSTORE Cycle Limits**

| Symbol             | Parameter                   | Min. | Max. | Units |

|--------------------|-----------------------------|------|------|-------|

| V <sub>ASTO</sub>  | AUTOSTORE Cycle Time        |      | 5    | ms    |

| V <sub>ASTH</sub>  | AUTOSTORE Threshold Voltage | 4.0  | 4.3  | V     |

| V <sub>ASEND</sub> | AUTOSTORE Cycle End Voltage | 3.5  |      | V     |

2051 PGM T13

# **AUTOSTORE Cycle Timing Diagrams**

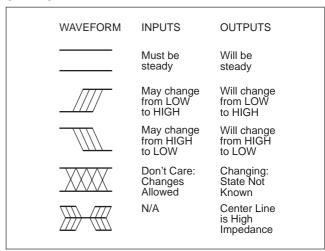

# **SYMBOL TABLE**

# **PACKAGING INFORMATION**

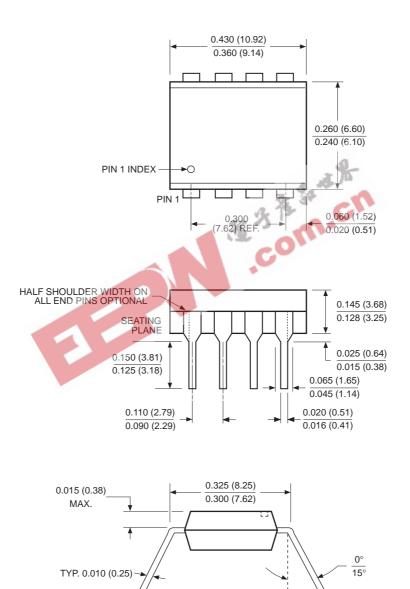

# 8-LEAD PLASTIC DUAL IN-LINE PACKAGE TYPE P

# NOTE:

- 1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

- 2. PACKAGE DIMENSIONS EXCLUDE MOLDING FLASH

3926 FHD F01

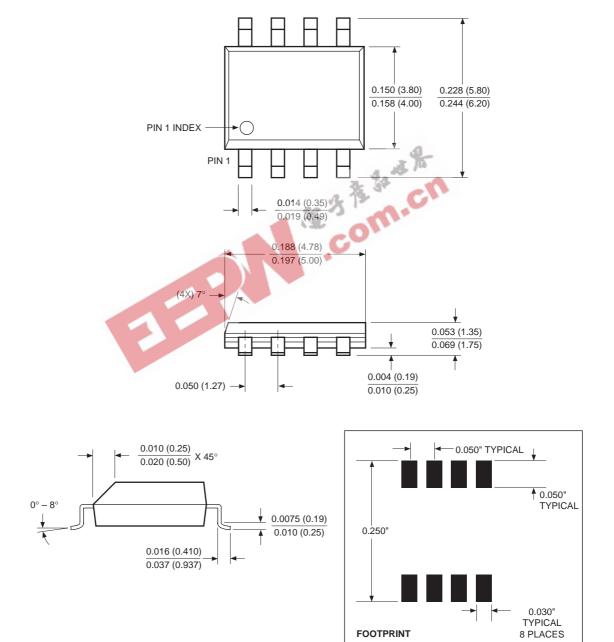

# **PACKAGING INFORMATION**

# 8-LEAD PLASTIC SMALL OUTLINE GULL WING PACKAGE TYPE S

NOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

3926 FHD F22.1

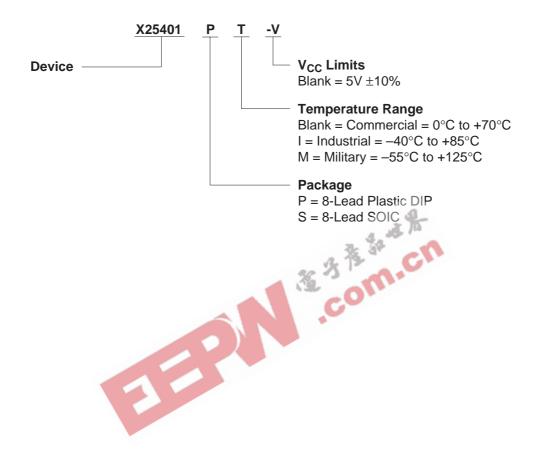

#### ORDERING INFORMATION

# LIMITED WARRANTY

Devices sold by Xicor, Inc. are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Xicor, Inc. makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Xicor, Inc. makes no warranty of merchantability or fitness tor any purpose. Xicor, Inc. reserves the right to discontinue production and change specifications and prices at any time and without notice.

Xicor, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a Xicor, Inc. product. No other circuits, patents, licenses are implied.

# **US. PATENTS**

Xicor products are covered by one or more of the following U.S. Patents: 4,263,664; 4,274,012; 4,300,212; 4,314,265; 4,326,134; 4,393,481; 4,404,475; 4,450,402; 4,486,769; 4,488,060; 4,520,461; 4,533,846; 4,599,706; 4,617,652; 4,668,932; 4,752,912; 4,829,482; 4,874,967; 4,883,976. Foreign patents and additional patents pending.

#### LIFE RELATED POLICY

In situations where semiconductor component failure may endanger life, system designers using this product should design the system with appropriate error detection and correction, redundancy and back-up features to prevent such an occurrence.

Xicor's products are not authorized for use as critical components in life support devices or systems.

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its satety or effectiveness.