# YAMAHA L 5 I

# **YSS231**

# **GE**

Graphic Equalizer

#### OUTLINE

The YSS231 is an LSI which performs filtering required by equalizers, etc. It is capable of implementing functions such as de-emphasis, sound multiplex processing, voice cancel, and equalizing.

Filtering through digital signal processing, this LSI can obtain various filtering characteristics by entering coefficient values from the microprocessor.

#### FEATURES

- Processing digital data with a sampling frequency of 32k to 48kHz.

- Two operation modes to meet the usage required.

- The center frequency, gain, and Q for the equalizer can be set at your option.

- lacktriangle High-speed multiplier, 24 bit data  $\times$  18 bit coefficient value = 30 bit data.

- The digital input/output format of 16 bits or 18 bits is selectable in stereo mode.

- Zero cross mute function which permits selection of four kinds of border value levels.

- Easy setting of commands and coefficient values by the microprocessor interface.

- Master clock of 256fs or 384fs.

- 5V or 3.3V single power supply, Si-gate CMOS process.

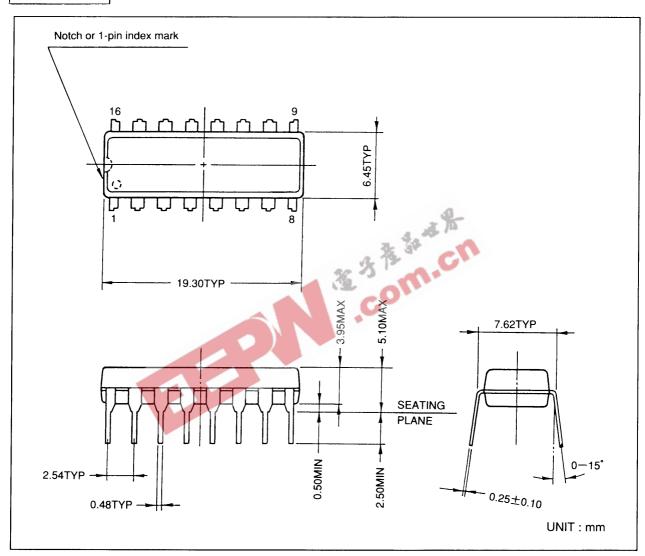

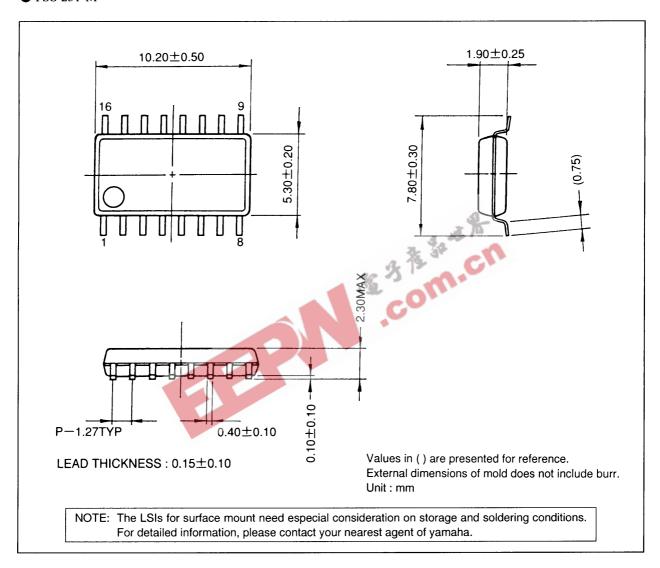

- This package is

16-pin plastic DIP (YSS231-D)

16-pin plastic SOP (YSS231-M)

20-pin plastic SSOP (YSS231-E)

YAMAHA CORPORATION

YSS231 CATALOG CATALOG No. : -LSI 4SS231A3 1995. 12

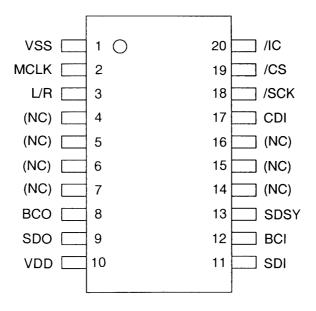

# **PIN CONFIGURATION**

<Top View Common to 16-pin DIP and 16-pin SOP>

<20pin SSOP Top View>

# **PIN FUNCTION**

| N       | 0.   |      |     |                                          |  |  |  |  |  |  |

|---------|------|------|-----|------------------------------------------|--|--|--|--|--|--|

| DIP,SOP | SSOP | Name | I/O | Function                                 |  |  |  |  |  |  |

| 1       | 1    | VSS  | -   | Ground                                   |  |  |  |  |  |  |

| 2       | 2    | MCLK | I   | Clock input                              |  |  |  |  |  |  |

| 4       | 3    | L/R  | 0   | Digital audio signal output Word clock   |  |  |  |  |  |  |

| 5       | 8    | BCO  | 0   | Digital audio signal output Bit clock    |  |  |  |  |  |  |

| 7       | 9    | SDO  | 0   | Digital audio signal output Serial clock |  |  |  |  |  |  |

| 8       | 10   | VDD  | -   | Power supply                             |  |  |  |  |  |  |

| 9       | 11   | SDI  | I   | Digital audio signal input Serial data   |  |  |  |  |  |  |

| 10      | 12   | BCI  | I   | Digital audio signal input Bit clock     |  |  |  |  |  |  |

| 12      | 13   | SDSY | I   | Digital audio signal input Word clock    |  |  |  |  |  |  |

| 13      | 17   | CDI  | I   | Microprocessor interface Serial data     |  |  |  |  |  |  |

| 14      | 18   | /SCK | I   | Microprocessor interface Serial clock    |  |  |  |  |  |  |

| 15      | 19   | /CS  | I   | Microprocessor interface Chip select     |  |  |  |  |  |  |

| 16      | 20   | /IC  | I   | Initial clear input                      |  |  |  |  |  |  |

| BLOCK   |      |      |     |                                          |  |  |  |  |  |  |

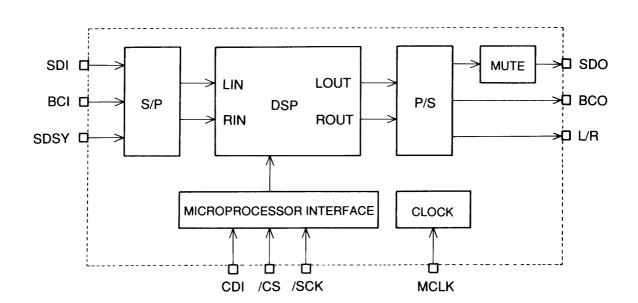

# **BLOCK DIAGRAM**

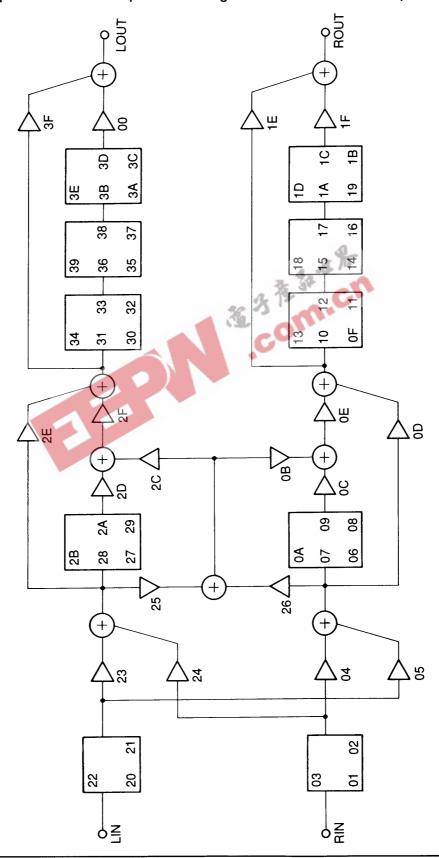

# **SIGNAL FLOW DIAGRAM**

1. Mode 1 (De-emphasis + Sound Multiplex Processing + 5-band Equalizer)

2. Mode 2 (De-emphasis + Sound Multiplex Processing + Voice Cancel + 3-band Equalizer)

#### 3. Notes on Signal Flow Diagram

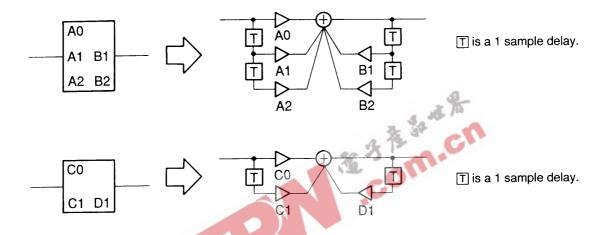

#### ● IIR Filter

In the signal flow diagram, a 2nd order IIR filter is represented as a box with five coefficient addresses, and a 1st order IIR filter as a box with three coefficient addresses.

#### IMPORTANT:

After setting the coefficients, the YSS231 quadruples the coefficient values of coefficient addresses A0 and A2 of the 2nd order IIR filter and also doubles the coefficient values of A1, B1, and B2. Therefore, the coefficients of A0 and A2 must be divided by four, and the coefficients of A1, B1, and B2 by two, before entering the coefficients from the microprocessor.

#### **IFUNCTION DESCRIPTION**

#### 1. Master clock MCLK

An external clock of 384fs or 256fs is inputted through the MCLK terminal.

After /IC raise, CLK bit of the OPR register is set "0", and master clock moves 384fs. If 256fs is used at MCLK frequency, set "1" to CLK bit of OPR register after /IC raise.

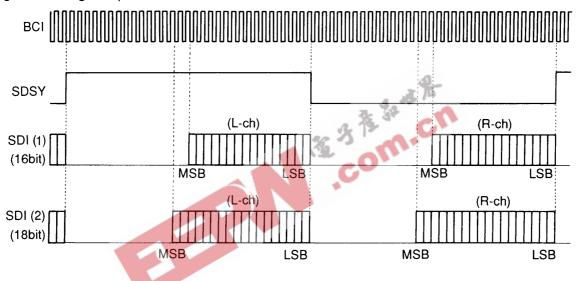

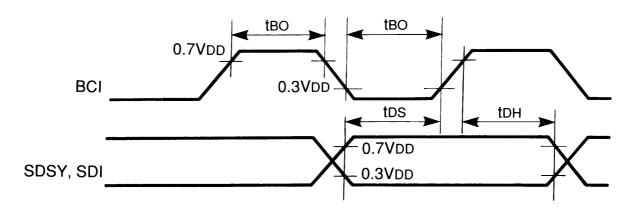

#### 2. Data input/output SDI, BCI, SDSY, SDO, BCO, L/R

Digital audio signal input format

Each format data for digital audio signal is input to the BCI, SDSY and SDI terminal.

From power on to down, input the signal of sampling frequency to the SDSY terminal.

If one cycle of SDSY is shifted 1/32fs or more to sampling frequency, internal coefficient data is destroyed. When this condition happened, set the coefficient register again.

From power on to down, input the clock frequency of decided range to the BCI terminal.

When the input data is 16 bit (OPR register, IN bit = "0"), the frequency range of the BCI is  $32fs^{\sim}192fs$ , and the when 18 bit (OPR register, IN bit "1"),  $36fs^{\sim}192fs$ .

The digital audio signal input 16 or 18 bit to the SDI terminal. Set to IN bit of OPR register by the microprocessor.

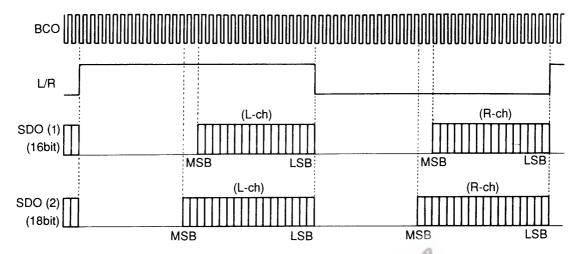

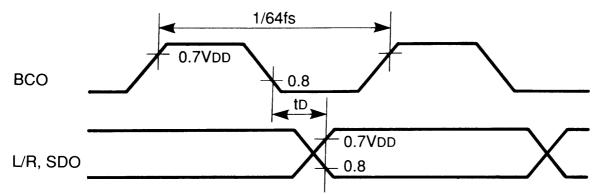

Digital audio signal output format

Each format data for digital audio signal is output from the BCO, L/R and SDO terminal.

The digital audio signal output 16 or 18 bit to the SDO terminal. Set to OUT bit of OPR register by the mocroprocessor.

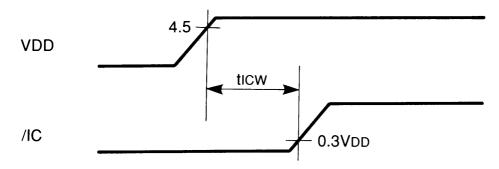

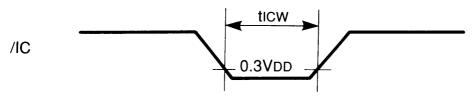

#### 3. Initial clear /IC

This LSI requires initial clear when the power is turned on.

The time taken for initial clear is at least 5/fs (fs: sampling frequency). The preservation of coefficient values is not guaranteed after initial clear.

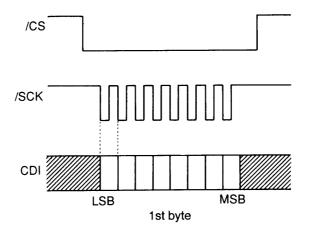

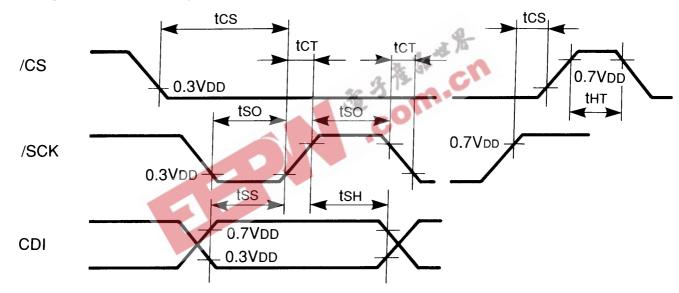

#### 4. Microprocessor interface

CDI, /SCK, /CS

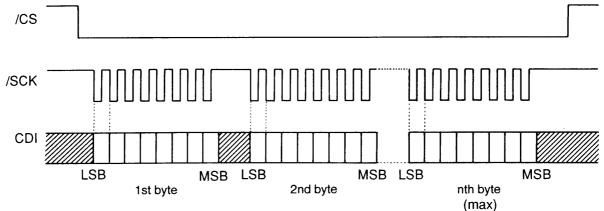

#### 4.1 Command write timing

#### 1-byte command

Note: The shaded parts are "don't care."

#### 4.2 Command map

Commands each are classified by the upper 2 bits of the first byte.

| Command  | Name | No. of bytes | Function                                                             |

|----------|------|--------------|----------------------------------------------------------------------|

| 00XXXXXX | OPR  | 1            | Operation control register                                           |

| 01XXXXXX | TEST | 1            | Test register (Do not write usually)                                 |

| 10XXXXXX | MUTE | 1            | Mute control register                                                |

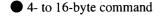

| 11XXXXXX | ADRS | 4~16         | Write the coefficient values of each filter, etc. by 4 to 16 bytes.* |

<sup>\*</sup>Note: Up to five coefficient values can be transferred at a time.

#### 4.3 Explanation of commands

#### (a) OPR (Operation control register)

| MSB | В6 | B5   | B4   | В3   | B2  | B1 | LSB |

|-----|----|------|------|------|-----|----|-----|

| 0   | 0  | TEST | MUTE | PROG | OUT | IN | CLK |

Note: B5 to LSB are set to "0" at initial clear.

● TEST: For LSI test

Usually set to "0".

MUTE: Mute setting

0 = Mute ON

1 = Mute OFF

● PROG: Selection of operation mode

0 = Mode 1

1 = Mode 2

OUT: Selection of output bit

0 = 16 bits

1 = 18 bits

IN: Selection of input bit

0 = 16 bits

1 = 18 bits

• CLK: Selection of master clock

0 = 384 fs

1 = 256 fs

#### (b) MUTE (Mute control register)

| MSB                                              | В6       | B5          | B4   | В3 | B2 | B1   | LSB        |   |  |  |  |

|--------------------------------------------------|----------|-------------|------|----|----|------|------------|---|--|--|--|

| 1                                                | 0        | LVL2        | LVL1 | D3 | D2 | D1 🦥 | <b>D</b> 0 | 4 |  |  |  |

| Note: B5 to LSB are set to "0" at initial clear. |          |             |      |    |    |      |            |   |  |  |  |

| ● LVL2,                                          | LVL1: Mu | te border v | alue |    | N  | .C   |            |   |  |  |  |

#### ● LVL2, LVL1: Mute border value

Muting takes place when the audio data drops below each border value.

Muting is performed independently for each of L and R.

| B5   | B4   | Border |

|------|------|--------|

| LVL2 | LVL1 | value  |

| 0    | 0    | -30dB  |

| 0    | 1    | -36dB  |

| 1    | 0    | -42dB  |

| 1    | 1    | -48dB  |

#### • D3, D2, D1, D0: Maximum time taken before muting

Muting is performed forcibly if the audio data does not drop below the border value programmed by LVL2 or LVL1 even if the mute function is turned ON.

Mute time = (D3 \* 8 + D2 \* 4 + D1 \* 2 + D0) \* 2048 \* (sampling cycle)

Muting takes place immediately when D3 = D2 = D1 = D0 = 0.

#### (c) ADRS

Maximum 5 coefficient values can be transferred at one time. When 2 or more coefficient values is transferred at one time, the coefficient values should be transferred from the lower address.

When transferring n (1 to 5) coefficient value(s) at a time, (3 \* n + 1) bytes should be transferred with the first byte at the top, as shown below.

| MSB | В6 | B5 | B4 | В3 | B2 | B1 | LSB |

|-----|----|----|----|----|----|----|-----|

| 1   | 1  | 0  | 0  | 0  | 0  | 0  | 0   |

1st byte

| MSB | В6 | B5 | B4 | В3 | B2 | B1   | LSB |

|-----|----|----|----|----|----|------|-----|

| D1  | D0 | A5 | A4 | A3 | A2 | A1 🦸 | A0  |

2nd byte (5th byte) (8th byte) (11th byte) (14th byte)

|   | MSB | В6 | B5 | B4 | В3 | <b>B</b> 2 | B1 | LSB |

|---|-----|----|----|----|----|------------|----|-----|

| į | D9  | D8 | D7 | D6 | D5 | D4         | D3 | D2  |

3rd byte (6th byte) (9th byte) (12th byte) (15th byte)

| MSB | В6  | B5  | B4  | В3  | B2  | B1  | LSB |

|-----|-----|-----|-----|-----|-----|-----|-----|

| D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 |

4th byte (7th byte) (10th byte) (13th byte) (16th byte)

#### $\bullet$ A5 $\sim$ A0 : Coefficient address

The coefficient address is set by the lower 6 bits of (3n-1)th byte.

The filter for equalizing consists of the 2nd order IIR filter. And it is necessary to set 5 coefficient values for one filter. The filter for de-emphasis consists of the 1st order IIR filter. And it is necessary to set 3 coefficient values for one filter.

#### ● D17~D0: Coefficient value

The coefficient value is set from D17 to D0 formed by 18 bits and 2's complement. D17 is the sign bit.

Coefficient value =

$$(-1) \times D17 + \sum_{n=0}^{16} Dn \times 2^{n-17}$$

# **ELECTRICAL CHARACTERISTICS**

#### 1. Absolute Maximum Ratings

| Parameter             | Symbol          | Rating       | Unit         |

|-----------------------|-----------------|--------------|--------------|

| Power supply voltage  | V <sub>DD</sub> | -0.3~7.0     | V            |

| Input voltage         | Vı              | -0.3~VDD+0.3 | V            |

| Operating temperature | Тор             | -40~85       | $\mathbb{C}$ |

| Storage temperature   | Tstg            | -50~125      | C            |

#### 2. Recommended Operating Conditions

|    | Parameter             |  | Symbol            | Min. | Тур.   | Max.   | Unit         |  |  |

|----|-----------------------|--|-------------------|------|--------|--------|--------------|--|--|

| r  | Power supply voltage  |  | $V_{\mathrm{DD}}$ | 3.0  | 5.0    | 5.5    | V            |  |  |

|    | Operating temperature |  | Тор               | 0    | 25     | 70     | $\mathbb{C}$ |  |  |

| DC | OC Characteristics    |  |                   |      |        |        |              |  |  |

|    | Parameter             |  | Symbol            | Conc | lition | Min.   | Тур.         |  |  |

| Γ  | Input voltage H level |  | Vih               |      |        | 0.7Vdd |              |  |  |

|    |                       |  |                   |      |        |        |              |  |  |

#### 3. DC Characteristics

| Parameter              | Symbol | Condition             | Min.   | Тур. | Max.   | Unit |

|------------------------|--------|-----------------------|--------|------|--------|------|

| Input voltage H level  | Vih    |                       | 0.7Vdd |      |        | V    |

| Input voltage L level  | Vil    |                       |        |      | 0.3Vdd | V    |

| Output voltage H level | Vон    | Iон=0.25mA            | 0.8VDD |      |        | V    |

| Output voltage L level | Vol    | IoL=1.0mA             |        |      | 0.4    | V    |

| Input leakage current  | Ili    |                       | -10    |      | 10     | μΑ   |

| Power dissipation      | <br>PD | V <sub>DD</sub> =5.0V |        | 20   | 70     | mW   |

|                        |        | $V_{DD}=3.3V$         |        | 10   | 30     |      |

#### 4. AC Characteristics

|                      | Parameter           | Symbol             | Min.     | Тур.        | Max.   | Unit |

|----------------------|---------------------|--------------------|----------|-------------|--------|------|

| MCLK                 | Input frequency     | fc1 (*1)           | 8.0      |             | 12.5   | MHz  |

|                      |                     | fc2 (*2)           | 12.0     |             | 18.5   | MHz  |

|                      | Duty                | Rc                 | 40       | 50          | 60     | %    |

| BCI                  | ON/OFF time         | tво                | 40       |             |        | ns   |

| SDSY, SDI Setup time |                     | tos                | 20       |             |        | ns   |

|                      | Hold time           | tdh                | 20       |             |        | ns   |

| L/R, SD0             | Acess time          | tD                 | -40      |             | 40     | ns   |

| /CS                  | Setup time (1)      | tcs1 (*3)          | 1/100fs  |             |        | s    |

|                      | Setup time (2)      | tcs2 (*4)          | 1/65fs   |             |        | s    |

|                      | H level time        | tнт                | 131/64fs |             |        | s    |

| /SCK                 | ON/OFF time (1)     | tso1 ( <b>*</b> 3) | 1/50fs   |             | - %-   | s    |

|                      | ON/OFF time (2)     | tso2 (*4)          | 1/32fs   | 2. 4.2      |        | s    |

|                      | Transition time (1) | tct1 ( <b>*</b> 3) |          | 5<br>表<br>S | 1/64fs | s    |

|                      | Transition time (2) | tct2 (*4)          | 36       | 3. 30       | 1/42fs | s    |

| CDI                  | Setup time (1)      | tss1 ( <b>*</b> 3) | 1/100fs  | "O,,        |        | s    |

|                      | Setup time (2)      | tss2 (*4)          | 1/65fs   |             |        | s    |

|                      | Hold time (1)       | tsнı ( <b>*</b> 3) | 1/100fs  |             |        | s    |

|                      | Hold time (2)       | tsH2 (*4)          | 1/65fs   |             |        | s    |

| /IC                  | Pulse width         | ticw               | 5/fs     |             |        | s    |

- (\*1) While master clock is 256fs.

- (\*2) While master clock is 384fs.

- (\*3) Nomally operation.

- (\*4) The characteristics while the "1" is set to LSB in OPR register on the master clock 256fs operation.

#### Audio data input timing

## Audio data output timing

#### Microprocessor interface timing

# • Initial clear timing (At power on)

## • Initial clear timing (normally)

# **EXTERNAL DIMENSIONS**

#### **EXTERNAL DIMENSIONS**

#### ●YSS 231-M

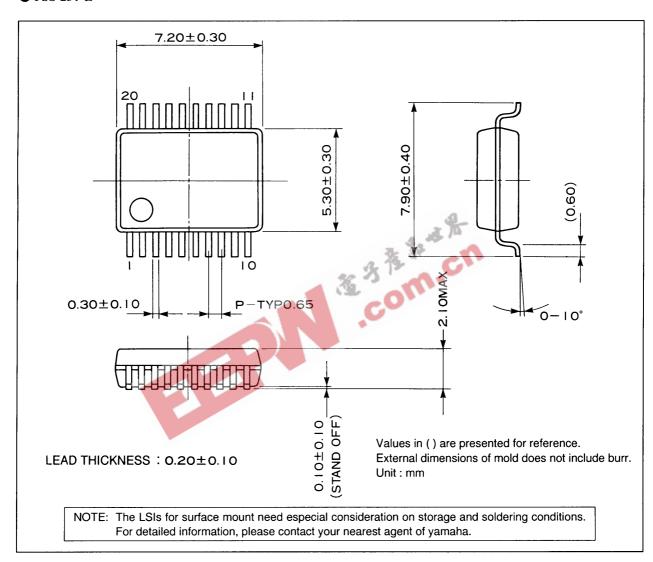

# **EXTERNAL DIMENSIONS**

#### ●YSS 231-E

# **IMPORTANT NOTICE**

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANYTHIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

The specifications of this product are subject to improvement changes without prior notice.

# ----AGENCY

# YAMAHA CORPORATION

Address inquiries to:

Semiconductor Sales & Marketing Department

■ Head Office 203, Matsunokijima, Toyooka-mura,

Iwata-gun, Shizuoka-ken, 438-0192 Tel. +81-539-62-4918 Fax. +81-539-62-5054

■ Tokyo Office 2-17-11, Takanawa, Minato-ku,

Tokyo, 108-8568

Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

■ Osaka Office Namba Tsujimoto Nissei Bldg. 4F

1-13-17, Namba Naka, Naniwa-ku, Osaka City, Osaka, 556-0011

Tel. +81-6-6633-3690 Fax. +81-6-6633-3691

■ U.S.A. Office YAMAHA Systems Technology 100 Century Center Court, San Jose,

CA 95112

Tel. +1-408-467-2300 Fax. +1-408-437-8791