CUSTOMER PROCUREMENT SPECIFICATION

### Z86C83/C84 Z8<sup>®</sup> MCU MICROCONTROLLERS

### **FEATURES**

| Device                  | ROM<br>(KB) | RAM*<br>(Bytes) | I/O<br>Lines | Voltage<br>Range |  |  |  |  |

|-------------------------|-------------|-----------------|--------------|------------------|--|--|--|--|

| Z86C83                  | 4           | 237             | 21           | 3.0V to 5.5V     |  |  |  |  |

| Z86C84                  | 4           | 237             | 17           | 3.0V to 5.5V     |  |  |  |  |

| Note: * General-Purpose |             |                 |              |                  |  |  |  |  |

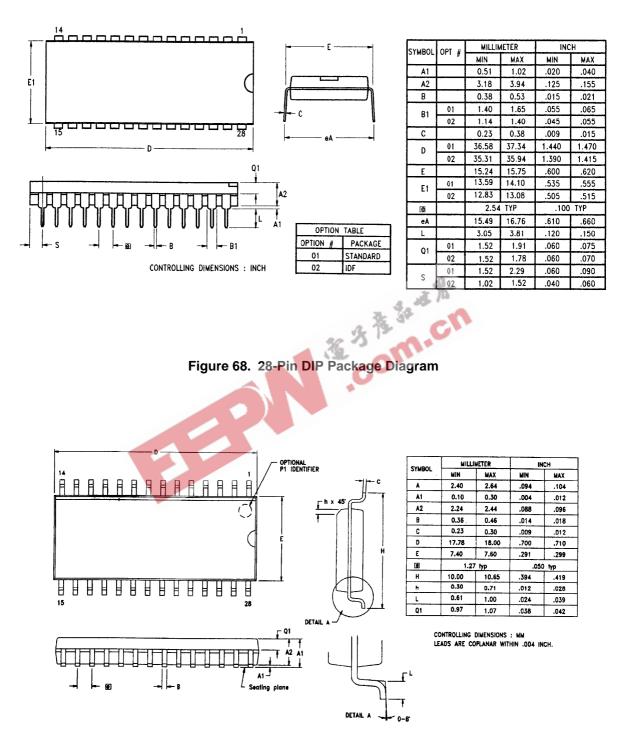

- 28-Pin DIP, SOIC, and PLCC Packages

- Clock Speed: 16 MHz

- Three Expanded Register Groups

- 8-Channel, 8-Bit A/D Converter with Track and Hold, and Unique R-Ladder A<sub>GND</sub> Offset Control

- Z86C84 has two 8-Bit D/A Converters with Programmable Gain Stages, 3 µs Settling Time

### **GENERAL DESCRIPTION**

The Z86C83/C84 Consumer Controller Processors  $(CCP^{T})$  are full-featured members of the CMOS Z8 microcontroller family offering a unique register-to-register architecture that avoids accumulator bottlenecks for higher code efficiency than RISC processors.

The Z86C83/C84 are designed to be used in a wide variety of embedded control applications, such as appliances, process controls, keyboards, security systems, battery chargers, and automotive modules.

For applications requiring powerful I/O capabilities, the Z86C83/C84 devices can have up to 21/17 (C83/C84 respectively) pins dedicated to input and output. These lines are grouped into three ports, and are configured by software to provide digital/analog I/O timing and status signals.

An on-chip, half-flash 8-bit  $\pm$ 1/2 Least Significant Bit (LSB) A/D converter can multiplex up to eight analog inputs.

- Six Vectored, Prioritized Interrupts from Six Different Sources

- Two Analog Comparator Inputs with Programmable Interrupt Polarity

- Two Programmable 8-Bit Timers, each with a 6-Bit Programmable Prescaler

- Auto Latch Mask Option for P00, P01, and P02

- Power-On Reset (POR) Timer

- Permanent Watch-Dog Timer (WDT) Mask Option

- Software-Programmable Pull-Up Resistors

- On-Chip Oscillator for Crystal, Resonator or LC

Unused analog inputs revert to standard digital I/O use. Unique, programmable  $A_{GND}$  offset control of the A/D resistor ladder compresses the converter's dynamic range for maximum effective 9-bit A/D resolution.

The Z86C84 has two 8-bit  $\pm$ 1/2 LSB D/A converters. High and low reference voltages provide precise control of the output voltage range. Programmable gain for each D/A converter provides a maximum effective 10-bit resolution for many tasks.

On-chip 8-bit counter/timers with many user-selectable modes simplify real-time tasks, such as counting, timing, and generation of PWM signals.

The designer can prioritize six different maskable, vectored, internal or external interrupts for efficient interrupt handling and multitasking functions.

### **GENERAL DESCRIPTION** (Continued)

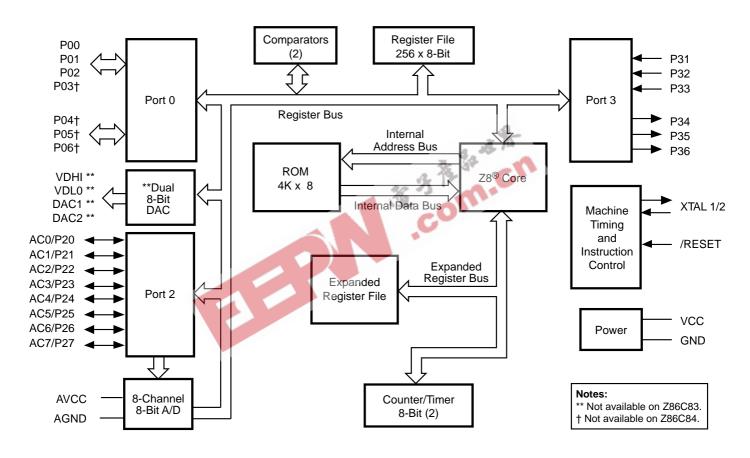

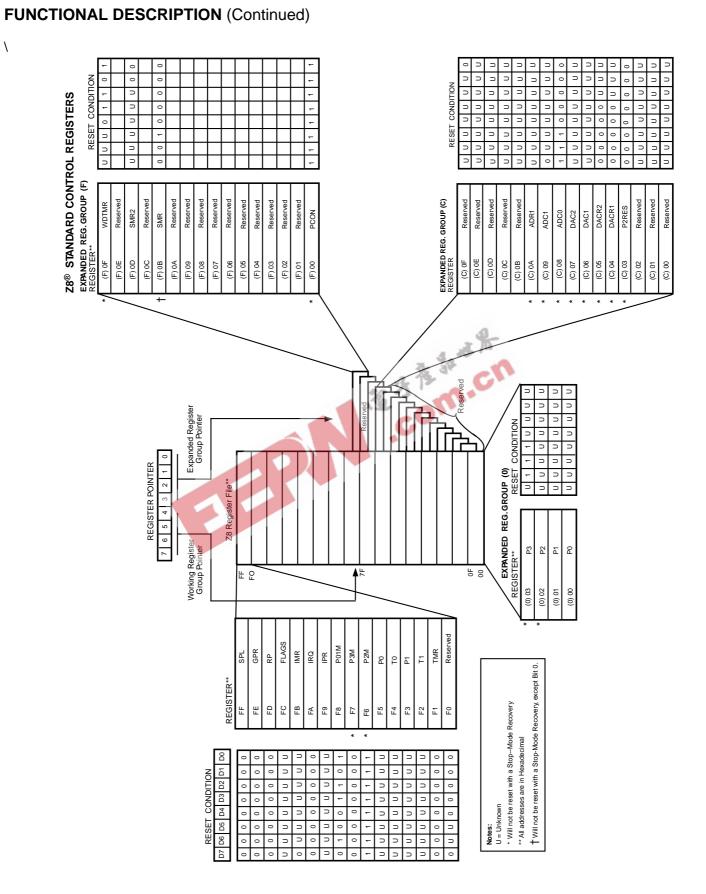

By means of an expanded register file, the designer has access to additional control registers for configuring peripheral functions including the A/D and D/A converters, counter/timers, and I/O port functions (Figure 1).

**Notes:** All Signals with a preceding front slash, "/", are active Low, e.g., B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>cc</sub> | V <sub>cc</sub> |

| Ground     | GND             | V <sub>ss</sub> |

Figure 1. Z86C83/C84 Functional Block Diagram

### <u> Asire</u>

### **PIN DESCRIPTION**

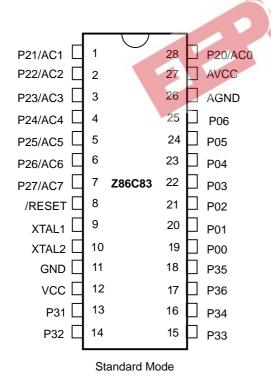

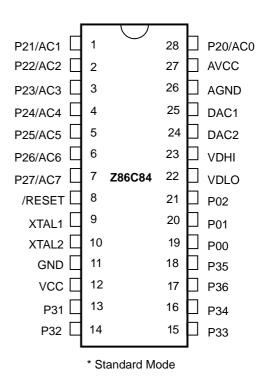

#### Table 1. Z86C83 28-Pin DIP, SOIC Pin Identification\*

| No    | Symbol          | Function         | Direction    |

|-------|-----------------|------------------|--------------|

| 1-7   | P21-P27         | Port 2, Bit 1-7  | Input/Output |

|       | or AC1-AC7      | Analog In 1-7    |              |

| 8     | /RESET          | Reset            | Input        |

| 9     | XTAL1           | Oscillator Clock | Input        |

| 10    | XTAL2           | Oscillator Clock | Output       |

| 11    | GND             | Ground           |              |

| 12    | V <sub>cc</sub> | Power            |              |

| 13-15 | P31-P33         | Port 3, Bits 1-3 | Input        |

| 16    | P34             | Port 3, Bit 4    | Output       |

| 17    | P36             | Port 3, Bit 6    | Output       |

| 18    | P35             | Port 3, Bit 5    | Output       |

| 19-25 | P0-P06          | Port 0, Bits 0-6 | Input/Output |

| 26    | $A_{GND}$       | Analog Ground    |              |

| 27    | $AV_{cc}$       | Analog Power     |              |

| 28    | P20             | Port 2, Bit 0    | Input/Output |

|       | or AC0          | Analog In 0      | -            |

| No    | Symbol           | Function            | Direction    |

|-------|------------------|---------------------|--------------|

| 1-7   | P21-P27          | Port 2, Bit 1-7     | Input/Output |

|       | or AC1-AC7       | Analog In 1-7       |              |

| 8     | /RESET           | Reset               | Input        |

| 9     | XTAL1            | Oscillator Clock    | Input        |

| 10    | XTAL2            | Oscillator Clock    | Output       |

| 11    | GND              | Ground              |              |

| 12    | V <sub>cc</sub>  | Power               |              |

| 13-15 | P31-P33          | Port 3, Bits 1-3    | Input        |

| 16    | P34              | Port 3, Bit 4       | Output       |

| 17    | P36              | Port 3, Bit 6       | Output       |

| 18    | P35              | Port 3, Bit 5       | Output       |

| 19-21 | P0-P02           | Port 0, Bits 0-3    | Input/Output |

| 22    | VDLO             | D/A Ref. Volt.,Low  | Input        |

| 23    | VDHI             | D/A Ref. Volt.,High | Input        |

| 24-25 | DAC2-1 🔬         | D/A Converter       | Output       |

| 26    | A <sub>GND</sub> | Analog Ground       |              |

| 27    | AV <sub>cc</sub> | Analog Power        |              |

| 28    | P20              | Port 2, Bit 0       | Input/Output |

| 32    | or AC0           | Analog In 0         |              |

#### Table 2. Z86C84 28-Pin DIP, SOIC Pin Identification\*

Note:

\* DIP and SOIC Pin Description and Configuration are identical.

### Note:

\* DIP and SOIC Pin Description and Configuration are identical

### Figure 3. Z86C84 28-Pin DIP and SOIC Pin Configuration\*

### **PIN DESCRIPTION** (Continued)

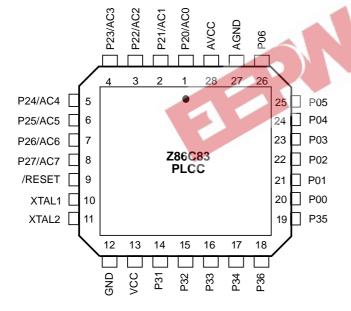

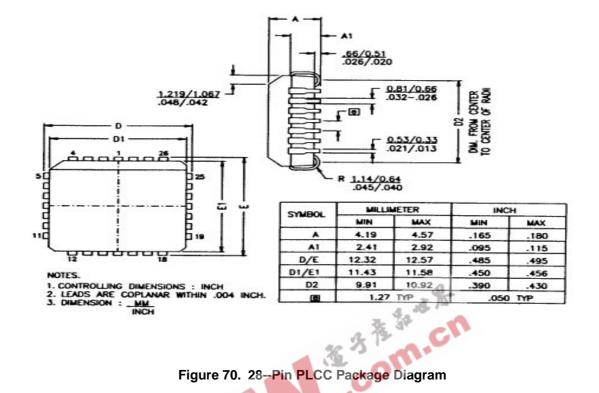

### Table 3. Z86C83 28-Pin PLCC Pin Identification

| No    | Symbol           | Function         | Direction    |

|-------|------------------|------------------|--------------|

| 1-8   | P20-P27          | Port 2, Bit 0-7  | Input/Output |

|       | or AC0-AC7       | Analog In 0-7    |              |

| 9     | /RESET           | Reset            | Input        |

| 10    | XTAL1            | Oscillator Clock | Input        |

| 11    | XTAL2            | Oscillator Clock | Output       |

| 12    | GND              | Ground           |              |

| 13    | V <sub>cc</sub>  | Power            |              |

| 14-16 | P31-P33          | Port 3, Bits 1-3 | Input        |

| 17    | P34              | Port 3, Bit 4    | Output       |

| 18    | P36              | Port 3, Bit 6    | Output       |

| 19    | P35              | Port 3, Bit 5    | Output       |

| 20-26 | P00-P06          | Port 0, Bits 0-6 | Input/Output |

| 27    | $A_{GND}$        | Analog Ground    |              |

| 28    | AV <sub>cc</sub> | Analog Power     |              |

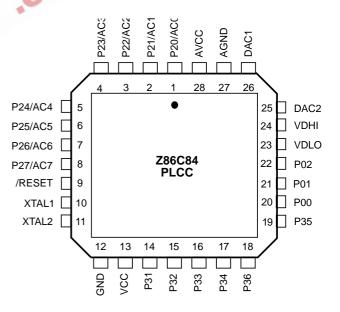

| No    | Symbol           | Function            | Direction    |

|-------|------------------|---------------------|--------------|

| 1-8   | P20-P27          | Port 2, Bit 0-7     | Input/Output |

|       | or AC0-AC7       | Analog In 0-7       |              |

| 9     | /RESET           | Reset               | Input        |

| 10    | XTAL1            | Oscillator Clock    | Input        |

| 11    | XTAL2            | Oscillator Clock    | Output       |

| 12    | GND              | Ground              |              |

| 13    | V <sub>cc</sub>  | Power               |              |

| 14-16 | P31-P33          | Port 3, Bits 1-3    | Input        |

| 17    | P34              | Port 3, Bit 4       | Output       |

| 18    | P36              | Port 3, Bit 6       | Output       |

| 19    | P35              | Port 3, Bit 5       | Output       |

| 20-22 | P00-P02          | Port 0, Bits 0-3    | Input/Output |

| 23    | VDLO             | D/A Ref. Volt,Low   | Input        |

| 24    | VDHI             | D/A Ref. Volt.,High | Input/Output |

| 25-26 | DAC2-DAC1        | D/A Converter       | Output       |

| 27    | A <sub>GND</sub> | Analog Ground       |              |

| 28 🦽  | AV <sub>cc</sub> | Analog Power        |              |

| 32.7  | m                |                     |              |

Figure 5. Z86C84 28-Pin PLCC Pin Configuration

### Table 4. Z86C84 28-Pin PLCC Pin Identification

& Silæ

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                                       | Min  | Max                | Units |

|-----------------------------------------------------------------|------|--------------------|-------|

| Ambient Temperature under Bias                                  | -40  | +105               | С     |

| Storage Temperature                                             | -65  | +150               | С     |

| Voltage on any Pin with Respect to V <sub>ss</sub> [Note 1]     | -0.6 | +7                 | V     |

| Voltage on $V_{cc}$ Pin with Respect to $V_{ss}$                | -0.3 | +7                 | V     |

| Voltage on /RESET Pins with Respect to V <sub>ss</sub> [Note 2] | -0.6 | V <sub>cc</sub> +1 | V     |

| Total Power Dissipation                                         |      | 770                | mW    |

| Maximum Current out of V <sub>ss</sub>                          |      | 140                | mA    |

| Maximum Current into V <sub>cc</sub>                            |      | 125                | mA    |

| Maximum Current into an Input Pin [Note 3]                      | -600 | +600               | μΑ    |

| Maximum Current into an Open-Drain Pin [Note 4]                 | -600 | +600               | μΑ    |

| Maximum Output Current Sinked by Any I/O Pin                    |      | 25                 | mA    |

| Maximum Output Current Sourced by Any I/O Pin                   |      | 25                 | mA    |

#### Notes:

1. This applies to all pins except XTAL and /RESET pins and where otherwise noted. A SA A R

- 2. There is no input protection diode from pin to  $V_{cc}$ .

- 3. This excludes XTAL pins.

- 4. Device pin is not at an output Low state.

#### Notice:

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period may affect device reliability.

### STANDARD TEST CONDITIONS

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to Ground. Positive current flows into the referenced pin (Figure 6).

Total power dissipation should not exceed 770 mW for the package. Power dissipation is calculated as follows:

Total Power Dissipation =

From Output

Under Test O

$V_{

m cc}~{

m x}$  [ I $_{

m cc}$  – (sum of I $_{

m OH}$ ) ] + sum of [  $(V_{cc} - V_{OH}) \times I_{OH}$ ] + sum of  $(V_{0L} \times I_{0L})$

150 pF

) I

### **V**<sub>DD</sub> SPECIFICATION

$V_{DD} = 3.0V$  to 5.5V

### ⊗ ZiLŒ

### CAPACITANCE

$T_{A} = 25^{\circ}C$ ,  $V_{cc} = GND = 0V$ , f = 1.0 MHz, unmeasured pins returned to GND.

| Parameter          | Min | Max   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 20 pF |

| Output capacitance | 0   | 20pF  |

| I/O capacitance    | 0   | 20 pF |

### DC ELECTRICAL CHARACTERISTICS

|                  |                             | V <sub>cc</sub> | T <sub>A</sub> =<br>to +7 |                      | T <sub>▲</sub> =<br>to +1 |                      | Typical<br>[13] |       |                                             |       |

|------------------|-----------------------------|-----------------|---------------------------|----------------------|---------------------------|----------------------|-----------------|-------|---------------------------------------------|-------|

| Sym              | Parameter                   | Note 3          | Min                       | Max                  | Min                       | Max                  |                 | Units | Conditions                                  | Notes |

| V <sub>CH</sub>  | Clock Input High<br>Voltage | 3.0V            | $0.7  V_{cc}$             | V <sub>cc</sub> +0.3 | $0.7  \mathrm{V_{cc}}$    | V <sub>cc</sub> +0.3 | 1.3             | V     | Driven by External Clock<br>Generator       |       |

|                  |                             | 5.5V            | $0.7  \mathrm{V_{cc}}$    | V <sub>cc</sub> +0.3 | $0.7  \mathrm{V_{cc}}$    | V <sub>cc</sub> +0.3 | 2.5             | V     | Driven by External Clock<br>Generator       |       |

| V <sub>cl</sub>  | Clock Input Low<br>Voltage  | 3.0V            | GND-0.3                   | $0.2V_{cc}$          | GND-0.3                   | $0.2  V_{cc}$        | 0.7             | V     | Driven by External Clock<br>Generator       |       |

|                  |                             | 5.5V            | GND-0.3                   | $0.2V_{cc}$          | GND-0.3                   | $0.2\mathrm{V_{cc}}$ | 1.5             | V     | Driven by External Clock<br>Generator       |       |

| V <sub>IH</sub>  | Input High Voltage          | 3.0V            | $0.7  V_{cc}$             | V <sub>cc</sub> +0.3 | $0.7  V_{cc}$             | V <sub>cc</sub> +0.3 | 1.3             | V     |                                             |       |

|                  |                             | 5.5V            | 0.7 V <sub>cc</sub>       | V <sub>cc</sub> +0.3 | 0.7 V <sub>cc</sub>       | V <sub>cc</sub> +0.3 | 2.5             | V     |                                             |       |

| V                | Input Low Voltage           | 3.0V            |                           |                      | GND-0.3                   |                      | 0.7             | V     |                                             |       |

|                  |                             | 5.5V            | GND-0.3                   |                      | GND-0.3                   |                      | 1.5             | V     |                                             |       |

| V <sub>OH1</sub> | Output High                 | 3.0V            | V <sub>cc</sub> -0.4      |                      | V <sub>cc</sub> -0.4      |                      | 3.1             | V     | I <sub>он</sub> = -2.0 mA                   | 8     |

| om               | Voltage                     | 5.5V            | V <sub>cc</sub> -0.4      |                      | V <sub>cc</sub> -0.4      |                      | 4.8             | V     | I <sub>он</sub> = -2.0 mA                   | 8     |

| V <sub>ol1</sub> | Output Low                  | 3.0V            |                           | 0.6                  |                           | 0.6                  | 0.2             | V     | $l_{ol} = +4.0 \text{ mA}$                  | 8     |

| 021              | Voltage                     | 5.5V            |                           | 0.4                  |                           | 0.4                  | 0.1 🚽           | V     | $l_{ol} = +4.0 \text{ mA}$                  | 8     |

| V <sub>OL2</sub> | Output Low                  | 3.0V            |                           | 1.2                  |                           | 1.2                  | 0.3             | V     | $I_{0} = +6 \text{ mA}$                     | 8     |

|                  | Voltage                     | 5.5V            |                           | 1.2                  |                           | 1.2                  | 0.3             | V     | l <sub>oL</sub> = +12 mA                    | 8     |

| V <sub>RH</sub>  | Reset Input High            | 3.0V            | .8 V <sub>cc</sub>        | V <sub>cc</sub>      | .8 V <sub>cc</sub>        | V <sub>cc</sub>      | 1.5             | V     |                                             |       |

|                  | Voltage                     | 5.5V            | .8 V <sub>cc</sub>        | V <sub>cc</sub>      | .8 V <sub>cc</sub>        | V <sub>cc</sub>      | 2.1             | V     |                                             |       |

| V <sub>RI</sub>  | Reset Input Low             | 3.0V            | GND-0.3                   | 0.2 V <sub>cc</sub>  | GND-0.3                   | Y                    | 1.1             | V     |                                             |       |

|                  | Voltage                     | 5.5V            | GND-0.3                   | 0.2 V <sub>cc</sub>  | GND-0.3                   | 0.2 V <sub>cc</sub>  | 1.7             | V     |                                             |       |

| VOFFSET          | Comparator Input<br>Offset  | 3.0V            | ~                         | 25                   |                           | 25                   | 10              | mV    |                                             | 10    |

|                  | Voltage                     | 5.5V            |                           | 25                   |                           | 25                   | 10              | mV    |                                             | 10    |

| I <sub>IL</sub>  | Input Leakage               | 3.0V            | -1                        | 1                    | -1                        | 2                    | <1              | μΑ    | $V_{IN} = OV, V_{CC}$                       |       |

|                  |                             | 5.5V            | -1                        | 1                    | -1                        | 2                    | <1              | μA    | $V_{IN} = OV, V_{CC}$                       |       |

| I <sub>ol</sub>  | Output Leakage              | 3.0V            | -1                        | 1                    | -1                        | 2                    | <1              | μA    | $V_{IN} = OV, V_{CC}$                       |       |

|                  |                             | 5.5V            | -1                        | 1                    | -1                        | 2                    | <1              | μA    | $V_{IN} = OV, V_{CC}$                       |       |

| l <sub>ir</sub>  | Reset Input                 | 3.0V            |                           | -130                 |                           | -130                 | -25             | μA    |                                             |       |

|                  | Current                     | 5.5V            |                           | -180                 |                           | -180                 | -40             | μΑ    |                                             |       |

| I <sub>cc</sub>  | Supply Current              | 3.0V            |                           | 20                   |                           | 20                   | 7               | mA    | @ 16 MHz                                    | 4, 15 |

|                  |                             | 5.5V            |                           | 25                   |                           | 25                   | 20              | mA    | @ 16 MHz                                    | 4, 15 |

|                  |                             | 5.0V            |                           | 7                    |                           | 7                    | 3               | mA    | @ 3.58 MHz                                  | 4, 15 |

|                  |                             | 5.0V            |                           | 10                   |                           | 10                   | 5               | mA    | @ 8 MHz                                     | 4, 15 |

| I <sub>CC1</sub> | Standby Current             | 3.0V            |                           | 4.5                  |                           | 4.5                  | 2.0             | mA    | HALT Mode $V_{IN} = OV, V_{CC} @ 16$<br>MHz | 4     |

|                  |                             | 5.5V            |                           | 8                    |                           | 8                    | 3.7             | mA    | HALT Mode $V_{IN} = OV, V_{CC} @ 16$<br>MHz | 4     |

|                  |                             | 3.0V            |                           | 3.4                  |                           | 3.4                  | 1.5             | mA    | Clock Divide-by-16 @ 16 MHz                 | 4     |

|                  |                             | 5.5V            |                           | 7.0                  |                           | 7.0                  | 2.9             | mA    | Clock Divide-by-16 @ 16 MHz                 | 4     |

#### Z86C83/C84 **Z8® MCU Microcontrollers**

|                  |                                                   | V <sub>cc</sub>   |     | = 0° C<br>+70°C       |            | = −40°C<br>+105°C     | Typical<br>[13] |       |                                                          |                |

|------------------|---------------------------------------------------|-------------------|-----|-----------------------|------------|-----------------------|-----------------|-------|----------------------------------------------------------|----------------|

| Sym              | Parameter                                         | Note 3            | Min | Max                   | Min        | Max                   |                 | Units | Conditions                                               | Notes          |

| I <sub>CC2</sub> | Standby Current                                   | 3.0V              |     | 8                     |            | 15                    | 1               | μΑ    | STOP Mode $V_{IN} = OV$ ,<br>$V_{cc}$ WDT is not Running | 6,11,15        |

|                  |                                                   | 5.5V              |     | 10                    |            | 20                    | 2               | μA    | STOP Mode $V_{IN} = OV$ ,<br>$V_{cc}$ WDT is not Running | 6,11,15        |

|                  |                                                   | 3.0V              |     | 500                   |            | 600                   | 310             | μA    | STOP Mode $V_{IN} = OV$ ,<br>$V_{cc}$ WDT is Running     | 6,11,14,<br>15 |

|                  |                                                   | 5.5V              |     | 800                   |            | 1000                  | 600             | μA    | STOP Mode $V_{IN} = OV$ ,<br>$V_{cc}$ WDT is Running     | 6,11,14,<br>15 |

| $V_{ICR}$        | Input Common<br>Mode                              | 3.0               | 0   | V <sub>cc</sub> -1.0∖ | / 0        | V <sub>cc</sub> -1.5V |                 | V     |                                                          | 10             |

|                  | Voltage Range                                     | 5.5               | 0   | V <sub>cc</sub> -1.0\ | / 0        | V <sub>cc</sub> -1.5V |                 | V     |                                                          | 10             |

|                  | Auto Latch Low                                    | 3.0V              |     | 8                     |            | 10                    | 5               | μA    | $OV < V_{IN} < V_{CC}$                                   | 9              |

|                  | Current                                           | 5.5V              |     | 15                    |            | 20                    | 11              | μA    | $OV < V_{IN} < V_{CC}$                                   | 9              |

|                  | Auto Latch High                                   | 3.0V              |     | -5                    |            | -7                    | -3              | μA    | $OV < V_{IN} < V_{CC}$                                   | 9              |

|                  | Current                                           | 5.5V              |     | -8                    |            | -10                   | -6              | μA    | $OV < V_{IN} < V_{CC}$                                   | 9              |

| V <sub>LV</sub>  | V <sub>cc</sub> Low-Voltage<br>Protection Voltage |                   | 2.0 | 3.3                   | 2.2        | 3.6                   | 3.0             | V     | 2 MHz max Int. CLK Freq.                                 | 7              |

| Note<br>1.       | s:<br>I <sub>cc1</sub><br>Clock-Driven            | Typical<br>0.3 mA |     |                       | Unit<br>mA | Freq<br>8 MHz         | 方を              | 2     | n                                                        |                |

| 0165.               |         |     |

|---------------------|---------|-----|

| 1. I <sub>cc1</sub> | Typical | Max |

| ١. | CC1          | i ypicai | iviax | Unit | Freq    |

|----|--------------|----------|-------|------|---------|

|    | Clock-Driven | 0.3 mA   | 5     | mA   | 8 MHz 👷 |

| 2  | GND = 0V     |          |       |      |         |

2. GND = 0V.

3. 3.0V V<sub>cc</sub> voltage specification guarantees 3.3V  $\pm$ 0.3V, and 5.5V V<sub>cc</sub> voltage specification guarantees 5.0V  $\pm$ 0.5V.

4. All outputs unloaded, I/O pins floating, inputs at rail.

- 5. CL1 = CL2 = 100 pF.

- 6. Same as note [4] except inputs at V $_{\rm cc}.$

7. The V<sub>1V</sub> increases as the temperature decreases

- 8. Standard Mode (not Low EMI).

- 9. Auto Latch (mask option) selected.

10. For analog comparator, inputs when analog comparators are enabled.

11. Clock must be forced Low, when XTAL 1 is clock-driven and XTAL2 is floating.

12. Excludes clock pins.

- 13. Typicals are at  $V_{\rm cc}$  = 5.0V and 3.3V.

- 14. Internal RC selected.

- 15. Combined Digital and Analog  $V_{\rm cc}$  supply current.

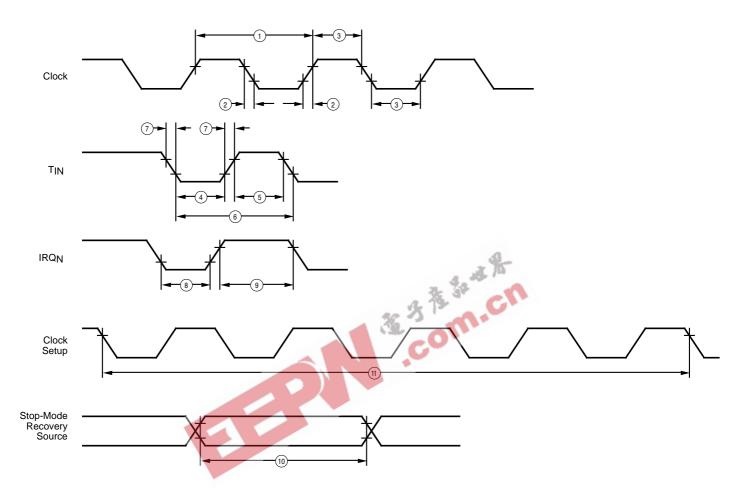

### AC ELECTRICAL CHARACTERISTICS

Additional Timing Diagram

Figure 7. Additional Timing

###

### AC ELECTRICAL CHARACTERISTICS (Continued)

Additional Timing Table (SCLK/TCLK = XTAL/2)

|    |         |                                  | V <sub>cc</sub> | 121  | Γ = 0°C<br>MHz | to +70° | C<br>MHz |      | T =40<br>MHz | +1 C to 0°C)<br>1 | I05°C<br>6 MHz |       |    |     |

|----|---------|----------------------------------|-----------------|------|----------------|---------|----------|------|--------------|-------------------|----------------|-------|----|-----|

| No | Symbol  | Parameter                        | Note 6          | Min  | Max            | Min     | Max      | Min  | Max          | Min               | Max            | Units | No | tes |

| 1  | ТрС     | Input Clock Period               | 3.0V            | 83   | DC             | 62.5    | DC       | 83   | DC           | 62.5              | DC             | ns    |    | 1   |

|    |         |                                  | 5.5V            | 83   | DC             | 62.5    | DC       | 83   | DC           | 62.5              | DC             | ns    |    | 1   |

| 2  | TrC,TfC | Clock Input Rise & Fall          | 3.0V            |      | 15             |         | 15       |      | 15           |                   | 15             | ns    |    | 1   |

|    |         | Times                            | 5.5V            |      | 15             |         | 15       |      | 15           |                   | 15             | ns    |    | 1   |

| 3  | TwC     | Input Clock Width                | 3.0V            | 41   |                | 31      |          | 41   |              | 31                |                | ns    |    | 1   |

|    |         |                                  | 5.5V            | 41   |                | 31      |          | 41   |              | 31                |                | ns    |    | 1   |

| 4  | TwTinL  | Timer Input Low Width            | 3.0V            | 100  |                | 100     |          | 100  |              | 100               |                | ns    |    | 1   |

|    |         |                                  | 5.5V            | 70   |                | 70      |          | 70   |              | 70                |                | ns    |    | 1   |

| 5  | TwTinH  | Timer Input High Width           | 3.0V            | 5TpC |                | 5TpC    |          | 5TpC |              | 5TpC              |                |       |    | 1   |

|    |         |                                  | 5.5V            | 5TpC |                | 5TpC    |          | 5TpC |              | 5TpC              |                |       |    | 1   |

| 6  | TpTin   | Timer Input Period               | 3.0V            | 8TpC |                | 8TpC    |          | 8TpC |              | 8TpC              |                |       |    | 1   |

|    |         |                                  | 5.5V            | 8TpC |                | 8TpC    |          | 8TpC |              | 8TpC              |                |       |    | 1   |

| 7  | TrTin,  | Timer Input Rise & Fall<br>Timer | 3.0V            |      | 100            |         | 100      |      | 100          |                   | 100            | ns    |    | 1   |

|    | TfTin   |                                  | 5.5V            |      | 100            |         | 100 <    | 1.10 | 100          |                   | 100            | ns    |    | 1   |

| 8A | TwIL    | Int. Request Low Time            | 3.0V            | 100  |                | 100     | X        | 100  | 110          | 100               |                | ns    | 1  | ,2  |

|    |         | I                                | 5.5V            | 70   |                | 70      | 510      | 70   |              | 70                |                | ns    |    | ,2  |

| 8B | TwIL    | Int. Request Low Time            | 3.0V            | 5TpC |                | 5TpC    |          | 5TpC |              | 5TpC              |                |       | 1  | ,3  |

|    |         | ·                                | 5.5V            | 5TpC |                | 5TpC    | <u> </u> | 5TpC |              | 5TpC              |                |       | 1  | ,3  |

| 9  | TwIH    | Int. Request Input High          | 3.0V            | 5TpC |                | 5TpC    |          | 5TpC |              | 5TpC              |                |       | 1  | ,2  |

|    |         | Time                             | 5.5V            | 5TpC |                | 5TpC    |          | 5TpC |              | 5TpC              |                |       | 1  | ,2  |

| 10 | Twsm    | STOP-Mode Recovery               | 3.0V            | 12   |                | 12      |          | 12   |              | 12                |                | ns    |    |     |

|    |         | Width Spec                       | 5.5V            | 12   |                | 12      |          | 12   |              | 12                |                | ns    |    |     |

| 11 | Tost    | Oscillator Startup Time          | 3.0V            |      | 5TpC           |         | 5TpC     |      | 5TpC         |                   | 5TpC           |       | 4  | 4   |

|    |         |                                  | 5.5V            |      | 5TpC           |         | 5TpC     |      | 5TpC         |                   | 5TpC           |       | 4  | 4   |

| 12 | Twdt    | Watch-Dog Timer Delay            |                 |      |                |         |          |      |              |                   | WDTMR          | Reg.  | D1 | D0  |

|    |         | Time                             | 3.0V            | 6.25 |                | 6.25    |          | 6.25 |              | 6.25              |                | ms    | 0  | 0   |

|    |         |                                  | 3.0V            | 12.5 |                | 12.5    |          | 12.5 |              | 12.5              |                | ms    | 0  | 1   |

|    |         |                                  | 3.0V            | 25   |                | 25      |          | 25   |              | 25                |                | ms    | 1  | 0   |

|    |         |                                  | 3.0V            | 100  |                | 100     |          | 100  |              | 100               |                | ms    | 1  | 1   |

| 13 | T       | Power On Reset Delay             | 3.0V            | 7    | 24             | 7       | 25       | 7    | 24           | 7                 | 25             | ms    |    | •   |

|    | POR     |                                  | 5.5V            | 3    | 13             | 3       | 14       | 3    | 13           | 3                 | 14             | ms    |    |     |

Notes:

1. Timing Reference uses 0.7  $V_{\rm cc}$  for a logic 1 and 0.2  $V_{\rm cc}$  for a logic 0.

2. Interrupt request via Port 3 (P31-P33).

3. Interrupt request via Port 3 (P30).

4. SMR-D5 = 0.

5. The V<sub>cc</sub> voltage specification of 3.0V guarantees 3.3V  $\pm$ 0.3V, and the V<sub>cc</sub> voltage specification of 5.5V guarantees 5.0V  $\pm$ 0.5V.

### AC ELECTRICAL CHARACTERISTICS (Continued)

Additional Timing Table (Divide-By-One Mode, SCLK/TCLK = XTAL)

|    |         |                               | V <sub>cc</sub> | $T_A = 0^{\circ}C$<br>4 N |      | $T_A = -40^{\circ}C$<br>4 N |      |       |         |

|----|---------|-------------------------------|-----------------|---------------------------|------|-----------------------------|------|-------|---------|

| No | Symbol  | Parameter                     | Note 6          | Min                       | Max  | Min                         | Max  | Units | Notes   |

| 1  | ТрС     | Input Clock Period            | 3.0V            | 250                       | DC   | 250                         | DC   | ns    | 1,7,8   |

|    |         |                               | 5.5V            | 250                       | DC   | 250                         | DC   | ns    | 1,7,8   |

| 2  | TrC,TfC | Clock Input Rise & Fall Times | 3.0V            |                           | 25   |                             | 25   | ns    | 1,7,8   |

|    |         |                               | 5.5V            |                           | 25   |                             | 25   | ns    | 1,7,8   |

| 3  | TwC     | Input Clock Width             | 3.0V            | 125                       |      | 125                         |      | ns    | 1,7,8   |

|    |         |                               | 5.5V            | 125                       |      | 125                         |      | ns    | 1,7,8   |

| 4  | TwTinL  | Timer Input Low Width         | 3.0V            | 100                       |      | 100                         |      | ns    | 1,7,8   |

|    |         |                               | 5.5V            | 70                        |      | 70                          |      | ns    | 1,7,8   |

| 5  | TwTinH  | Timer Input High Width        | 3.0V            | 3TpC                      |      | 3TpC                        |      |       | 1,7,8   |

|    |         |                               | 5.5V            | 3TpC                      |      | 3TpC                        |      |       | 1,7,8   |

| 6  | TpTin   | Timer Input Period            | 3.0V            | 4TpC                      |      | 4TpC                        |      |       | 1,7,8   |

|    |         |                               | 5.5V            | 4TpC                      |      | 4TpC                        |      |       | 1,7,8   |

| 7  | TrTin,  | Timer Input Rise & Fall Timer | 3.0V            |                           | 100  | 10                          | 100  | ns    | 1,7,8   |

|    | TfTin   |                               | 5.5V            |                           | 100  | -                           | 100  | ns    | 1,7,8   |

| 8A | TwIL    | Int. Request Low Time         | 3.0V            | 100                       | 12   | 0100                        |      | ns    | 1,2,7,8 |

|    |         |                               | 5.5V            | 70                        | -11- | 70                          |      | ns    | 1,2,7,8 |

| 8B | TwIL    | Int. Request Low Time         | 3.0V            | 3TpC                      | 0.   | 3TpC                        |      |       | 1,3,7,8 |

|    |         |                               | 5.5V            | 3TpC                      |      | 3TpC                        |      |       | 1,3,7,8 |

| 9  | TwIH    | Int. Request Input High Time  | 3.0V            | ЗТрС                      |      | 3TpC                        |      |       | 1,2,7,8 |

|    |         |                               | 5.5V            | 3TpC                      |      | 2TpC                        |      |       | 1,2,7,8 |

| 10 | Twsm    | STOP-Mode Recovery Width Spec | 3.0V            | 12                        |      | 12                          |      | ns    | 4,8     |

|    |         |                               | 5.5V            | 12                        |      | 12                          |      | ns    | 4,8     |

| 11 | Tost    | Oscillator Startup Time       | 3.0V            |                           | 5TpC |                             | 5TpC |       | 4,8,9   |

|    |         |                               | 5.5V            |                           | 5TpC |                             | 5TpC |       | 4,8,9   |

#### Notes:

1. Timing Reference uses 0.7  $V_{\rm cc}$  for a logic 1 and 0.2  $V_{\rm cc}$  for a logic 0.

2. Interrupt request via Port 3 (P33-P31).

3. Interrupt request via Port 3 (P30).

4. SMR-D5 = 1, POR STOP mode delay is on.

5. Reg. WDTMR.

6. The V<sub>cc</sub> voltage specification of 3.0V guarantees 3.3V  $\pm$ 0.3V, and the V<sub>cc</sub> voltage specification of 5.5V guarantees 5.0V  $\pm$ 0.5V. 7. SMR D1 = 0.

8. Maximum frequency for internal system clock is 4 MHz when using XTAL divide-by-one mode.

9. For XTAL and LC oscillator, and for oscillator driven by clock driver.

### **AC ELECTRICAL CHARACTERISTICS**

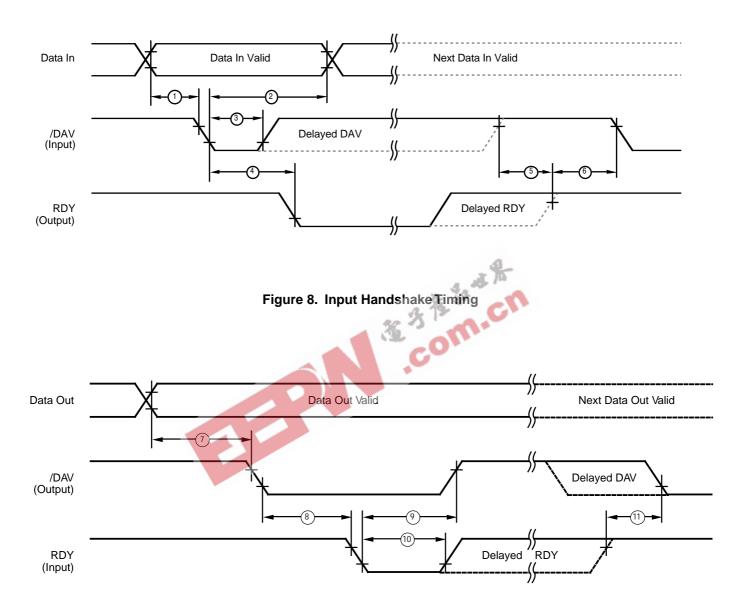

Handshake Timing Diagrams

Figure 9. Output Handshake Timing

### AC ELECTRICAL CHARACTERISTICS (Continued)

Handshake Timing Table

|    |              |                            | v                          |             | = 0°C      |             |            |             | –40°C      |     |            | Dete              |

|----|--------------|----------------------------|----------------------------|-------------|------------|-------------|------------|-------------|------------|-----|------------|-------------------|

| No | Symbol       | Parameter                  | V <sub>cc</sub><br>Note1,2 | 12 M<br>Min | MHz<br>Max | 16 I<br>Min | MHz<br>Max | 12 I<br>Min | MHz<br>Max |     | MHz<br>Max | Data<br>Direction |

| 1  | TsDI(DAV)    | Data In Setup Time         | 3.0V                       | 0           |            | 0           |            | 0           |            | 0   |            | IN                |

|    |              |                            | 5.5V                       | 0           |            | 0           |            | 0           |            | 0   |            | IN                |

| 2  | ThDI(DAV)    | Data In Hold Time          | 3.0V                       | 160         |            | 160         |            | 160         |            | 160 |            | IN                |

|    |              |                            | 5.5V                       | 115         |            | 115         |            | 115         |            | 115 |            | IN                |

| 3  | TwDAV        | Data Available Width       | 3.0V                       | 155         |            | 155         |            | 155         |            | 155 |            | IN                |

|    |              |                            | 5.5V                       | 110         |            | 110         |            | 110         |            | 110 |            | IN                |

| 4  | TdDAVI(RDY)  | DAV Fall to RDY Fall Delay | 3.0V                       |             | 160        |             | 160        |             | 160        |     | 160        | IN                |

|    |              |                            | 5.5V                       |             | 115        |             | 115        |             | 115        |     | 115        | IN                |

| 5  | TdDAVId(RDY) | DAV Rise to RDY Rise Delay | 3.0V                       |             | 120        |             | 120        |             | 120        |     | 120        | IN                |

|    |              |                            | 5.5V                       |             | 80         |             | 80         |             | 80         |     | 80         | IN                |

| 6  | TdRDY0(DAV)  | RDY Rise to DAV Fall Delay | 3.0V                       | 0           |            | 0           |            | 0           |            | 0   |            | IN                |

|    |              |                            | 5.5V                       | 0           |            | 0           |            | 0           |            | 0   |            | IN                |

| 7  | TdD0(DAV)    | Data Out to DAV Fall Delay | 3.0V                       | 42          |            | 31          | 175        | 42          |            | 31  |            | OUT               |

|    |              |                            | 5.5V                       | 42          | -ðc        | 31          |            | 42          |            | 31  |            | OUT               |

| 8  | TdDAV0(RDY)  | DAV Fall to RDY Fall Delay | 3.0V                       | 0           | 273        | 0           | C          | 0           |            | 0   |            | OUT               |

|    |              |                            | 5.5V                       | 0           |            | 0           |            | 0           |            | 0   |            | OUT               |

| 9  | TdRDY0(DAV)  | RDY Fall to DAV Rise Delay | 3.0V                       |             | 160        |             | 160        |             | 160        |     | 160        | OUT               |

|    |              |                            | 5.5V                       |             | 115        |             | 115        |             | 115        |     | 115        | OUT               |

| 10 | TwRDY        | RDY Width                  | 3.0V                       | 110         |            | 110         |            | 110         |            | 110 |            | OUT               |

|    |              |                            | 5.5V                       | 80          |            | 80          |            | 80          |            | 80  |            | OUT               |

| 11 | TdRDY0d(DAV) | RDY Rise to DAV Fall Delay | 3.0V                       |             | 110        |             | 110        |             | 110        |     | 110        | OUT               |

|    |              |                            | 5.5V                       |             | 80         |             | 80         |             | 80         |     | 80         | OUT               |

Notes:

1. Timing Reference uses 0.7 V<sub>cc</sub> for a logic 1 and 0.2 V<sub>cc</sub> for a logic 0.

2. The V<sub>cc</sub> voltage specification of 3.0V guarantees 3.3V ±0.3V and the V<sub>cc</sub> voltage specification of 5.5V guarantees 5.0V ±0.5V.

### Z86C83/C84 Z8<sup>®</sup> MCU Microcontrollers

<sup>®</sup>ZiLŒ

| Table 5. | D/A Converter Electrical Characteristics |

|----------|------------------------------------------|

|          | $V_{cc}$ = 3.3V $\pm$ 10%                |

| Parameter                  | Minimum | Typical | Maximum | Units  |

|----------------------------|---------|---------|---------|--------|

| Resolution                 |         | 8       |         | Bits   |

| Integral non-linearity     |         | 0.25    | 1       | LSB    |

| Differential non-linearity |         | 0.25    | 0.5     | LSB    |

| Setting time, 1/2 LSB      |         | 1.5     | 3.0     | μsec   |

| Zero Error at 25°C         |         | 10      | 20      | mV     |

| Full Scale error at 25°C   |         | 0.25    | 0.5     | LSB    |

| Supply Range               | 3.0     | 3.3     | 3.6     | Volts  |

| Power dissipation, no load |         | 10      |         | mW     |

| Ref Input resistance       | 2K      | 4K      | 10K     | Ohms   |

| Output noise voltage       |         | 50      |         | μVp-p  |

| VDHI range at 3 volts      | 1.5     | 1.8     | 2.1     | Volts  |

| VDLO range at 3 volts      | 0.2     | 0.5     | 0.8     | Volts  |

| VDHI–VDLO, at 3 volts      | 1.3     | 1.6     | 1.9     | Volts  |

| Capacitive output load, CL |         |         | 20      | pF     |

| Resistive output load, RL  | 50K     |         |         | Ohms   |

| Output slew rate           | 1.0     | 3.0     | 8-      | V/µsec |

| Notes:                     |         | × 3 × 3 | -       |        |

| Voltage: 3.0V to 3.6V      |         | n B     | C       |        |

| Temp: 0–70°C               |         | 38. 35  |         |        |

# Table 6. D/A Converter Electrical Characteristics $V_{cc}$ = 5.0V ±10%

| Parameter                  | Minimum | Typical | Maximum | Units  |

|----------------------------|---------|---------|---------|--------|

| Resolution                 |         | 8       |         | Bits   |

| Integral non-linearity     |         | 0.25    | 1       | LSB    |

| Differential non-linearity |         | 0.25    | 0.5     | LSB    |

| Setting time, 1/2 LSB      |         | 1.5     | 3.0†    | μsec   |

| Zero Error at 25°C         |         | 10      | 20      | mV     |

| Full Scale error at 25°C   |         | 1       | 2       | % FSR  |

| Supply Range               | 4.5     | 5.0     | 5.5     | Volts  |

| Power dissipation, no load |         | 50      | 85      | mW     |

| Ref Input resistance       | 2K      | 4K      | 10K     | Ohms   |

| Output noise voltage       |         | 50      |         | μVp-p  |

| VDHI range at 5 volts      | 2.6     |         | 3.5     | Volts  |

| VDLO range at 5V volts     | 0.8     |         | 1.7     | Volts  |

| VDHI–VDLO, at 5V volts     | 0.9     |         | 2.7     | Volts  |

| Capacitive output load, CL |         |         | 30      | pF     |

| Resistive output load, RL  | 20K     |         |         | Ohms   |

| Output slew rate           | 1.0     | 3.0     |         | V/µsec |

Notes:

Voltage: 4.5V - 5.5V

† The C84 Emulator has maximum setting time of 20 µsec. (10 µsec. typical).

Temp: 0-70°C

### AC ELECTRICAL CHARACTERISTICS (Continued)

| Parameter                                                                            | Minimum               | Typical   | Maximum               | Units |

|--------------------------------------------------------------------------------------|-----------------------|-----------|-----------------------|-------|

| Resolution                                                                           |                       | 8         |                       | Bits  |

| Integral non-linearity                                                               |                       | 0.5       | 1                     | LSB   |

| Differential non-linearity                                                           |                       | 0.5       | 1                     | LSB   |

| Zero Error at 25°C                                                                   |                       |           | 5.0                   | mV    |

| Supply Range                                                                         | 3.0                   | 3.3       | 3.6                   | Volts |

| Power dissipation, no load                                                           |                       | 20        | 40                    | mW    |

| Clock frequency                                                                      |                       |           | 24                    | MHz   |

| Input voltage range                                                                  | VA <sub>LO</sub>      |           | VA <sub>HI</sub>      | Volts |

| Conversion time                                                                      | 4.3                   |           | 35 X SCLK             | μsec  |

| Input capacitance on ANA                                                             | 25                    |           | 40                    | pF    |

| VA <sub>HI</sub> range                                                               | VA <sub>LO</sub> +2.5 |           | AV <sub>cc</sub>      | Volts |

| VA <sub>LO</sub> range                                                               | AN <sub>GND</sub>     |           | AV <sub>cc</sub> –2.5 | Volts |

| VA <sub>HI</sub> VA <sub>LO</sub>                                                    | 2.5                   | đ         | AV <sub>cc</sub>      | Volts |

| Notes:<br>Voltage: 3.0V to 3.6V<br>Temp: 0-70°C<br>SCLK = System Clock on Bus Speed. |                       | * 3 1 3 4 |                       |       |

### Table 7. A/D Converter Electrical Characteristics $V^{}_{cc}$ = 3.3V $\pm$ 10%

## Table 8. A/D Converter Electrical Characteristics $V_{cc}$ = 5.0V ±10%

| Parameter                         | Minimum               | Typical | Maximum               | Units |

|-----------------------------------|-----------------------|---------|-----------------------|-------|

| Resolution                        |                       | 8       |                       | Bits  |

| Integral non-linearity            |                       | 0.5     | 1                     | LSB   |

| Differential non-linearity        |                       | 0.5     | 1                     | LSB   |

| Zero Error at 25°C                |                       |         | 45                    | mV    |

| Supply Range                      | 4.5                   | 5.0     | 5.5                   | Volts |

| Power dissipation, no load        |                       | 50      | 85                    | mW    |

| Clock frequency                   |                       |         | 33                    | MHz   |

| Input voltage range               | VA <sub>LO</sub>      |         | VA <sub>HI</sub>      | Volts |

| Conversion time                   | 4.3                   |         | 35 X SCLK             | μsec  |

| Input capacitance on ANA          | 25                    |         | 40                    | pF    |

| VA <sub>HI</sub> range            | VA <sub>LO</sub> +2.5 |         | AV <sub>cc</sub>      | Volts |

| VA <sub>LO</sub> range            | AN <sub>GND</sub>     |         | AV <sub>cc</sub> -2.5 | Volts |

| VA <sub>HI</sub> VA <sub>LO</sub> | 2.5                   |         | AV <sub>cc</sub>      | Volts |

Notes:

Voltage: 4.5V -5.5V

Temp: 0-70°C

Conversion time is defined as the time from initiation of A-D conversion to storage of the digital result in the ADR register. SCLK = System Clock on Bus Speed.

### **PIN FUNCTIONS**

### **Application Precaution**

The production test-mode environment may be enabled accidentally during normal operation if **excessive noise surges above**  $V_{cc}$  occur on the /RESET pin.

Recommendations for dampening voltage surges in both test and OTP mode include the following:

- Using a clamping diode to /RESET

- Adding a capacitor to the affected pin

**XTAL1.** *Crystal 1* (time-based input). This pin connects a parallel-resonant crystal, ceramic resonator, LC network or an external single-phase clock to the on-chip oscillator input.

**XTAL2.** *Crystal 2* (time-based output). This pin connects a parallel-resonant crystal, ceramic resonator, LC network to the on-chip oscillator output.

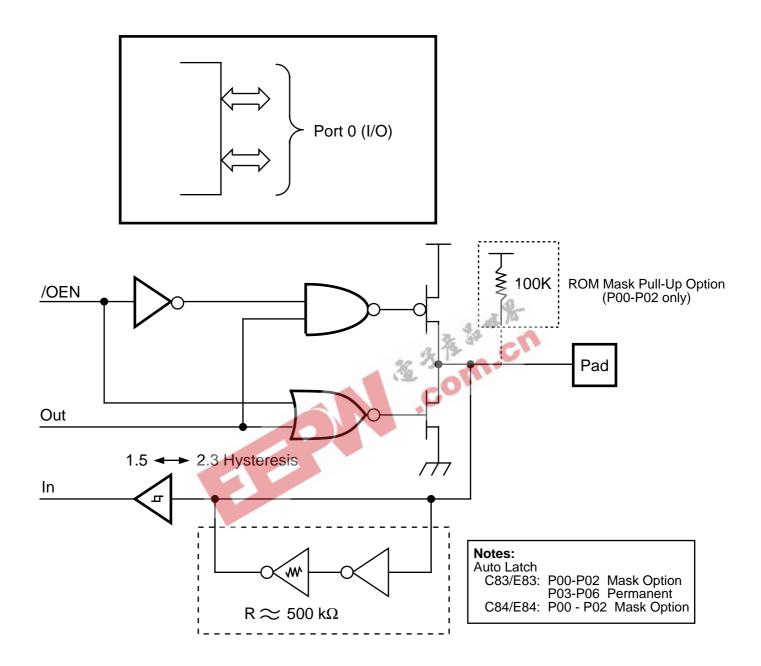

**Port 0 P00-P06.** (*P03-P06 is not available on the Z86C84*). Port 0 is a 7-bit, bidirectional, CMOS-compatible I/O port. These seven I/O lines can be nibble programmable as P00-P03 input/output and P04-P06 input/output, separately (Figure 10). All input buffers are Schmitt-triggered and output drivers are push-pull. There is a ROM mask option to enable 100K (±40%) pull-up resistors to Port 0, P00 to P02.

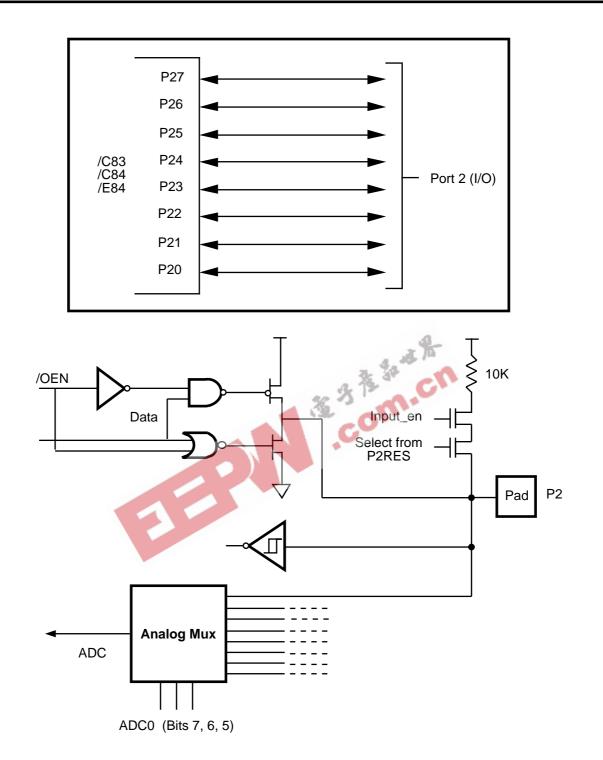

**Port 0 Auto Latch.** (Auto Latch Mask Option available only on P00-P02. P03-P06 has the Auto Latches permanently enabled.) The Auto Latch provides valid CMOS Levels when P00-P06 (P00-P02 on C84) are selected as inputs and not externally driven. It is impossible to determine if a non-driven input is 1 or 0, however; the Auto Latch will sense the input condition and drive a valid CMOS level, thereby eliminating a floating mode that could cause excessive current. (Auto Latch is a ROM mask option for the Z86C83, Z86C84). **Port 2 (P27-P20)** Port 2 is an 8-bit, bi-directional, CMOScompatible I/O port and an 8-channel muxed input to the 8-bit ADC. When configured as a digital input, by programming the Port2 Mode register, the Port 2 register can be evaluated to read digital data applied to Port 2, or the ADC result register can be read to evaluate the analog signals applied to Port 2 after configuring the ADC Control Registers. The direction of each of the eight Port 2 I/O lines can be configured individually (Figure 11).

In addition, all four versions of the device provide the capability of connecting 10K ( $\pm$ 20%) pull-up resistors to each of the Port 2 I/O lines individually. The pull-ups are connected when activated through software control of P2RES register (Figure 67) when the corresponding Port 2 pin is configured to be an input. The pull-up resistor of a Port 2 I/O line is automatically disabled when the corresponding I/O is an output, regardless of the state of the corresponding P2RES bit value.

**Note:** The Z86C83/C84 Emulator does not emulate the P2RES Register. Selection of the pull-ups are done via jumper settings on the emulator.

### ⊗ZiL05

### **PIN FUNCTIONS** (Continued)

Figure 10. Port 0 Configuration

17

Figure 11. Port 2 Configuration

### **PIN FUNCTIONS** (Continued)

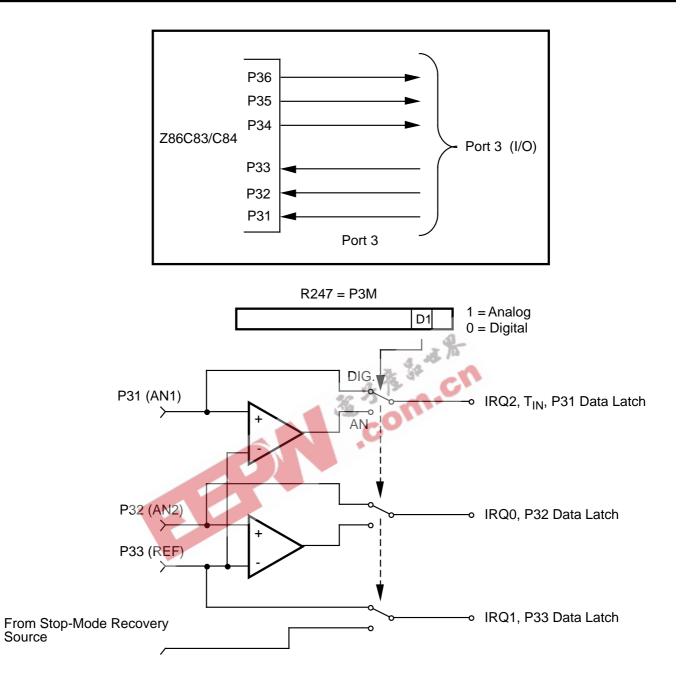

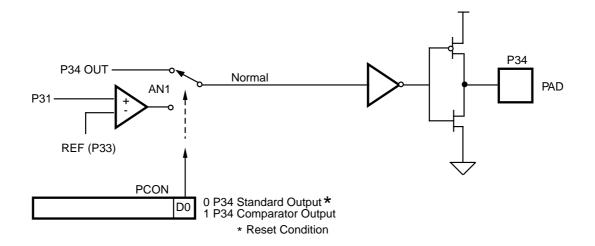

**Port 3 (P37-P30).** Port 3 is a 6-bit, CMOS-compatible port, with three fixed inputs (P33-P31) and three fixed outputs (P34-P36), configured under software control for Input/Output, Counter/Timers, interrupt, and port handshake. P31, P32, and P33 are standard CMOS inputs (no Auto Latches). Pins P34, P35, and P36 are push-pull output lines (Figure 11). Low EMI output buffers can be globally programmed by the software.

Two on-board comparators can process analog signals on P31 and P32 with reference to the voltage on P33. The analog function is enabled by programming Port 3 Mode Register (P3M bit 1). For Interrupt functions, Port 3, pin 3 is falling-edge interrupt input. P31 and P32 are programmable as rising, falling, or both edge triggered interrupts (IRQ register bits 6 and bit 7). P33 is the comparator reference voltage input when in Analog Mode. Access to Counter/Timers 1 is made through P31 ( $T_{IN}$ ) and P36 ( $T_{OUT}$ ). Handshake lines for Ports 0 and 2 are available on P31/P36 and P32/P35 (Table 9).

Port 3 also provides the following control functions: handshake for Ports 0 and 2 (/DAV and RDY); three external interrupt request signals (IRQ2-IRQ0); timer input and output signals ( $T_{IN}$  and  $T_{our}$ ).

|                                         |               | Table 9.         | Port 3 Pin | Assign | ments |       |

|-----------------------------------------|---------------|------------------|------------|--------|-------|-------|

| Pin                                     | I/O           | CTC1             | Analog     | Int.   | P0 HS | P2 HS |

| P31                                     | IN            | T <sub>IN</sub>  | AN1        | IRQ2   |       | D/R   |

| P32                                     | IN            |                  | AN2        | IRQ0   | D/R   |       |

| P33                                     | IN            |                  | REF        | IRQ1   |       |       |

| P34                                     | OUT           |                  | AN1-OUT    |        |       |       |

| P35                                     | OUT           |                  |            |        | R/D   |       |

| P36                                     | OUT           | T <sub>OUT</sub> |            |        |       | R/D   |

| <b>Note:</b><br>HS =<br>D = /[<br>R = R | Handsh<br>DAV | nake Sign        | als        |        |       |       |

**Auto Latch.** The Auto-Latch instruction puts valid CMOS levels on all CMOS inputs (except P33-P31) that are not externally driven. Whether this level is 0 or 1, cannot be determined. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer.

### Notes:

- 1. Deletion of Port Auto Latches is available as a ROM mask option. The Auto Latch Delete option is selected by the customer when the ROM code is submitted.

- 2. Ports 03, 04, 05, 07 have permanently enabled Auto Latches.

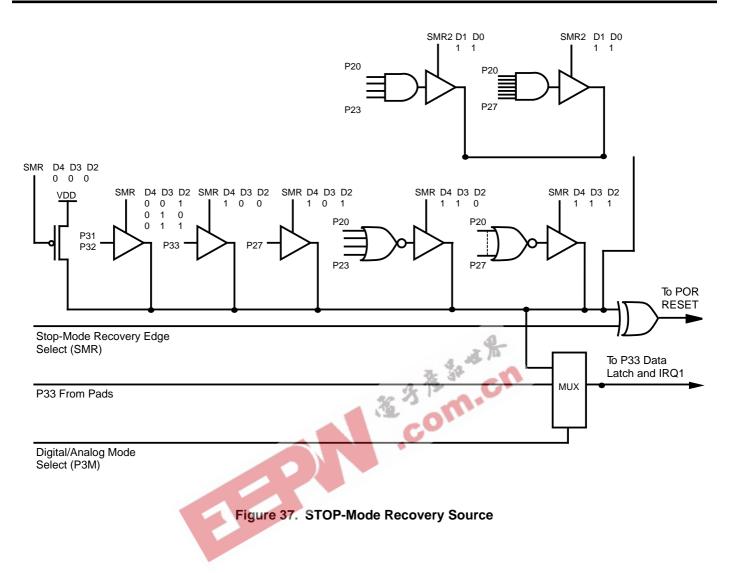

**Comparator Inputs.** Port 3, P31 and P32, each have a comparator front end. The comparator reference voltage, P33, is common to both comparators. In analog mode, the P33 input functions as a reference voltage to the comparators. In Analog Mode, the internal P33 register and its corresponding IRQ1 is connected to the Stop-Mode Recovery source selected by the SMR register. In this mode, any of the Stop-Mode Recovery sources are used to toggle the P33 bit or generate IRQ1. In Digital Mode, P33 can be used as a Port 3 register input or IRQ1 source. P34 outputs the comparator outputs by software programming the PCON Register bit D0 to 1.

Figure 12. Port 3 Input Configuration

@ Zilœ

### **PIN FUNCTIONS** (Continued)

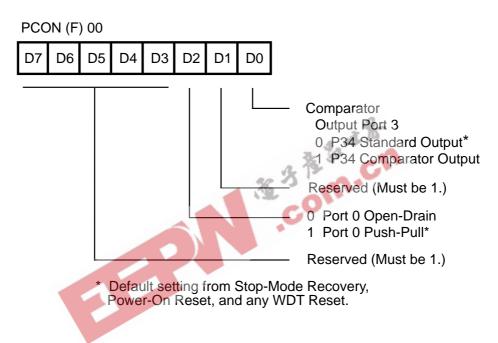

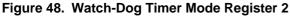

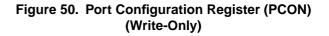

**Port Configuration Register (PCON).** The PCON configures the ports individually for comparator output on Port 3. The PCON Register is located in the Expanded Register File at Bank F, location 00 (Figure 13).

Bit 0 multiplexes comparator AN1 Output at P34. A "1" in this location brings the comparator output to P34

(Figure 14), and a "0" puts P34 into its standard I/O configuration.

**Note:** Only comparator output AN1 is multiplexed to a Port 3 output. Comparator AN2 output is not connected to any pins. Note that the PCON Register is reset upon the occurrence of a WDT RESET (not in Stop Mode), and Power-On Reset (POR).

Figure 13. Port Configuration Register (PCON) (Write-Only)

### FUNCTIONAL DESCRIPTION

**RESET.** (Input, Active Low). This pin initializes the MCU. Reset is accomplished either through Power-On Reset (POR), Watch-Dog Timer (WDT) Reset, or external reset. During POR, and WDT Reset, the internally generated reset is driving the reset pin Low for the POR time. *Any devices driving the reset line must be open-drain to avoid damage from a possible conflict during reset conditions.* Pull-up is provided internally.

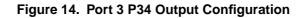

After the POR time, /RESET is a Schmitt-triggered input. After the reset is detected, an internal RST signal is latched and held for an internal register count of 18 external clocks, or for the duration of the external reset, whichever is longer. Program execution begins at location 000C (hex), 5-10 TpC cycles after the RST is released. For POR, the reset output time is  $T_{POR}$ .

**Program Memory.** C83/C84 can address up to 4 KB of internal Program Memory (Figure 15). The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts. Bytes 13 to 4095 consist of on-chip, mask-programmed ROM.

**ROM Protect.** The 4 KB of Program Memory is mask programmable. A ROM protect feature will prevent dumping of the ROM contents from an external program outside the ROM.

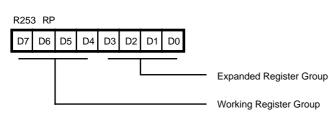

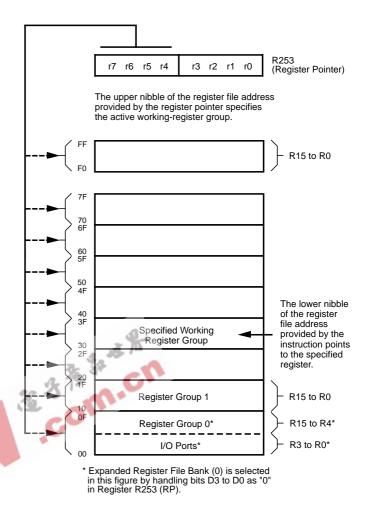

**Expanded Register File.** The register file has been expanded to allow for additional system control registers and for mapping of additional peripheral devices and input/output ports into the register address area. The Z8 register address space R0 through R15 is implemented as 16 groups of 16 registers per group (Figure 16). These register banks are known as the Expanded Register File (ERF). Bits 3-0 of the Register Pointer (RP) select the active ERF bank. Bits 7-4 of register RP select the working register group (Figure 17). Four system configuration registers reside in the ERF address space in Bank F and eight registers reside in Bank C. The rest of the ERF addressing space is not physically implemented, and is open for future expansion.

**Note:** When using Zilog's Cross Assembler version 2.1 or earlier, use the LD RP, #0X instruction rather than the SRP #0X instruction to access the ERF.

Figure 15. Program Memory Map

2ilas

### Figure 16. Expanded Register File Architecture

#### Z86C83/C84 Z8<sup>®</sup> MCU Microcontrollers

### <sup>®</sup>ZiLŒ

Note: Default Setting After Reset = 0000000

#### Figure 17. Register Pointer Register

**Register File.** The Register File consists of three I/O port registers, 237 general-purpose registers, 15 control and status registers, and four system configuration registers in the Expanded Register Group (Figure 16). The instructions can access registers directly or indirectly through an 8-bit address field. This allows a short 4-bit register address using the Register Pointer (Figure 18). In the 4-bit mode, the Register File is divided into 16 working register groups, each occupying 16 continuous locations. The Register Pointer addresses the starting location of the active working-register group.

**Note:** Register Bank E0-EF is only accessed through working registers and indirect addressing modes.

CAUTION: D4 of Control Register P01M (R251) must be 0.

**R254.** The C83/C84 has one extra general-purpose register located at FEH (R254). It is set to 00H after any reset.

**Stack.** The C83/C84 has an 8-bit Stack Pointer (R255) used for the internal stack that resides within the 236 general-purpose registers. Register R254 cannot be used for stack.

**General-Purpose Registers (GPR).** These registers are undefined after the device is powered up. The registers keep their last value after any reset, as long as the reset occurs in the  $V_{cc}$  voltage-specified operating range. It will not keep its last state from a  $V_{LV}$  reset if the  $V_{cc}$  drops below 1.8V. This includes Register R254.

**Note:** Register Bank E0-EF is only accessed through working register and indirect addressing modes.

Figure 18. Register Pointer

**RAM Protect.** The upper portion of the RAM's address spaces %80F to %EF (excluding the control registers) are protected from reading and writing. The RAM Protect bit option is mask-programmable and is selected by the customer when the ROM code is submitted. After the mask option is selected, the user activates this feature from the internal ROM code to turn off/on the RAM Protect by loading either a 0 or 1 into the Interrupt Mask (IMR) register, bit D6. A 1 in D6 enables RAM Protect.

### & Sirue

### FUNCTIONAL DESCRIPTION (Continued)

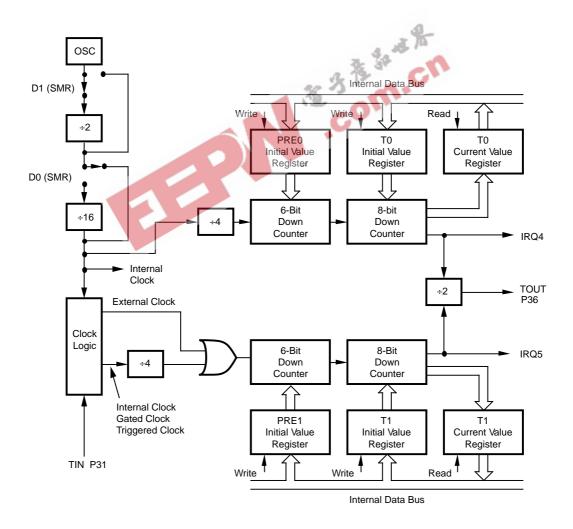

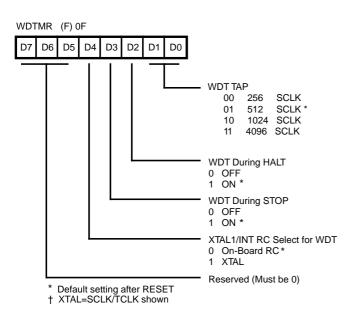

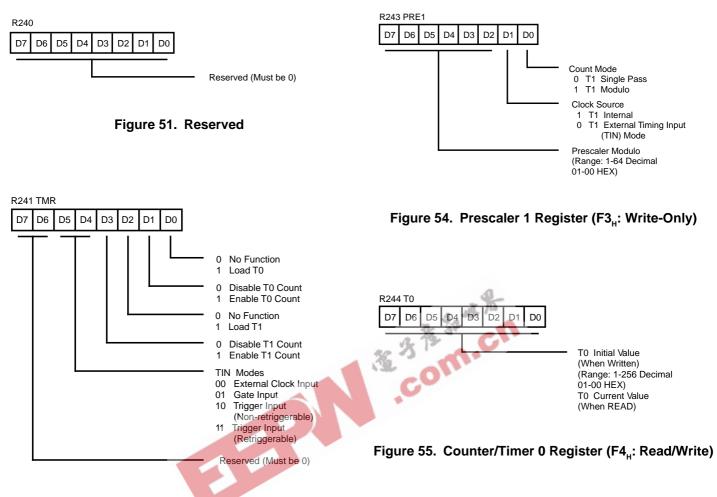

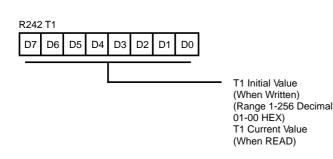

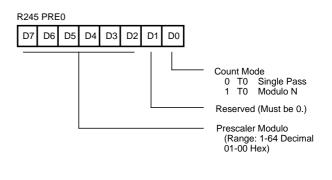

**Counter/Timers.** There are two 8-bit programmable counter/timers (T0-T1), each driven by its own 6-bit programmable prescaler. The T1 prescaler is driven by internal or external clock sources; however, the T0 prescaler is driven by the internal clock only (Figure 19).

The 6-bit prescalers can divide the input frequency of the clock source by any integer number from 1 to 64. Each prescaler drives its counter, which decrements the value (1 to 256) that has been loaded into the counter. When the counter reaches the end of the count, a timer interrupt request, IRQ4 (T0) or IRQ5 (T1), is generated.

The counters can be programmed to start, stop, restart to continue, or restart from the initial value. The counters can

also be programmed to stop upon reaching zero (single pass mode) or to automatically reload the initial value and continue counting (modulo-n continuous mode).

The counters, **but not the prescalers**, are read at any time without disturbing their value or count mode. The clock source for T1 is user-definable and is either the internal microprocessor clock divide-by-four, or an external signal input through Port 3. The Timer Mode register configures the external timer input (P31) as an external clock, a trigger input that can be retriggerable or non-retriggerable, or as a gate input for the internal clock. The counter/timers can be cascaded by connecting the T0 output to the input of T1. T<sub>IN</sub> Mode is enabled by setting R243 PRE1 Bit D1 to 0.

Figure 19. Counter/Timer Block Diagram

#### Z86C83/C84 Z8<sup>®</sup> MCU Microcontrollers

### & Silæ

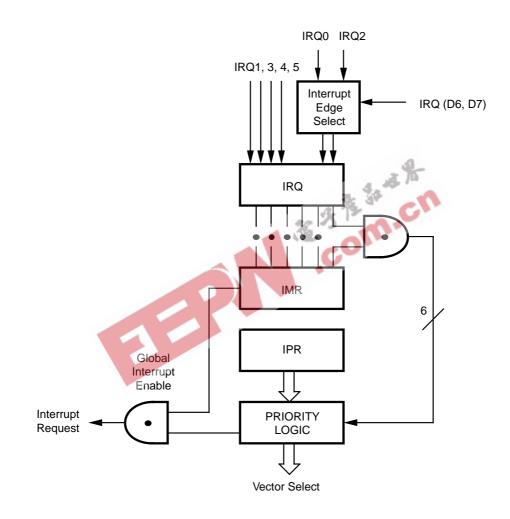

**Interrupts.** The Z8 has six different interrupts from six different sources. These interrupts are maskable, prioritized (Figure 20) and the six sources are divided as follows: four sources are claimed by Port 3 lines P33-P30, and two in counter/timers (Table 10). The Interrupt Mask Register globally or individually enables or disables the six interrupt requests.

When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority register. An interrupt machine cycle is activated when an interrupt request is granted. This action disables all subsequent interrupts, saves the Program Counter and Status Flags, and then branches to the program memory vector location reserved for that interrupt.

Figure 20. Interrupt Block Diagram

| Name  | Source                       | Vector Location | Comments                                  |

|-------|------------------------------|-----------------|-------------------------------------------|

| IRQ0  | /DAV0, IRQ0                  | 0, 1            | External (P32), Rise/ Fall Edge Triggered |

| IRQ1, | IRQ1                         | 2, 3            | External (P33), Fall Edge Triggered       |

| IRQ2  | /DAV2, IRQ2, T <sub>IN</sub> | 4, 5            | External (P31), Rise /Fall Edge Triggered |

| IRQ3  | IRQ3                         | 6, 7            | By User Software                          |

| IRQ4  | ТО                           | 8, 9            | Internal                                  |

| IRQ5  | T1                           | 10, 11          | Internal                                  |

| Table 10. | Interrupt Types, Sources, and Vectors |  |

|-----------|---------------------------------------|--|

|-----------|---------------------------------------|--|

### FUNCTIONAL DESCRIPTION (Continued)

All Z8 interrupts are vectored through locations in the program memory. This memory location and the next byte contain the 16-bit address of the interrupt service routine for that particular interrupt request. To accommodate polled interrupt systems, interrupt inputs are masked and the Interrupt Request register is polled to determine which of the interrupt requests need service.

An interrupt resulting from AN1 is mapped into IRQ2, and an interrupt from AN2 is mapped into IRQ0. Interrupts IRQ2 and IRQ0 may be rising, falling, or both edge triggered, and are programmable by the user. The software may poll to identify the state of the pin.

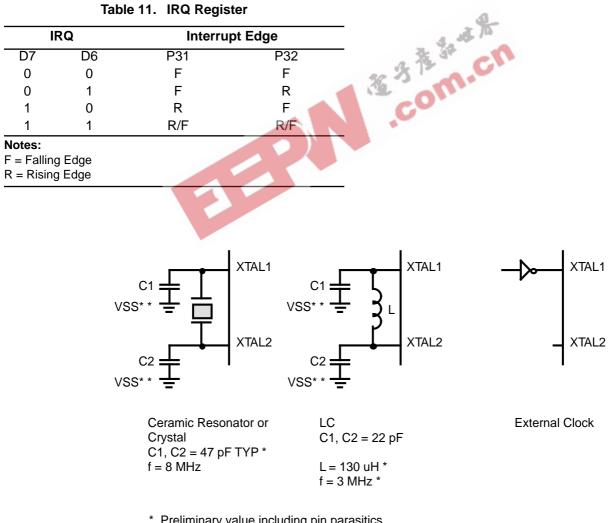

Programming bits for the Interrupt Edge Select is located in the IRQ Register (R250), bits D7 and D6. The configuration is shown in Table 11.

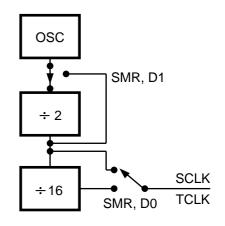

Clock. The Z8 on-chip oscillator has a high-gain, parallelresonant amplifier for connection to a crystal, LC, RC, ceramic resonator, or any suitable external clock source (XTAL1 = Input, XTAL2 = Output). The crystal should be AT cut, 16 MHz max., with a series resistance (RS) of less than or equal to 100 Ohms when clocking from 1 MHz to 16 MHz.

The crystal should be connected across XTAL1 and XTAL2 using the vendor's recommended capacitor values from each pin directly to the device Ground pin to reduce Ground noise injection into the oscillator.

Note: For better noise immunity, the capacitors should be tied directly to the device Ground pin ( $V_{ss}$ ).

\* Preliminary value including pin parasitics

\* \* Device ground pin

### Figure 21. Oscillator Configuration

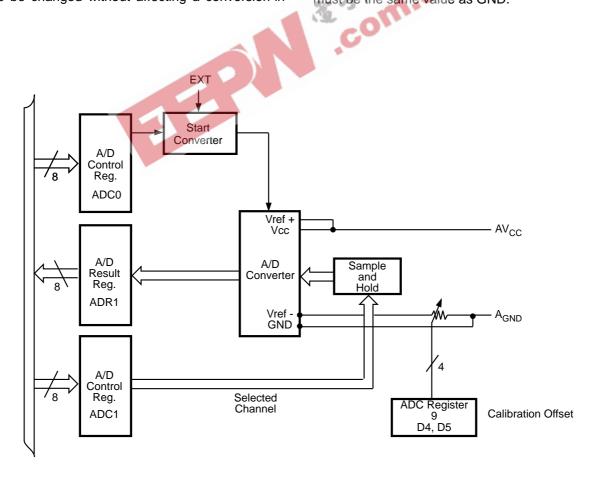

### **Analog-to-Digital Converter**

The Analog-to-Digital (ADC) is an 8-bit half flash converter that uses two reference resistor ladders for its upper 4 bits (MSBs) and lower 4 bits (LSBs) conversion. Two reference voltage pins,  $AV_{\rm cc}$  and  $A_{_{\rm GND}}\!,$  are provided for external reference voltage supplies. During the sampling period from one of the eight channel inputs, the converter is also being auto-zeroed before starting the conversion. The conversion time is dependent on the internal clock frequency. The minimum conversion time is 35 X SCLK(see Figure 22).

The ADC is controlled by the Z8<sup>®</sup> and its three registers (two Control and one Result) are mapped into the Extended Register File. A conversion can be initiated by writing to the ADC Control Register 0 after the ADC Control Register 1 is configured.

The start command is implemented in such a way as to begin a conversion at any time, if a conversion is in progress and a new start command is received, then the conversion in progress will be aborted and a new conversion will be initiated. This allows the programmed values to be changed without affecting a conversion-inprogress. The new values will take effect only after a new start command is received.

The ADC can be disabled (for low power) or enabled by a Control Register bit.

Though the ADC will function for a smaller input voltage and voltage reference, the noise and offsets remain constant over the specified electrical range. The errors of the converter will increase and the conversion time may also take slightly longer due to smaller input signals.

### ADC Calibration Offset

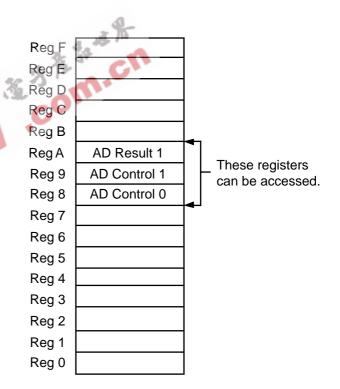

Specially matched resistors are program-enabled to allow 35.0 percent or 50 percent offset from A<sub>GND</sub>. They may selectively enable these resistors to offset the AGND by 35.0 percent (2.5V to 5V) or 50 percent (1.75V to 5V) thereby allowing the 8-bit ADC across a narrower voltage range. This will allow significant resolution improvement within the reduced voltage range.

Note: The  $AV_{cc}$  must be the same value as  $V_{cc}$  and  $A_{gND}$ must be the same value as GND.

Figure 22. ADC Architecture

ه کناره

### <u> Silæ</u>

### FUNCTIONAL DESCRIPTION (Continued)

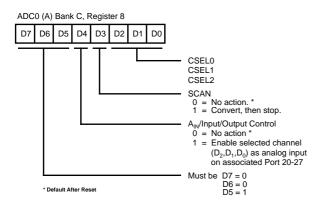

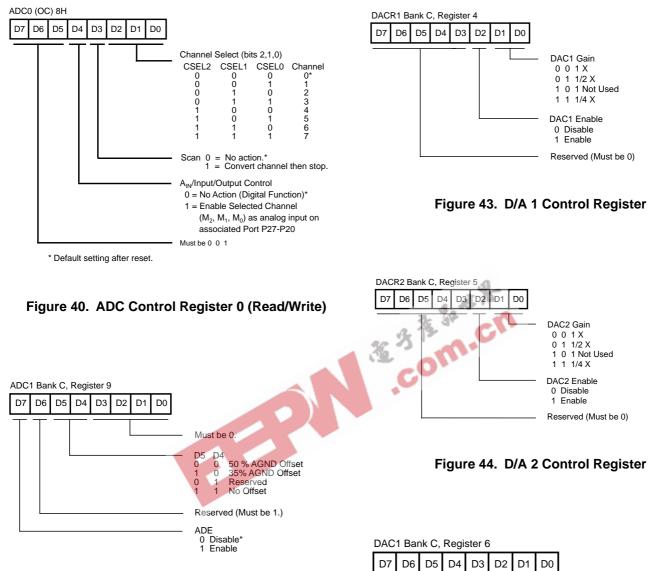

Figure 23. ADC Control Register 0 (Read/Write)

**ADE (bit 7).** A zero disables any A/D conversions or accessing any ADC registers except writing to ADE bit. A one Enables all ADC accesses. ADC result register is shown in Figure 25.

| CAN   |                   |              |          |

|-------|-------------------|--------------|----------|

| 0     | No action*        |              |          |

| 1     | Convert channe    | el then stop |          |

| annel | Select (bits 2, 1 | , 0).        |          |

| CSEL  | 2 CSEL1           | CSEL0        | Channel  |

| 0     | 0                 | 0            | 0 (P20)* |

| 0     | 0                 | 1            | 1 (P21)  |

| 0     | 1                 | 0            | 2 (P22)  |

| 0     | 1                 | 1            | 3 (P23)  |

| 1     | 0                 | 0            | 4 (P24)  |

| 1     | 0                 | 1            | 5 (P25)  |

| 1     | 1                 | 0            | 6 (P26)  |

|       |                   | 4            | 7 (P27)  |

Figure 24. ADC Control Register 1 (Read/Write)

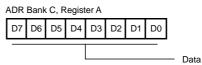

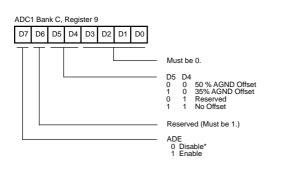

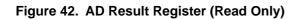

Figure 26. Bank C

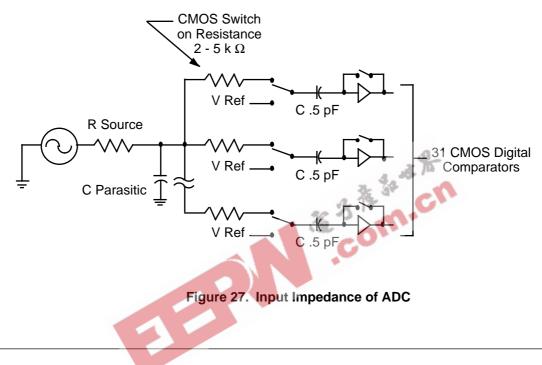

Figure 27 shows the input circuit of the ADC. When conversion starts the analog input voltage is connected to the MSB and LSB flash converter inputs as shown in the Input Impedance CKT diagram. Effectively, shunting 31 parallel internal resistance of the analog switches and simultaneously charging 31 parallel 0.5 pF capacitors, which is equivalent to seeing a 400 Ohms input impedance

in parallel with a 16 pF capacitor. Other input stray capacitance adds about 10 pF to the input load. For input source resistances up to 2 kOhms can be used under normal operating condition without any degradation of the input settling time. For larger input source resistance, longer conversion cycle time may be required to compensate the input settling time problem.

### Typical Z8 A/D Conversion Sequence

- 1. Set the register pointer to Extended Bank (C),that is, SRP #%0C instruction.

- 2. Next, set ADE flag by loading ADC1 Control Register Bank (C) Register 9, bit 7. Also, load bits 0-4 of this same register to select a  $AV_{cc}$  or  $A_{gND}$  offset value. A precision voltage divider connected to the A/D resistive ladder can offset conversion dynamic range to specified limits within the  $AV_{cc}$  and  $A_{gND}$  limits. By loading Bank (C) Register 9, bits 0-4, with the appropriate value it is possible to select from these groups:

- a. No Offset. The Converter Dynamic range is from 0V to 5.0V for AV $_{\rm cc}$  = 5.0V.

- b. 35 Percent A<sub>GND</sub> Offset. The Converter Dynamic range is 1.75V 5.0V for AV<sub>cc</sub> = 5.0V.

- c. 50 Percent A\_{\_{GND}} Offset. The Converter Dynamic range is 2.5V 5.0V for AV $_{\rm cc}$  = 5.0V.

- Select one of the eight A/D inputs for conversion by loading Bank (C) Register 8 with the desired attributes: Bits 0 - 2 select an A/D input, bits 3 and 4 select A/D conversion (or digital port I/O).

- 4. Set Bank (C) Register 8, bit 3 to enable A/D conversion. (This flag can be set concurrently with step 3.) This flag is automatically reset when the A/D conversion is completed, so a bit test can be performed to determine A/D readiness if necessary.

- 5. Read the A/D result in Bank (C) Register A. Please note that the A/D result is not valid (indeterminate) unless ADE flag (Register 9, bit 7) was previously set, otherwise A/D converter output is tri-stated.

### FUNCTIONAL DESCRIPTION (Continued)

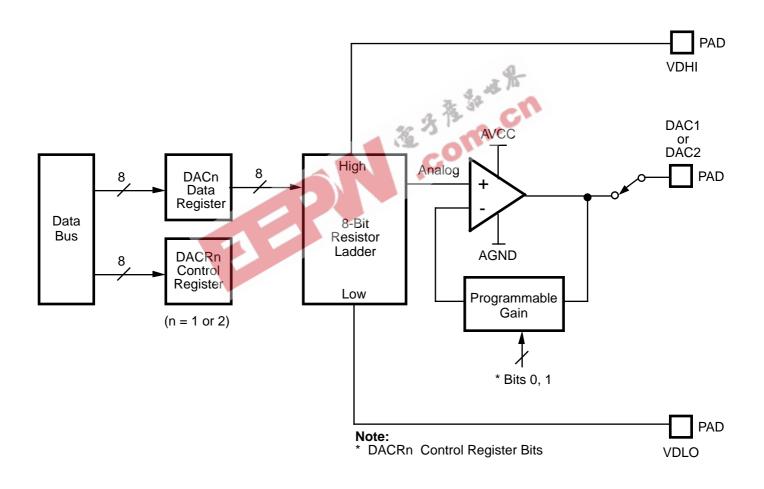

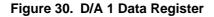

### **Digital-to-Analog Converters**

The Z86C84 has two Digital-to-Analog Converters (DACs). Each DAC is an 8-bit resistor string, with a programmable 0.25X, 0.5X, or 1X gain output buffer. The DAC output voltage settles after the internal data is latched into the DAC Data register. The top and bottom ends of the resistor ladder are register-selected to be connected to either the analog supply rails,  $AV_{cc}$  and  $A_{GND}$ , or two externally-provided reference voltages, VDHI and VDLO. External references are recommended to explicitly set the DAC output limits. Since the gain stage cannot drive to the

supply rails, VDHI and VDLO must be within ranges shown in the specifications. If either reference approaches the analog supply rails, the output will be unable to span the reference voltage range. The externally provided reference voltages should not exceed the supply voltages. The DAC outputs are latch-up protected and can drive output loads (Figure 28).

Note: The AV $_{\rm cc}$  must be the same value as  $V_{\rm cc}$  and  $A_{_{\rm GND}}$  must be the same value as GND

#### Z86C83/C84 Z8<sup>®</sup> MCU Microcontrollers

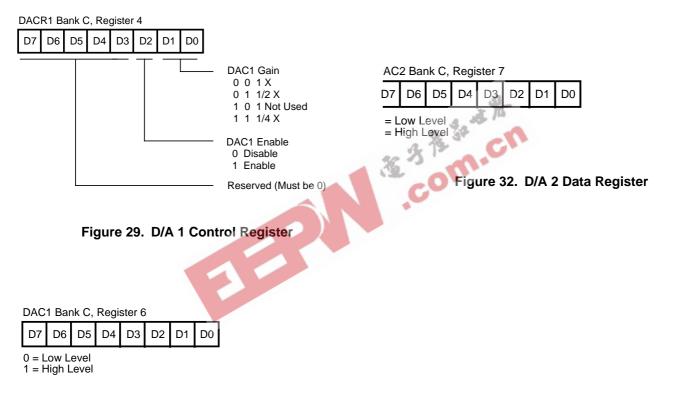

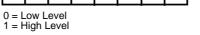

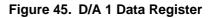

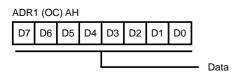

The D/A conversion for DAC1 is driven by writing 8-bit data to the DAC1 data register (Bank C, Register 06H). The D/A conversion for DAC 2 is controlled by the DAC2 data register (Bank C, Register 07H). Each DAC data register is initialized to midrange 80H on power-up.

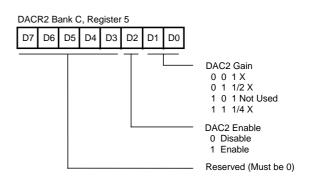

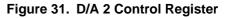

There are two DAC control registers: DACR1 (Bank C, Register 04H) for DAC1, and DACR2 (Bank C, Register 05H) for DAC2. Control register bits 0 and 1 set the DAC gain. When DAC data is 80H, the DAC output is constant for any gain setting (Figure 29 and Figure 31).

2ila

& Sira

### FUNCTIONAL DESCRIPTION (Continued)

Figure 33. Gain Control on DAC

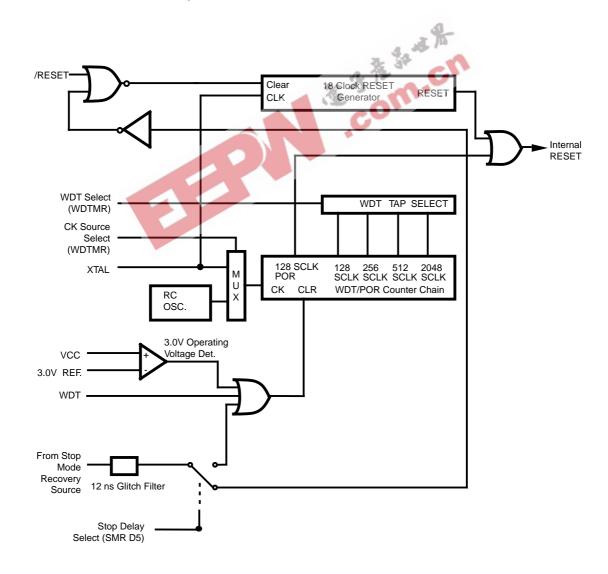

**Power-On Reset (POR).** A timer circuit clocked by a dedicated on-board RC oscillator or by the XTAL oscillator is used for the POR timer function. The POR time allows  $V_{cc}$  and the oscillator circuit to stabilize before instruction execution begins. The POR timer circuit is a one-shot timer triggered by one of three conditions:

- Power Fail to Power OK Status

- Stop-Mode Recovery (If D5 of SMR Register = 1)

- WDT Time-Out (Including from Stop Mode)