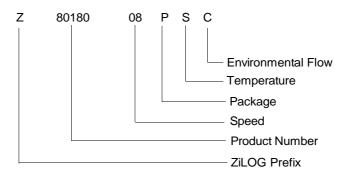

Z8018x

Family MPU

User Manual

UM005001-ZMP0400

# Z8018x **Family MPU User Manual**

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact

### **ZiLOG Worldwide Headquarters**

910 E. Hamilton Avenue Campbell, CA 95008 Telephone: 408.558.8500

Windows is a registered trademark of Microsoft Corporation.

### **Document Disclaimer**

© 2000 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

Z8018x Family

### **MANUAL OBJECTIVES**

This user manual describes the features of the Z8018x Family MPUs. This manual provides basic programming information for the Z80180/Z8S180/Z8L180. These cores and base perippheral sets are used in a large family of ZiLOG products. Below is a list of ZiLOG products that use this class of processor, along with the associated processor family. This document is also the core user manual for the following products:

| Part       | Family          |

|------------|-----------------|

| Z80180     | <b>Z8</b> 0180  |

| Z8S180     | Z8S180          |

| Z8L180     | Z8L180          |

| Z80181     | Z80180          |

| Z80182     | Z80180, Z8S180* |

| Z80S183    | Z8S180          |

| Z80185/195 | Z8S180          |

| Z80189     | Z8S180          |

<sup>\*</sup> Part number-dependant

### **Intended Audience**

This manual is written for those who program the Z8018x Family.

### **Manual Organization**

The Z8018x Family User Manual is divided into five sections, seven appendices, and an index.

### **Sections**

### **Z8018X MPU Operation**

Presents features, a general description, pins descriptions, block diagrams, registers, and details of operating modes for the Z8018x MPUs.

### **Software Architecture**

Provides instruction sets and CPU registers for the Z8018x MPUs.

### **DC** Characteristics

Presents the DC parameters and absolute maximum ratings for the Z8X180 MPUs.

### **AC Characteristics**

Presents the AC parameters for the Z8018x MPUs.

### **Timing Diagrams**

Contains timing diagrams and standard test conditions for the Z8018x MPUs.

## **Appendices**

The appendixes in this manual provide additional information applicable to the Z8018x family of ZiLOG MPUs:

- Instruction set

- Instruction summary table

- Op Code map

- Bus Control signal conditions in each machine cycle and interrupt conditions

- Operating mode summary

- Status signals

- I/O registers and ordering information

# Table of Contents

| Z80180, Z8S180, Z8L180 MPU Operation                         | 1   |

|--------------------------------------------------------------|-----|

| Features                                                     | 1   |

| General Description                                          | 1   |

| Pin Description                                              | 7   |

| Features  General Description  Pin Description  Architecture | 12  |

| Operation Modes                                              | 15  |

| CPU Timing                                                   |     |

| Wait State Generator                                         |     |

| HALT and Low Power Operation Modes                           |     |

| (Z80180-Class Processors Only)                               | 31  |

| Low Power Modes                                              |     |

| (Z8S180/Z8L180 only)                                         | 36  |

| Add-On Features                                              | 36  |

| STANDBY Mode                                                 | 37  |

| STANDBY Mode Exit wiht BUS REQUEST                           | 38  |

| STANDBY Mode EXit with External Interrupts                   | 39  |

| IDLE Mode                                                    | 40  |

| STANDBY-QUICK RECOVERY Mode                                  | 41  |

| Internal I/O Registers                                       | 41  |

| MMU Register Description                                     | 60  |

| Interrupts                                                   | 65  |

| Interrupt Acknowledge Cycle Timings                          | 82  |

| Interrupt Sources During RESET                               |     |

| Dynamic RAM Refresh Control                                  |     |

| DMA Controller (DMAC)                                        | 90  |

| Asynchronous Serial Communication Interface (ASCI)           | 115 |

## Z8018x Family MPU User Manual

|             | Baud Rate Generator                   |               |

|-------------|---------------------------------------|---------------|

|             | (Z8S180/Z8L180-Class Processors Only) | 143           |

|             | Clocked Serial I/O Port (CSI/O)       |               |

|             | CSI/O Registers Description           | 147           |

|             | Programmable Reload Timer (PRT)       | 156           |

|             | Miscellaneous                         | 172           |

| Software A  | Instruction Set                       | . <i>17</i> 3 |

|             | Instruction Set                       | 173           |

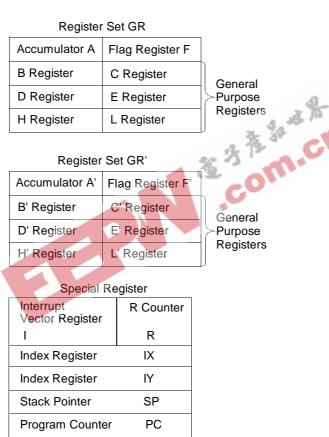

|             | CPU Registers                         | 175           |

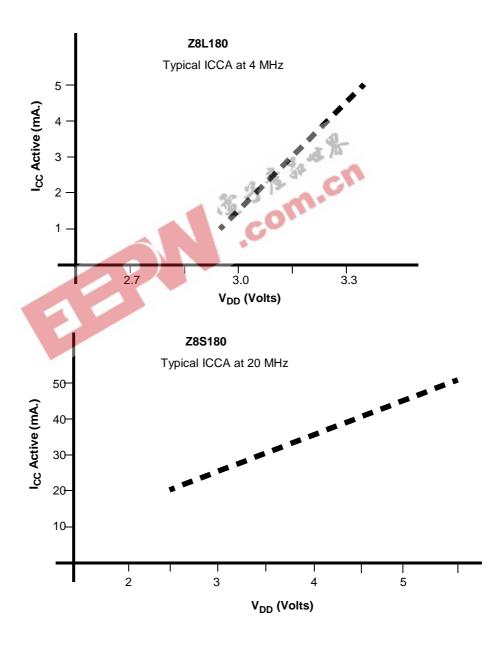

| DC Charac   | teristics                             | . 185         |

|             | Absolute Maximum Rating               | 185           |

|             | Z80180 DC Characteristics             | 186           |

|             | Z8S180 DC Characteristics             | 187           |

|             | Z8L180 DC Characteristics             | 189           |

| AC Charact  | teristics                             | . 193         |

|             | AC Characteristics—Z8S180             | 193           |

| Timing Dia  | grams                                 | . 197         |

|             | Standard Test Conditions              | 205           |

| Instruction | Set                                   | . 207         |

|             | Register                              | 207           |

|             | Bit                                   | 207           |

|             | Condition                             | 208           |

|             | Restart Address                       | 209           |

|             |                                       |               |

# Z8018x Family MPU User Manual

vii

|                  | Flag                                                   | 209 |

|------------------|--------------------------------------------------------|-----|

|                  | Miscellaneous                                          | 210 |

|                  | Data Manipulation Instructions                         | 211 |

|                  | Data Transfer Instructions                             |     |

|                  | Program and Control Instructions                       | 235 |

| Instruction      | Summary                                                | 237 |

| Op Code M        | Summary                                                | 247 |

| Bus Contro       | ol Signal Conditions                                   | 251 |

|                  | Bus and Control Signal Condition in each Machine Cycle |     |

|                  | Interrupts                                             | 279 |

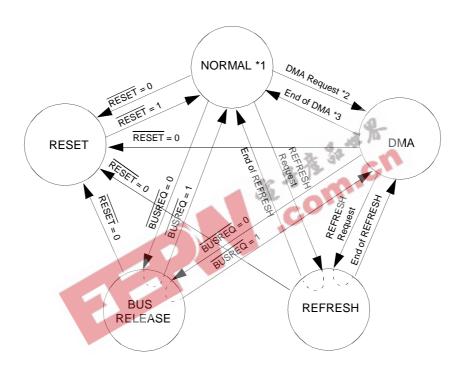

| <b>Operating</b> | Modes Summary                                          | 281 |

|                  | Request Acceptances in Each Operating Mode             | 281 |

|                  | Request Priority                                       | 282 |

|                  | Operation Mode Transition                              | 283 |

|                  | Other Operation Mode Transitions                       | 285 |

| Status Sign      | nals                                                   | 287 |

|                  | Pin Outputs in Each Operating Mode                     | 287 |

|                  | Pin Status                                             | 288 |

| I/O Registe      | ers                                                    | 293 |

|                  | Internal I/O Registers                                 | 293 |

|                  | Ordering Information                                   |     |

iv

# List of Figures

| Z80180, Z8 | S180, Z81  | L180 MPU Operation                                   |

|------------|------------|------------------------------------------------------|

|            | Figure 1.  | 64-Pin DIP                                           |

|            | Figure 2.  | 68-Pin PLCC                                          |

|            | Figure 3.  | 80-Pin QFP                                           |

|            | Figure 4.  | Z80180/Z8S180/Z8L180 Block Diagram                   |

|            | Figure 5.  | Operation Mode Control Register                      |

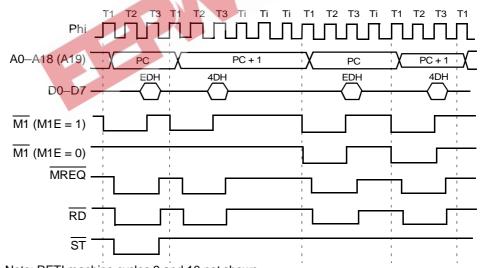

|            | Figure 6.  | M1 Temporary Enable Timing                           |

|            | Figure 7.  | I/O Read and Write Cycles with IOC = 1               |

|            |            | Timing Diagram17                                     |

|            | Figure 8.  | I/O Read and Write cycles with $IOC = 0$             |

|            |            | Timing Diagram17                                     |

|            | Figure 9.  | Op Code Fetch (without Wait State) Timing Diagram 19 |

|            | Figure 10. | Op Code Fetch (with Wait State) Timing Diagram20     |

|            | Figure 11. | Memory Read/Write (without Wait State)               |

|            |            | Timing Diagram21                                     |

|            | Figure 12. | Memory Read/Write (with Wait State)                  |

|            |            | Timing Diagram22                                     |

|            | Figure 13. | I/O Read/Write Timing Diagram                        |

|            | Figure 14. | Instruction Timing Diagram24                         |

|            | Figure 15. | RESET Timing Diagram                                 |

|            | Figure 16. | Bus Exchange Timing During Memory Read               |

|            | Figure 17. | Bus Exchange Timing During CPU Internal Operation 27 |

|            | Figure 18. | WAIT Timing Diagram28                                |

|            | Figure 19. | Memory and I/O Wait State Insertion                  |

|            |            | (DCNTL – DMA/Wait Control Register)                  |

|            | Figure 20. | HALT Timing Diagram33                                |

## Z8018x Family MPU User Manual

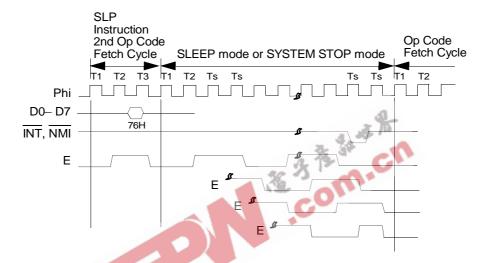

| Figure 21. | SLEEP Timing Diagram                                 |

|------------|------------------------------------------------------|

| Figure 22. | I/O Address Relocation                               |

| Figure 23. | Logical Address Mapping Examples                     |

| Figure 24. | Physical Address Transition                          |

| Figure 25. | MMU Block Diagram                                    |

| Figure 26. | I/O Address Translation                              |

| Figure 27. | Logical Memory Organization 58                       |

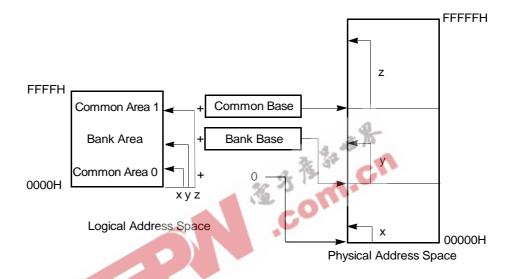

| Figure 28. | Logical Space Configuration                          |

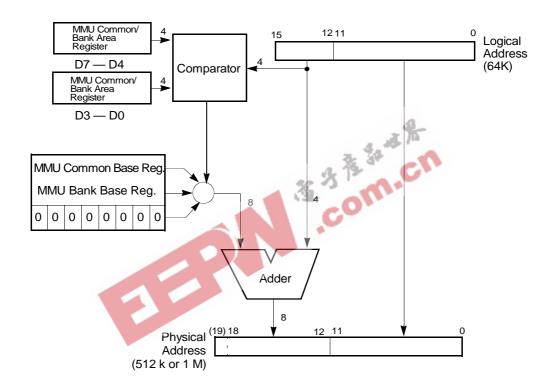

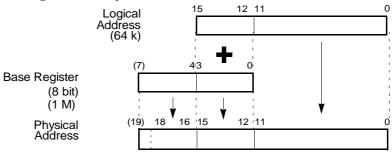

| Figure 29. | Physical Address Generation 64                       |

| Figure 30. | Physical Address Generation 2 64                     |

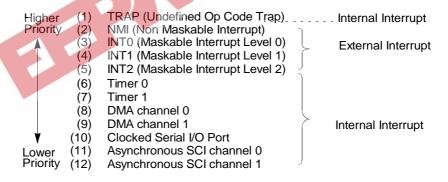

| Figure 31. | Interrupt Sources                                    |

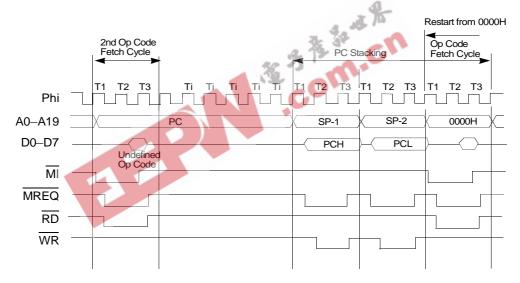

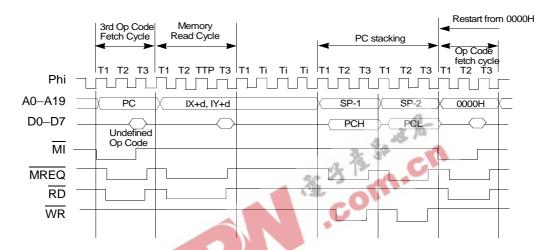

| Figure 32. | TRAP Timing Diagram -2nd Op Code Undefined 71        |

| Figure 33. | TRAP Timing - 3rd Op Code Undefined                  |

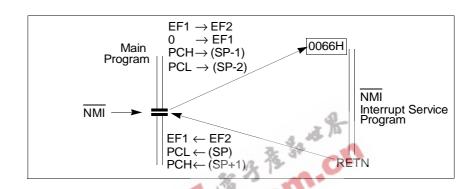

| Figure 34. | NMI Use                                              |

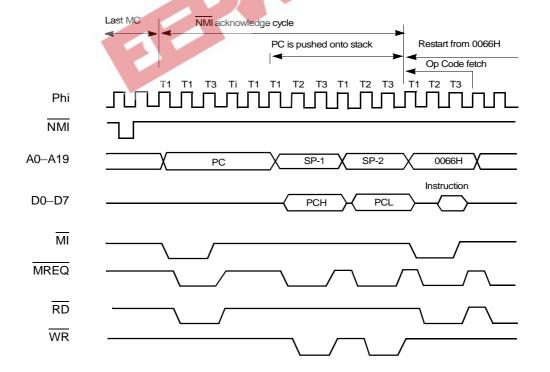

| Figure 35. | <b>NMI</b> Timing                                    |

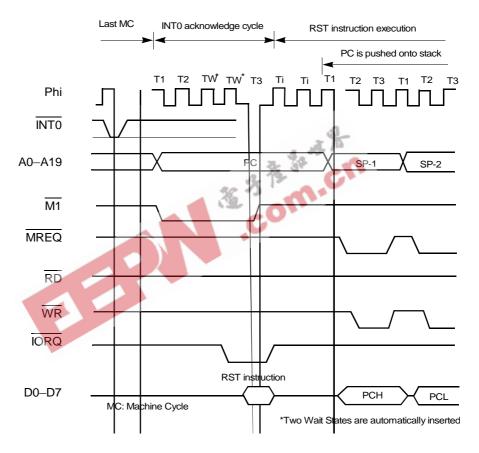

| Figure 36. | INTO Mode 0 Timing Diagram                           |

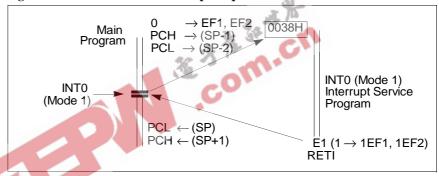

| Figure 37. | INTO Mode 1 Interrupt Sequence                       |

| Figure 38. | INTO Mode 1 Timing                                   |

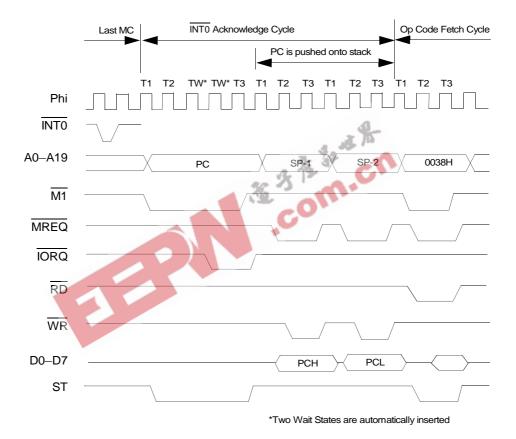

| Figure 39. | INTO Mode 2 Vector Acquisition                       |

| Figure 40. | INTO Interrupt Mode 2 Timing Diagram                 |

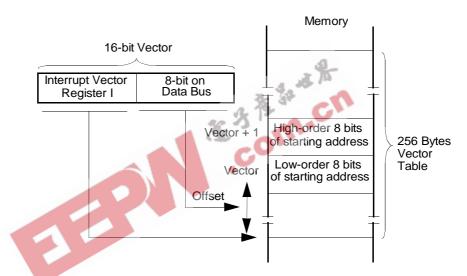

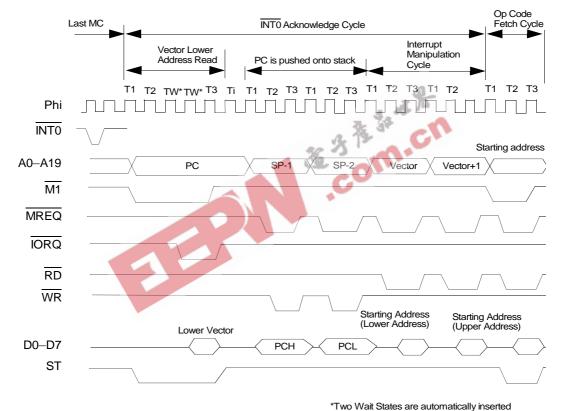

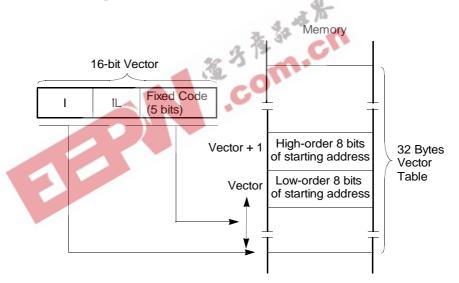

| Figure 41. | INT1, INT2 Vector Acquisition                        |

| Figure 42. | RETI Instruction Sequence                            |

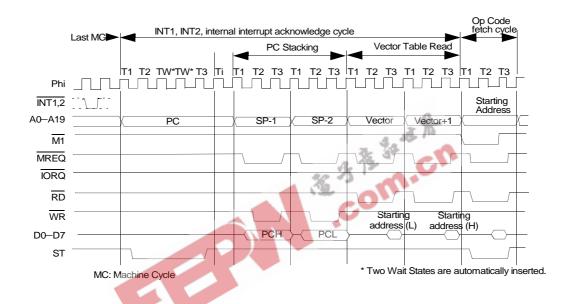

| Figure 43. | INT1, INT2 and Internal Interrupts Timing Diagram 86 |

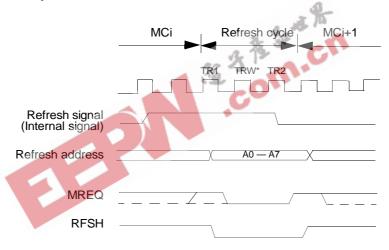

| Figure 44. | Refresh Cycle Timing Diagram 87                      |

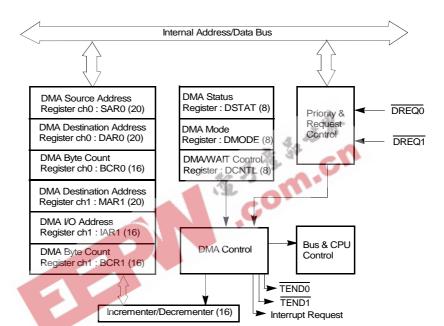

| Figure 45. | DMAC Block Diagram                                   |

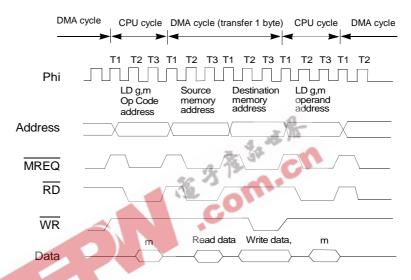

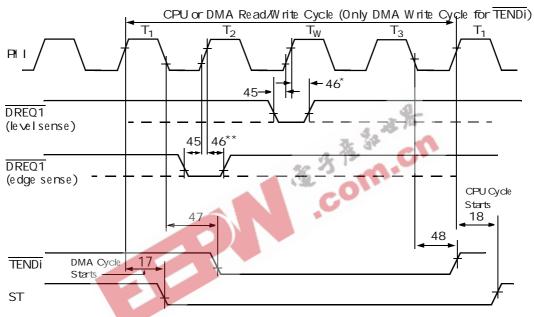

| Figure 46. | DMA Timing Diagram-CYCLE STEAL Mode 106              |

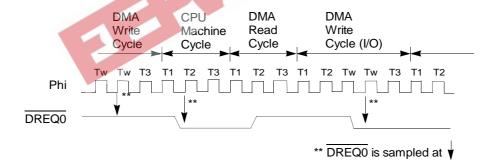

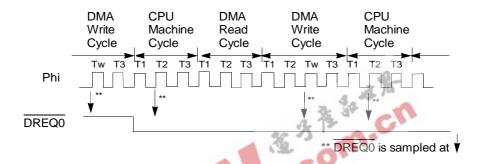

| Figure 47. | CPU Operation and DMA Operation DREQ0                |

|            | is Programmed for Level-Sense                        |

| Figure 48. | CPU Operation and DMA Operation DREQ0                |

|            | is Programmed for Edge-Sense                         |

# Z8018x Family MPU User Manual

|   | ٠ |

|---|---|

| v | ı |

| ж | ı |

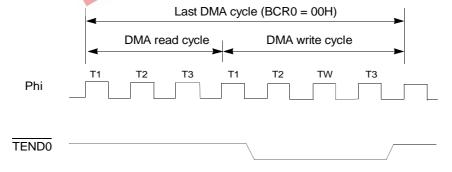

| TEND0 Output Timing Diagram                                                     |

|---------------------------------------------------------------------------------|

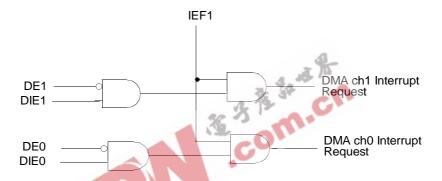

| DMA Interrupt Request Generation                                                |

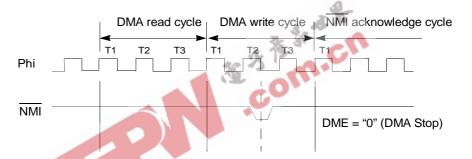

| NMI and DMA Operation Timing Diagram115                                         |

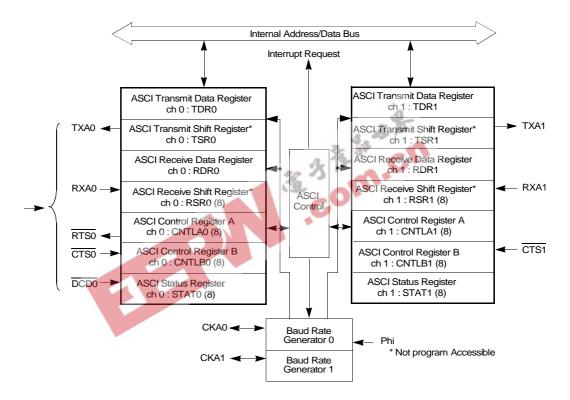

| ASCI Block Diagram                                                              |

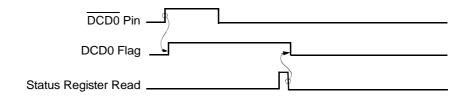

| DCD0 Timing Diagram                                                             |

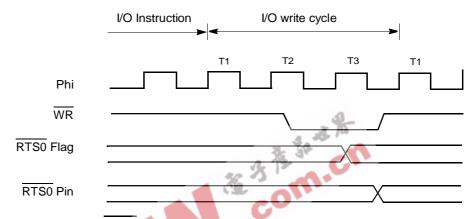

| RTS0 Timing Diagram                                                             |

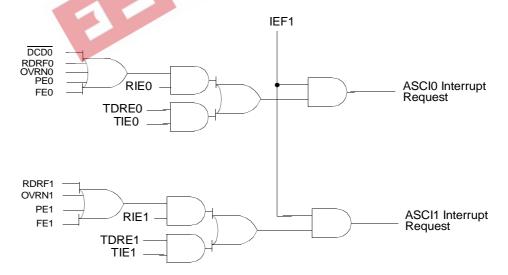

| ASCI Interrupt Request Circuit Diagram140                                       |

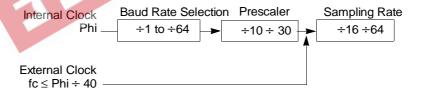

| ASCI Clock                                                                      |

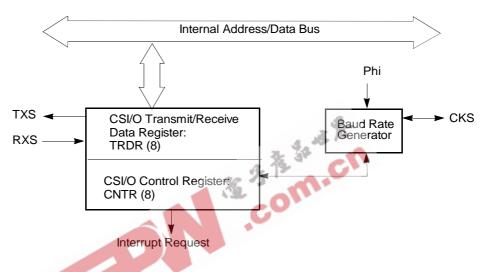

| CSI/O Block Diagram                                                             |

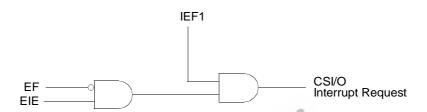

| CSI/O Interrupt Request Generation                                              |

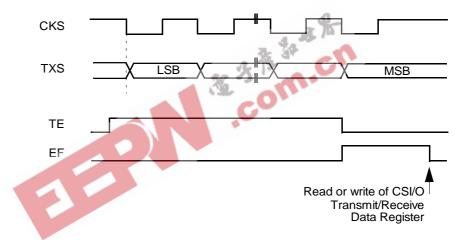

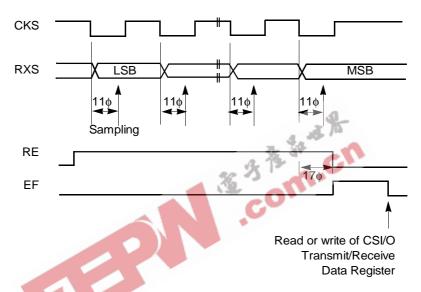

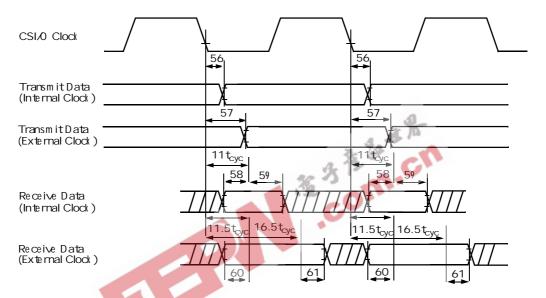

| Transmit Timing Diagram–Internal Clock153                                       |

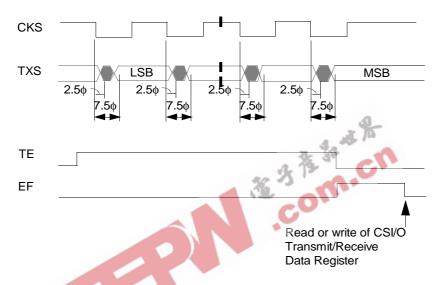

| Transmit Timing-External Clock                                                  |

| CSI/O Receive Timing–Internal Clock                                             |

| CSI/O Receive Timing–External Clock                                             |

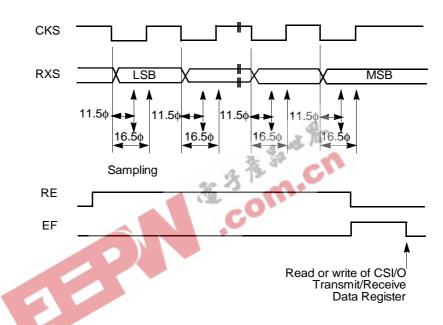

| PRT Block Diagram                                                               |

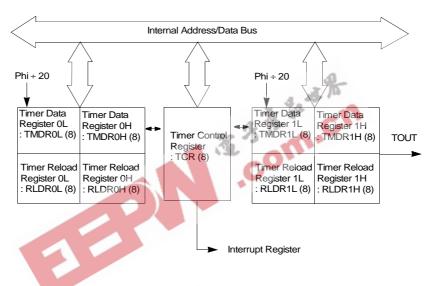

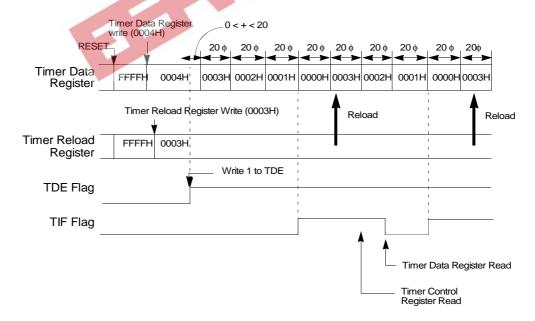

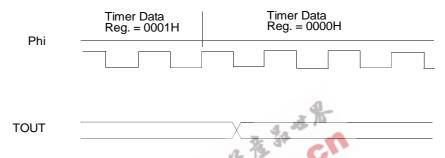

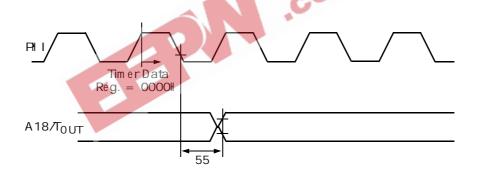

| Timer Initialization, Count Down, and Reload Timing Diagram                     |

| Timer Output Timing Diagram                                                     |

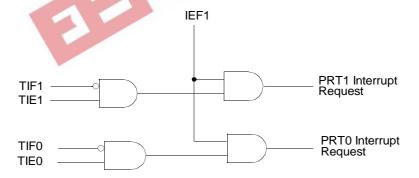

| PRT Interrupt Request Generation164                                             |

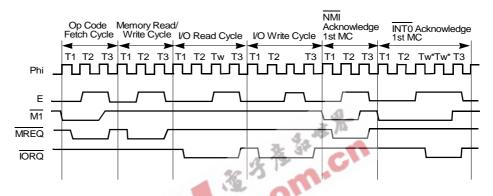

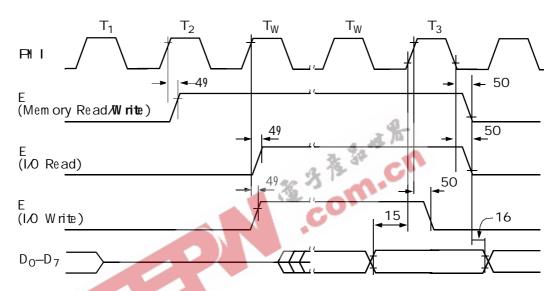

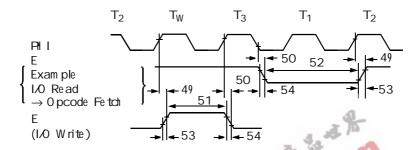

| E Clock Timing Diagram (During Read/Write Cycle and Interrupt Acknowledge Cycle |

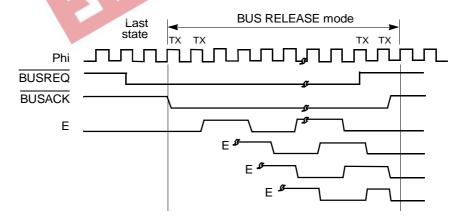

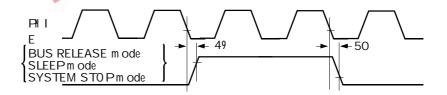

| E Clock Timing in BUS RELEASE Mode                                              |

| E Clock Timing in SLEEP Mode and SYSTEM STOP Mode                               |

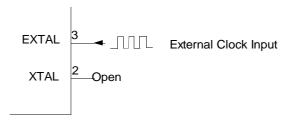

| External Clock Interface                                                        |

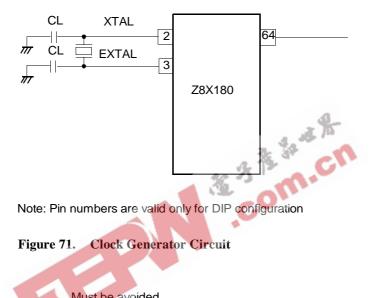

| Clock Generator Circuit                                                         |

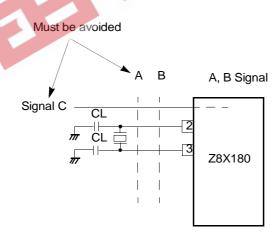

| Circuit Board Design Rules                                                      |

| Example of Board Design                                                         |

|                                                                                 |

## Z8018x Family MPU User Manual

| Software Architectur | e                                                                  |

|----------------------|--------------------------------------------------------------------|

| Figure 74.           | CPU Register Configurations                                        |

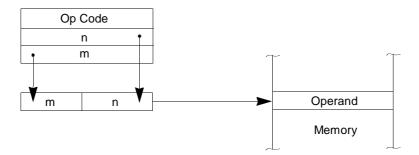

| Figure 75.           | Register Direct — Bit Field Definitions 181                        |

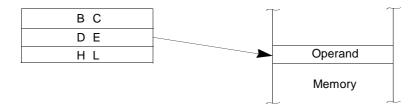

| Figure 76.           | Register Indirect Addressing                                       |

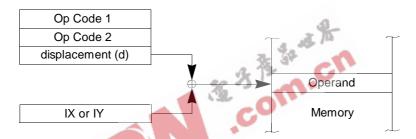

| Figure 77.           | Indexed Addressing                                                 |

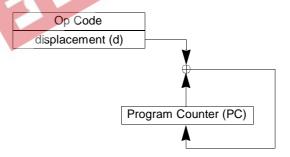

| Figure 78.           | Indexed Addressing182Extended Addressing182                        |

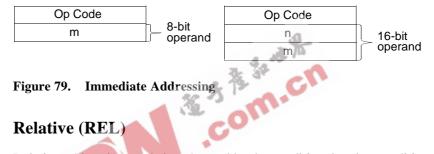

| Figure 79.           | Immediate Addressing                                               |

| Figure 80.           | Immediate Addressing                                               |

| Timing Diagrams      |                                                                    |

| Figure 81.           | AC Timing Diagram 1                                                |

|                      | AC Timing Diagram 2                                                |

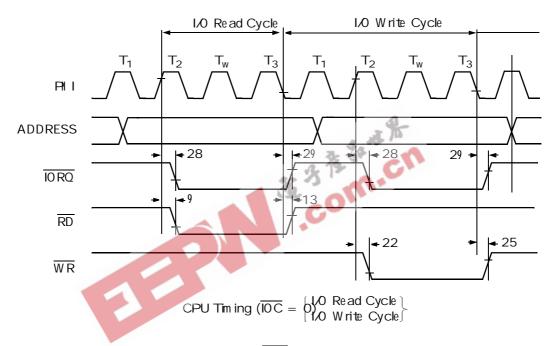

| Figure 83.           | CPU Timing (IOC = 0) (I/O Read Cycle, I/O Write Cycle)             |

| Figure 84.           | DMA Control Signals                                                |

| Figure 85.           | E Clock Timing (Memory R/W Cycle) (I/O R/W Cycle) 201              |

| Figure 86.           | E Clock Timing (BUS RELEASE Mode, SLEEP Mode, and SYSTEM STOP Mode |

| Figure 87.           | EClockTiming(MinimumTimingExampleofPWELandPWEH) 202                |

| Figure 88.           | Timer Output Timing                                                |

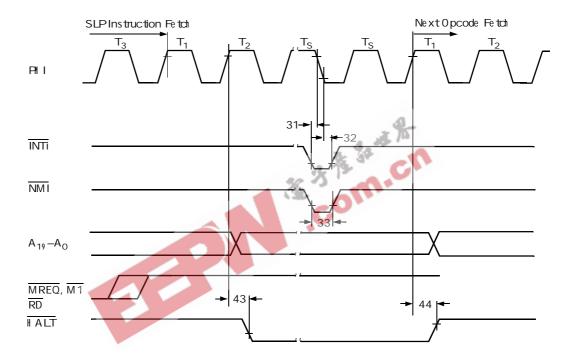

| Figure 89.           | SLP Execution Cycle Timing Diagram                                 |

| Figure 90.           | CSI/O Receive/Transmit Timing Diagram 204                          |

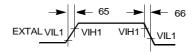

| Figure 91.           | External Clock Rise Time and Fall Time 204                         |

| Figure 92.           | Input Rise Time and Fall Time (Except EXTAL, RESET)                |

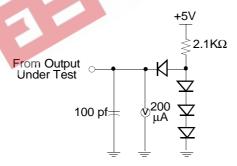

| Figure 93.           | Test Setup                                                         |

|                      |                                                                    |

# Z8018x Family MPU User Manual

viv

# List of Tables

| Z80180, Z8 | S180, Z81 | L180 MPU Operation1                                 |

|------------|-----------|-----------------------------------------------------|

|            | Table 1.  | Status Summary                                      |

|            | Table 2.  | Multiplexed Pin Descriptions12                      |

|            | Table 3.  | Memory Wait States                                  |

|            | Table 4.  | Wait State Insertion                                |

|            | Table 5.  | Power-Down Modes                                    |

|            |           | (Z8S180/Z8L180-Class Processor Only)37              |

|            | Table 6.  | I/O Address Map for Z80180-Class Processors Only 44 |

|            | Table 7.  | I/O Address Map                                     |

|            |           | (Z8S180/Z8L180-Class Processors Only)               |

|            | Table 8.  | State of IEF1 and IEF269                            |

|            | Table 9.  | Vector Table82                                      |

|            | Table 10. | RETI Control Signal States                          |

|            | Table 11. | DRAM Refresh Intervals89                            |

|            | Table 12. | Channel 0 Destination                               |

|            | Table 13. | Channel 0 Source99                                  |

|            | Table 14. | Transfer Mode Combinations                          |

|            | Table 15. | Channel 1 Transfer Mode                             |

|            | Table 16. | DMA Transfer Request                                |

|            | Table 17. | Data Formats                                        |

|            | Table 18. | Divide Ratio                                        |

|            | Table 19. | ASCI Baud Rate Selection                            |

|            | Table 20. | Clock Mode Bit Values                               |

|            | Table 21. | 2^ss Values                                         |

|            | Table 22  | CSI/O Raud Rate Selection 150                       |

## Z8018x Family MPU User Manual

| v | ١, |

|---|----|

| Л | v  |

|   |    |

| Т             | able 23.  | Timer Output Control1                       | 63        |

|---------------|-----------|---------------------------------------------|-----------|

| Т             | able 24.  | E Clock Timing in Each Condition            | 66        |

| Т             | able 25.  | Z8X180 Operating Frequencies                | 69        |

| Software Arci | hitectur  | e                                           | 73        |

|               | able 26.  | Instruction Set Summary                     |           |

| DC Character  | ristics . |                                             | 85        |

|               | able 27.  | Absolute Maximum Rating                     |           |

| Т             | able 28.  | Z80180 DC Characteristics                   |           |

| Т             | able 29.  | Z8S180 DC Characteristics                   | 87        |

| Т             | able 30.  | Z8L180 DC Characteristics                   | 89        |

| AC Character  | ristics . |                                             | 93        |

| Т             | able 31.  | Z8S180 AC Characteristics                   | 93        |

| Instruction S | et        |                                             | <i>97</i> |

| Т             | able 32.  | Register Values                             | 07        |

| Т             | able 33.  | Bit Values                                  | 208       |

| Т             | able 34.  | Instruction Values                          | :08       |

| Т             | able 35.  | Address Values                              | :09       |

| Т             | able 36.  | Flag Conditions                             | :09       |

| Т             | able 37.  | Operations Mnemonics                        | 10        |

| Т             | able 38.  | Arithmetic and Logical Instructions (8-bit) | 11        |

| Т             | able 39.  | Rotate and Shift Instructions               | 16        |

| Т             | able 40.  | Arithmetic Instructions (16-bit)            |           |

| Т             | able 41.  | 8-Bit Load                                  | :22       |

| Т             | able 42.  | 16-Bit Load                                 | 23        |

## Z8018x Family MPU User Manual

| Block Transfer                                         |

|--------------------------------------------------------|

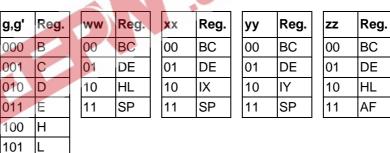

| Stock and Exchange                                     |

| Program Control Instructions                           |

| I/O Instructions                                       |

| Special Control Instructions                           |

|                                                        |

| 1st Op Code Map Instruction Format: XX 247             |

| 2nd Op Code Map Instruction Format: CB XX 249          |

| 2nd Op Code Map Instruction Format: ED XX 250          |

| Conditions251                                          |

| Bus and Control Signal Condition in Each Machine Cycle |

| Interrupts                                             |

| mmary                                                  |

| Request Acceptances in Each Operating Mode 281         |

| The Z80180 Types of Requests                           |

|                                                        |

| Pin Outputs in Each Operating Mode                     |

| Pin Status During RESET and LOW POWER OPERATION Modes  |

|                                                        |

| Internal I/O Registers                                 |

|                                                        |

ΧV

## Z80180, Z8S180, Z8L180 MPU Operation

### **FEATURES**

- Operating Frequency to 33 MHz

- On-Chip MMU Supports Extended Address Space

- Two DMA Channels

- On-Chip Wait State Generators

- Two Universal Asynchronous Receiver/Transmitter (UART) Channels

- Two 16-Bit Timer Channels

- On-Chip Interrupt Controller

- On-Chip Clock Oscillator/Generator

- Clocked Serial I/O Port

- Code Compatible with ZiLOG Z80 CPU

- Extended Instructions

### **GENERAL DESCRIPTION**

Based on a microcoded execution unit and an advanced CMOS manufacturing technology, the Z80180, Z8S180, Z8L180 (Z8X180) is an 8-bit MPU which provides the benefits of reduced system costs and low power operation while offering higher performance and maintaining compatibility with a large base of industry standard software written around the ZiLOG Z8X CPU.

Higher performance is obtained by virtue of higher operating frequencies, reduced instruction execution times, an enhanced instruction set, and an

on-chip memory management unit (MMU) with the capability of addressing up to 1 MB of memory.

Reduced system costs are obtained by incorporating several key system functions on-chip with the CPU. These key functions include I/O devices such as DMA, UART, and timer channels. Also included on-chip are several *glue* functions such as dynamic RAM refresh control, wait state generators, clock oscillator, and interrupt controller.

Not only does the Z8X180 consume a low amount of power during normal operation, but processors with Z8S180 and Z8L180 class processors also provides two operating modes that are designed to drastically reduce the power consumption even further. The SLEEP mode reduces power by placing the CPU into a *stopped* state, thereby consuming less current, while the on-chip I/O device is still operating. The SYSTEM STOP mode places both the CPU and the on-chip peripherals into a *stopped* state, thereby reducing power consumption even further.

When combined with other CMOS VLSI devices and memories, the Z8X180 provides an excellent solution to system applications requiring high performance, and low power operation.

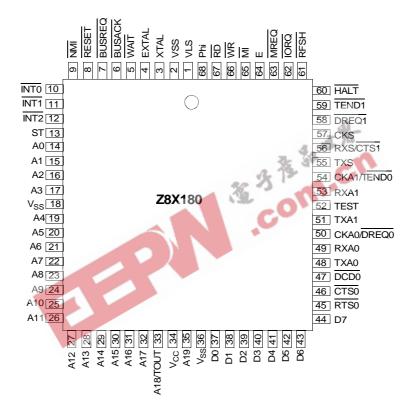

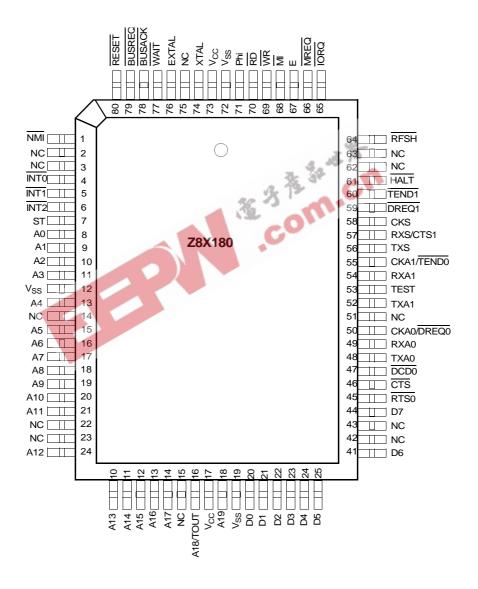

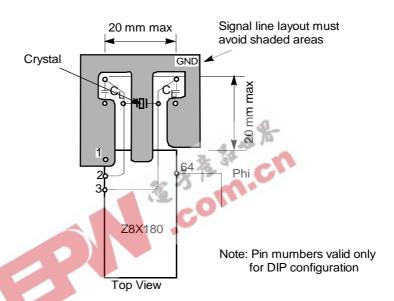

Figures 1 through 3 illustrate the three pin packages in the Z8X180 MPU family:

- 64-Pin Dual In-line Package (DIP), Figure 1

- 68-Pin Plastic Leaded Chip Carrier (PLCC), Figure 2

- 80-Pin Quad Flat Pack (QFP), Figure 3

Pin out package descriptions for other Z8X180-based products are covered in their respective product specifications.

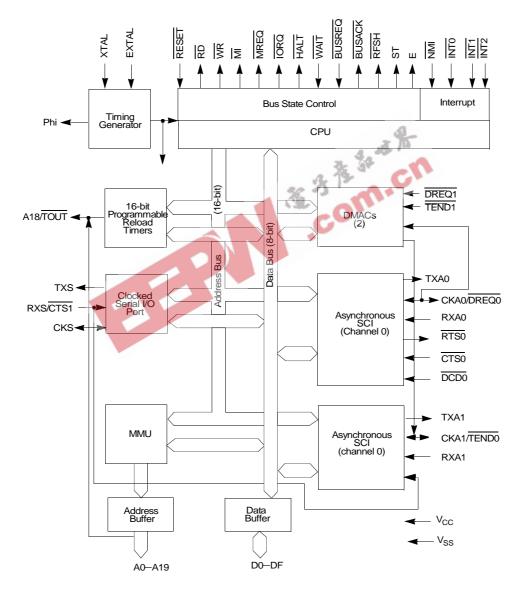

Figure 4 depicts the block diagram that is shared throughout all configurations of the Z8X180.

Figure 1. 64-Pin DIP

Figure 2. 68-Pin PLCC

Figure 3. 80-Pin QFP

# Z 8018x Family M PU User M anual

Figure 4. Z80180/Z8S180/Z8L180 Block Diagram

### PIN DESCRIPTION

**A0–A19.** Address Bus (Output, Active High, 3-state). A0–A19 form a 20-bit address bus. The Address Bus provides the address for memory data bus exchanges, up to 1 MB, and I/O data bus exchanges, up to 64K. The address bus enters a high impedance state during RESET and external bus acknowledge cycles. Address line A18 is multiplexed with the output of PRT channel 1 (TOUT, selected as address output on RESET) and address line A19 is not available in DIP versions of the Z8X180.

BUSACK. Bus Acknowledge (Output, Active Low). BUSACK indicates that the requesting device, the MPU address and data bus, and some control signals, have entered their high impedance state.

BUSREQ. Bus Request (Input, Active Low). This input is used by external devices (such as DMA controllers) to request access to the system bus. This request has a higher priority than NMI and is always recognized at the end of the current machine cycle. This signal stops the CPU from executing further instructions and places the address and data buses, and other control signals, into the high impedance state.

**CKA0, CKA1.** Asynchronous Clock 0 and 1 (Bidirectional, Active High). These pins are the transmit and receive clocks for the ASCI channels. CKA0, is multiplexed with  $\overline{\text{DREQ0}}$  and CKA1 is multiplexed with  $\overline{\text{TEND0}}$ .

**CKS.** *Serial Clock (Bidirectional, Active High)*. This line is the clock for the CSIO channel.

**CLOCK (PHI).** System Clock (Output, Active High). The output is used as a reference clock for the MPU and the external system. The frequency of this output is equal to one-half that of the crystal or input clock frequency.

**CTS0, CTS1.** *Clear to Send 0 and 1 (Inputs, Active Low)*. These lines are modem control signals for the ASCI channels. CTS1 is multiplexed with RXS.

**D0–D7.** *Data Bus (Bidirectional, Active High, 3-state).* D0-D7 constitute an 8-bit bidirectional data bus, used for the transfer of information to and from I/O and memory devices. The data bus enters the high impedance state during RESET and external bus acknowledge cycles.

**DCD0.** *Data Carrier Detect 0 (Input, Active Low)*. This input is a programmable modem control signal for ASCI channel 0.

**DREQ0, DREQ1.** *DMA Request 0 and 1 (Input, Active Low)*. DREQ is used to request a DMA transfer from one of the on-chip DMA channels. The DMA channels monitor these inputs to determine when an external device is ready for a read or write operation. These inputs can be programmed to be either level- or edge-sensed. DREQ0 is multiplexed with CKA0.

**E.** Enable Clock (Output, Active High). Synchronous machine cycle clock output during bus transactions.

**EXTAL.** *External Clock/Crystal (Input, Active High)*. Crystal oscillator connection. An external clock can be input to the Z8X180 on this pin when a crystal is not used. This input is Schmitt-triggered.

HALT. Halt/Sleep Status (Output, Active Low). This output is asserted after the CPU has executed either the HALT or SLP instruction, and is waiting for either non-maskable or maskable interrupt before operation can resume. HALT is also used with the M1 and ST signals to decode status of the CPU machine cycle.

**INT0.** *Maskable Interrupt Request 0 (Input, Active Low).* This signal is generated by external I/O devices. The CPU honors this request at the end of the current instruction cycle as long as the NMI and BUSREQ signals are inactive. The CPU acknowledges this interrupt request with an interrupt acknowledge cycle. During this cycle, both the M1 and IORQ signals become Active.

**INT1, INT2**. *Maskable Interrupt Requests 1 and 2 (Inputs, Active Low)*. This signal is generated by external I/O devices. The CPU honors these requests at the end of the current instruction cycle as long as the NMI,

BUSREQ, and INTO signals are inactive. The CPU acknowledges these interrupt requests with an interrupt acknowledge cycle. Unlike the acknowledgment for INTO, during this cycle neither the M1 or IORQ signals become Active.

**IORQ.** *I/O Request (Output, Active Low, 3-state)*. IORQ indicates that the address bus contains a valid I/O address for an I/O read or I/O write operation. IORQ is also generated, along with M1, during the acknowledgment of the INTO input signal to indicate that an interrupt response vector can be placed onto the data bus. This signal is analogous to the IOE signal of the Z64180.

M1. Machine Cycle 1 (Output, Active Low). Together with MREQ, M1 indicates that the current cycle is the Op Code fetch cycle of an instruction execution. Together with IORQ, M1 indicates that the current cycle is for an interrupt acknowledge. It is also used with the HALT and ST signal to decode status of the CPU machine cycle. This signal is analogous to the LIR signal of the Z64180.

MREQ. Memory Request (Output, Active Low, 3-state). MREQ indicates that the address bus holds a valid address for a memory read or memory write operation. This signal is analogous to the ME signal of the Z64180.

**NMI.** *Non-maskable Interrupt (Input, negative edge triggered).* NMI has a higher priority than  $\overline{\text{INT}}$  and is always recognized at the end of an instruction, regardless of the state of the interrupt enable flip-flops. This signal forces CPU execution to continue at location 0066H.

**RD.** Read (Output active Low, 3-state).  $\overline{\text{RD}}$  indicates that the CPU wants to read data from memory or an I/O device. The addressed I/O or memory device must use this signal to gate data onto the CPU data bus.

**RFSH.** Refresh (Output, Active Low). Together with MREQ, RFSH indicates that the current CPU machine cycle and the contents of the address bus must be used for refresh of dynamic memories. The low order 8 bits of the address bus (A7–A0) contain the refresh address.

This signal is analogous to the  $\overline{REF}$  signal of the Z64180.

**RTS0.** Request to Send 0 (Output, Active Low). This output is a programmable modem control signal for ASCI channel 0.

**RXA0, RXA1.** *Receive Data 0 and 1 (Inputs, Active High).* These signals are the receive data to the ASCI channels.

**RXS.** Clocked Serial Receive Data (Input, Active High). This line is the receiver data for the CSIO channel. RXS is multiplexed with the CTS1 signal for ASCI channel 1.

ST. Status (Output, Active High). This signal is used with the M1 and HALT output to decode the status of the CPU machine cycle. Table 1 provides status summary.

Table 1. Status Summary

| ST | HALT  | M1 | Operation                                                |

|----|-------|----|----------------------------------------------------------|

| 0  | 1     | 0  | CPU operation (1st Op Code fetch)                        |

| 1  | 1     | 0  | CPU operation (2nd Op Code and 3rd Op Code fetch)        |

| 1  | 1     | 1  | CPU operation (MC <sup>2</sup> except for Op Code fetch) |

| 0  | $X^1$ | 1  | DMA operation                                            |

| 0  | 0     | 0  | HALT mode                                                |

| 1  | 0     | 1  | SLEEP mode (including SYSTEM STOP mode)                  |

|    |       |    |                                                          |

- 1. X = Don't care

- 2. MC = Machine cycle

**TEND0, TEND1.** *Transfer End 0 and 1 (Outputs, Active Low)*. This output is asserted active during the last write cycle of a DMA operation. It is used to indicate the end of the block transfer. TEND0 in multiplexed with CKA1.

**TEST.** *Test* (*Output*, *not on DIP version*). This pin is for test and must be left open.

**TOUT.** *Timer Out (Output, Active High).* TOUT is the pulse output from PRT channel 1. This line is multiplexed with A18 of the address bus.

**TXA0, TXA1.** *Transmit Data 0 and 1 (Outputs, Active High).* These signals are the transmitted data from the ASCI channels. Transmitted data changes are with respect to the falling edge of the transmit clock.

**TXS.** Clocked Serial Transmit Data (Output, Active High). This line is the transmitted data from the CSIO channel.

WAIT. Wait (Input; Active Low). WAIT indicates to the CPU that the addressed memory or I/O devices are not ready for a data transfer. This input is used to induce additional clock cycles into the current machine cycle. The WAIT input is sampled on the falling edge of T2 (and subsequent Wait States). If the input is sampled Low, then additional Wait States are inserted until the WAIT input is sampled High, at which time execution continues.

WR. Write (Output, Active Low, 3-state). WR indicates that the CPU data bus holds valid data to be stored at the addressed I/O or memory location.

**XTAL.** Crystal (Input, Active High). Crystal oscillator connection. This pin must be left open if an external clock is used instead of a crystal. The oscillator input is not a TTL level (reference DC characteristics).

Multiplexed pins are described in Table 2.

**Table 2.** Multiplexed Pin Descriptions

| Multiplexed<br>Pins | Descriptions                                                                                                                                                                                                               |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A18/TOUT            | During RESET, this pin is initialized as A18 pin. If either TOC1 or TOC0 bit of the Timer Control Register (TCR) is set to 1, TOUT function is selected. If TOC1 and TOC0 bits are cleared to 0, A18 function is selected. |

| CKA0/DREQ0          | During RESET, this pin is initialized as CKA <sub>0</sub> pin. If either <u>DM1</u> or <u>SM1</u> in DMA Mode Register (DMODE) is set to 1, <u>DREQ0</u> function is always selected.                                      |

| CKA1/TEND0          | During RESET, this pin is initialized as CKA1 pin. If CKA1D bit in ASCI control register ch 1 (CNTLA1) is set to 1, TEND0 function is selected. If CKA1D bit is set to 0, CKA1 function is selected.                       |

| RXS/CTS1            | During RESET, this pin is initialized as RXS pin. If CTS1E bit in ASCI status register ch 1 (STAT1) is set to 1, CTS1 function is selected. If CTS1E bit is 0, RXS function is selected.                                   |

### **ARCHITECTURE**

The Z8X180 combines a high performance CPU core with a variety of system and I/O resources useful in a broad range of applications. The CPU core consists of five functional blocks: clock generator, bus state controller (including dynamic memory refresh), interrupt controller, memory management unit (MMU), and the central processing unit (CPU). The integrated I/O resources make up the remaining four functional blocks:

- Direct Memory Access (DMA) Control (2 channels)

- Asynchronous Serial Communications Interface (ASCI, 2 channels),

- Programmable Reload Timers (PRT, 2 channels)

- Clock Serial I/O (CSIO) channel.

Other Z8X180 family members (such as Z80183, Z80S183, Z80S185/195) feature, in addition to these blocks, additional peripherals and are covered in their associated Product Specification

### **Clock Generator**

This logic generates the system clock from either an external crystal or clock input. The external clock is divided by two and provided to both internal and external devices.

### **Bus State Controller**

This logic performs all of the status and bus control activity associated with both the CPU and some on-chip peripherals. This includes Wait State timing, RESET cycles, DRAM refresh, and DMA bus exchanges.

### **Interrupt Controller**

This block monitors and prioritizes the variety of internal and external interrupts and traps to provide the correct responses from the CPU. To remain compatible with the Z80 CPU, three different interrupt modes are supported.

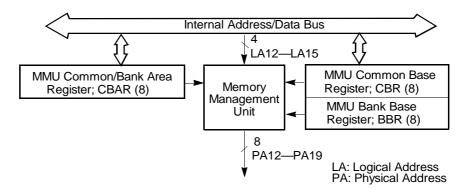

### **Memory Management Unit**

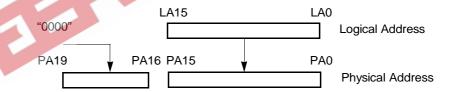

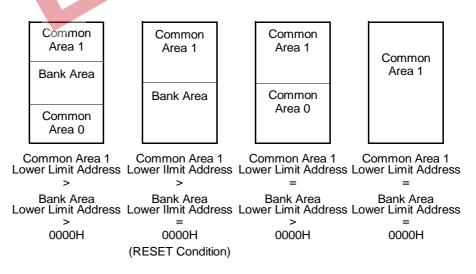

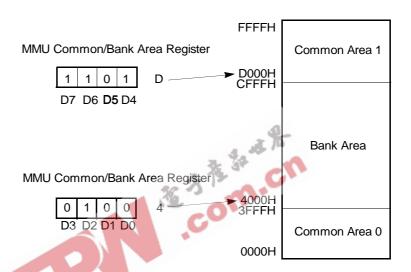

The MMU allows the user to map the memory used by the CPU (logically only 64K) into the 1MB addressing range supported by the Z8X180. The organization of the MMU object code features compatibility with the Z80 CPU while offering access to an extended memory space. This capability is accomplished by using an effective *common area - banked area* scheme.

### **Central Processing Unit**

The CPU is microcoded to provide a core that is object code compatible with the Z80 CPU. It also provides a superset of the Z80 instruction set, including 8-bit multiply and divide. This core has been enhanced to allow many of the instructions to execute in fewer clock cycles.

### **DMA Controller**

The DMA controller provides high speed transfers between memory and I/O devices. Transfer operations supported are memory-to-memory, memory to/from I/O and I/O to I/O. Transfer modes supported are REQUEST, BURST, and CYCLE STEAL. DMA transfers can access the full 1MB addressing range with a block length up to 64KB, and can cross over 64K boundaries.

### **Asynchronous Serial Communications Interface (ASCI)**

The ASCI logic provides two individual full-duplex UARTs. Each channel includes a programmable baud rate generator and modem control signals. The ASCI channels can also support a multiprocessor communications format.

### **Programmable Reload Timer (PRT)**

This logic consists of two separate channels, each containing a 16-bit counter (timer) and count reload register. The time base for the counters is derived from the system clock (divided by 20) before reaching the counter. PRT channel 1 provides an optional output to allow for waveform generation.

### Clocked Serial I/O (CSIO)

The CSIO channel provides a half-duplex serial transmitter and receiver. This channel can be used for simple high-speed data connection to another microprocessor or microcomputer.

### **OPERATION MODES**

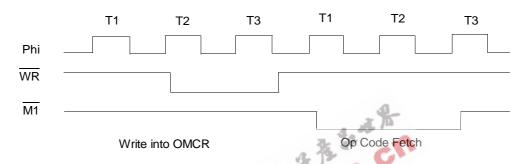

The Z8X180 can be configured to operate like the Hitachi HD64180. This functionality is accomplished by allowing user control over the  $\overline{M1}$ , IORQ, WR, and RD signals. The Operation Mode Control Register (OMCR), illustrated in Figure 5, determines the  $\overline{\text{M1}}$  options, the timing of the  $\overline{IORQ}$ ,  $\overline{RD}$ , and  $\overline{WR}$  signals, and the RETI operation.

### Operation Mode Control Register

| Bit                                                          | 7   | 6    | 5   | 4 3 7 | C        | 0 |  |  |  |  |

|--------------------------------------------------------------|-----|------|-----|-------|----------|---|--|--|--|--|

| Bit/Field                                                    | M1E | M1TE | IOC | 132   | Reserved |   |  |  |  |  |

| R/W                                                          | R/W | W    | R/W | C     | _        |   |  |  |  |  |

| Reset                                                        | 1   | 1    | 1   |       | _        |   |  |  |  |  |

| Note: R = Read W = Write X = Indeterminate? = Not Applicable |     |      |     |       |          |   |  |  |  |  |

**Operation Mode Control Register**

M1E (M1\_Enable): This bit controls the  $\overline{\text{M1}}$  output and is set to a 1 during

When M1E is 1, the  $\overline{\text{M1}}$  output is asserted Low during the Op Code fetch cycle, the INTO acknowledge cycle, and the first machine cycle of the NMI acknowledge. This action also causes the M1 signal to be Active during both fetches of the RETI instruction sequence, and may cause corruption of the external interrupt daisy chain. Therefore, this bit must be 0 for the Z8X180. When M1E is 0 the  $\overline{\text{M1}}$  output is normally inactive and asserted <u>Low</u> only during the refetch of the RETI instruction sequence and the INTO acknowledge cycle (Figure 6).

Figure 6. M1 Temporary Enable Timing

M1TE (M1 Temporary Enable): This bit controls the temporary assertion of the M1 signal. It is always read back as a 1 and is set to 1 during RESET. This function is used to *arm* the internal interrupt structure of the Z80PIO. When a control word is written to the Z80PIO to enable interrupts, no enable actually takes place until the PIO sees an active M1 signal. When M1TE is 1, there is no change in the operation of the M1 signal and M1E controls its function. When M1TE is 0, the M1 output is asserted during the next Op Code fetch cycle regardless of the state programmed into the M1E bit. This situation is only momentary (one time) and the user need not reprogram a 1 to disable the function (See Figure 7).

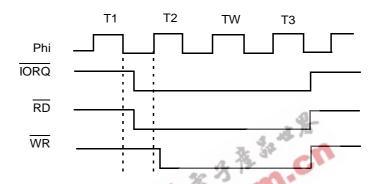

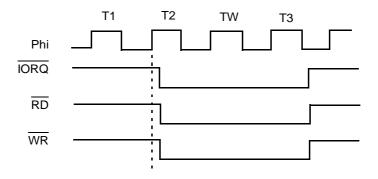

$\overline{IOC}$ : This bit controls the timing of the  $\overline{IORQ}$  and  $\overline{RD}$  signals.  $\overline{IOC}$  is set to 1 by RESET.

When  $\overline{IOC}$  is 1, the  $\overline{IORQ}$  and  $\overline{RD}$  signals function the same as the HD64180.

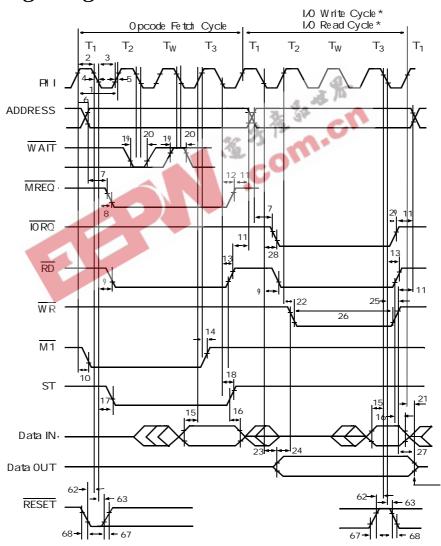

I/O Read and Write Cycles with IOC = 1 Timing Diagram Figure 7.

When IOC is 0, the timing of the IORQ and RD signals match the timing required by the Z80 family of peripherals. The  $\overline{IORQ}$  and  $\overline{RD}$  signals go active as a result of the rising edge of T2. This timing allows the Z8X180 to satisfy the setup times required by the Z80 peripherals on those two signals (Figure ).

Figure 8. I/O Read and Write cycles with IOC = 0 Timing Diagram

For the remainder of this document, assume that M1E is 0 and  $\overline{IOC}$  is 0.

The user must program the Operation Mode Control Register Note: before the first I/O instruction is executed.

### **CPU Timing**

This section explains the Z8X180 CPU timing for the following operations:

- Operand and data read/write timing

I/O read/write timin

- Basic instruction (fetch and execute) timing

- RESET timing

- BUSREQ/BUSACK bus exchange timing

The basic CPU operation consists of one or more Machine Cycles (MC). A machine cycle consists of three system clocks, T1, T2, and T3 while accessing memory or I/O, or it consists of one system clock (T1) during CPU internal operations. The system clock is half the frequency of the Crystal oscillator (that is, an 8-MHz crystal produces 4 MHz or 250 nsec). For interfacing to slow memory or peripherals, optional Wait States (TW) may be inserted between T2 and T3.

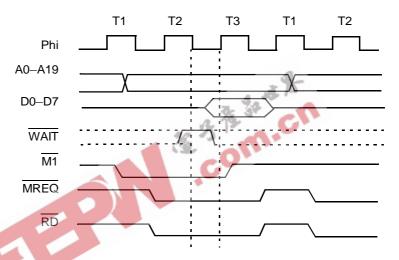

### **Instruction (Op Code) Fetch Timing**

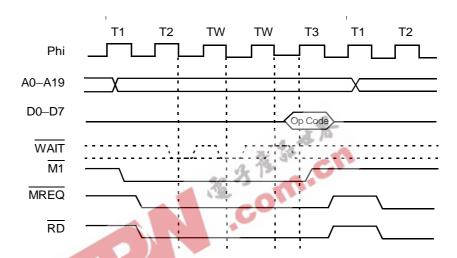

Figure 9 illustrates the instruction (Op Code) fetch timing with no Wait States. An Op Code fetch cycle is externally indicated when the  $\overline{\text{M1}}$ output pin is Low.

In the first half of T1, the address bus (A0-A19) is driven from the contents of the Program Counter (PC). This address bus is the translated address output of the Z8X180 on-chip MMU.

In the second half of T1, the  $\overline{\text{MREQ}}$ . (Memory Request) and  $\overline{\text{RD}}$  (Read) signals are asserted Low, enabling the memory.

The Op Code on the data bus is latched at the rising edge of T3 and the bus cycle terminates at the end of T3.

Op Code Fetch (without Wait State) Timing Diagram Figure 9.

Figure 10 illustrates the insertion of Wait States (TW) into the Op Code fetch cycle. Wait States (TW) are controlled by the external WAIT input combined with an on-chip programmable Wait State generator.

At the falling edge of T2 the combined  $\overline{WAIT}$  input is sampled. If  $\overline{WAIT}$ input is asserted Low, a Wait State (TW) is inserted. The address bus,  $\overline{\text{MREQ}}$ ,  $\overline{\text{RD}}$  and  $\overline{\text{M1}}$  are held stable during Wait States. When WAIT is sampled inactive High at the falling edge of TW, the bus cycle enters T3 and completes at the end of T3.

Figure 10. Op Code Fetch (with Wait State) Timing Diagram

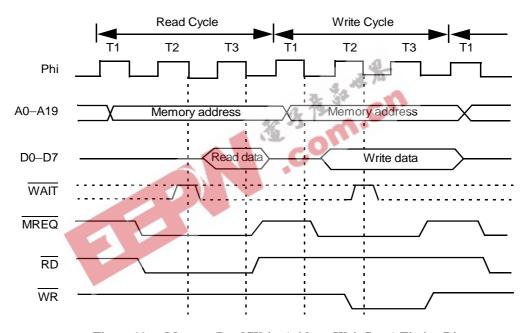

### **Operand and Data Read/Write Timing**

The instruction operand and data read/write timing differs from Op Code fetch timing in two ways:

- The  $\overline{\text{M1}}$  output is held inactive

- The read cycle timing is relaxed by one-half clock cycle because data is latched at the falling edge of T3

Instruction operands include immediate data, displacement, and extended addresses, and contain the same timing as memory data reads.

During memory write cycles the MREQ signal goes active in the second half of T1. At the end of T1, the data bus is driven with the write data.

At the start of T2, the  $\overline{WR}$  signal is asserted Low enabling the memory.  $\overline{MREQ}$  and  $\overline{WR}$  go inactive in the second half of T3 followed by disabling of the write data on the data bus.

Wait States (TW) are inserted as previously described for Op Code fetch cycles. Figure 11 illustrates the read/write timing without Wait States (Tw), while Figure 12 illustrates read/write timing with Wait States (TW).

Figure 11. Memory Read/Write (without Wait State) Timing Diagram

Figure 12. Memory Read/Write (with Wait State) Timing Diagram

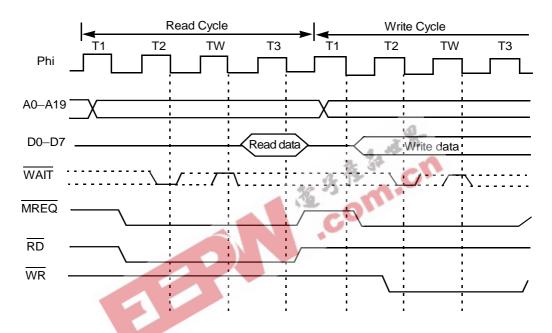

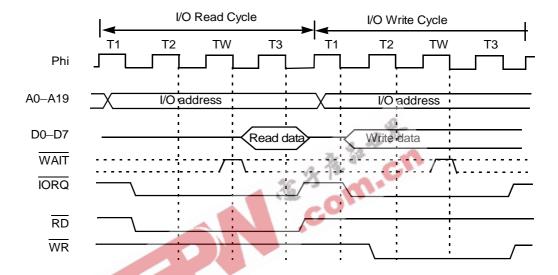

## I/O Read/Write Timing

I/O Read/Write operations differ from memory Read/Write operations in the following three ways:

- The  $\overline{IORQ}$  (I/O Request) signal is asserted Low instead of the  $\overline{MREQ}$  signal

- The 16-bit I/O address is not translated by the MMU

- A16–A19 are held Low

At least one Wait State (TW) is always inserted for I/O read and write cycles (except internal I/O cycles).

Figure 13 illustrates I/O read/write timing with the automatically inserted Wait State (TW).

Figure 13. I/O Read/Write Timing Diagram

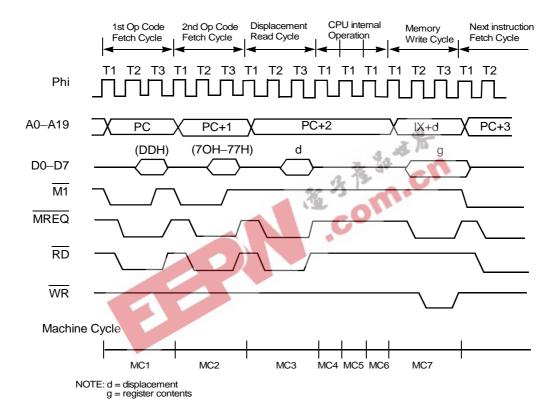

## **Basic Instruction Timing**

An instruction may consist of a number of machine cycles including Op Code fetch, operand fetch, and data read/write cycles. An instruction may also include cycles for internal processes which make the bus IDLE. The example in Figure 14 illustrates the bus timing for the data transfer instruction LD (IX+d),g.

Figure 14. Instruction Timing Diagram

This instruction moves the contents of a CPU register (g) to the memory location with address computed by adding a signed 8-bit displacement (d) to the contents of an index register (IX).

The instruction cycle begins with the two machine cycles to read the two byte instruction Op Code as indicated by  $\overline{M1}$  Low. Next, the instruction operand (d) is fetched.

**18018x** Family

The external bus is IDLE while the CPU computes the effective address. Finally, the computed memory location is written with the contents of the CPU register (g).

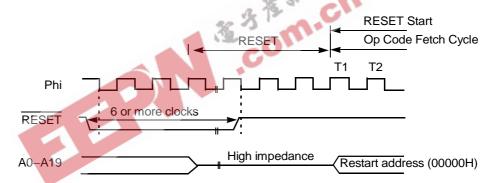

#### **RESET Timing**

Figure 15 depicts the Z8X180 hardware RESET timing. If the RESET pin is Low for six or more clock cycles, processing is terminated and the Z8X180 restarts execution from (logical and physical) address 00000H.

Figure 15. RESET Timing Diagram

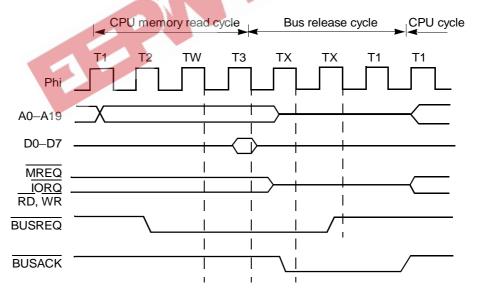

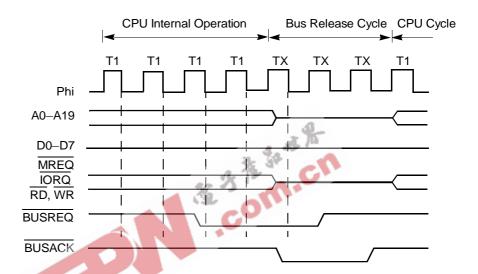

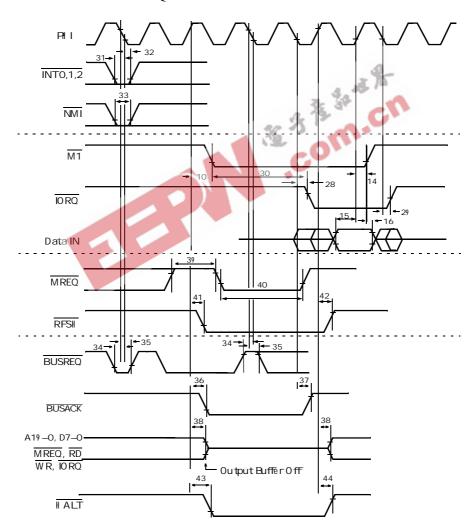

## **BUSREQ/BUSACK** Bus Exchange Timing

The Z8X180 can coordinate the exchange of control, address and data bus ownership with another bus master. The alternate bus master can request the bus release by asserting the  $\overline{BUSREQ}$  (Bus Request) input Low. After the Z8X180 releases the bus, it relinquishes control to the alternate bus master by asserting the  $\overline{BUSACK}$  (Bus Acknowledge) output Low.

The bus may be released by the Z8X180 at the end of each machine cycle. In this context, a machine cycle consists of a minimum of three clock cycles (more if wait states are inserted) for Op Code fetch, memory read/write, and I/O read/write cycles. Except for these cases, a machine cycle corresponds to one clock cycle.

When the bus is released, the address (A0–A19), data (D0–D7), and control ( $\overline{MREQ}$ ,  $\overline{IORQ}$ ,  $\overline{RD}$ , and  $\overline{WR}$ ) signals are placed in the high impedance state.

Dynamic RAM refresh is not performed when the Z8X180 has released the bus. The alternate bus master must provide dynamic memory refreshing if the bus is released for long periods of time.

Figure 16 illustrates BUSREQ/BUSACK bus exchange during a memory read cycle. Figure 17 illustrates bus exchange when the bus release is requested during a Z8X180 CPU internal operation. BUSREQ is sampled at the falling edge of the system clock prior to T3, T1 and Tx (BUS RELEASE state). If BUSREQ is asserted Low at the falling edge of the clock state prior to Tx, another Tx is executed.

Figure 16. Bus Exchange Timing During Memory Read

Figure 17. Bus Exchange Timing During CPU Internal Operation

#### **Wait State Generator**

To ease interfacing with slow memory and I/O devices, the Z8X180 uses Wait States (TW) to extend bus cycle timing. A Wait State(s) is inserted based on the combined (logical OR) state of the external WAIT input and an internal programmable wait state (TW) generator. Wait States (TW) can be inserted in both CPU execution and DMA transfer cycles.

When the external WAIT input is asserted Low, Wait State(s) (TW) are inserted between T2 and T3 to extend the bus cycle duration. The WAIT input is sampled at the falling edge of the system clock in T2 or TW. If the WAIT input is asserted Low at the falling edge of the system clock in TW, another TW is inserted into the bus cycle.

Note: WAIT input transitions must meet specified setup and hold times. This specification can easily be accomplished by

externally synchronizing  $\overline{WAIT}$  input transitions with the rising edge of the system clock.

Dynamic RAM refresh is not performed during Wait States (TW) and thus system designs which use the automatic refresh function must consider the affects of the occurrence and duration of wait states (TW). Figure 18 depicts WAIT timing.

Figure 18. WAIT Timing Diagram

## **Programmable Wait State Insertion**

In addition to the WAIT input, Wait States (TW) can also be inserted by program using the Z8X180 on-chip Wait State generator (see Figure 19. Wait State (TW) timing applies for both CPU execution and on-chip DMAC cycles.

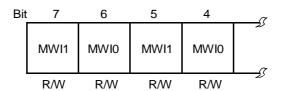

By programming the four significant bits of the DMA/Wait Control Register (DCNTL) the number of Wait States, (TW) automatically inserted in memory and I/O cycles, can be separately specified. Bits 4 and 5 specify the number of Wait States (TW) inserted for I/O access and bits 6 and 7 specify the number of Wait States (TW) inserted for memory access. These bit pairs all 0–3 programmed Wait States for either I/O or memory access.

Figure 19. Memory and I/O Wait State Insertion (DCNTL – DMA/Wait Control Register)

The number of Wait States (TW) inserted in a specific cycle is the maximum of the number requested by the WAIT input, and the number automatically generated by the on-chip Wait State generator.

## Bit 7, 6: MWII MWI0, (Memory Wait Insertion)

For CPU and DMAC cycles which access memory (including memory mapped I/O), zero to three Wait States may be automatically inserted depending on the programmed value in MWI1 and MWI0 as depicted in Table 3

Table 3.

Memory Wait States

| MW11 | MWI0 | The Number of Wait States |

|------|------|---------------------------|

| 0    | 0    | 0                         |

| 0    | 1    | 1                         |

| 1    | 0    | 2                         |

| 1    | 1    | 3                         |

#### Bit 5, 4: IWI1, IWI0 (I/O Wait Insertion)

For CPU and DMA cycles which access external I/O (and interrupt acknowledge cycles), one to six Wait States (TW) may be automatically

inserted depending on the programmed value in IWI1 and IWI0. Refer to Table 4.

**Table 4.** Wait State Insertion

|      |       |                                     | The Number of Wait States |                                                       |          |                                                                                    |  |  |  |

|------|-------|-------------------------------------|---------------------------|-------------------------------------------------------|----------|------------------------------------------------------------------------------------|--|--|--|

| W 11 | IW IO | For external I/O registers accesses | re gis te rs              | For INTO<br>interrupt<br>ack now ledge<br>cycles when | inte mal | For NM I<br>interrupt<br>ack now ledge<br>cycles<br>when M 1 is<br>Low<br>(Note 2) |  |  |  |

| 0    | 0     | 1                                   | 0)                        | 2                                                     | 2        | 0                                                                                  |  |  |  |

| 0    | 1     | 2                                   | (Note 1)                  | 4                                                     |          |                                                                                    |  |  |  |

| 1    | 0     | 3                                   |                           | 5                                                     |          |                                                                                    |  |  |  |

| 1    | 1     | 4                                   |                           | 6                                                     |          |                                                                                    |  |  |  |

#### Note:

- For Z8X180 internal I/O register access (I/O addresses 0000H-003FH), IWI1 and IWI0 do not

determine wait state (TW) timing. For ASCI, CSI/O and PRT Data Register accesses, 0 to 4 Wait States

(TW) are generated. The number of Wait States inserted during access to these registers is a function of

internal synchronization requirements and CPU state. All other on-chip I/O register accesses (that is,

MMU, DMAC, ASCI Control Registers, for instance.) have no Wait States inserted and thus require only

three clock cycles.

- 2. For interrupt acknowledge cycles in which M1 is High, such as interrupt vector table read and PC stacking cycle, memory access timing applies.

#### **WAIT Input and RESET**

During RESET, MWI1, MWI0 IWI1 and IWI0, are all 1, selecting the maximum number of Wait States (TW) (three for memory accesses, four for external I/O accesses).

Also, the  $\overline{WAIT}$  input is ignored during RESET. For example, if RESET is detected while the Z8X180 is in a Wait State (TW), the Wait Stated cycle in progress is aborted, and the RESET sequence initiated. Thus,  $\overline{RESET}$  has higher priority than  $\overline{WAIT}$ .

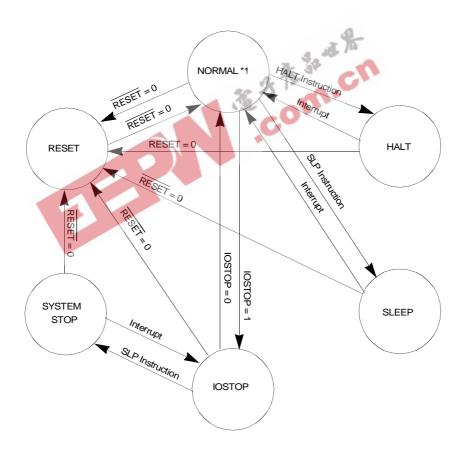

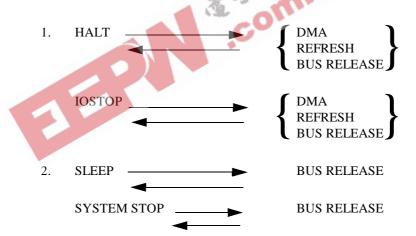

# HALT and Low Power Operation Modes (Z80180-Class Processors Only)

The Z80180 can operate in two different modes:

- HALT mode

- IOSTOP mode

and two low-power operation modes:

- SLEEP

- SYSTEM STOP

In all operating modes, the basic CPU clock (XTAL, EXTAL) must remain active.

#### **HALT Mode**

HALT mode is entered by execution of the HALT instruction (Op Code 76H) and has the following characteristics:

- The internal CPU clock remains active

- All internal and external interrupts can be received

- Bus exchange (BUSREQ and BUSACK) can occur

- Dynamic RAM refresh cycle (\overline{RFSH}) insertion continues at the programmed interval

- I/O operations (ASCI, CSI/O and PRT) continue

- The DMAC can operate

- The HALT output pin is asserted Low

- The external bus activity consists of repeated dummy fetches of the Op Code following the HALT instruction.

Essentially, the Z80180 operates normally in HALT mode, except that instruction execution is stopped.

HALT mode can be exited in the following two ways:

- RESET Exit from HALT Mode

If the RESET input is asserted Low for at least six clock cycles,

HALT mode is exited and the normal RESET sequence (restart at address 00000H) is initiated.

- Interrupt Exit from HALT mode

When an internal or external interrupt is generated, HALT mode is exited and the normal interrupt response sequence is initiated.

If the interrupt source is masked (individually by enable bit, or globally by IEF1 state), the Z80180 remains in HALT mode. However, NMI interrupt initiates the normal NMI interrupt response sequence independent of the state of IEF1.

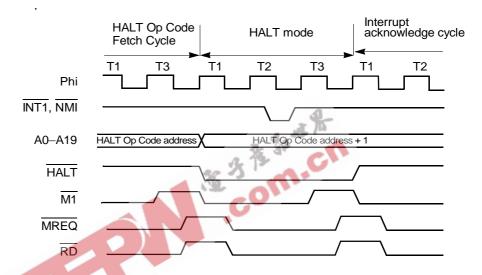

HALT timing is illustrated in Figure 20.

**HALT Timing Diagram** Figure 20.

#### **SLEEP Mode**

SLEEP mode is entered by execution of the 2-byte SLP instruction. SLEEP mode contains the following characteristics:

- The internal CPU clock stops, reducing power consumption

- The internal crystal oscillator does not stop

- Internal and external interrupt inputs can be received

- DRAM refresh cycles stop

- I/O operations using on-chip peripherals continue

- The internal DMAC stop

- BUSREQ can be received and acknowledged

- Address outputs go High and all other control signal outputs become inactive High

Data Bus, 3-state

SLEEP mode is exited in one of two ways as described below.

- RESET Exit from SLEEP mode. If the RESET input is held Low for at least six clock cycles, it exits SLEEP mode and begins the normal RESET sequence with execution starting at address (logical and physical) 00000H.

- Interrupt Exit from SLEEP mode. The SLEEP mode is exited by detection of an external (NMI, INTO, INT2) or internal (ASCI, CSI/O, PRT) interrupt.

In case of NMI, SLEEP mode is exited and the CPU begins the normal NMI interrupt response sequence.

In the case of all other interrupts, the interrupt response depends on the state of the global interrupt enable flag IEF1 and the individual interrupt source enable bit.

If the individual interrupt condition is disabled by the corresponding enable bit, occurrence of that interrupt is ignored and the CPU remains in the SLEEP mode.

Assuming the individual interrupt condition is enabled, the response to that interrupt depends on the global interrupt enable flag (IEF1). If interrupts are globally enabled (IEF1 is 1) and an individually enabled interrupt occurs, SLEEP mode is exited and the appropriate normal interrupt response sequence is executed.

If interrupts are globally disabled (IEF1 is 0) and an individually enabled interrupt occurs, SLEEP mode is exited and instruction execution begins with the instruction following the SLP instruction. This feature provides a technique for synchronization with high speed external events without incurring the latency imposed by an interrupt response sequence.

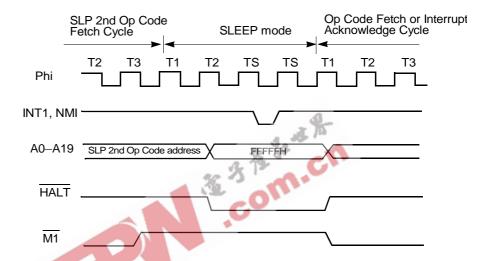

Figure 21 depicts SLEEP timing.

Figure 21. SLEEP Timing Diagram

#### **IOSTOP Mode**

IOSTOP mode is entered by setting the IOSTOP bit of the I/O Control Register (ICR) to 1. In this case, on-chip I/O (ASCI, CSI/O, PRT) stops operating. However, the CPU continues to operate. Recovery from IOSTOP mode is by resetting the IOSTOP bit in ICR to 0.

#### **SYSTEM STOP Mode**

SYSTEM STOP mode is the combination of SLEEP and IOSTOP modes. SYSTEM STOP mode is entered by setting the IOSTOP bit in ICR to 1 followed by execution of the SLP instruction. In this mode, on-chip I/O and CPU stop operating, reducing power consumption. Recovery from SYSTEM STOP mode is the same as recovery from SLEEP mode, noting that internal I/O sources, (disabled by IOSTOP) cannot generate a recovery interrupt.

36 72 36

## Low Power Modes (Z8S180/Z8L180 only)

The following section is a detailed description of the enhancements to the Z8S180/L180 from the standard Z80180 in the areas of STANDBY, IDLE and STANDBY QUICK RECOVERY modes.

#### **Add-On Features**

There are five different power-down modes. SLEEP and SYSTEM STOP are inherited from the Z80180. In SLEEP mode, the CPU is in a stopped state while the on-chip I/Os are still operating. In I/O STOP mode, the on-chip I/Os are in a stopped state while leaving the CPU running. In SYSTEM STOP mode, both the CPU and the on-chip I/Os are in the stopped state to reduce current consumption. The Z8S180 features two additional power-down modes, STANDBY and IDLE, to reduce current consumption even further. The differences in these power-down modes are summarized in Table 5.

Table 5. Power-Down Modes (Z8S180/Z8L180-Class Processors Only)

| Power-<br>Down<br>Modes | CPU Core | On-Chip<br>I/O | Osc.    | CLKOUT  | Recovery<br>Source              | Recovery Time<br>(Minimum)                                                                            |

|-------------------------|----------|----------------|---------|---------|---------------------------------|-------------------------------------------------------------------------------------------------------|

| SLEEP                   | Stop     | Running        | Running | Running | RESET,<br>Interrupts            | 1.5 Clock                                                                                             |

| I/O STOP                | Running  | Stop           | Running | Running | By<br>Programming               | _                                                                                                     |

| SYSTEM<br>STOP          | Stop     | Stop           | Running | Running | RESET,<br>Interrupts            | 1.5 Clock                                                                                             |

| IDLE †                  | Stop     | Stop           | Running | Stop    | RESET,<br>Interrupts,<br>BUSREQ | 8 + 1.5 Clock                                                                                         |

| STANDBY †               | Stop     | Stop           | Stop    | Stop    | RESET,<br>Interrupts,<br>BUSREQ | 2 <sup>17</sup> + 1.5 Clock<br>(Normal<br>Recovery)<br>2 <sup>6</sup> + 1.5 Clock<br>(Quick Recovery) |

<sup>†</sup> IDLE and STANDBY modes are only offered in the Z8S180. The minimum recovery time can be achieved if INTERRUPT is used as the Recovery Source.

## **STANDBY Mode**

The Z8S180/Z8L180 is designed to save power. Two low-power programmable power-down modes have been added:

- STANDBY mode

- IDLE mode

The STANDBY/IDLE mode is selected by multiplexing bits 1 and 3 of the CPU Control Register (CCR, I/O Address = 1FH).

To enter STANDBY mode:

- 1. Set bits 6 and 3 to 1 and 0, respectively.

- 2. Set the I/O STOP bits (bit 5 of ICR, I/O Address = 3FH) to 1.

- 3. Execute the SLEEP instruction.

When the device is in STANDBY mode, it performs similar to the SYSTEM STOP mode as it exists on the Z80180-class processors, except that the STANDBY mode stops the external oscillator, internal clocks and reduces power consumption to  $50 \,\mu\text{A}$  (typical).

Because the clock oscillator has been stopped, a restart of the oscillator requires a period of time for stabilization. An 18-bit counter has been added in the Z8S180Z8L180 to allow for oscillator stabilization. When the part receives an external IRQ or BUSREQ during STANDBY mode, the oscillator is restarted and the timer counts down  $2^{17}$  counts before acknowledgment is sent to the interrupt source.

The recovery source must remain asserted for the duration of the 2<sup>17</sup> count, otherwise STANDBY restarts.

#### STANDBY Mode Exit with BUS REQUEST

Optionally, if the BREXT bit (D5 of CPU Control Register) is set to 1, the Z8S180 exits STANDBY mode when the BUSREQ input is asserted. The crystal oscillator is then restarted. An internal counter automatically provides time for the oscillator to stabilize, before the internal clocking and the system clock output of the Z8S180 are resumed.

The Z8S180 relinquishes the system bus after the clocking is resumed by:

- 3-State the address outputs A19–A0

- 3-State the bus control outputs  $\overline{MREQ}$ ,  $\overline{IORQ}$ ,  $\overline{RD}$ , and  $\overline{WR}$

- Asserting BUSACK

The Z8S180 regains the system bus when  $\overline{BUSREQ}$  is deactivated. The address outputs and the bus control outputs are then driven High. The STANDBY mode is exited.

If the BREXT bit of the CPU Control Register (CCR) is cleared, asserting the  $\overline{BUSREQ}$  does not cause the Z8S180/Z8L180-class processors to exit STANDBY mode.

If STANDBY mode is exited because of a reset or an external interrupt, the Z8S180/Z8L180-class processors remains relinquished from the system bus as long as BUSREQ is active.

## STANDBY Mode EXit with External Interrupts

STANDBY mode can be exited by asserting input  $\overline{NMI}$ . The STANDBY mode may also exit by asserting  $\overline{INT0}$ .  $\overline{INT1}$  or  $\overline{INT2}$ , depending on the conditions specified in the following paragraphs.

INTO wake-up requires assertion throughout duration of clock stabilization time (2<sup>17</sup> clocks).

If exit conditions are met, the internal counter provides time for the crystal oscillator to stabilize, before the internal clocking and the system clock output within the Z8S180/Z8L180-class processors resume.

- Exit with Non-Maskable Interrupts

If NMI is asserted, the CPU begins a normal NMI interrupt acknowledge sequence after clocking resumes.

- Exit with External Maskable Interrupts

If an External Maskable Interrupt input is asserted, the CPU responds according to the status of the Global Interrupt Enable Flag IEF1 (determined by the ITE1 bit) and the settings of the corresponding interrupt enable bit in the Interrupt/Trap Control Register (ITC: I/O Address = 34H).

If an interrupt source is disabled in the ITC, asserting the corresponding interrupt input does not cause the Z8S180/Z8L180-class processors to exit STANDBY mode. This condition is true regardless of the state of the Global Interrupt Enable Flag IEF1.

If the Global Interrupt Enable Flag IEF1 is set to 1, and if an interrupt source is enabled in the ITC, asserting the corresponding interrupt input causes the Z8S180/Z8L180-class processors to exit STANDBY mode. The CPU performs an interrupt acknowledge sequence appropriate to the input being asserted when clocking is resumed if:

- The interrupt input follows the normal interrupt daisy-chain protocol

- The interrupt source is active until the acknowledge cycle is complete

If the Global Interrupt Enable Flag IEF1 is disabled (reset to 0) and if an interrupt source is enabled in the ITC, asserting the corresponding interrupt input still causes the Z8S180/Z8L180-class processors to exit STANDBY mode. The CPU proceeds to fetch and execute instructions that follow the SLEEP instruction when clocking resumes.

If the Extend Maskable Interrupt input is not active until clocking resumes, the Z8S180/Z8L180-class processors do not exit STANDBY mode. If the Non-Maskable Interrupt ( $\overline{NMI}$ ) is not active until clocking resumes, the Z8S180/Z8L180-class processors still exits the STANDBY mode even if the interrupt sources go away before the timer times out, because  $\overline{NMI}$  is edge-triggered. The condition is latched internally when  $\overline{NMI}$  is asserted Low.

#### **IDLE Mode**

IDLE mode is another power-down mode offered by the Z8S180/Z8L180-class processors.

- 1. Set bits 6 and 3 to 0 and 1, respectively.

- 2. Set the I/O STOP bit (bit 5 of ICR, I/O Address = 3FH to 1.

- 3. Execute the SLEEP instruction

When the part is in IDLE mode, the clock oscillator is kept oscillating, but the clock to the rest of the internal circuit, including the CLKOUT, is stopped completely. IDLE mode is exited in a similar way as STANDBY mode, using RESET, BUS REQUEST or EXTERNAL INTERRUPTS, except that the  $2^{17}$  bit wake-up timer is bypassed. All control signals are asserted eight clock cycles after the exit conditions are gathered.

#### STANDBY-QUICK RECOVERY Mode

STANDBY-QUICK RECOVERY mode is an option offered in STANDBY mode to reduce the clock recovery time in STANDBY mode from  $2^{17}$  clock cycles (4  $\mu$ s at 33 MHz) to  $2^6$  clock cycles (1.9  $\mu$ s at 33 MHz). This feature can only be used when providing an oscillator as clock source.

To enter STANDBY-QUICK RECOVERY mode:

- 1. Set bits 6 and 3 to 1 and 1, respectively.

- 2. Set the I/O STOP bit (bit 5 of ICR, I/O Address = 3FH) to 1.

- 3. Execute the SLEEP instruction

When the part is in STANDBY-QUICK RECOVERY mode, the operation is identical to STANDBY mode except when exit conditions are gathered, using RESET, BUS REQUEST or EXTERNAL INTERRUPTS. The clock and other control signals are recovered sooner than the STANDBY mode.

>

**Note:** If STANDBY-QUICK RECOVERY is enabled, the user must ensure stable oscillation is obtained within 64 clock cycles

## **Internal I/O Registers**

The Z8X180 internal I/O Registers occupy 64 I/O addresses (including reserved addresses). These registers access the internal I/O modules (ASCI, CSI/O, PRT) and control functions (DMAC, DRAM refresh, interrupts, wait state generator, MMU and I/O relocation).

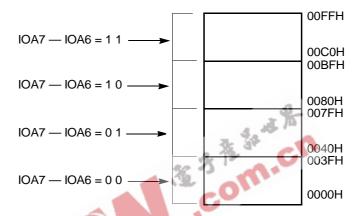

To avoid address conflicts with external I/O, the Z8X180 internal I/O addresses can be relocated on 64-byte boundaries within the bottom 256 bytes of the 64KB I/O address space.

## I/O Control Register (ICR)

ICR allows relocating of the internal I/O addresses. ICR also controls enabling/disabling of the IOSTOP mode.

## I/O Control Register (ICR: 3FH)

| Bit       | 7    | 6    | 5     | 4 | 3  | 2 | 1 | 0 |

|-----------|------|------|-------|---|----|---|---|---|

| Bit/Field | IOA7 | IOA6 | IOSTP | 1 | -O |   | _ | _ |

| R/W       | R/W  | R/W  | R/W   |   | .0 |   |   |   |

| Reset     | 0    | 0    | 0     |   |    |   |   |   |

R = Read W = Write X = Indeterminate ? = Not Applicable

| Bit<br>Position | Bit/Field | R/W Value | Description                                                                                                                                                                   |

|-----------------|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–6             | IOA7:6    | R/W       | IOA7 and IOA6 relocate internal I/O as depicted in Figure . The high-order 8 bits of 16-bit internal I/O addresses are always 0. IOA7 and IOA6 are cleared to 0 during RESET. |

| 5               | IOSTP     | R/W       | IOSTOP mode is enabled when IOSTP is set to 1.<br>Normal. I/O operation resumes when IOSTP is reset to 0.                                                                     |

Figure 22. I/O Address Relocation

## Internal I/O Registers Address Map

The internal I/O register addresses are described in Table 6 and Table 7. These addresses are relative to the 64-byte boundary base address specified in ICR.

#### I/O Addressing Notes

The internal I/O register addresses are located in the I/O address space from 0000H to 00FFH (16-bit I/O addresses). Thus, to access the internal I/O registers (using I/O instructions), the high-order 8 bits of the 16-bit I/O address must be 0.

The conventional I/O instructions (OUT (m), A/IN A, (m) / OUTI/INI, for example) place the contents of a CPU register on the high-order 8 bits of the address bus, and thus may be difficult to use for accessing internal I/O registers.

For efficient internal I/O register access, a number of new instructions have been added, which force the high-order 8 bits of the 16-bit I/O

address to 0. These instructions are IN0, OUT0, OTIM, OTIMR, OTDM, OTDMR and TSTIO (see Instruction Set).

When writing to an internal I/O register, the same I/O write occurs on the external bus. However, the duplicate external I/O write cycle exhibits internal I/O write cycle timing. For example, the  $\overline{\text{WAIT}}$  input and programmable Wait State generator are ignored. Similarly, internal I/O read cycles also cause a duplicate external I/O read cycle. However, the external read data is ignored by the Z8X180.

Normally, external I/O addresses should be chosen to avoid overlap with internal I/O addresses and duplicate I/O accesses.

Table 6. I/O Address Map for Z80180-Class Processors Only

|       |                                      |          | Ad       | ldress |      |

|-------|--------------------------------------|----------|----------|--------|------|

|       | Register                             | Mnemonic | Binary   | Hex    | Page |

| ASCI  | ASCI Control Register A Ch 0         | CNTLA0   | XX000000 | 00H    | 125  |

|       | ASCI Control Register A Ch 1         | CNTLA1   | XX000001 | 01H    | 128  |

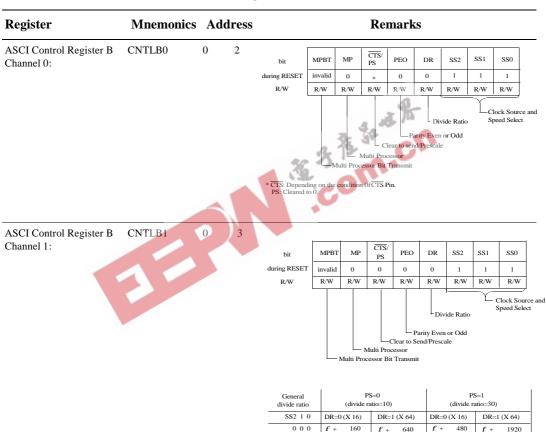

|       | ASCI Control Register B Ch 0         | CNTLB0   | XX000010 | 02H    | 132  |

|       | ASCI Control Register B Ch 1         | CNTLB1   | XX000011 | 03H    | 132  |

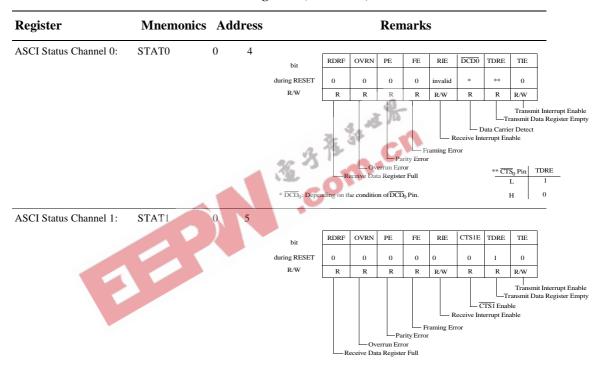

|       | ASCI Status Register Ch 0            | STAT0    | XX000100 | 04H    | 120  |

|       | ASCI Status Register Ch 1            | STAT1    | XX000101 | 05H    | 123  |

|       | ASCI Transmit Data Register Ch 0     | TDR0     | XX000110 | 06H    | 118  |

|       | ASCI Transmit Data Register Ch 1     | TDR1     | XX000111 | 07H    | 118  |

|       | ASCI Receive Data Register Ch 0      | RDR0     | XX001000 | 08H    | 119  |

|       | ASCI Receive Data Register Ch 1      | RDR1     | XX001001 | 09H    | 119  |

| CSI/O | CSI/O Control Register               | CNTR     | XX001010 | 0AH    | 147  |

|       | CSI/O Transmit/Receive Data Register | TRD      | XX1011   | 0BH    | 149  |

Table 6. I/O Address Map for Z80180-Class Processors Only (Continued)

|        |                        |          | Ac        | ddress    |      |

|--------|------------------------|----------|-----------|-----------|------|

|        | Register               | Mnemonic | Binary    | Hex       | Page |

| Timer  | Data Register Ch 0 L   | TMDR0L   | XX001100  | 0CH       | 159  |

|        | Data Register Ch 0 H   | TMDR0H   | XX001101  | 0DH       | 159  |

|        | Reload Register Ch 0 L | RLDR0L   | XX001110  | 0EH       | 159  |

|        | Reload Register Ch 0 H | RLDR0H   | XX001111  | 0FH       | 159  |

|        | Timer Control Register | TCR      | XX010000  | 10H       | 161  |

|        | Reserved               | C        | XX010001  | 11H       |      |

|        |                        |          | <b>\$</b> | <b>\$</b> |      |

|        |                        |          | XX010011  | 13H       |      |